Welcome to E-XFL.COM

### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

E·XFI

| 2 0 0 0 0 0             |                                                           |  |  |

|-------------------------|-----------------------------------------------------------|--|--|

| Product Status          | Active                                                    |  |  |

| Туре                    | Audio Processor                                           |  |  |

| Interface               | Host Interface, I <sup>2</sup> C, SAI, SPI                |  |  |

| Clock Rate              | 150MHz                                                    |  |  |

| Non-Volatile Memory     | ROM (84kB)                                                |  |  |

| On-Chip RAM             | 54kB                                                      |  |  |

| Voltage - I/O           | 3.30V                                                     |  |  |

| Voltage - Core          | 1.25V                                                     |  |  |

| Operating Temperature   | -40°C ~ 85°C (TA)                                         |  |  |

| Mounting Type           | Surface Mount                                             |  |  |

| Package / Case          | 80-LQFP                                                   |  |  |

| Supplier Device Package | 80-LQFP (14x14)                                           |  |  |

| Purchase URL            | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=dspb56374afc |  |  |

|                         |                                                           |  |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

(DMA). The DSP56374 offers 150 million instructions per second (MIPS) using an internal 150 MHz clock.

| Data Sheet Conventions                                                                                            |                                                                            |                                                                                                   |                             |                 |  |  |

|-------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------|-----------------------------|-----------------|--|--|

| This data she                                                                                                     | This data sheet uses the following conventions:                            |                                                                                                   |                             |                 |  |  |

|                                                                                                                   |                                                                            |                                                                                                   |                             |                 |  |  |

| OVERBAR                                                                                                           |                                                                            | e a signal that is ac<br>is active when low                                                       | tive when pulled lov<br>/.) | w (For example, |  |  |

| "asserted"                                                                                                        | Means that a hi<br>(active low) sigr                                       | 0 ( 0                                                                                             | h) signal is high or        | that a low true |  |  |

| "deasserted"                                                                                                      |                                                                            | Means that a high true (active high) signal is low or that a low true (active low) signal is high |                             |                 |  |  |

| Examples:                                                                                                         | Signal/<br>Symbol Logic State Signal State Voltage*                        |                                                                                                   |                             |                 |  |  |

|                                                                                                                   | -                                                                          | _                                                                                                 |                             |                 |  |  |

|                                                                                                                   | PIN True Asserted V <sub>IL</sub> / V <sub>OL</sub>                        |                                                                                                   |                             |                 |  |  |

|                                                                                                                   | $\overline{\text{PIN}}$ False Deasserted V <sub>IH</sub> / V <sub>OH</sub> |                                                                                                   |                             |                 |  |  |

|                                                                                                                   | PIN True Asserted $V_{IH} / V_{OH}$                                        |                                                                                                   |                             |                 |  |  |

|                                                                                                                   | PIN False Deasserted $V_{IL} / V_{OL}$                                     |                                                                                                   |                             |                 |  |  |

| Note: *Values for $V_{IL}$ , $V_{OL}$ , $V_{IH}$ , and $V_{OH}$ are defined by individual product specifications. |                                                                            |                                                                                                   |                             |                 |  |  |

DSP56374 Data Sheet, Rev. 4.2

• Hardware Watchdog Timer

## 2.4 Packages

80-pin and 52-pin plastic LQFP packages.

# 3 Documentation

Table 2 lists the documents that provide a complete description of the DSP56374 and are required to design properly with the part. Documentation is available from a local Freescale Semiconductor, Inc. (formerly Motorola) distributor, semiconductor sales office, Literature Distribution Center, or through the Freescale DSP home page on the Internet (the source for the latest information).

| Document Name                 | Description                                                                                             | Order Number  |

|-------------------------------|---------------------------------------------------------------------------------------------------------|---------------|

| DSP56300 Family Manual        | Detailed description of the 56300-family architecture and the 24-bit core processor and instruction set | DSP56300FM/AD |

| DSP56374 User's Manual        | Detailed description of memory, peripherals, and interfaces                                             | DSP56374UM/D  |

| DSP56374 Technical Data Sheet | Electrical and timing specifications; pin and package descriptions                                      | DSP56374      |

| DSP56374 Product Brief        | Brief description of the chip                                                                           | DSP56374PB/D  |

Table 2. DSP56374 Documentation

# 4 Signal Groupings

The input and output signals of the DSP56374 are organized into functional groups, which are listed in Table 3.

The DSP56374 is operated from a 1.25 V and 3.3 V supply; however, some of the inputs can tolerate 5.0 V. A special notice for this feature is added to the signal descriptions of those inputs.

| Functional Group           | Number of<br>Signals <sup>1</sup> | Detailed<br>Description |          |

|----------------------------|-----------------------------------|-------------------------|----------|

| Power (V <sub>DD</sub> )   |                                   | 11                      | Table 15 |

| Ground (GND)               |                                   | 9                       | Table 5  |

| Scan Pins                  | 1                                 | Table 6                 |          |

| Clock and PLL              | 3                                 | Table 7                 |          |

| Interrupt and mode control | Port H <sup>2</sup>               | 5                       | Table 8  |

| SHI                        | 5                                 | Table 9                 |          |

| ESAI                       | 12                                | Table 10                |          |

| ESAI_1                     | 12                                | Table 11                |          |

Table 3. DSP56374 Functional Signal Groupings

## 4.5 Interrupt and Mode Control

The interrupt and mode control signals select the chip's operating mode as it comes out of hardware reset. After  $\overline{\text{RESET}}$  is de-asserted, these inputs are hardware interrupt request lines.

| Signal Name | Туре                                 | State<br>during<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|--------------------------------------|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MODA/IRQA   | Input                                | MODA<br>Input            | Mode Select A/External Interrupt Request A—MODA/IRQA is an active-low Schmitt-trigger input, internally synchronized to the DSP clock. MODA/IRQA selects the initial chip operating mode during hardware reset and becomes a level-sensitive or negative-edge-triggered, maskable interrupt request input during normal instruction processing. This pin can also be programmed as GPIO. MODA, MODB, MODC, and MODD select one of 16 initial chip operating modes, latched into the OMR when the RESET signal is de-asserted. If the processor is in the stop standby state and the MODA/IRQA pin is pulled to GND, the processor will exit the stop state. This pin has an internal pull up resistor. This input is 5 V tolerant. |

| PHO         | Input, output,<br>or<br>disconnected |                          | Port H0—When the MODA/IRQA is configured as GPIO, this signal is individually programmable as input, output, or internally disconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MODB/IRQB   | Input                                | MODB<br>Input            | Mode Select B/External Interrupt Request B—MODB/IRQB is an<br>active-low Schmitt-trigger input, internally synchronized to the DSP<br>clock. MODB/IRQB selects the initial chip operating mode during<br>hardware reset and becomes a level-sensitive or<br>negative-edge-triggered, maskable interrupt request input during<br>normal instruction processing. This pin can also be programmed as<br>GPIO. MODA, MODB, MODC, and MODD select one of 16 initial chip<br>operating modes, latched into OMR when the RESET signal is<br>de-asserted.<br>This pin has an internal pull up resistor.<br>This input is 5 V tolerant.                                                                                                     |

| PH1         | Input, output,<br>or<br>disconnected |                          | Port H1—When the MODB/IRQB is configured as GPIO, this signal is individually programmable as input, output, or internally disconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MODC/IRQC   | Input                                | MODC<br>Input            | Mode Select C/External Interrupt Request C—MODC/IRQC is an active-low Schmitt-trigger input, internally synchronized to the DSP clock. MODC/IRQC selects the initial chip operating mode during hardware reset and becomes a level-sensitive or negative-edge-triggered, maskable interrupt request input during normal instruction processing. This pin can also be programmed as GPIO. MODA, MODB, MODC, and MODD select one of 16 initial chip operating modes, latched into OMR when the RESET signal is de-asserted.<br>This pin has an internal pull up resistor.<br>This input is 5 V tolerant.                                                                                                                             |

### Table 8. Interrupt and Mode Control

| Signal Name | Туре                                 | State<br>during<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-------------|--------------------------------------|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PH2         | Input, output,<br>or<br>disconnected |                          | Port H2—When the MODC/IRQC is configured as GPIO, this signal is individually programmable as input, output, or internally disconnected.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| MODD/IRQD   | Input                                | MODD<br>Input            | Mode Select D/External Interrupt Request D—MODD/IRQD is an active-low Schmitt-trigger input, internally synchronized to the DSP clock. MODD/IRQD selects the initial chip operating mode during hardware reset and becomes a level-sensitive or negative-edge-triggered, maskable interrupt request input during normal instruction processing. This pin can also be programmed as GPIO. MODA, MODB, MODC, and MODD select one of 16 initial chip operating modes, latched into OMR when the RESET signal is de-asserted.                                 |

|             |                                      |                          | This pin has an internal pull up resistor.<br>This input is 5 V tolerant.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| PH3         | Input, output,<br>or<br>disconnected |                          | Port H3—When the MODD/IRQD is configured as GPIO, this signal is individually programmable as input, output, or internally disconnected.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RESET       | Input                                | Input                    | Reset— <u>RESET</u> is an active-low, Schmitt-trigger input. When asserted, the chip is placed in the Reset state and the internal phase generator is reset. The Schmitt-trigger input allows a slowly rising input (such as a capacitor charging) to reset the chip reliably. When the <u>RESET</u> signal is de-asserted, the initial chip operating mode is latched from the MODA, MODB, MODC, and MODD inputs. The <u>RESET</u> signal must be asserted during power up. A stable EXTAL signal must be supplied while <u>RESET</u> is being asserted. |

|             |                                      |                          | This pin has an internal pull up resistor.<br>This input is 5 V tolerant.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Table 8. Interrupt and Mode | Control (continued) |

|-----------------------------|---------------------|

|-----------------------------|---------------------|

## 4.6 Serial Host Interface

The SHI has five I/O signals that can be configured to allow the SHI to operate in either SPI or I<sup>2</sup>C mode.

| Signal<br>Name | Signal Type                      | State during<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|----------------|----------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SCK            | Input or output                  | Tri-stated            | SPI Serial Clock—The SCK signal is an output when the SPI is configured as a master and a Schmitt-trigger input when the SPI is configured as a slave. When the SPI is configured as a master, the SCK signal is derived from the internal SHI clock generator. When the SPI is configured as a slave, the SCK signal is an input, and the clock signal from the external master synchronizes the data transfer. The SCK signal is ignored by the SPI if it is defined as a slave and the slave select ( $\overline{SS}$ ) signal is not asserted. In both the master and slave SPI devices, data is shifted on one edge of the SCK signal and is sampled on the opposite edge where data is stable. Edge polarity is determined by the SPI transfer protocol.            |

| SCL            | Input or output                  |                       | $\rm I^2C$ Serial Clock—SCL carries the clock for $\rm I^2C$ bus transactions in the $\rm I^2C$ mode. SCL is a Schmitt-trigger input when configured as a slave and an open-drain output when configured as a master. SCL should be connected to $\rm V_{DD}$ through an external pull-up resistor according to the $\rm I^2C$ specifications.                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                |                                  |                       | This signal is tri-stated during hardware, software, and individual reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                |                                  |                       | This pin has an internal pull up resistor.<br>This input is 5 V tolerant.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| MISO           | Input or output                  | Tri-stated            | SPI Master-In-Slave-Out—When the SPI is configured as a master, MISO is the master data input line. The MISO signal is used in conjunction with the MOSI signal for transmitting and receiving serial data. This signal is a Schmitt-trigger input when configured for the SPI Master mode, an output when configured for the SPI Slave mode, and tri-stated if configured for the SPI Slave mode when $\overline{SS}$ is de-asserted. An external pull-up resistor is not required for SPI operation.                                                                                                                                                                                                                                                                    |

| SDA            | Input or<br>open-drain<br>output |                       | $\rm I^2C$ Data and Acknowledge—In $\rm I^2C$ mode, SDA is a Schmitt-trigger input when receiving and an open-drain output when transmitting. SDA should be connected to V <sub>DD</sub> through a pull-up resistor. SDA carries the data for I <sup>2</sup> C transactions. The data in SDA must be stable during the high period of SCL. The data in SDA is only allowed to change when SCL is low. When the bus is free, SDA is high. The SDA line is only allowed to change during the time SCL is high in the case of start and stop events. A high-to-low transition of the SDA line while SCL is high is a unique situation, and is defined as the start event. A low-to-high transition of SDA while SCL is high is a unique situation defined as the stop event. |

|                |                                  |                       | This signal is tri-stated during hardware, software, and individual reset.<br>Thus, there is no need for an external pull-up in this state.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                |                                  |                       | This pin has an internal pull up resistor.<br>This input is 5 V tolerant.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Table 9. | Serial | Host | Interface | Signals |

|----------|--------|------|-----------|---------|

|----------|--------|------|-----------|---------|

## 4.7 Enhanced Serial Audio Interface

Table 10. Enhanced Serial Audio Interface Signals

| Signal Name | Signal Type                       | State during<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                               |

|-------------|-----------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HCKR        | Input or output                   | GPIO<br>disconnected  | High Frequency Clock for Receiver—When programmed<br>as an input, this signal provides a high frequency clock<br>source for the ESAI receiver as an alternate to the DSP<br>core clock. When programmed as an output, this signal can<br>serve as a high-frequency sample clock (e.g., for external<br>digital to analog converters [DACs]) or as an additional<br>system clock. |

| PC2         | Input, output, or<br>disconnected |                       | Port C2—When the ESAI is configured as GPIO, this signal<br>is individually programmable as input, output, or internally<br>disconnected.<br>The default state after reset is GPIO disconnected.<br>This pin has an internal pull up resistor.                                                                                                                                   |

|             |                                   |                       | This input is 5 V tolerant.                                                                                                                                                                                                                                                                                                                                                      |

| НСКТ        | Input or output                   | GPIO<br>disconnected  | High Frequency Clock for Transmitter—When programmed<br>as an input, this signal provides a high frequency clock<br>source for the ESAI transmitter as an alternate to the DSP<br>core clock. When programmed as an output, this signal can<br>serve as a high frequency sample clock (e.g., for external<br>DACs) or as an additional system clock.                             |

| PC5         | Input, output, or<br>disconnected |                       | Port C5—When the ESAI is configured as GPIO, this signal is individually programmable as input, output, or internally disconnected.                                                                                                                                                                                                                                              |

|             |                                   |                       | The default state after reset is GPIO disconnected.                                                                                                                                                                                                                                                                                                                              |

|             |                                   |                       | This pin has an internal pull up resistor.<br>This input is 5 V tolerant.                                                                                                                                                                                                                                                                                                        |

|             |                                   | [                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|-----------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name | Signal Type                       | State during<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SCKR        | Input or output                   | GPIO<br>disconnected  | Receiver Serial Clock—SCKR provides the receiver serial<br>bit clock for the ESAI. The SCKR operates as a clock input<br>or output used by all the enabled receivers in the<br>asynchronous mode (SYN=0), or as serial flag 0 pin in the<br>synchronous mode (SYN=1).                                                                                                                                                                                                                                                                                                                      |

|             |                                   |                       | When this pin is configured as serial flag pin, its direction is<br>determined by the RCKD bit in the RCCR register. When<br>configured as the output flag OF0, this pin will reflect the<br>value of the OF0 bit in the SAICR register, and the data in<br>the OF0 bit will show up at the pin synchronized to the<br>frame sync in normal mode or the slot in network mode.<br>When configured as the input flag IF0, the data value at the<br>pin will be stored in the IF0 bit in the SAISR register,<br>synchronized by the frame sync in normal mode or the slot<br>in network mode. |

| PC0         | Input, output, or disconnected    |                       | Port C0—When the ESAI is configured as GPIO, this signal is individually programmable as input, output, or internally disconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                                   |                       | The default state after reset is GPIO disconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                                   |                       | Internal Pull down resistor.<br>This input is 5 V tolerant.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| SCKT        | Input or output                   | GPIO<br>disconnected  | Transmitter Serial Clock—This signal provides the serial bit<br>rate clock for the ESAI. SCKT is a clock input or output used<br>by all enabled transmitters and receivers in synchronous<br>mode, or by all enabled transmitters in asynchronous<br>mode.                                                                                                                                                                                                                                                                                                                                 |

| PC3         | Input, output, or<br>disconnected |                       | Port C3—When the ESAI is configured as GPIO, this signal is individually programmable as input, output, or internally disconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                                   |                       | The default state after reset is GPIO disconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             |                                   |                       | Internal Pull down resistor.<br>This input is 5 V tolerant.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Signal Name | Signal Type                       | State during<br>Reset | Signal Description                                                                                                                               |  |  |  |

|-------------|-----------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SDO5        | Output                            | GPIO<br>disconnected  | Serial Data Output 5—When programmed as a transmitter,<br>SDO5 is used to transmit data from the TX5 serial transmit<br>shift register.          |  |  |  |

| SDI0        | Input                             |                       | Serial Data Input 0—When programmed as a receiver,<br>SDI0 is used to receive serial data into the RX0 serial<br>receive shift register.         |  |  |  |

| PC6         | Input, output, or disconnected    |                       | Port C6—When the ESAI is configured as GPIO, this signal is individually programmable as input, output, or internally disconnected.              |  |  |  |

|             |                                   |                       | The default state after reset is GPIO disconnected.                                                                                              |  |  |  |

|             |                                   |                       | Internal Pull down resistor.<br>This input is 5 V tolerant.                                                                                      |  |  |  |

| SDO4        | Output                            | GPIO<br>disconnected  | Serial Data Output 4—When programmed as a transmitter,<br>SDO4 is used to transmit data from the TX4 serial transmit<br>shift register.          |  |  |  |

| SDI1        | Input                             |                       | Serial Data Input 1—When programmed as a receiver,<br>SDI1 is used to receive serial data into the RX1 serial<br>receive shift register.         |  |  |  |

| PC7         | Input, output, or disconnected    |                       | Port C7—When the ESAI is configured as GPIO, this signal is individually programmable as input, output, or internally disconnected.              |  |  |  |

|             |                                   |                       | The default state after reset is GPIO disconnected.                                                                                              |  |  |  |

|             |                                   |                       | Internal Pull down resistor.<br>This input is 5 V tolerant.                                                                                      |  |  |  |

| SDO3        | Output                            | GPIO<br>disconnected  | <b>Serial Data Output 3</b> —When programmed as a transmitter, SDO3 is used to transmit data from the TX3 serial transmit shift register.        |  |  |  |

| SDI2        | Input                             |                       | <b>Serial Data Input 2</b> —When programmed as a receiver,<br>SDI2 is used to receive serial data into the RX2 serial<br>receive shift register. |  |  |  |

| PC8         | Input, output, or<br>disconnected |                       | Port C8—When the ESAI is configured as GPIO, this signal is individually programmable as input, output, or internally disconnected.              |  |  |  |

|             |                                   |                       | The default state after reset is GPIO disconnected.                                                                                              |  |  |  |

|             |                                   |                       | Internal Pull down resistor.<br>This input is 5 V tolerant.                                                                                      |  |  |  |

| Signal Name | Signal Type                       | State during<br>Reset | Signal Description                                                                                                                       |

|-------------|-----------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| _           |                                   | Resel                 |                                                                                                                                          |

| SDO2        | Output                            | GPIO<br>disconnected  | Serial Data Output 2—When programmed as a transmitter,<br>SDO2 is used to transmit data from the TX2 serial transmit<br>shift register   |

| SDI3        | Input                             |                       | Serial Data Input 3—When programmed as a receiver,<br>SDI3 is used to receive serial data into the RX3 serial<br>receive shift register. |

| PC9         | Input, output, or<br>disconnected |                       | Port C9—When the ESAI is configured as GPIO, this signal is individually programmable as input, output, or internally disconnected.      |

|             |                                   |                       | The default state after reset is GPIO disconnected.                                                                                      |

|             |                                   |                       | Internal Pull down resistor.<br>This input is 5 V tolerant.                                                                              |

| SDO1        | Output                            | GPIO<br>disconnected  | Serial Data Output 1—SDO1 is used to transmit data from the TX1 serial transmit shift register.                                          |

| PC10        | Input, output, or disconnected    |                       | Port C10—When the ESAI is configured as GPIO, this signal is individually programmable as input, output, or internally disconnected.     |

|             |                                   |                       | The default state after reset is GPIO disconnected.                                                                                      |

|             |                                   |                       | Internal Pull down resistor.<br>This input is 5 V tolerant.                                                                              |

| SDO0        | Output                            | GPIO<br>disconnected  | Serial Data Output 0—SDO0 is used to transmit data from the TX0 serial transmit shift register.                                          |

| PC11        | Input, output, or<br>disconnected |                       | Port C11—When the ESAI is configured as GPIO, this signal is individually programmable as input, output, or internally disconnected.     |

|             |                                   |                       | The default state after reset is GPIO disconnected.                                                                                      |

|             |                                   |                       | Internal Pull down resistor.<br>This input is 5 V tolerant.                                                                              |

## 4.8 Enhanced Serial Audio Interface\_1

Table 11. Enhanced Serial Audio Interface\_1 Signals

| Signal Name | Signal Type                       | State during<br>Reset | Signal Description                                                                                                                                                                                                                                                                                                                                                                 |

|-------------|-----------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HCKR_1      | Input or output                   | GPIO<br>disconnected  | High Frequency Clock for Receiver—When programmed as<br>an input, this signal provides a high frequency clock source<br>for the ESAI_1 receiver as an alternate to the DSP core<br>clock. When programmed as an output, this signal can<br>serve as a high-frequency sample clock (e.g., for external<br>digital to analog converters [DACs]) or as an additional<br>system clock. |

| PE2         | Input, output, or<br>disconnected |                       | Port E2—When the ESAI_1 is configured as GPIO, this signal is individually programmable as input, output, or internally disconnected.                                                                                                                                                                                                                                              |

|             |                                   |                       | The default state after reset is GPIO disconnected.<br>Internal Pull down resistor.<br>This input is 5 V tolerant.                                                                                                                                                                                                                                                                 |

| HCKT_1      | Input or output                   | GPIO<br>disconnected  | High Frequency Clock for Transmitter—When programmed<br>as an input, this signal provides a high frequency clock<br>source for the ESAI_1 transmitter as an alternate to the<br>DSP core clock. When programmed as an output, this<br>signal can serve as a high frequency sample clock (e.g., for<br>external DACs) or as an additional system clock.                             |

| PE5         | Input, output, or<br>disconnected |                       | Port E5—When the ESAI_1 is configured as GPIO, this signal is individually programmable as input, output, or internally disconnected.                                                                                                                                                                                                                                              |

|             |                                   |                       | The default state after reset is GPIO disconnected.                                                                                                                                                                                                                                                                                                                                |

|             |                                   |                       | Internal Pull down resistor.<br>This input is 5 V tolerant.                                                                                                                                                                                                                                                                                                                        |

# 4.9 Dedicated GPIO-Port G

Table 12. Dedicated GPIO-Port G Signals

| Signal<br>Name | Туре                                 | State During<br>Reset | Signal Description                                                                                                                                              |

|----------------|--------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PG0            | Input,<br>output, or<br>disconnected | GPIO<br>disconnected  | Port G0—This signal is individually programmable as input,<br>output, or internally disconnected.<br>Internal Pull down resistor.<br>This input is 5 V tolerant |

| PG1            | Input,<br>output, or<br>disconnected | GPIO<br>disconnected  | Port G1—This signal is individually programmable as input,<br>output, or internally disconnected.<br>Internal Pull down resistor.<br>This input is 5 V tolerant |

| PG2            | Input,<br>output, or<br>disconnected | GPIO<br>disconnected  | Port G2—This signal is individually programmable as input,<br>output, or internally disconnected.<br>Internal Pull down resistor.<br>This input is 5 V tolerant |

| PG3            | Input,<br>output, or<br>disconnected | GPIO<br>disconnected  | Port G3—This signal is individually programmable as input,<br>output, or internally disconnected.<br>Internal Pull down resistor.<br>This input is 5 V tolerant |

| PG4            | Input,<br>output, or<br>disconnected | GPIO<br>disconnected  | Port G4—This signal is individually programmable as input,<br>output, or internally disconnected.<br>Internal Pull down resistor.<br>This input is 5 V tolerant |

| PG5            | Input,<br>output, or<br>disconnected | GPIO<br>disconnected  | Port G5—This signal is individually programmable as input,<br>output, or internally disconnected.<br>Internal Pull down resistor.<br>This input is 5 V tolerant |

| PG6            | Input,<br>output, or<br>disconnected | GPIO<br>disconnected  | Port G6—This signal is individually programmable as input,<br>output, or internally disconnected.<br>Internal Pull down resistor.<br>This input is 5 V tolerant |

| PG7            | Input,<br>output, or<br>disconnected | GPIO<br>disconnected  | Port G7—This signal is individually programmable as input,<br>output, or internally disconnected.<br>Internal Pull down resistor.<br>This input is 5 V tolerant |

| PG8            | Input,<br>output, or<br>disconnected | GPIO<br>disconnected  | Port G8—This signal is individually programmable as input,<br>output, or internally disconnected.<br>Internal Pull down resistor.<br>This input is 5 V tolerant |

| Signal<br>Name | Туре   | State<br>during<br>Reset | Signal Description                                                                                                                                                                                                                                                                                           |

|----------------|--------|--------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PLOCK          | Output |                          | PLOCK—When this pin is configured as a PLL lock pin, this signal is<br>asserted high when the on-chip PLL enabled and locked and<br>de-asserted when the PLL enabled and unlocked. This pin is also<br>asserted high when the PLL is disabled.<br>Internal Pull down resistor.<br>This input is 5 V tolerant |

## 4.11 JTAG/OnCE Interface

| Signal<br>Name | Signal<br>Type | State<br>during<br>Reset | Signal Description                                                                                                                                                                                                               |

|----------------|----------------|--------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ТСК            | Input          | Input                    | Test Clock—TCK is a test clock input signal used to synchronize the JTAG test logic.<br>Internal Pull up resistor.                                                                                                               |

|                |                |                          | This input is 5 V tolerant.                                                                                                                                                                                                      |

| TDI            | Input          | Input                    | Test Data Input—TDI is a test data serial input signal used for test instructions and data. TDI is sampled on the rising edge of TCK.                                                                                            |

|                |                |                          | Internal Pull up resistor.<br>This input is 5 V tolerant.                                                                                                                                                                        |

| TDO            | Output         | Tri-stated               | Test Data Output—TDO is a test data serial output signal used for test instructions and data. TDO is tri-statable and is actively driven in the shift-IR and shift-DR controller states. TDO changes on the falling edge of TCK. |

| TMS            | Input          | Input                    | Test Mode Select—TMS is an input signal used to sequence the test controller's state machine. TMS is sampled on the rising edge of TCK.                                                                                          |

|                |                |                          | Internal Pull up resistor.<br>This input is 5 V tolerant.                                                                                                                                                                        |

### Table 14. JTAG/OnCE Interface

## 5 Maximum Ratings

### CAUTION

This device contains circuitry protecting against damage due to high static voltage or electrical fields. However, normal precautions should be taken to avoid exceeding maximum voltage ratings. Reliability of operation is enhanced if unused inputs are pulled to an appropriate logic voltage level (e.g., either GND or  $V_{DD}$ ). The suggested value for a pullup or pulldown resistor is 4.7 k $\Omega$ .

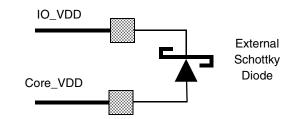

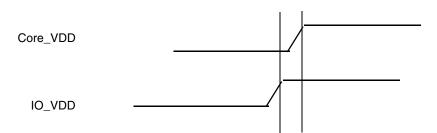

To prevent a high current condition upon power up, the IO\_VDD must be applied ahead of the Core\_VDD as shown below if the external Schottky is not used.

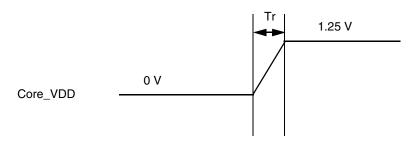

For correct operation of the internal power on reset logic, the Core\_VDD ramp rate (Tr) to full supply must be less than 10 ms. This is shown below.

# 7 Thermal Characteristics

### **Table 16. Thermal Characteristics**

| Characteristic                                                                                                                                                                                                                                | Symbol                           | LQFP Values                  | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|------------------------------|------|

| Natural Convection, Junction-to-ambient thermal resistance <sup>1,2</sup>                                                                                                                                                                     | $R_{\theta JA}$ or $\theta_{JA}$ | 68 (52 LQFP)<br>50 (80 LQFP) | °C/W |

| Junction-to-case thermal resistance <sup>3</sup>                                                                                                                                                                                              | $R_{\theta JC}$ or $\theta_{JC}$ | 17 (52 LQFP)<br>11 (80 LQFP) | °C/W |

| Note:<br><sup>1</sup> Junction temperature is a function of die size, on-ch<br>mounting site (board) temperature, ambient temper<br>on the board, and board thermal resistance.<br><sup>2</sup> Per SEMI G38-87 and JEDEC JESD51-2 with the s | ature, air flow, pow             | er dissipation of ot         |      |

<sup>3</sup> Thermal resistance between the die and the case top surface as measured by the cold plate method (MIL SPEC-883 Method 1012.1).

DSP56374 Data Sheet, Rev. 4.2

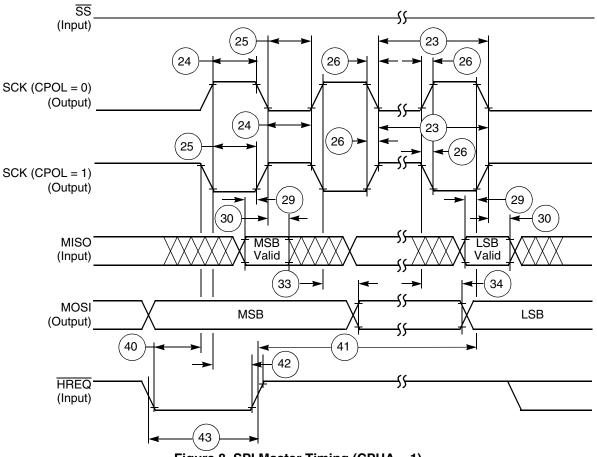

# 13 Serial Host Interface SPI Protocol Timing

| No. | Characteristics <sup>1,3,4</sup>                      | Mode         | Filter Mode | Expression                   | Min   | Max | Unit |

|-----|-------------------------------------------------------|--------------|-------------|------------------------------|-------|-----|------|

| 23  | Minimum serial clock cycle = t <sub>SPICC</sub> (min) | Master/Slave | Bypassed    | 10.0 x T <sub>C</sub> + 9    | 76.0  | _   | ns   |

|     |                                                       |              | Very Narrow | 10.0 x T <sub>C</sub> + 9    | 76.0  |     | ns   |

|     |                                                       |              | Narrow      | 10.0 x T <sub>C</sub> + 133  | 200.0 |     | ns   |

|     |                                                       |              | Wide        | 10.0 x T <sub>C</sub> + 333  | 400.0 |     | ns   |

| XX  | Tolerable Spike width on data or clock in.            | _            | Bypassed    | _                            | —     | 0   | ns   |

|     |                                                       |              | Very Narrow |                              | —     | 10  | ns   |

|     |                                                       |              | Narrow      | —                            | —     | 50  | ns   |

|     |                                                       |              | Wide        |                              | —     | 100 | ns   |

| 24  | Serial clock high period                              | Master       | Bypassed    |                              | 38.0  | _   | ns   |

|     |                                                       |              | Very Narrow |                              | 38.0  |     | ns   |

|     |                                                       |              | Narrow      |                              | 100.0 | _   | ns   |

|     |                                                       |              | Wide        |                              | 200.0 | _   | ns   |

|     |                                                       | Slave        | Bypassed    | 2.0 x T <sub>C</sub> + 19.6  | 33.0  | _   | ns   |

|     |                                                       |              | Very Narrow | 2.0 x T <sub>C</sub> + 19.6  | 33.0  | _   | ns   |

|     |                                                       |              | Narrow      | 2.0 x T <sub>C</sub> + 86.6  | 100.0 | _   | ns   |

|     |                                                       |              | Wide        | 2.0 x T <sub>C</sub> + 186.6 | 200.0 | _   | ns   |

| 25  | Serial clock low period                               | Master       | Bypassed    | _                            | 38.0  | _   | ns   |

|     |                                                       |              | Very Narrow | _                            | 38.0  | _   | ns   |

|     |                                                       |              | Narrow      |                              | 100.0 | _   | ns   |

|     |                                                       |              | Wide        |                              | 200.0 | _   | ns   |

|     |                                                       | Slave        | Bypassed    | 2.0 x T <sub>C</sub> + 19.6  | 33.0  | _   | ns   |

|     |                                                       |              | Very Narrow | 2.0 x T <sub>C</sub> + 19.6  | 33.0  | _   | ns   |

|     |                                                       |              | Narrow      | 2.0 x T <sub>C</sub> + 86.6  | 100.0 |     | ns   |

|     |                                                       |              | Wide        | 2.0 x T <sub>C</sub> + 186.6 | 200.0 |     | ns   |

| 26  | Serial clock rise/fall time                           | Master       | —           | —                            | —     | —   | ns   |

|     |                                                       | Slave        | —           | —                            |       | 5   | ns   |

|     |                                                       |              |             | _                            |       |     |      |

## Table 21. Serial Host Interface SPI Protocol Timing

### Serial Host Interface (SHI) I<sup>2</sup>C Protocol Timing

|     |                                                                                                                                   | Standard I <sup>2</sup> C                      |                              |               |                              |               |                          |

|-----|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------|---------------|------------------------------|---------------|--------------------------|

|     | Oberranden: 12345                                                                                                                 | Symbol/                                        | Standard                     |               | Fast-Mode                    |               | Unit                     |

| No. | Characteristics <sup>1,2,3,4,5</sup>                                                                                              | Expression                                     | Min                          | Max           | Min                          | Max           |                          |

| 47  | Start condition hold time                                                                                                         | T <sub>HD;STA</sub>                            | 4.0                          | —             | 0.6                          | —             | μs                       |

| 48  | SCL low period                                                                                                                    | T <sub>LOW</sub>                               | 4.7                          | —             | 1.3                          | —             | μs                       |

| 49  | SCL high period                                                                                                                   | T <sub>HIGH</sub>                              | 4.0                          | —             | 1.3                          | —             | μs                       |

| 50  | SCL and SDA rise time                                                                                                             | т <sub>R</sub>                                 | —                            | 5.0           |                              | 5.0           | ns                       |

| 51  | SCL and SDA fall time                                                                                                             | T <sub>F</sub>                                 | —                            | 5.0           |                              | 5.0           | ns                       |

| 52  | Data set-up time                                                                                                                  | T <sub>SU;DAT</sub>                            | 250                          | _             | 100                          | _             | ns                       |

| 53  | Data hold time                                                                                                                    | T <sub>HD;DAT</sub>                            | 0.0                          | _             | 0.0                          | 0.9           | μs                       |

| 54  | DSP clock frequency<br>• Filters bypassed<br>• Very Narrrow filters enabled<br>• Narrow filters enabled<br>• Wide filters enabled | F <sub>osc</sub>                               | 10.6<br>10.6<br>11.8<br>13.1 |               | 28.5<br>28.5<br>39.7<br>61.0 | _<br>_<br>_   | MHz<br>MHz<br>MHz<br>MHz |

| 55  | SCL low to data out valid                                                                                                         | T <sub>VD;DAT</sub>                            | _                            | 3.4           |                              | 0.9           | μs                       |

| 56  | Stop condition setup time                                                                                                         | T <sub>SU;STO</sub>                            | 4.0                          | _             | 0.6                          | _             | μs                       |

| 57  | HREQ in deassertion to last SCL edge<br>(HREQ in set-up time)                                                                     | t <sub>SU;RQI</sub>                            | 0.0                          |               | 0.0                          |               | ns                       |

| 58  | First SCL sampling edge to HREQ output deassertion <sup>2</sup>                                                                   | T <sub>NG;RQO</sub>                            |                              |               |                              |               |                          |

|     | Filters bypassed                                                                                                                  | $4 \times T_{C} + 30$<br>$4 \times T_{C} + 50$ | —                            | 57.0          | —                            | 57.0          | ns                       |

|     | <ul> <li>Very Narrow filters enabled</li> <li>Narrow filters enabled</li> </ul>                                                   | $4 \times T_{\rm C} + 130$                     | _                            | 77.0<br>157.0 |                              | 67.0<br>157.0 | ns<br>ns                 |

|     | Wide filters enabled                                                                                                              | $4 \times T_{C} + 230$                         | _                            | 257.0         | _                            | 257.0         | ns                       |

| 59  | Last SCL edge to HREQ output not deasserted <sup>2</sup>                                                                          | T <sub>AS;RQO</sub>                            |                              |               |                              |               |                          |

|     | <ul> <li>Filters bypassed</li> </ul>                                                                                              | $2 \times T_{C} + 30$                          | 44                           |               | 44                           | —             | ns                       |

|     | Very Narrow filters enabled                                                                                                       | $2 \times T_{C} + 40$                          | 54                           | —             | 54                           | —             | ns                       |

|     | <ul> <li>Narrow filters enabled</li> </ul>                                                                                        | $2 \times T_{C} + 80$                          | 94                           |               | 94                           | —             | ns                       |

|     | Wide filters enabled                                                                                                              | 2 × T <sub>C</sub> + 130                       | 144                          | —             | 144                          | —             | ns                       |

| 60  | <ul> <li>HREQ in assertion to first SCL edge</li> <li>Filters bypassed</li> <li>Very Narrow filters enabled</li> </ul>            | T <sub>AS;RQI</sub>                            | 4327<br>4317                 |               | 927<br>917                   | _             | ns<br>ns                 |

|     | <ul> <li>Narrow filters enabled</li> </ul>                                                                                        |                                                | 4282                         | —             | 877                          | _             | ns                       |

|     | Wide filters enabled                                                                                                              |                                                | 4227                         | —             | 827                          | -             | ns                       |

| 61  | First SCL edge to HREQ is not asserted (HREQ in hold time.)                                                                       | t <sub>HO;RQI</sub>                            | 0.0                          | —             | 0.0                          | —             | ns                       |

## Table 22. SHI I<sup>2</sup>C Protocol Timing (continued)

### Enhanced Serial Audio Interface Timing

| No. | Characteristics <sup>1, 2, 3</sup>                                | Symbol | Expression <sup>3</sup> | Min         | Max         | Condition <sup>4</sup> | Unit |

|-----|-------------------------------------------------------------------|--------|-------------------------|-------------|-------------|------------------------|------|

| 88  | SCKT edge to transmitter #0 drive enable deassertion <sup>7</sup> | _      | —                       |             | 14.0<br>9.0 | x ck<br>i ck           | ns   |

| 89  | FST input (bl, wr) setup time before SCKT edge <sup>6</sup>       |        |                         | 2.0<br>18.0 |             | x ck<br>i ck           | ns   |

| 90  | FST input (wl) setup time before SCKT edge                        | —      | _                       | 2.0<br>18.0 | _           | x ck<br>i ck           | ns   |

| 91  | FST input hold time after SCKT edge                               | —      | _                       | 4.0<br>5.0  | _           | x ck<br>i ck           | ns   |

| 92  | FST input (wl) to data out enable from high impedance             | _      |                         | —           | 21.0        | _                      | ns   |

| 93  | FST input (wl) to transmitter #0 drive enable assertion           | _      | _                       | —           | 14.0        | —                      | ns   |

| 94  | Flag output valid after SCKT rising edge                          | —      |                         |             | 14.0<br>9.0 | x ck<br>i ck           | ns   |

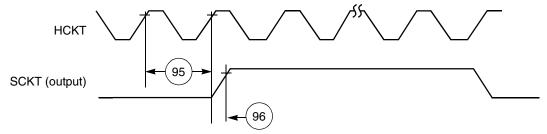

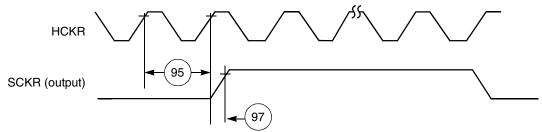

| 95  | HCKR/HCKT clock cycle                                             | _      | 2 x T <sub>C</sub>      | 13.4        | —           |                        | ns   |

| 96  | HCKT input edge to SCKT output                                    | —      | _                       | —           | 18.0        |                        | ns   |

| 97  | HCKR input edge to SCKR output                                    | _      | —                       |             | 18.0        |                        | ns   |

### Table 24. Enhanced Serial Audio Interface Timing (continued)

Note:

$^{1}$  V<sub>CORE\_VDD</sub> = 1.25 ± 0.05 V; T<sub>J</sub> = -40°C to 110°C (52 LQFP) / -40°C to 105°C (80 LQFP), C<sub>L</sub> = 50 pF

<sup>2</sup> i ck = internal clock

x ck = external clock

i ck a = internal clock, asynchronous mode

(asynchronous implies that SCKT and SCKR are two different clocks)

i ck s = internal clock, synchronous mode

(synchronous implies that SCKT and SCKR are the same clock)

- <sup>3</sup> bl = bit length

- wl = word length

- wr = word length relative

- <sup>4</sup> SCKT(SCKT pin) = transmit clock SCKR(SCKR pin) = receive clock FST(FST pin) = transmit frame sync FSR(FSR pin) = receive frame sync HCKT(HCKT pin) = transmit high frequency clock HCKR(HCKR pin) = receive high frequency clock