#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                             |

|----------------------------|----------------------------------------------------------------------|

| Core Processor             | ST7                                                                  |

| Core Size                  | 8-Bit                                                                |

| Speed                      | 8MHz                                                                 |

| Connectivity               | SCI, SPI                                                             |

| Peripherals                | POR, PWM, WDT                                                        |

| Number of I/O              | 24                                                                   |

| Program Memory Size        | 8KB (8K x 8)                                                         |

| Program Memory Type        | FLASH                                                                |

| EEPROM Size                | -                                                                    |

| RAM Size                   | 384 x 8                                                              |

| Voltage - Supply (Vcc/Vdd) | 3.8V ~ 5.5V                                                          |

| Data Converters            | A/D 8x10b                                                            |

| Oscillator Type            | External                                                             |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                        |

| Package / Case             | 32-LQFP                                                              |

| Supplier Device Package    | -                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/st72f32ak2t6 |

|                            |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| 2 PIN D<br>3 REG | ODUCTION<br>DESCRIPTION<br>ISTER & MEMORY MAP<br>SH PROGRAM MEMORY | 8<br>13 |

|------------------|--------------------------------------------------------------------|---------|

| 4.1              | INTRODUCTION                                                       |         |

| 4.2              | MAIN FEATURES                                                      |         |

| 4.3              | STRUCTURE                                                          | 17      |

|                  | 4.3.1 Read-out Protection                                          | 17      |

| 4.4              |                                                                    | 18      |

| 4.5              | ICP (IN-CIRCUIT PROGRAMMING)                                       | 19      |

| 4.6              | IAP (IN-APPLICATION PROGRAMMING)                                   | 19      |

| 4.7              | RELATED DOCUMENTATION                                              | 19      |

|                  | 4.7.1 Register Description                                         |         |

|                  | TRAL PROCESSING UNIT                                               |         |

| 5.1              |                                                                    |         |

| 5.2              | MAIN FEATURES                                                      |         |

| 5.3              | CPU REGISTERS                                                      |         |

|                  | PLY, RESET AND CLOCK MANAGEMENT                                    |         |

| 6.1              | PHASE LOCKED LOOP                                                  |         |

| 6.2              | MULTI-OSCILLATOR (MO)                                              |         |

| 6.3              | RESET SEQUENCE MANAGER (RSM)                                       |         |

|                  | 6.3.1 Introduction                                                 |         |

|                  | 6.3.2 Asynchronous External RESET pin                              |         |

|                  | 6.3.3 External Power-On RESET 2   6.3.4 Internal Watchdog RESET 2  |         |

| 6.4              | SYSTEM INTEGRITY MANAGEMENT                                        |         |

|                  | 6.4.1 Register Description                                         |         |

| 7 INTE           | RRUPTS                                                             |         |

| 7.1              |                                                                    | 28      |

| 7.2              | MASKING AND PROCESSING FLOW                                        | 28      |

| 7.3              | INTERRUPTS AND LOW POWER MODES                                     | 30      |

| 7.4              | CONCURRENT & NESTED MANAGEMENT                                     | 30      |

| 7.5              | INTERRUPT REGISTER DESCRIPTION                                     | 31      |

| 7.6              | EXTERNAL INTERRUPTS                                                | 33      |

|                  | 7.6.1 I/O Port Interrupt Sensitivity                               | 33      |

| 7.7              | EXTERNAL INTERRUPT CONTROL REGISTER (EICR)                         | 35      |

| 8 POW            | /ER SAVING MODES                                                   | 37      |

| 8.1              |                                                                    | 37      |

| 8.2              | SLOW MODE                                                          |         |

| 8.3              | WAIT MODE                                                          | 38      |

| 8.4              | ACTIVE-HALT AND HALT MODES                                         | 39      |

|                  | 8.4.1 ACTIVE-HALT MODE                                             |         |

|                  | 8.4.2 HALT MODE                                                    | 40      |

57

| Address        | Block   | Register<br>Label | Register Name                                             | Reset<br>Status | Remarks   |

|----------------|---------|-------------------|-----------------------------------------------------------|-----------------|-----------|

| 0031h          |         | TACR2             | Timer A Control Register 2                                | 00h             | R/W       |

| 0032h          |         | TACR1             | Timer A Control Register 1                                | 00h             | R/W       |

| 0033h          |         | TACSR             | Timer A Control/Status Register                           | xxxx x0xxb      | R/W       |

| 0034h          |         | TAIC1HR           | Timer A Input Capture 1 High Register                     | xxh             | Read Only |

| 0035h          |         | TAIC1LR           | Timer A Input Capture 1 Low Register                      | xxh             | Read Only |

| 0036h          |         | TAOC1HR           | Timer A Output Compare 1 High Register                    | 80h             | R/W       |

| 0037h          |         | TAOC1LR           | Timer A Output Compare 1 Low Register                     | 00h             | R/W       |

| 0038h          | TIMER A | TACHR             | Timer A Counter High Register                             | FFh             | Read Only |

| 0039h          |         | TACLR             | Timer A Counter Low Register                              | FCh             | Read Only |

| 003Ah          |         | TAACHR            | Timer A Alternate Counter High Register                   | FFh             | Read Only |

| 003Bh          |         | TAACLR            | Timer A Alternate Counter Low Register                    | FCh             | Read Only |

| 003Ch          |         | TAIC2HR           | Timer A Input Capture 2 High Register                     | xxh             | Read Only |

| 003Dh          |         | TAIC2LR           | Timer A Input Capture 2 Low Register                      | xxh             | Read Only |

| 003Eh          |         | TAOC2HR           | Timer A Output Compare 2 High Register                    | 80h             | R/W       |

| 003Fh          |         | TAOC2LR           | Timer A Output Compare 2 Low Register                     | 00h             | R/W       |

| 0040h          |         |                   | Reserved Area (1 Byte)                                    |                 |           |

|                |         |                   |                                                           |                 |           |

| 0041h          |         | TBCR2             | Timer B Control Register 2                                | 00h             | R/W       |

| 0042h          |         | TBCR1             | Timer B Control Register 1                                | 00h             | R/W       |

| 0043h          |         | TBCSR             | Timer B Control/Status Register                           | xxxx x0xxb      | R/W       |

| 0044h          |         | TBIC1HR           | Timer B Input Capture 1 High Register                     | xxh             | Read Only |

| 0045h          |         | TBIC1LR           | Timer B Input Capture 1 Low Register                      | xxh             | Read Only |

| 0046h          |         | TBOC1HR           | Timer B Output Compare 1 High Register                    | 80h             | R/W       |

| 0047h          |         | TBOC1LR           | Timer B Output Compare 1 Low Register                     | 00h             | R/W       |

| 0048h          | TIMER B | TBCHR             | Timer B Counter High Register                             | FFh             | Read Only |

| 0049h          |         | TBCLR             | Timer B Counter Low Register                              | FCh             | Read Only |

| 004Ah          |         | TBACHR            | Timer B Alternate Counter High Register                   | FFh             | Read Only |

| 004Bh          |         | TBACLR            | Timer B Alternate Counter Low Register                    | FCh             | Read Only |

| 004Ch          |         | TBIC2HR           | Timer B Input Capture 2 High Register                     | xxh             | Read Only |

| 004Dh          |         | TBIC2LR           | Timer B Input Capture 2 Low Register                      | xxh             | Read Only |

| 004Eh          |         | TBOC2HR           | Timer B Output Compare 2 High Register                    | 80h             | R/W       |

| 004Fh          |         | TBOC2LR           | Timer B Output Compare 2 Low Register                     | 00h             | R/W       |

| 00505          |         | 00100             | COL Status Desister                                       | 004             | Deed Only |

| 0050h          |         | SCISR             | SCI Status Register                                       | C0h             | Read Only |

| 0051h          |         | SCIDR             | SCI Data Register                                         | xxh             | R/W       |

| 0052h          |         | SCIBRR            | SCI Baud Rate Register                                    | 00h             | R/W       |

| 0053h          | SCI     | SCICR1            | SCI Control Register 1                                    | x000 0000h      | R/W       |

| 0054h          |         | SCICR2            | SCI Control Register 2                                    | 00h             | R/W       |

| 0055h          |         | SCIERPR           | SCI Extended Receive Prescaler Register                   | 00h             | R/W       |

| 0056h<br>0057h |         | SCIETPR           | Reserved area<br>SCI Extended Transmit Prescaler Register | <br>00h         | R/W       |

|                |         |                   | Sor Extended Hansmit Flescaler negister                   | 001             | I 1/ VV   |

| 0058h          |         |                   | Beconved Area (04 Pitter)                                 |                 |           |

| to<br>006Fh    |         |                   | Reserved Area (24 Bytes)                                  |                 |           |

| 000F11         |         | 1                 | I                                                         | 1               |           |

| 0070h          |         | ADCCSR            | Control/Status Register                                   | 00h             | R/W       |

| 0071h          | ADC     | ADCDRH            | Data High Register                                        | 00h             | Read Only |

| 0072h          |         | ADCDRL            | Data Low Register                                         | 00h             | Read Only |

| 0073h<br>007Fh |         | 1                 | Reserved Area (13 Bytes)                                  | 1               |           |

Legend: x=undefined, R/W=read/write

## Notes:

- 1. The contents of the I/O port DR registers are readable only in output configuration. In input configuration, the values of the I/O pins are returned instead of the DR register contents.

- 2. The bits associated with unavailable pins must always keep their reset value.

## INTERRUPTS (Cont'd)

## 7.3 INTERRUPTS AND LOW POWER MODES

All interrupts allow the processor to exit the WAIT low power mode. On the contrary, only external and other specified interrupts allow the processor to exit from the HALT modes (see column "Exit from HALT" in "Interrupt Mapping" table). When several pending interrupts are present while exiting HALT mode, the first one serviced can only be an interrupt with exit from HALT mode capability and it is selected through the same decision process shown in Figure 16.

**Note:** If an interrupt, that is not able to Exit from HALT mode, is pending with the highest priority when exiting HALT mode, this interrupt is serviced after the first one serviced.

## 7.4 CONCURRENT & NESTED MANAGEMENT

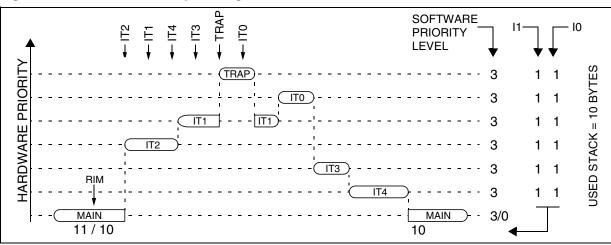

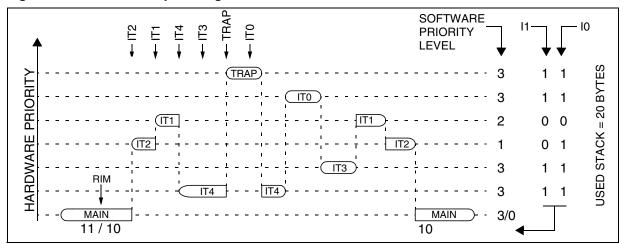

The following Figure 17 and Figure 18 show two different interrupt management modes. The first is called concurrent mode and does not allow an interrupt to be interrupted, unlike the nested mode in Figure 18. The interrupt hardware priority is given in this order from the lowest to the highest: MAIN, IT4, IT3, IT2, IT1, IT0. The software priority is given for each interrupt.

**Warning**: A stack overflow may occur without notifying the software of the failure.

**47**/

#### Figure 17. Concurrent Interrupt Management

Figure 18. Nested Interrupt Management

## **INTERRUPTS** (Cont'd)

## 7.7 EXTERNAL INTERRUPT CONTROL REGISTER (EICR)

#### Read/Write

Reset Value: 0000 0000 (00h)

| 7    |      |     |      |      |     |   | 0 |

|------|------|-----|------|------|-----|---|---|

| IS11 | IS10 | IPB | IS21 | IS20 | IPA | 0 | 0 |

Bit 7:6 = IS1[1:0] ei2 and ei3 sensitivity The interrupt sensitivity, defined using the IS1[1:0] bits, is applied to the following external interrupts: - ei2 (port B3..0)

| IS11 | IS10 | External Interrupt Sensitivity   |                             |  |  |  |  |

|------|------|----------------------------------|-----------------------------|--|--|--|--|

| 1311 | 1010 | IPB bit =0                       | IPB bit =1                  |  |  |  |  |

| 0    | 0    | Falling edge &<br>low level      | Rising edge<br>& high level |  |  |  |  |

| 0    | 1    | Rising edge only                 | Falling edge only           |  |  |  |  |

| 1    | 0    | Falling edge only Rising edge on |                             |  |  |  |  |

| 1    | 1    | Rising and falling edge          |                             |  |  |  |  |

- ei3 (port B4)

| IS11 | IS10 | External Interrupt Sensitivity |

|------|------|--------------------------------|

| 0    | 0    | Falling edge & low level       |

| 0    | 1    | Rising edge only               |

| 1    | 0    | Falling edge only              |

| 1    | 1    | Rising and falling edge        |

These 2 bits can be written only when I1 and I0 of the CC register are both set to 1 (level 3).

#### Bit 5 = **IPB** Interrupt polarity for port B

This bit is used to invert the sensitivity of the port B [3:0] external interrupts. It can be set and cleared by software only when I1 and I0 of the CC register are both set to 1 (level 3).

0: No sensitivity inversion

1: Sensitivity inversion

Bit 4:3 = **IS2[1:0]** ei0 and ei1 sensitivity The interrupt sensitivity, defined using the IS2[1:0] bits, is applied to the following external interrupts:

- ei0 (port A3..0)

| IS21 | IS20 | External Interrupt Sensitivity |                             |  |  |  |

|------|------|--------------------------------|-----------------------------|--|--|--|

| 1321 | 1320 | IPA bit =0                     | IPA bit =1                  |  |  |  |

| 0    | 0    | Falling edge &<br>low level    | Rising edge<br>& high level |  |  |  |

| 0    | 1    | Rising edge only               | Falling edge only           |  |  |  |

| 1    | 0    | Falling edge only              | Rising edge only            |  |  |  |

| 1    | 1    | Rising and                     | falling edge                |  |  |  |

- ei1 (port F2..0)

| IS21 | IS20 | External Interrupt Sensitivity |

|------|------|--------------------------------|

| 0    | 0    | Falling edge & low level       |

| 0    | 1    | Rising edge only               |

| 1    | 0    | Falling edge only              |

| 1    | 1    | Rising and falling edge        |

These 2 bits can be written only when I1 and I0 of the CC register are both set to 1 (level 3).

#### Bit 2 = **IPA** Interrupt polarity for port A

This bit is used to invert the sensitivity of the port A [3:0] external interrupts. It can be set and cleared by software only when I1 and I0 of the CC register are both set to 1 (level 3). 0: No sensitivity inversion

1: Sensitivity inversion

Bits 1:0 = Reserved, must always be kept cleared.

## POWER SAVING MODES (Cont'd)

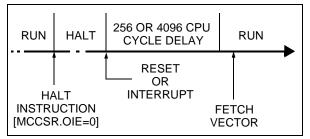

#### 8.4.2 HALT MODE

The HALT mode is the lowest power consumption mode of the MCU. It is entered by executing the 'HALT' instruction when the OIE bit of the Main Clock Controller Status register (MCCSR) is cleared (see Section 10.2 on page 53 for more details on the MCCSR register).

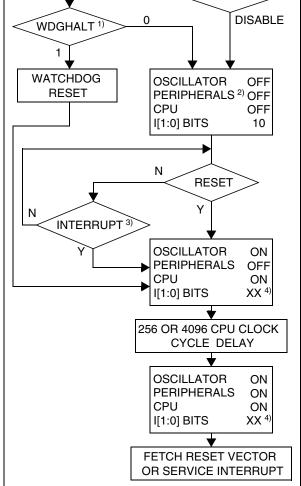

The MCU can exit HALT mode on reception of either a specific interrupt (see Table 8, "Interrupt Mapping," on page 33) or a RESET. When exiting HALT mode by means of a RESET or an interrupt, the oscillator is immediately turned on and the 256 or 4096 CPU cycle delay is used to stabilize the oscillator. After the start up delay, the CPU resumes operation by servicing the interrupt or by fetching the reset vector which woke it up (see Figure 26).

When entering HALT mode, the I[1:0] bits in the CC register are forced to '10b'to enable interrupts. Therefore, if an interrupt is pending, the MCU wakes up immediately.

In HALT mode, the main oscillator is turned off causing all internal processing to be stopped, including the operation of the on-chip peripherals. All peripherals are not clocked except the ones which get their clock supply from another clock generator (such as an external or auxiliary oscillator).

The compatibility of Watchdog operation with HALT mode is configured by the "WDGHALT" option bit of the option byte. The HALT instruction when executed while the Watchdog system is enabled, can generate a Watchdog RESET (see Section 14.1 on page 145) for more details.

HALT INSTRUCTION (MCCSR.OIE=0) ENABLE WATCHDOG WDGHALT 1) 0 DISAE

Figure 26. HALT Mode Flow-chart

#### Notes:

1. WDGHALT is an option bit. See option byte section for more details.

2. Peripheral clocked with an external clock source can still be active.

3. Only some specific interrupts can exit the MCU from HALT mode (such as external interrupt). Refer to Table 8, "Interrupt Mapping," on page 33 for more details.

4. Before servicing an interrupt, the CC register is pushed on the stack. The I[1:0] bits of the CC register are set to the current software priority level of the interrupt routine and recovered when the CC register is popped.

## more de-

#### I/O PORTS (Cont'd)

**CAUTION**: The alternate function must not be activated as long as the pin is configured as input with interrupt, in order to avoid generating spurious interrupts.

#### Analog alternate function

When the pin is used as an ADC input, the I/O must be configured as floating input. The analog multiplexer (controlled by the ADC registers) switches the analog voltage present on the selected pin to the common analog rail which is connected to the ADC input.

It is recommended not to change the voltage level or loading on any port pin while conversion is in progress. Furthermore it is recommended not to have clocking pins located close to a selected analog pin.

**WARNING**: The analog input voltage level must be within the limits stated in the absolute maximum ratings.

#### 9.3 I/O PORT IMPLEMENTATION

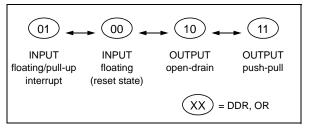

The hardware implementation on each I/O port depends on the settings in the DDR and OR registers and specific feature of the I/O port such as ADC Input or true open drain.

Switching these I/O ports from one state to another should be done in a sequence that prevents unwanted side effects. Recommended safe transitions are illustrated in Figure 28 Other transitions are potentially risky and should be avoided, since they are likely to present unwanted side-effects such as spurious interrupt generation.

#### Figure 28. Interrupt I/O Port State Transitions

#### 9.4 LOW POWER MODES

| Mode Description |                                                                                      |  |  |

|------------------|--------------------------------------------------------------------------------------|--|--|

| WAIT             | No effect on I/O ports. External interrupts cause the device to exit from WAIT mode. |  |  |

| HALT             | No effect on I/O ports. External interrupts cause the device to exit from HALT mode. |  |  |

#### 9.5 INTERRUPTS

The external interrupt event generates an interrupt if the corresponding configuration is selected with DDR and OR registers and the interrupt mask in the CC register is not active (RIM instruction).

| Interrupt Event                               | Interrupt Event Flag |             | Exit<br>from<br>Wait | Exit<br>from<br>Halt |

|-----------------------------------------------|----------------------|-------------|----------------------|----------------------|

| External interrupt on selected external event | -                    | DDRx<br>ORx | Yes                  | Yes                  |

| Address<br>(Hex.) | Register<br>Label | 7    | 6  | 5  | 4  | 3  | 2  | 1  | 0  |

|-------------------|-------------------|------|----|----|----|----|----|----|----|

| 002Ah             | WDGCR             | WDGA | T6 | T5 | T4 | T3 | T2 | T1 | T0 |

|                   | Reset Value       | 0    | 1  | 1  | 1  | 1  | 1  | 1  | 1  |

## Table 14. Watchdog Timer Register Map and Reset Values

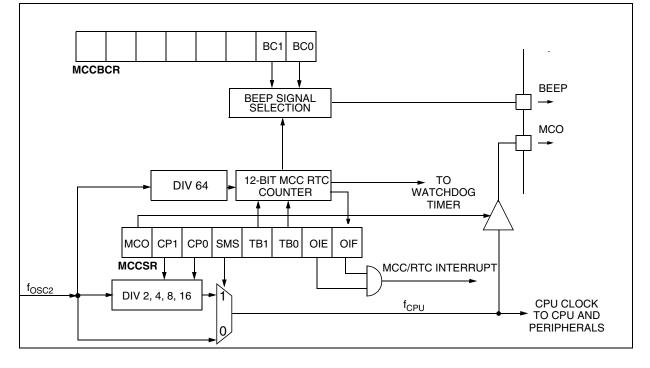

## 10.2 MAIN CLOCK CONTROLLER WITH REAL TIME CLOCK AND BEEPER (MCC/RTC)

The Main Clock Controller consists of three different functions:

- a programmable CPU clock prescaler

- a clock-out signal to supply external devices

- a real time clock timer with interrupt capability

Each function can be used independently and simultaneously.

#### 10.2.1 Programmable CPU Clock Prescaler

The programmable CPU clock prescaler supplies the clock for the ST7 CPU and its internal peripherals. It manages SLOW power saving mode (See Section 8.2 SLOW MODE for more details).

The prescaler selects the  $f_{CPU}$  main clock frequency and is controlled by three bits in the MCCSR register: CP[1:0] and SMS.

#### 10.2.2 Clock-out Capability

47/

The clock-out capability is an alternate function of an I/O port pin that outputs a  $f_{OSC2}$  clock to drive

external devices. It is controlled by the MCO bit in the MCCSR register.

**CAUTION**: When selected, the clock out pin suspends the clock during ACTIVE-HALT mode.

#### 10.2.3 Real Time Clock Timer (RTC)

The counter of the real time clock timer allows an interrupt to be generated based on an accurate real time clock. Four different time bases depending directly on  $f_{OSC2}$  are available. The whole functionality is controlled by four bits of the MCC-SR register: TB[1:0], OIE and OIF.

When the RTC interrupt is enabled (OIE bit set), the ST7 enters ACTIVE-HALT mode when the HALT instruction is executed. See Section 8.4 AC-TIVE-HALT AND HALT MODES for more details.

#### 10.2.4 Beeper

The beep function is controlled by the MCCBCR register. It can output three selectable frequencies on the BEEP pin (I/O port alternate function).

#### Figure 32. Main Clock Controller (MCC/RTC) Block Diagram

#### 16-BIT TIMER (Cont'd)

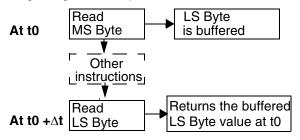

**16-bit read sequence:** (from either the Counter Register or the Alternate Counter Register).

#### Beginning of the sequence

Sequence completed

The user must read the MS Byte first, then the LS Byte value is buffered automatically.

This buffered value remains unchanged until the 16-bit read sequence is completed, even if the user reads the MS Byte several times.

After a complete reading sequence, if only the CLR register or ACLR register are read, they return the LS Byte of the count value at the time of the read.

Whatever the timer mode used (input capture, output compare, one pulse mode or PWM mode) an overflow occurs when the counter rolls over from FFFFh to 0000h then:

- The TOF bit of the SR register is set.

- A timer interrupt is generated if:

- TOIE bit of the CR1 register is set and

- I bit of the CC register is cleared.

If one of these conditions is false, the interrupt remains pending to be issued as soon as they are both true. Clearing the overflow interrupt request is done in two steps:

1. Reading the SR register while the TOF bit is set. 2. An access (read or write) to the CLR register.

**Notes:** The TOF bit is not cleared by accesses to ACLR register. The advantage of accessing the ACLR register rather than the CLR register is that it allows simultaneous use of the overflow function and reading the free running counter at random times (for example, to measure elapsed time) without the risk of clearing the TOF bit erroneously.

The timer is not affected by WAIT mode.

In HALT mode, the counter stops counting until the mode is exited. Counting then resumes from the previous count (MCU awakened by an interrupt) or from the reset count (MCU awakened by a Reset).

#### 10.3.3.2 External Clock

The external clock (where available) is selected if CC0=1 and CC1=1 in the CR2 register.

The status of the EXEDG bit in the CR2 register determines the type of level transition on the external clock pin EXTCLK that will trigger the free running counter.

The counter is synchronized with the falling edge of the internal CPU clock.

A minimum of four falling edges of the CPU clock must occur between two consecutive active edges of the external clock; thus the external clock frequency must be less than a quarter of the CPU clock frequency.

## 16-BIT TIMER (Cont'd)

## Figure 40. Output Compare Timing Diagram, f<sub>TIMER</sub> =f<sub>CPU</sub>/2

| INTERNAL CPU CLOCK<br>TIMER CLOCK<br>COUNTER REGISTER |      |

|-------------------------------------------------------|------|

| OUTPUT COMPARE REGISTER <i>i</i> (OCR <i>i</i> )      | 2ED3 |

| OUTPUT COMPARE FLAG i (OCFi)                          |      |

| OCMP <i>i</i> PIN (OLVL <i>i</i> =1)                  |      |

|                                                       |      |

## Figure 41. Output Compare Timing Diagram, $f_{TIMER} = f_{CPU}/4$

| INTERNAL CPU CLOCK<br>TIMER CLOCK<br>COUNTER REGISTER<br>OUTPUT COMPARE REGISTER <i>i</i> (OCR <i>i</i> ) |  |

|-----------------------------------------------------------------------------------------------------------|--|

| COMPARE REGISTER / LATCH                                                                                  |  |

| OUTPUT COMPARE FLAG <i>i</i> (OCF <i>i</i> )                                                              |  |

| OCMP <i>i</i> PIN (OLVL <i>i</i> =1)                                                                      |  |

## SERIAL COMMUNICATIONS INTERFACE (Cont'd)

#### 10.5.4.2 Transmitter

The transmitter can send data words of either 8 or 9 bits depending on the M bit status. When the M bit is set, word length is 9 bits and the 9th bit (the MSB) has to be stored in the T8 bit in the SCICR1 register.

#### **Character Transmission**

During an SCI transmission, data shifts out least significant bit first on the TDO pin. In this mode, the SCIDR register consists of a buffer (TDR) between the internal bus and the transmit shift register (see Figure 51).

#### Procedure

- Select the M bit to define the word length.

- Select the desired baud rate using the SCIBRR and the SCIETPR registers.

- Set the TE bit to assign the TDO pin to the alternate function and to send a idle frame as first transmission.

- Access the SCISR register and write the data to send in the SCIDR register (this sequence clears the TDRE bit). Repeat this sequence for each data to be transmitted.

Clearing the TDRE bit is always performed by the following software sequence:

- 1. An access to the SCISR register

- 2. A write to the SCIDR register

The TDRE bit is set by hardware and it indicates:

- The TDR register is empty.

- The data transfer is beginning.

- The next data can be written in the SCIDR register without overwriting the previous data.

This flag generates an interrupt if the TIE bit is set and the I bit is cleared in the CCR register.

When a transmission is taking place, a write instruction to the SCIDR register stores the data in the TDR register and which is copied in the shift register at the end of the current transmission.

When no transmission is taking place, a write instruction to the SCIDR register places the data directly in the shift register, the data transmission starts, and the TDRE bit is immediately set. When a frame transmission is complete (after the stop bit) the TC bit is set and an interrupt is generated if the TCIE is set and the I bit is cleared in the CCR register.

Clearing the TC bit is performed by the following software sequence:

1. An access to the SCISR register

A write to the SCIDR register

**Note:** The TDRE and TC bits are cleared by the same software sequence.

#### **Break Characters**

Setting the SBK bit loads the shift register with a break character. The break frame length depends on the M bit (see Figure 52).

As long as the SBK bit is set, the SCI send break frames to the TDO pin. After clearing this bit by software the SCI insert a logic 1 bit at the end of the last break frame to guarantee the recognition of the start bit of the next frame.

#### **Idle Characters**

Setting the TE bit drives the SCI to send an idle frame before the first data frame.

Clearing and then setting the TE bit during a transmission sends an idle frame after the current word.

**Note:** Resetting and setting the TE bit causes the data in the TDR register to be lost. Therefore the best time to toggle the TE bit is when the TDRE bit is set i.e. before writing the next byte in the SCIDR.

## SERIAL COMMUNICATIONS INTERFACE (Cont'd)

#### 10.5.4.7 Parity Control

Parity control (generation of parity bit in transmission and parity checking in reception) can be enabled by setting the PCE bit in the SCICR1 register. Depending on the frame length defined by the M bit, the possible SCI frame formats are as listed in Table 20.

| M bit | PCE bit | SCI frame                  |

|-------|---------|----------------------------|

| 0     | 0       | SB   8 bit data   STB      |

| 0     | 1       | SB   7-bit data   PB   STB |

| 1     | 0       | SB   9-bit data   STB      |

| 1     | 1       | SB   8-bit data PB   STB   |

**Legend:** SB = Start Bit, STB = Stop Bit,

PB = Parity Bit

**Note:** In case of wake up by an address mark, the MSB bit of the data is taken into account and not the parity bit

**Even parity:** the parity bit is calculated to obtain an even number of "1s" inside the frame made of the 7 or 8 LSB bits (depending on whether M is equal to 0 or 1) and the parity bit.

Ex: data=00110101; 4 bits set => parity bit will be 0 if even parity is selected (PS bit = 0).

**Odd parity:** the parity bit is calculated to obtain an odd number of "1s" inside the frame made of the 7 or 8 LSB bits (depending on whether M is equal to 0 or 1) and the parity bit.

Ex: data=00110101; 4 bits set => parity bit will be 1 if odd parity is selected (PS bit = 1).

**Transmission mode:** If the PCE bit is set then the MSB bit of the data written in the data register is not transmitted but is changed by the parity bit.

**Reception mode:** If the PCE bit is set then the interface checks if the received data byte has an

even number of "1s" if even parity is selected (PS=0) or an odd number of "1s" if odd parity is selected (PS=1). If the parity check fails, the PE flag is set in the SCISR register and an interrupt is generated if PIE is set in the SCICR1 register.

#### 10.5.4.8 SCI Clock Tolerance

During reception, each bit is sampled 16 times. The majority of the 8th, 9th and 10th samples is considered as the bit value. For a valid bit detection, all the three samples should have the same value otherwise the noise flag (NF) is set. For example: if the 8th, 9th and 10th samples are 0, 1 and 1 respectively, then the bit value will be "1", but the Noise Flag bit is be set because the three samples values are not the same.

Consequently, the bit length must be long enough so that the 8th, 9th and 10th samples have the desired bit value. This means the clock frequency should not vary more than 6/16 (37.5%) within one bit. The sampling clock is resynchronized at each start bit, so that when receiving 10 bits (one start bit, 1 data byte, 1 stop bit), the clock deviation must not exceed 3.75%.

**Note:** The internal sampling clock of the microcontroller samples the pin value on every falling edge. Therefore, the internal sampling clock and the time the application expects the sampling to take place may be out of sync. For example: If the baud rate is 15.625 kbaud (bit length is 64µs), then the 8th, 9th and 10th samples will be at 28µs, 32µs & 36µs respectively (the first sample starting ideally at 0µs). But if the falling edge of the internal clock occurs just before the pin value changes, the samples would then be out of sync by ~4us. This means the entire bit length must be at least 40µs (36µs for the 10th sample + 4µs for synchronization with the internal sampling clock).

## SERIAL COMMUNICATIONS INTERFACE (Cont'd) CONTROL REGISTER 2 (SCICR2)

#### Read/Write

Reset Value: 0000 0000 (00h)

| 7   |      |     |      |    |    |     | 0   |

|-----|------|-----|------|----|----|-----|-----|

| TIE | TCIE | RIE | ILIE | TE | RE | RWU | SBK |

Bit 7 = **TIE** *Transmitter interrupt enable.* This bit is set and cleared by software. 0: Interrupt is inhibited

1: An SCI interrupt is generated whenever TDRE=1 in the SCISR register

Bit 6 = TCIE *Transmission complete interrupt enable*

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An SCI interrupt is generated whenever TC=1 in the SCISR register

#### Bit 5 = **RIE** Receiver interrupt enable.

This bit is set and cleared by software.

- 0: Interrupt is inhibited

- 1: An SCI interrupt is generated whenever OR=1 or RDRF=1 in the SCISR register

#### Bit 4 = **ILIE** *Idle line interrupt enable.*

This bit is set and cleared by software.

0: Interrupt is inhibited

1: An SCI interrupt is generated whenever IDLE=1 in the SCISR register.

#### Bit 3 = **TE** *Transmitter enable.*

This bit enables the transmitter. It is set and cleared by software. 0: Transmitter is disabled

1: Transmitter is enabled

#### Notes:

- During transmission, a "0" pulse on the TE bit ("0" followed by "1") sends a preamble (idle line) after the current word.

- When TE is set there is a 1 bit-time delay before the transmission starts.

**Caution:** The TDO pin is free for general purpose I/O only when the TE and RE bits are both cleared (or if TE is never set).

#### Bit 2 = **RE** Receiver enable.

This bit enables the receiver. It is set and cleared by software.

- 0: Receiver is disabled

- 1: Receiver is enabled and begins searching for a start bit

#### Bit 1 = **RWU** *Receiver wake-up.*

This bit determines if the SCI is in mute mode or not. It is set and cleared by software and can be cleared by hardware when a wake-up sequence is recognized.

- 0: Receiver in Active mode

- 1: Receiver in Mute mode

**Note:** Before selecting Mute mode (setting the RWU bit), the SCI must receive some data first, otherwise it cannot function in Mute mode with wakeup by idle line detection.

#### Bit 0 = SBK Send break.

This bit set is used to send break characters. It is set and cleared by software.

0: No break character is transmitted

1: Break characters are transmitted

**Note:** If the SBK bit is set to "1" and then to "0", the transmitter will send a BREAK word at the end of the current word.

#### **12.2 ABSOLUTE MAXIMUM RATINGS**

Stresses above those listed as "absolute maximum ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device under these condi-

#### 12.2.1 Voltage Characteristics

tions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| Symbol                                                                    | Ratings                                           | Maximum value                  | Unit    |  |

|---------------------------------------------------------------------------|---------------------------------------------------|--------------------------------|---------|--|

| V <sub>DD</sub> - V <sub>SS</sub>                                         | Supply voltage                                    | 6.5                            |         |  |

| V <sub>PP</sub> - V <sub>SS</sub>                                         | Programming Voltage                               | 13                             | v       |  |

| V <sub>IN</sub> <sup>1) &amp; 2)</sup>                                    | Input Voltage on true open drain pin              | V <sub>SS</sub> -0.3 to 6.5    | v       |  |

| VIN /                                                                     | Input voltage on any other pin                    | $V_{SS}$ -0.3 to $V_{DD}$ +0.3 |         |  |

| $ \Delta V_{DDx} $ and $ \Delta V_{SSx} $                                 | Variations between different digital power pins   | 50                             | mV      |  |

| IV <sub>SSA</sub> - V <sub>SSx</sub> I                                    | Variations between digital and analog ground pins | 50                             | IIIV    |  |

| V <sub>ESD(HBM)</sub> Electro-static discharge voltage (Human Body Model) |                                                   | see Section 12.7.3 on p        | 200 127 |  |

| V <sub>ESD(MM)</sub>                                                      | Electro-static discharge voltage (Machine Model)  | 366 366001 12.7.3 01 p         | aye 127 |  |

#### **12.2.2 Current Characteristics**

| Symbol                                       | Ratings                                                               | Ratings                                                 |      |    |  |

|----------------------------------------------|-----------------------------------------------------------------------|---------------------------------------------------------|------|----|--|

| I <sub>VDD</sub>                             | Total current into V <sub>DD</sub> power lines (source) <sup>3)</sup> |                                                         |      | mA |  |

| I <sub>VSS</sub>                             | Total current out of $V_{SS}$ ground lines (sink) <sup>3)</sup>       |                                                         |      | mA |  |

|                                              | Output current sunk by any standard I/                                | Output current sunk by any standard I/O and control pin |      |    |  |

| I <sub>IO</sub>                              | Output current sunk by any high sink I/                               | 50                                                      |      |    |  |

|                                              | Output current source by any I/Os and                                 | - 25                                                    |      |    |  |

|                                              | Injected current on V <sub>PP</sub> pin                               |                                                         | ± 5  |    |  |

|                                              | Injected current on RESET pin                                         |                                                         | ± 5  | mA |  |

| I <sub>INJ(PIN)</sub> <sup>2) &amp; 4)</sup> | Injected current on OSC1 and OSC2 p                                   | ins                                                     | ± 5  |    |  |

|                                              | Injected current on Flash device pin PE                               | +5                                                      |      |    |  |

|                                              | Injected current on any other pin 5) & 6)                             | ± 5                                                     |      |    |  |

| ΣI <sub>INJ(PIN)</sub> <sup>2)</sup>         | Total injected current (sum of all I/O ar                             | id control pins) <sup>5)</sup>                          | ± 25 |    |  |

#### Notes:

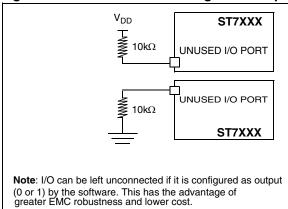

1. Directly connecting the RESET and I/O pins to V<sub>DD</sub> or V<sub>SS</sub> could damage the device if an unintentional internal reset is generated or an unexpected change of the I/O configuration occurs (for example, due to a corrupted program counter). To guarantee safe operation, this connection has to be done through a pull-up or pull-down resistor (typical: 4.7k $\Omega$  for RESET, 10k $\Omega$  for I/Os). For the same reason, unused I/O pins must not be directly tied to V<sub>DD</sub> or V<sub>SS</sub>.

2.  $I_{INJ(PIN)}$  must never be exceeded. This is implicitly insured if  $V_{IN}$  maximum is respected. If  $V_{IN}$  maximum cannot be respected, the injection current must be limited externally to the  $I_{INJ(PIN)}$  value. A positive injection is induced by  $V_{IN} > V_{DD}$  while a negative injection is induced by  $V_{IN} < V_{SS}$ . For true open-drain pads, there is no positive injection current, and the corresponding  $V_{IN}$  maximum must always be respected

3. All power ( $V_{DD}$ ) and ground ( $V_{SS}$ ) lines must always be connected to the external supply.

4. Negative injection disturbs the analog performance of the device. See note in "ADC Accuracy" on page 140.

For best reliability, it is recommended to avoid negative injection of more than 1.6mA.

5. When several inputs are submitted to a current injection, the maximum  $\Sigma I_{INJ(PIN)}$  is the absolute sum of the positive and negative injected currents (instantaneous values). These results are based on characterisation with  $\Sigma I_{INJ(PIN)}$  maximum current injection on four I/O port pins of the device.

6. True open drain I/O port pins do not accept positive injection.

## EMC CHARACTERISTICS (Cont'd)

# 12.7.3 Absolute Maximum Ratings (Electrical Sensitivity)

Based on three different tests (ESD, LU and DLU) using specific measurement methods, the product is stressed in order to determine its performance in terms of electrical sensitivity. For more details, refer to the application note AN1181.

## 12.7.3.1 Electro-Static Discharge (ESD)

Electro-Static Discharges (a positive then a negative pulse separated by 1 second) are applied to the pins of each sample according to each pin combination. The sample size depends on the number of supply pins in the device (3 parts\*(n+1) supply pin). Two models can be simulated: Human Body Model and Machine Model. This test conforms to the JESD22-A114A/A115A standard.

#### Absolute Maximum Ratings

| Symbol                | Ratings                                                    | Conditions            | Maximum value 1) | Unit |

|-----------------------|------------------------------------------------------------|-----------------------|------------------|------|

| V <sub>ESD(HBM)</sub> | Electro-static discharge voltage<br>(Human Body Model)     | T <sub>A</sub> =+25°C | 2000             |      |

| V <sub>ESD(MM)</sub>  | Electro-static discharge voltage (Machine Model)           | T <sub>A</sub> =+25°C | 200              | V    |

| V <sub>ESD(CD)</sub>  | Electro-static discharge voltage<br>(Charged Device Model) | T <sub>A</sub> =+25°C | 250              |      |

#### Notes:

1. Data based on characterization results, not tested in production.

- 12.7.3.2 Static and Dynamic Latch-Up

- LU: 3 complementary static tests are required on 10 parts to assess the latch-up performance. A supply overvoltage (applied to each power supply pin) and a current injection (applied to each input, output and configurable I/O pin) are performed on each sample. This test conforms to the EIA/JESD 78 IC latch-up standard. For more details, refer to the application note AN1181.

- DLU: Electro-Static Discharges (one positive then one negative test) are applied to each pin of 3 samples when the micro is running to assess the latch-up performance in dynamic mode. Power supplies are set to the typical values, the oscillator is connected as near as possible to the pins of the micro and the component is put in reset mode. This test conforms to the IEC1000-4-2 and SAEJ1752/3 standards. For more details, refer to the application note AN1181.

#### **Electrical Sensitivities**

| Symbol | Parameter              | Conditions                                                             | Class <sup>1)</sup> |

|--------|------------------------|------------------------------------------------------------------------|---------------------|

|        |                        | $T_{A}$ =+25°C<br>$T_{A}$ =+85°C<br>$T_{A}$ =+105°C<br>$T_{A}$ =+125°C | А                   |

| LU     |                        | T <sub>A</sub> =+85°C                                                  | A                   |

| LU     | Static latch-up class  | T <sub>A</sub> =+105°C                                                 | A                   |

|        |                        | T <sub>A</sub> =+125°C                                                 | А                   |

| DLU    | Dynamic latch-up class | $V_{DD}\!\!=\!\!5.5V,f_{OSC}\!\!=\!\!4MHz,T_{A}\!\!=\!\!+25^{\circ}C$  | A                   |

#### Notes:

1. Class description: A Class is an STMicroelectronics internal specification. All its limits are higher than the JEDEC specifications, that means when a device belongs to Class A it exceeds the JEDEC standard. B Class strictly covers all the JEDEC criteria (international standard).

## **12.8 I/O PORT PIN CHARACTERISTICS**

## **12.8.1 General Characteristics**

Subject to general operating conditions for V<sub>DD</sub>, f<sub>OSC</sub>, and T<sub>A</sub> unless otherwise specified.

| Symbol                                  | Parameter                                                        | Conditions                                           | Min                             | Тур | Max                 | Unit             |

|-----------------------------------------|------------------------------------------------------------------|------------------------------------------------------|---------------------------------|-----|---------------------|------------------|

| V <sub>IL</sub>                         | Input low level voltage (standard voltage devices) <sup>1)</sup> |                                                      |                                 |     | 0.3xV <sub>DD</sub> | V                |

| V <sub>IH</sub>                         | Input high level voltage 1)                                      |                                                      | $0.7 \mathrm{xV}_{\mathrm{DD}}$ |     |                     | v                |

| V <sub>hys</sub>                        | Schmitt trigger voltage hysteresis <sup>2)</sup>                 |                                                      |                                 | 0.7 |                     | v                |

| ı 3)                                    | Injected Current on Flash device pin PB0                         |                                                      | 0                               |     | +4                  |                  |

| $\left _{\mathrm{INJ(PIN)}}^{3}\right)$ | Injected Current on other I/O pins                               | V <sub>DD</sub> =5V                                  |                                 |     | ±4                  | mA               |

| $\Sigma I_{\rm INJ(PIN)}^{3)}$          | Total injected current (sum of all I/O and control pins)         |                                                      |                                 |     | ±25                 |                  |

| l <sub>ikg</sub>                        | Input leakage current                                            | $V_{SS} \le V_{IN} \le V_{DD}$                       |                                 |     | ±1                  |                  |

| ۱ <sub>S</sub>                          | Static current consumption induced by each floating input pin    | Floating input mode <sup>4)</sup>                    |                                 | 200 |                     | μA               |

| R <sub>PU</sub>                         | Weak pull-up equivalent resistor <sup>5)</sup>                   | V <sub>IN</sub> =V <sub>SS</sub> V <sub>DD</sub> =5V | 50                              | 120 | 250                 | kΩ               |

| C <sub>IO</sub>                         | I/O pin capacitance                                              |                                                      |                                 | 5   |                     | pF               |

| t <sub>f(IO)out</sub>                   | Output high to low level fall time <sup>1)</sup>                 | C <sub>L</sub> =50pF                                 |                                 | 25  |                     |                  |

| t <sub>r(IO)out</sub>                   | Output low to high level rise time <sup>1)</sup>                 | Between 10% and 90%                                  |                                 | 25  |                     | ns               |

| t <sub>w(IT)in</sub>                    | External interrupt pulse time <sup>6)</sup>                      |                                                      | 1                               |     |                     | t <sub>CPU</sub> |

#### Notes:

1. Data based on characterization results, not tested in production.

2. Hysteresis voltage between Schmitt trigger switching levels. Based on characterization results, not tested.

3. When the current limitation is not possible, the V<sub>IN</sub> maximum must be respected, otherwise refer to  $I_{INJ(PIN)}$  specification. A positive injection is induced by  $V_{IN}$ >V<sub>DD</sub> while a negative injection is induced by  $V_{IN}$ <V<sub>SS</sub>. Refer to Section 12.2.2 on page 114 for more details.

4. Configuration not recommended, all unused pins must be kept at a fixed voltage: using the output mode of the I/O for example and leaving the I/O unconnected on the board or an external pull-up or pull-down resistor (see Figure 66). Static peak current value taken at a fixed  $V_{IN}$  value, based on design simulation and technology characteristics, not tested in production. This value depends on  $V_{DD}$  and temperature values.

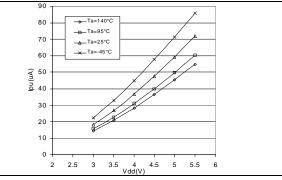

5. The R<sub>PU</sub> pull-up equivalent resistor is based on a resistive transistor (corresponding IPU current characteristics described in Figure 67).

6. To generate an external interrupt, a minimum pulse width has to be applied on an I/O port pin configured as an external interrupt source.

## Figure 66. Unused I/O Pins configured as input

## Figure 67. Typical I<sub>PU</sub> vs. V<sub>DD</sub> with V<sub>IN</sub>=V<sub>SS</sub>

## I/O PORT PIN CHARACTERISTICS (Cont'd)

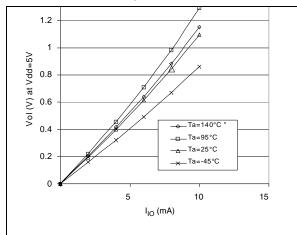

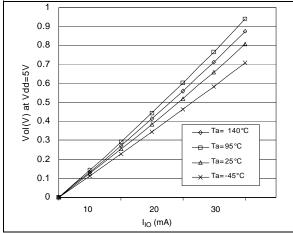

## 12.8.2 Output Driving Current

Subject to general operating conditions for V<sub>DD</sub>, f<sub>CPU</sub>, and T<sub>A</sub> unless otherwise specified.

| Symbol                        | Parameter                                                                                                                                                                                                                                          |  | Conditions                                                           | Min                  | Max        | Unit |

|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|----------------------------------------------------------------------|----------------------|------------|------|

|                               | OL <sup>1)</sup> Output low level voltage for a standard I/O pin<br>when 8 pins are sunk at same time<br>(see Figure 68)<br>Output low level voltage for a high sink I/O pin<br>when 4 pins are sunk at same time<br>(see Figure 69 and Figure 71) |  | I <sub>IO</sub> =+5mA                                                |                      | 1.2        |      |

| 1)                            |                                                                                                                                                                                                                                                    |  | I <sub>IO</sub> =+2mA                                                |                      | 0.5        |      |

| V <sub>OL</sub> ')            |                                                                                                                                                                                                                                                    |  | I <sub>IO</sub> =+20mA, T <sub>A</sub> ≤85°C<br>T <sub>A</sub> >85°C |                      | 1.3<br>1.5 | v    |

|                               |                                                                                                                                                                                                                                                    |  | I <sub>IO</sub> =+8mA                                                |                      | 0.6        |      |

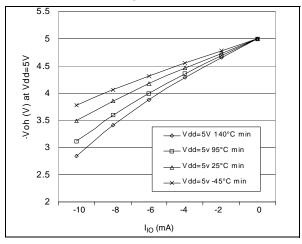

| V <sub>OH</sub> <sup>2)</sup> | Output high level voltage for an I/O pin when 4 pins are sourced at same time                                                                                                                                                                      |  | I <sub>IO</sub> =-5mA, T <sub>A</sub> ≤85°C<br>T <sub>A</sub> >85°C  |                      |            |      |

|                               | (see Figure 70 and Figure 73)                                                                                                                                                                                                                      |  | I <sub>IO</sub> =-2mA                                                | V <sub>DD</sub> -0.7 |            | 1    |

## Figure 68. Typical V<sub>OL</sub> at V<sub>DD</sub>=5V (std. ports)

## Figure 69. Typ. V<sub>OL</sub> at V<sub>DD</sub>=5V (high-sink ports)

#### Notes:

<u>ل</u>حک

1. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in Section 12.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

2. The I<sub>IO</sub> current sourced must always respect the absolute maximum rating specified in Section 12.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VDD</sub>. True open drain I/O pins do not have V<sub>OH</sub>.

## Figure 70. Typical $V_{OH}$ at $V_{DD}$ =5V

## **12.9 CONTROL PIN CHARACTERISTICS**

## 12.9.1 Asynchronous RESET Pin

Subject to general operating conditions for  $V_{DD}$ ,  $f_{CPU}$ , and  $T_A$  unless otherwise specified.

| Symbol                  | Parameter                              | Cor                 | Conditions            |                                  | Тур | Max                              | Unit |

|-------------------------|----------------------------------------|---------------------|-----------------------|----------------------------------|-----|----------------------------------|------|

| V <sub>hys</sub>        | Schmitt trigger voltage hysteresis 2)  |                     |                       |                                  | 2.5 |                                  |      |

| V <sub>IL</sub>         | Input low level voltage 1)             |                     |                       |                                  |     | $0.16 \mathrm{xV}_{\mathrm{DD}}$ | V    |

| V <sub>IH</sub>         | Input high level voltage 1)            |                     |                       | $0.85 \mathrm{xV}_{\mathrm{DD}}$ |     |                                  | v    |

| V <sub>OL</sub>         | Output low level voltage 3)            | V <sub>DD</sub> =5V | I <sub>IO</sub> =+2mA |                                  | 0.2 | 0.5                              | V    |

| I <sub>IO</sub>         | Driving current on RESET pin           |                     |                       |                                  | 2   |                                  | mA   |

| R <sub>ON</sub>         | Weak pull-up equivalent resistor       | V <sub>DD</sub> =5V |                       | 20                               | 30  | 120                              | kΩ   |

| t <sub>w(RSTL)out</sub> | Generated reset pulse duration         | Internal re         | eset sources          | 20                               | 30  | 42 <sup>6)</sup>                 | μS   |

| t <sub>h(RSTL)in</sub>  | External reset pulse hold time 4)      |                     |                       | 2.5                              |     |                                  | μS   |

| t <sub>g(RSTL)in</sub>  | Filtered glitch duration <sup>5)</sup> |                     |                       |                                  | 200 |                                  | ns   |

#### Notes:

1. Data based on characterization results, not tested in production.

2. Hysteresis voltage between Schmitt trigger switching levels.

3. The I<sub>IO</sub> current sunk must always respect the absolute maximum rating specified in Section 12.2.2 and the sum of I<sub>IO</sub> (I/O ports and control pins) must not exceed I<sub>VSS</sub>.

4. To guarantee the reset of the device, a minimum pulse has to be applied to the  $\overrightarrow{\text{RESET}}$  pin. All short pulses applied on the RESET pin with a duration below  $t_{h(\text{RSTL})in}$  can be ignored.

5. The reset network (the resistor and two capacitors) protects the device against parasitic resets, especially in noisy environments.

6. Data guaranteed by design, not tested in production.

## **14.6 ST7 APPLICATION NOTES**

## Table 30. ST7 Application Notes

| IDENTIFICATION | DESCRIPTION                                                                      |

|----------------|----------------------------------------------------------------------------------|

| APPLICATION EX | AMPLES                                                                           |

| AN1658         | SERIAL NUMBERING IMPLEMENTATION                                                  |

| AN1720         | MANAGING THE READ-OUT PROTECTION IN FLASH MICROCONTROLLERS                       |

| AN1755         | A HIGH RESOLUTION/PRECISION THERMOMETER USING ST7 AND NE555                      |

| EXAMPLE DRIVER | RS                                                                               |

| AN 969         | SCI COMMUNICATION BETWEEN ST7 AND PC                                             |

| AN 970         | SPI COMMUNICATION BETWEEN ST7 AND EEPROM                                         |

| AN 972         | ST7 SOFTWARE SPI MASTER COMMUNICATION                                            |

| AN 973         | SCI SOFTWARE COMMUNICATION WITH A PC USING ST72251 16-BIT TIMER                  |

| AN 974         | REAL TIME CLOCK WITH ST7 TIMER OUTPUT COMPARE                                    |

| AN 976         | DRIVING A BUZZER THROUGH ST7 TIMER PWM FUNCTION                                  |

| AN 979         | DRIVING AN ANALOG KEYBOARD WITH THE ST7 ADC                                      |

| AN 980         | ST7 KEYPAD DECODING TECHNIQUES, IMPLEMENTING WAKE-UP ON KEYSTROKE                |

| AN1041         | USING ST7 PWM SIGNAL TO GENERATE ANALOG OUTPUT (SINUSOÏD)                        |

| AN1044         | MULTIPLE INTERRUPT SOURCES MANAGEMENT FOR ST7 MCUS                               |

| AN1046         | UART EMULATION SOFTWARE                                                          |

| AN1047         | MANAGING RECEPTION ERRORS WITH THE ST7 SCI PERIPHERALS                           |

| AN1048         | ST7 SOFTWARE LCD DRIVER                                                          |

| AN1078         | PWM DUTY CYCLE SWITCH IMPLEMENTING TRUE 0% & 100% DUTY CYCLE                     |

| AN1445         | EMULATED 16 BIT SLAVE SPI                                                        |

| AN1504         | STARTING A PWM SIGNAL DIRECTLY AT HIGH LEVEL USING THE ST7 16-BIT TIMER          |

| GENERAL PURPC  | DSE                                                                              |

| AN1476         | LOW COST POWER SUPPLY FOR HOME APPLIANCES                                        |

| AN1709         | EMC DESIGN FOR ST MICROCONTROLLERS                                               |

| AN1752         | ST72324 QUICK REFERENCE NOTE                                                     |

| PRODUCT EVALU  |                                                                                  |

| AN 910         | PERFORMANCE BENCHMARKING                                                         |

| AN 990         | ST7 BENEFITS VERSUS INDUSTRY STANDARD                                            |

| AN1150         | BENCHMARK ST72 VS PC16                                                           |

| AN1151         | PERFORMANCE COMPARISON BETWEEN ST72254 & PC16F876                                |

| AN1278         | LIN (LOCAL INTERCONNECT NETWORK) SOLUTIONS                                       |

| PRODUCT MIGRA  |                                                                                  |

| AN1131         | MIGRATING APPLICATIONS FROM ST72511/311/214/124 TO ST72521/321/324               |

| PRODUCT OPTIM  | IZATION                                                                          |

|                | USING ST7 WITH CERAMIC RESONATOR                                                 |

| AN1014         | HOW TO MINIMIZE THE ST7 POWER CONSUMPTION                                        |

| AN1015         | SOFTWARE TECHNIQUES FOR IMPROVING MICROCONTROLLER EMC PERFORMANCE                |

| AN1070         | ST7 CHECKSUM SELF-CHECKING CAPABILITY                                            |

| AN1181         | ELECTROSTATIC DISCHARGE SENSITIVE MEASUREMENT                                    |

| AN1502         | EMULATED DATA EEPROM WITH ST7 HDFLASH MEMORY                                     |

| AN1530         | ACCURATE TIMEBASE FOR LOW-COST ST7 APPLICATIONS WITH INTERNAL RC OSCILLA-<br>TOR |

| AN1636         | UNDERSTANDING AND MINIMIZING ADC CONVERSION ERRORS                               |

| PROGRAMMING A  | AND TOOLS                                                                        |

| AN 978         | ST7 VISUAL DEVELOP SOFTWARE KEY DEBUGGING FEATURES                               |