#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Detuils                         |                                                                    |

|---------------------------------|--------------------------------------------------------------------|

| Product Status                  | Obsolete                                                           |

| Core Processor                  | ARM926EJ-S                                                         |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                     |

| Speed                           | -                                                                  |

| Co-Processors/DSP               | · .                                                                |

| RAM Controllers                 | DDR, SDRAM                                                         |

| Graphics Acceleration           | No                                                                 |

| Display & Interface Controllers | LCD                                                                |

| Ethernet                        | ·                                                                  |

| SATA                            | ·                                                                  |

| USB                             | USB 2.0 OTG (1)                                                    |

| Voltage - I/O                   | 1.8V, 2.5V, 3.3V                                                   |

| Operating Temperature           | -40°C ~ 105°C (TA)                                                 |

| Security Features               | Cryptography                                                       |

| Package / Case                  | 236-LFBGA                                                          |

| Supplier Device Package         | 236-MAPBGA (9x9)                                                   |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/scp2201vmu |

|                                 |                                                                    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Introduction

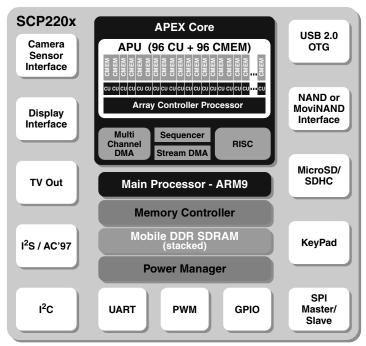

# 1.1 The SCP220x function blocks

Figure 1. SCP220x Image Cognition Processors

# 1.2 SCP220x Features

# 1.2.1 SCP220x General Features

CogniVue APEX Processor – programmable 34Billion-Operations per second Vision Processor with patented massively parallel Array Processor Unit (APU) with 96 Computing Units (CUs) with dedicated memory, discreet RISC processor, H/W acceleration blocks, wide-bandwidth stream DMAs and internal 64-bit data buses

ARM926EJ-S™ RISC processor with 16 KB of instruction cache (I-cache) and 16 KB of data cache (D-cache)

Multiple power domains for different peripheral IOs

## 1.2.2 Interconnect and Communication

### 1.2.2.1 Video Processing

Fully-programmable Array Processor (APEX) for running video/image processing algorithms

Video codecs support diverse resolutions at 30 fps with 4 Mbps maximum bitrate

Supported video decoding standards:

MPEG-4 Simple Profile and Advanced Simple Profile supports 720x480 at 30 fps

For other standards consult factory

Supported video encoding standard is MPEG-4 Simple Profile, 720x480 at 30 fps

| b001   | Code is resident in a serial NAND flash connected to the SPI port. The serial Flash Memory is an industry standard memory that supports the "read data bytes" command (0x03).                                                                                                                                                                                                                                                                                                             |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [b010] | [RESERVED]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| b100   | Code is resident in NAND flash. The NAND flash block read sequence is:<br>After reset is de-asserted, the bootloader will issue a "reset" command ("ff") followed by a 25 µsec<br>delay.<br>The boot loader then issues the page read command ("00") and 5 bytes of address (all "0"). This is<br>followed by a read confirm command ("30").<br>Before proceeding further, a 50 µsec delay occurs.<br>A 2 Kbyte page is then read. If ECC is enabled four 512 byte page reads are issued. |

| Table 5. Configuring Boot Load Using dip_data[5:3] Pins | Table 5. Configuring | Boot Load Using dip | data[5:3] Pins |

|---------------------------------------------------------|----------------------|---------------------|----------------|

|---------------------------------------------------------|----------------------|---------------------|----------------|

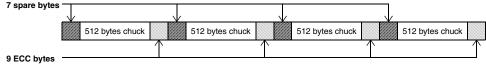

If booting from NAND Flash, there is an optional ECC checking mode that may be enabled via a software register. If ECC checking is enabled, the boot\_loader checks for errors after a block is read from the device. Upon error detection, the boot loader keeps the ARM926EJ-S processor in reset.

For NAND Flash, the data must be organized in the 2K Flash sector as follows.

4x 512 bytes chucks = 2048 bytes image

#### Figure 14. NAND Flash Data Organization

## 3.7 Low Power Configurations

The SCP220x chips offer three power consumption reduction features described below: voltage islands, clock gating and processor standby. They can be implemented independently for maximum control.

### 3.7.1 Voltage Islands

The SCP220x provides two voltage islands: Low Power Audio/Video domain and the IC Core domain (see Figure 2., SCP220x Internal Architecture).

The Low Power Audio/Video domain is powered through the VDD\_LP pin. This domain allows for processing at reduced power consumption. The ARM926EJ-S processor runs along with some of the blocks offering some processing, audio and display capability (digital out only, see Figure 30., Display Sub-System (DSS) Internal Architecture). Apex is not running and there is no input of images.

The IC Core domain is powered through the VDD\_CORE pin. This domain contains the high performance blocks such as the APEX, SIF and USB.

Low power consumption mode is achieved by removing power to the IC Core (VDD\_CORE) by an external device (i.e. power MOSFET) optionally controlled via a SCP220x GPIO pin. CogniVue Reference Design Kit (RDK) has this low power option implemented. NOTE: it is recommended that all the other power lines be connected at all times even if the corresponding blocks are not active.

### 3.7.2 Clock gating

It is possible to idle some blocks by gating their clocks. Clock gating is achieved through registers, see 5.4, Reset and Clock Gating. Note that this functionality is provided by the SDK, direct register setting is recommended only for custom bootloader code as SDK is not available at this stage.

### 3.7.3 Processor Standby

Another way to save power is to place the ARM926EJ-S processor in standby when no processing is required before an event.

# 4 Interconnect and Communication

## 4.1 NAND Flash Interface

The SCP2201 and SCP2207 products have a NAND flash interface for connectivity to an external NAND flash device. The following list details specific NAND flash features:

- 8-bit datapath

- Software configurable external control signal timing

- Incoming and outgoing datapath implemented using FIFOs

- Software controlled command and page address

- Read/Write datapath that bypasses the FIFO and allows direct access

- Configurable page size

- NAND flash read and write algorithms are software driven

- Optional hardware ECC support; a simple ECC (1bit correct, 2 bit detect) as well as a Reed Solomon ECC algorithm (4 bit correct)

- Supports up to 4 external chip selects

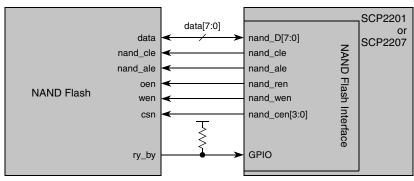

### 4.1.1 NAND Flash connection

The following figure shows the connection between the SCP2201 or SCP2207 and a typical external NAND flash device. It should be noted that the "ry\_by. signal is not a dedicated pin on the SCP2201 or SCP2207. Instead this connection, required for command status, is made to a GPIO. Alternatively, a software managed polling routing may be used to determine when various commands are completed.

Figure 15. NAND Flash Connectivity

The following table describes the NAND Flash Interface pinout for the SCP220x

| Signal      | Alternate Function                  | Pin Direction | Pin Description                            |

|-------------|-------------------------------------|---------------|--------------------------------------------|

| nand_D[7:0] | gpio[81:74] or<br>mmcplus_data[7:0] | Bi-dir.       | NAND data bus or alternate function        |

| nand_cle    | gpio[11]                            | Bi-dir.       | Command latch enable or alternate function |

| nand_ale    | gpio[10]                            | Bi-dir.       | Address latch enable or alternate function |

| nand_cen[0] | gpio[12] or mmcplus_clk             | Bi-dir.       | Chip select or alternate function          |

| nand_cen[1] | gpio[70] or mmcplus_cmd             | Bi-dir.       | Chip select or alternate function          |

| nand_cen[2] | gpio[71] or spi_Rxd1                | Bi-dir.       | Chip select or alternate function          |

| nand_cen[3] | gpio[72] or spi_Rxd2                | Bi-dir.       | Chip select or alternate function          |

| nand_ren    | gpio[14]                            | Bi-dir.       | Read enable or alternate function          |

| nand_wen    | gpio[13]                            | Bi-dir.       | Write enable or alternate function         |

Table 6. NAND Flash Interface

### 4.1.2 NAND Flash Hardware Description

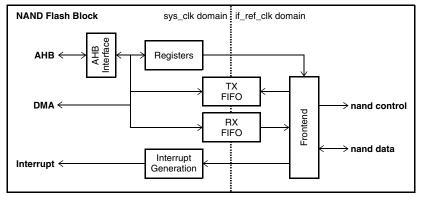

The hardware implementation for the NAND Flash block is as shown in the following diagram.

Figure 16. NAND Flash Hardware Architecture

The NAND Flash front-end contains a state machine that drives the external interface based on the configuration settings from the software interface.

The front-end block issues commands, address and data as directed by the particular software configuration. The transmit and receive fifos provide buffer space such that the internal bus-bandwidth required to move data is minimized because AMBA AHB bursts can efficiently move data minimizing overall bus bandwidth usage.

The following diagrams illustrate what the external waveforms look like and also illustrate any software configurable parameters that control the external signals.

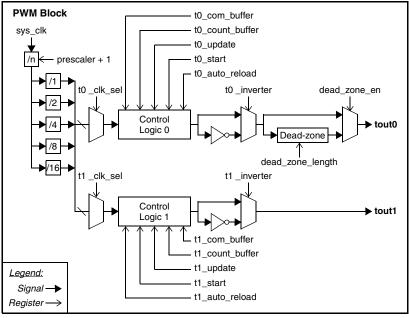

Figure 55. PWM Hardware Architecture

The Tout0 frequency is determined by the following formula:

For Tout1, just replace the t0 by t1.

PWM Control registers are described at 5.14, PWM Registers.

### 4.10.2 PWM Programming Notes

### 4.10.2.1 Example

The following section provides some details on appropriate programming of the PWM using an example. The following diagram illustrates a timeline for a particular PWM configuration.

|        |                | ios anu Alternate i t |       |   |         |

|--------|----------------|-----------------------|-------|---|---------|

| -      | spi1_ssn_p     | mp2ts1_sync           | JVDD  | С | PU/PU   |

| -      | spi1_txd_p     | mp2ts1_valid          | JVDD  | А | PD/none |

| -      | sdram_clkn_p   | sdram_clk_fb          | RVDD  | В | -       |

| gpio00 | Reserved_1     |                       | MVDD  | А | PD/none |

| gpio01 | sif_clkout_p   |                       | SVDD  | В | PD/none |

| gpio02 | Reserved_2     |                       | MVDD  | А | PD/PD   |

| gpio03 | dip_data_p[17] | scl_sec               | LVDD  | В | PD/none |

| gpio04 | dip_data_p[16] | sda_sec               | LVDD  | В | PD/none |

| gpio05 | dip_pclk_p     |                       | LVDD  | В | PD/none |

| gpio06 | Reserved_3     | pwi_clk               | MVDD  | А | PD/none |

| gpio07 | Reserved_4     | pwi_data              | MVDD  | А | PD/none |

| gpio08 | Reserved_5     |                       | MVDD  | А | PD/none |

| gpio09 | Reserved_6     |                       | MVDD  | А | PD/none |

| gpio10 | nand_ale_p     |                       | NVDD  | А | PD/none |

| gpio11 | nand_cle_p     |                       | NVDD  | А | PD/none |

| gpio12 | nand_cen_p[0]  | mmcplus_clk           | NVDD  | С | PU/PU   |

| gpio13 | nand_wen_p     |                       | NVDD  | А | PD/none |

| gpio14 | nand_ren_p     |                       | NVDD  | А | PD/none |

| gpio15 | dip_oen_p      | dip_blank             | LVDD  | В | PD/none |

| gpio16 | audio_clkr_p   |                       | AUVDD | А | PD/none |

| gpio17 | audio_dr_p     |                       | AUVDD | А | PD/none |

| gpio18 | audio_fsr_p    | pwm2_out              | AUVDD | А | PD/none |

| gpio19 | audio_clkx_p   |                       | AUVDD | А | PD/none |

| gpio20 | audio_dx_p     |                       | AUVDD | А | PD/none |

| gpio21 | audio_fsx_p    |                       | AUVDD | А | PD/none |

| gpio22 | uart_txd_p     |                       | JVDD  | А | PD/none |

| gpio23 | uart_rxd_p     |                       | JVDD  | А | PD/none |

| gpio24 | dip_csn2_p     |                       | LVDD  | D | PU/PU   |

| gpio25 | dip_csn3_p     |                       | LVDD  | D | PU/PU   |

| gpio26 | spi_txd_p      |                       | JVDD  | А | PD/none |

| gpio27 | spi_rxd_p      |                       | JVDD  | А | PD/none |

| gpio28 | spi_ssn_p      |                       | JVDD  | С | PU/PU   |

Table 23. GPIOs and Alternate Functions Shared with External Pins

\_\_\_\_\_

#### Registers

| Table 40. Alternate Function Enable Register |

|----------------------------------------------|

|----------------------------------------------|

|                  | 1  |                                                                                                                                                                                   |   |

|------------------|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| pwi interface    | 21 | 0 = main function selected (bb_audio_fsx,bb_audio_clkx)<br>1 = alternate function selected (pwi_clk,pwi_data)<br>reserved_3 = pwi_clk<br>reserved_4 = pwi_data                    | 0 |

| spi_device3      | 20 | 0 = main function selected (nand)<br>1 = alternate function selected (spi_device3)<br>reserved_15 = spi_ssn3<br>sc_card_voltage = spi_rxd3                                        | 0 |

| spi_device2      | 19 | 0 = main function selected (nand)<br>1 = alternate function selected (spi_device2)<br>uart_rts = spi_ssn2<br>nand_cen3 = spi_rxd2                                                 | 0 |

| spi_device1      | 18 | 0 = main function selected (nand)<br>1 = alternate function selected (spi_device1)<br>uart_cts = spi_ssn1<br>nand_cen2 = spi_rxd1                                                 | 0 |

| nand_or_mmc_plus | 17 | 0 = main function selected (nand)<br>1 = alternate function selected (mmc_plus)<br>mmc_plus _data[7:0] = nand_data[7:0]<br>mmc_plus _clk = nand_cen0<br>mmc_plus _cmd = nand_cen1 | 0 |

| uart_txd         | 16 | 0 = main function selected (uart_txd)<br>1 = alternate function selected (dip_ref_clk)                                                                                            | 0 |

| spi_sck          | 15 | 0 = main function selected (mmc_data3)<br>1 = alternate function selected (ac_clk)                                                                                                | 0 |

| spi_ssn          | 14 | 0 = main function selected (mmc_data2)<br>1 = alternate function selected (sys_clk)                                                                                               | 0 |

| spi_rxd          | 13 | 0 = main function selected (mmc_data1)<br>1 = alternate function selected (mem_ref_clk)                                                                                           | 0 |

| spi_txd          | 12 | 0 = main function selected (mmc_data0)<br>1 = alternate function selected (if_ref_clk)                                                                                            | 0 |

| reserved_14      | 11 | 0 = main function selected (reserved_14)<br>1 = alternate function selected (keyscan3_out)                                                                                        | 0 |

| reserved_13      | 10 | 0 = main function selected (reserved_13)<br>1 = alternate function selected (keyscan2_out)                                                                                        | 0 |

| reserved_12      | 9  | 0 = main function selected reserved_12)<br>1 = alternate function selected (keyscan1_out)                                                                                         | 0 |

| reserved_11      | 8  | 0 = main function selected (reserved_11)<br>1 = alternate function selected (keyscan0_out)                                                                                        | 0 |

| reserved_10      | 7  | 0 = main function selected (reserved_10)<br>1 = alternate function selected (keyscan3_in)                                                                                         | 0 |

| reserved_9       | 6  | 0 = main function selected (reserved_9)<br>1 = alternate function selected (keyscan2_in)                                                                                          | 0 |

| reserved_8 | 5 | 0 = main function selected (reserved_8)<br>1 = alternate function selected (keyscan1_in) | 0 |

|------------|---|------------------------------------------------------------------------------------------|---|

| reserved_7 | 4 | 0 = main function selected (reserved_7)<br>1 = alternate function selected (keyscan0_in) | 0 |

| dip_data17 | 3 | 0 = main function selected (dip_data17)<br>1 = alternate function selected (scl_sec)     | 0 |

| dip_data16 | 2 | 0 = main function selected (dip_data16)<br>1 = alternate function selected (sda_sec)     | 0 |

| audio_fsr  | 1 | 0 = main function selected (audio_fsr)<br>1 = alternate function selected (pwm_output2)  | 0 |

| sc_fcb     | 0 | 0 = main function selected (sc_fcb)<br>1 = alternate function selected (pwm_output1)     | 0 |

### Table 40. Alternate Function Enable Register

# 5.3.2 Drive Strength Register

| Drive Streng          | jth 1  |                                   |                                                                                                                                                                                                                                                                                                             |          |  |

|-----------------------|--------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|--|

| Address: 0xd003_0080  |        | Reset = 0                         | Type: RW                                                                                                                                                                                                                                                                                                    |          |  |

| Name                  | Bit    |                                   | Function                                                                                                                                                                                                                                                                                                    |          |  |

| drive_strength[31-0]  | 31-0   | allow<br>follow<br>they<br>0 = lo | A number of the external PADs have configurable drive strength. This register<br>allows software to configure the drive strength as low or as high. The<br>following table maps the drive_strength bits to the corresponding PAD that<br>they control.<br>0 = low drive strength<br>1 = high drive strength |          |  |

| Drive Streng          | jth 2  |                                   |                                                                                                                                                                                                                                                                                                             |          |  |

| Address: 0xd00        | 3_0084 |                                   | Reset = 0                                                                                                                                                                                                                                                                                                   | Type: RW |  |

| Name                  | Bit    |                                   | Function                                                                                                                                                                                                                                                                                                    |          |  |

| drive_strength[63-32] | 31-0   | allow<br>follow<br>they<br>0 = lo | A number of the external PADs have configurable drive strength. This register<br>allows software to configure the drive strength as low or as high. The<br>following table maps the drive_strength bits to the corresponding PAD that<br>they control.<br>0 = low drive strength<br>1 = high drive strength |          |  |

| Drive Streng          | jth 3  |                                   |                                                                                                                                                                                                                                                                                                             |          |  |

| Address: 0xd00        | 3_0088 |                                   | Reset = 0                                                                                                                                                                                                                                                                                                   | Type: RW |  |

| Name                  | Bit    | Function                          |                                                                                                                                                                                                                                                                                                             | Reset    |  |

#### Table 43. PAD Resistor Enable

| pad_resistor_ena<br>[31-0]   | 31-0     | resist<br>resist<br>corre<br>0 = P                                                                                                                                                                                                                                                                        | nber of the external PADs have configurate<br>ors in the PAD. This register allows softwater.<br>or. The following table maps these register<br>sponding PADs that they control.<br>AD resistor disabled<br>AD resistor enabled                                                                         | ire to enable the | 0x0801_003c |  |

|------------------------------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------|--|

| PAD Resistor E               | Enable 2 |                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                         |                   |             |  |

| Address: 0xd0                | 03_0090  |                                                                                                                                                                                                                                                                                                           | Reset = 0x0008_4f02                                                                                                                                                                                                                                                                                     | Туре:             | RW          |  |

| Name                         | Bit      |                                                                                                                                                                                                                                                                                                           | Function                                                                                                                                                                                                                                                                                                |                   | Reset       |  |

| pad_resistor_ena<br>[63-32]  | 31-0     | resist<br>resist<br>corre<br>0 = P                                                                                                                                                                                                                                                                        | A number of the external PADs have configurable pull-up/pull-down<br>esistors in the PAD. This register allows software to enable the<br>esistor. The following table maps these register bits to the<br>corresponding PADs that they control.<br>0 = PAD resistor disabled<br>= PAD resistor enabled   |                   |             |  |

| PAD Resistor B               | Enable 3 |                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                         |                   |             |  |

| Address: 0xd0                | 03_0094  |                                                                                                                                                                                                                                                                                                           | Reset = 0x01e7_f0d0                                                                                                                                                                                                                                                                                     | Туре:             | RW          |  |

| Name                         | Bit      |                                                                                                                                                                                                                                                                                                           | Function                                                                                                                                                                                                                                                                                                |                   |             |  |

| pad_resistor_ena<br>[95-64]  | 31-0     | resist<br>resist<br>corre<br>0 = P                                                                                                                                                                                                                                                                        | A number of the external PADs have configurable pull-up/pull-down<br>esistors in the PAD. This register allows software to enable the<br>esistor. The following table maps these register bits to the<br>corresponding PADs that they control.<br>0 = PAD resistor disabled<br>I = PAD resistor enabled |                   |             |  |

| PAD Resistor E               | Enable 4 |                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                         |                   |             |  |

| Address: 0xd0                | 03_0098  |                                                                                                                                                                                                                                                                                                           | Reset = 0x0000_00bf                                                                                                                                                                                                                                                                                     | Туре:             | RW          |  |

| Name                         | Bit      |                                                                                                                                                                                                                                                                                                           | Function                                                                                                                                                                                                                                                                                                |                   | Reset       |  |

| pad_resistor_ena<br>[117-96] | 31-0     | A number of the external PADs have configurable pull-up/pull-down<br>resistors in the PAD. This register allows software to enable the<br>resistor. The following table maps these register bits to the<br>corresponding PADs that they control.<br>0 = PAD resistor disabled<br>1 = PAD resistor enabled |                                                                                                                                                                                                                                                                                                         |                   | 0x0000_00bf |  |

The table indicates whether the PAD has a pull-up or pull-down with the PU/PD nomenclature in the bit location field.

| Name           | Bit  | Function                                                                                                                                                                                                 | Reset |

|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Reserved       | 31-4 | Reserved                                                                                                                                                                                                 |       |

| Cas_latency    | 3-1  | CAS latency in memory clock cycles.                                                                                                                                                                      | d3    |

| Cas_half_cycle | 0    | Encodes whether the CAS latency is half a memory clock cycle more than<br>the value given in bite[3:1].<br>0=zero cycle offset (is forced in MDDR and SDR mode)<br>1=half cycle offset to value in [3:1] | d0    |

### 5.6.8 Tdqss register

It can only be read/written to in the config or low-power state.

| Tdqss         |      |                    |                                      |       |

|---------------|------|--------------------|--------------------------------------|-------|

| Address: 0x18 |      | Reset = 0x1        | Type: RW                             | ,     |

| Name          | Bit  |                    | Function                             | Reset |

| Reserved      | 31-2 | Reserved           |                                      |       |

| Tdqss         | 1-0  | Write to DQS in me | Write to DQS in memory clock cycles. |       |

## 5.6.9 Tmrd register

It can only be read/written to in the config or low-power state.

| Tmrd          |      |                       |                                                         |  |

|---------------|------|-----------------------|---------------------------------------------------------|--|

| Address: 0x1C |      | Reset = 0x2           | Type: RW                                                |  |

| Name          | Bit  |                       | Function                                                |  |

| Reserved      | 31-7 | Reserved              | Reserved                                                |  |

| Tmrd          | 6-0  | Sets mode register of | Sets mode register command time in memory clock cycles. |  |

### 5.6.10 Tras Register

It can only be read/written to in the config or low-power state.

| Tras          |      |                    |                                   |       |

|---------------|------|--------------------|-----------------------------------|-------|

| Address: 0x20 |      | Reset = 0x7        | Type: RW                          |       |

| Name          | Bit  |                    | Function                          | Reset |

| Reserved      | 31-4 | Reserved           |                                   |       |

| Tras          | 3-0  | Sets RAS to precha | rge delay in memory clock cycles. | 0x7   |

## 5.6.11 Trc Register

It can only be read/written to in the config or low-power state.

| Tdqss         |      |                    |       |                                           |       |

|---------------|------|--------------------|-------|-------------------------------------------|-------|

| Address: 0x24 |      | Reset = 0xB        |       | Type: RW                                  |       |

| Name          | Bit  |                    |       | Function                                  | Reset |

| Reserved      | 31-4 | Reserved           |       |                                           |       |

| Trc           | 3-0  | Sets active bank x | to ac | tive bank x delay in memory clock cycles. | 0xB   |

### 5.6.12 Trcd Register

It can only be read/written to in the config or low-power state.

| Trcd          |      |                                                       |                                       |       |

|---------------|------|-------------------------------------------------------|---------------------------------------|-------|

| Address: 0x28 |      | Reset = 0x1D                                          | Type: RW                              |       |

| Name          | Bit  |                                                       | Function                              | Reset |

| Reserved      | 31-6 | Reserved                                              |                                       |       |

| Schedule_Trcd | 5-3  | Sets the RAS to CAS minimum delay in aclk cycles – 3. |                                       | 0x5   |

| Trcd          | 2-0  | Sets the RAS to CAS n                                 | ninimum delay in memory clock cycles. | 0x5   |

### 5.6.13 Trfc Register

It can only be read/written to in the config or low-power state.

| Trfc          |       |                                                            |                                                            |       |

|---------------|-------|------------------------------------------------------------|------------------------------------------------------------|-------|

| Address: 0x2C |       | Reset = 0x212                                              | Type: RW                                                   |       |

| Name          | Bit   |                                                            | Function                                                   | Reset |

| Reserved      | 31-10 | Reserved                                                   |                                                            |       |

| Schedule_Trfc | 9-5   | Sets the auto-refresh command time in aclk cycles - 3.   0 |                                                            | 0x10  |

| Trfc          | 4-0   | Sets the auto-refresh o                                    | Sets the auto-refresh command time in memory clock cycles. |       |

## 5.6.14 Trp Register

It can only be read/written to in the config or low-power state.

| Тгр           |     |              |          |       |

|---------------|-----|--------------|----------|-------|

| Address: 0x30 |     | Reset = 0x1d | Type: RW |       |

| Name          | Bit |              | Function | Reset |

#### Registers

| Part_number | 3-0 | Primecell part number. | 0x3 |

|-------------|-----|------------------------|-----|

|-------------|-----|------------------------|-----|

| Peripheral_id2 |      |                            |          |       |

|----------------|------|----------------------------|----------|-------|

| Address: 0xfe8 |      | Reset = 0x14               | Type: RO |       |

| Name           | Bit  |                            | Function | Reset |

| Reserved       | 31-8 | Reserved                   | Reserved |       |

| revision       | 7-4  | Primecell revision number. |          | 0x1   |

| designer       | 3-0  | Primecell designer.        |          | 0x4   |

| Peripheral_id3 |      |                      |          |       |

|----------------|------|----------------------|----------|-------|

| Address: 0xfec |      | Reset = 0x0          | Type: RO |       |

| Name           | Bit  |                      | Function | Reset |

| Reserved       | 31-4 | Reserved             |          |       |

| Customer_mod   | 3-0  | Customer Modified nu | mber.    | 0x0   |

# 5.6.26 Primecell Identification 0-3 registers

| Pcell_id0      |      |             |          |       |

|----------------|------|-------------|----------|-------|

| Address: 0xff0 |      | Reset = 0xD | Type: RO |       |

| Name           | Bit  |             | Function | Reset |

| Reserved       | 31-8 | Reserved    |          |       |

| ld_number      | 7-0  | ld_number   |          | 0xD   |

| Pcell_id1      |      |              |          |       |

|----------------|------|--------------|----------|-------|

| Address: 0xff4 |      | Reset = 0xF0 | Type: RO |       |

| Name           | Bit  |              | Function | Reset |

| Reserved       | 31-8 | Reserved     |          |       |

| ld_number      | 7-0  | Id_number    |          | 0xF0  |

| Pcell_id2      |      |              |          |       |

| Address: 0xff8 |      | Reset = 0x5  | Type: RO |       |

| rx_push_error  | 8 | asserted when the receive FIFO experiences an underrun condition or misaligned access. This error is from the perspective of the external interface.                                                                                                                                                                                                                                                                                                                                                        | 0x0 |

|----------------|---|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| dma_pop_error  | 7 | asserted when the receive FIFO experiences an underrun condition or misaligned access. This error is from the perspective of the internal APB bus.                                                                                                                                                                                                                                                                                                                                                          | 0x0 |

| dma_push_error | 6 | asserted when the transmit FIFO experiences an overrun condition or<br>misaligned access. A misaligned access can occur if the width of the write<br>has changed from a previous access. For example, if byte writes have<br>previously been used, the number of writes may be non-multiples of 32 bits.<br>If a 32 bit write now occurs, this is a misaligned access because the byte<br>pointers in the FIFO are not pointing to byte '0'. This error is from the<br>perspective of the internal APB bus. | 0x0 |

| rx_ff          | 5 | asserted when the receive FIFO has become full                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 0x0 |

| rx_hf          | 4 | asserted when the receive FIFO level (amount of bytes in the FIFO) is above the software configured "half" empty level.                                                                                                                                                                                                                                                                                                                                                                                     | 0x0 |

| rx_fe          | 3 | asserted when the receive FIFO has become NOT empty                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0x0 |

| tx_ff          | 2 | asserted when the transmit FIFO has become NOT full                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0x0 |

| tx_hf          | 1 | asserted when the transmit FIFO level (amount of space available) is above the software configured "half" full level.                                                                                                                                                                                                                                                                                                                                                                                       | 0x0 |

| tx_fe          | 0 | asserted when the transmit FIFO has become empty                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 0x0 |

|                |   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

### Table 52. Interrupt Source Register

## 5.7.3 Interrupt Mask Register

The interrupt mask register provides a mechanism to individually mask one or more of the interrupt sources.

### Table 53. Interrupt Mask Register

| Interrupt Mask Re   | gister |                                        |          |       |

|---------------------|--------|----------------------------------------|----------|-------|

| Address: 0x0        | 4      | Reset = 0xFFFF_FFF                     | Type: RW |       |

| Name                | Bit    | Function                               |          | Reset |

| Reserved            | 31-15  | Reserved                               |          |       |

| corrected_data_done | 14     | Masks the interrupt. 1=mask, 0=unmask. |          |       |

| read_ecc_complete   | 13     | Masks the interrupt. 1=mask, 0=unmask. |          | 0x1   |

| write_par_complete  | 12     | Masks the interrupt. 1=mask, 0=unmask. |          | 0x1   |

| nand_block_write    | 11     | Masks the interrupt. 1=mask, 0=unmask. |          | 0x1   |

| nand block read | 10 | Masks the interrupt. 1=mask, 0=unmask. | 0x1  |

|-----------------|----|----------------------------------------|------|

| hand_block_read | 10 |                                        | 0.11 |

| tx_pop_error    | 9  | Masks the interrupt. 1=mask, 0=unmask. | 0x1  |

| rx_push_error   | 8  | Masks the interrupt. 1=mask, 0=unmask. | 0x1  |

| dma_pop_error   | 7  | Masks the interrupt. 1=mask, 0=unmask. | 0x1  |

| dma_push_error  | 6  | Masks the interrupt. 1=mask, 0=unmask. | 0x1  |

| rx_ff           | 5  | Masks the interrupt. 1=mask, 0=unmask. | 0x1  |

| rx_hf           | 4  | Masks the interrupt. 1=mask, 0=unmask. | 0x1  |

| rx_fe           | 3  | Masks the interrupt. 1=mask, 0=unmask. | 0x1  |

| tx_ff           | 2  | Masks the interrupt. 1=mask, 0=unmask. | 0x1  |

| tx_hf           | 1  | Masks the interrupt. 1=mask, 0=unmask. | 0x1  |

| tx_fe           | 0  | Masks the interrupt. 1=mask, 0=unmask. | 0x1  |

#### Table 53. Interrupt Mask Register

### 5.7.4 Interrupt Clear Register

The interrupt clear register provides the mechanism for clearing the raw interrupt sources. Writing a "1. to the interrupt bit location will clear the interrupt.

| Table 54. Interrupt | Clear Register |

|---------------------|----------------|

|---------------------|----------------|

| Interrupt Clear R   | egister |                                        |          |  |

|---------------------|---------|----------------------------------------|----------|--|

| Address: 0x         | 08      | Reset = 0x0                            | Туре: WO |  |

| Name                | Bit     | Function                               | Reset    |  |

| Reserved            | 31-15   | Reserved                               |          |  |

| corrected_data_done | 14      | Clears the interrupt when written '1'. | 0x0      |  |

| read_ecc_complete   | 13      | Clears the interrupt when written '1'. | 0x0      |  |

| write_par_complete  | 12      | Clears the interrupt when written '1'. | 0x0      |  |

| nand_block_write    | 11      | Clears the interrupt when written '1'. |          |  |

| nand_block_read     | 10      | Clears the interrupt when written '1'. |          |  |

| tx_pop_error        | 9       | Clears the interrupt when written '1'. | 0x0      |  |

| rx_push_error       | 8       | Clears the interrupt when written '1'. | 0x0      |  |

| dma_pop_error       | 7       | Clears the interrupt when written '1'. | 0x0      |  |

| dma_push_error      | 6       | Clears the interrupt when written '1'. | 0x0      |  |

| rx_ff               | 5       | Clears the interrupt when written '1'. | 0x0      |  |

| rx_hf               | 4       | Clears the interrupt when written '1'. | 0x0      |  |

# 5.8 UART Control Registers

# 5.8.1 UART Register Description

#### Table 74. UART Register Map

| Register                | Address Offset | Mode  |

|-------------------------|----------------|-------|

| Interrupt Source        | 0x00           | RO    |

| Interrupt Mask          | 0x04           | RW    |

| Interrupt Clear         | 0x08           | WO    |

| baud rate control       | 0x0C           | RW    |

| Configuration           | 0x10           | RW    |

| fifo status             | 0x14           | RO/WO |

| fifo flag Configuration | 0x18           | RW    |

| reserved                | 0x1C-0xfff     | WO    |

| transmit fifo           | 0x1000-0x1fff  | WO    |

| receive fifo            | 0x2000-0x2fff  | RO    |

The register map is summarized below and described in the following sections.

## 5.8.2 Interrupt Source Register

### Table 75. Interrupt Source Register

| Interrupt Source | Register |                                                                                                                                                            |     |  |

|------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

| Address: 0       | x00      | Reset = 0x0 Type: RO                                                                                                                                       |     |  |

| Name             | Bit      | Function                                                                                                                                                   |     |  |

| Reserved         | 31-13    | Reserved                                                                                                                                                   |     |  |

| RTS_raw          | 12       | This bit reflects the state of the RTS modem signal.                                                                                                       |     |  |

| CTS_raw          | 11       | This bit reflects the state of the CTS modem signal.                                                                                                       |     |  |

| rx_push_error    | 10       | asserted when the receive fifo experiences an overrun condition or<br>mis-aligned access. This error is from the perspective of the external<br>interface. |     |  |

| parity_error     | 9        | asserted when the receive block detects a parity error                                                                                                     |     |  |

| frame_error      | 8        | asserted when the receive block has detected a frame error (missing stop $\ensuremath{bit}(s))$                                                            | 0x0 |  |

| Address: 0x28   |      | Reset = 0x0 Type: RW                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|-----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Name            | Bit  |                                                                                                                                                                                              | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                |     |

| switch_over_cnt | 31-0 | down register is used w<br>mode. It's count is used<br>data to just counting sau<br>lineup with a completed<br>If enter_track_mode is s<br>longer be stored in the f<br>When enter_track_mod | tet the start value of a count down register. The count<br>hen switching from acquisition mode to tracking<br>to synchronize when the switch over from storing<br>mples (data is thrown away) occurs. Usually it will<br>DMA transaction.<br>set, and the count down register is "0" data will no<br>ifo. Instead the sample_cnt will be incremented.<br>e is cleared, the data is once again stored in the fifo<br>tarts decrementing from its programmed start value. | 0x0 |

| GPS Count     | er 2 |                                                                       |                                                                                                                                                                                           |  |

|---------------|------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Address: 0x2C | ;    | Reset = 0x0                                                           | Туре: RO                                                                                                                                                                                  |  |

| Name          | Bit  |                                                                       | Function                                                                                                                                                                                  |  |

| sample_cnt    | 31-0 | mode of operation.<br>It is cleared when the<br>and the count down re | It is cleared when the following event occurs – the enter_track_mode is set<br>and the count down register is "0".<br>When enter_track_mode becomes "0", the sample_cnt holds its current |  |

The following sequence is a typical use of the GPS registers.

- Initially the acquisition mode is entered. The GPS interface is enabled and the data is moved by the mc-dma to a storage buffer. The switch\_over\_cnt is programmed with a sample number that matches the chunk size that the mc-dma is programmed with.

- After acquisition, the tracking mode is entered. During this mode, most of the data is not required but the number of samples that have been received needs to be saved. To enter this mode, the "enter\_track\_mode" field is asserted. When this is asserted, the hardware will wait until the down counter expires (so that a known amount of data is received) and then just counts the number of samples that occur. The incoming data is discarded.

- When additional data samples are required, the "enter\_track\_mode" field is de-asserted. This will re-enable the data path to the fifo and hold the sample count until the next time the tracking mode is entered.

### 5.9.11 Transmit FIFO

The Transmit FIFO operates as a fifo even though it has a range of addresses. The wider range allows bus bursting to fill the fifo.

| Transmit FIF       | 0    |             |          |       |

|--------------------|------|-------------|----------|-------|

| Address: 0x1000-0x | 1fff | Reset = 0x0 | Туре: WO |       |

| Name               | Bit  |             | Function | Reset |

| tx fifo | 0x1000-0x1fff | WO |

|---------|---------------|----|

| rx fifo | 0x2000-0x2fff | RO |

## 5.10.1 Interrupt Source Register

The interrupt source register contains the raw unmasked interrupts and can be used for polling purposes (instead of the external interrupt pin) or for determining which interrupt(s) have caused the external interrupt pin to assert.

| Interrupt Source Regi | ster  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                |       |

|-----------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Address: 0x00         |       | Reset = 0x2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Type: RO                                                                                                                                                                                                                       |       |

| Name                  | Bit   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Function                                                                                                                                                                                                                       | Reset |

| Reserved              | 31-14 | Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                |       |

| modem_status          | 13    | This interrupt is only ap asserted after the mode                                                                                                                                                                                                                                                                                                                                                                                                                                                             | plicable for the AC97 mode of operation. It is more status field is valid.                                                                                                                                                     | 0x0   |

| cmd_read_complete     | 12    | asserted after a request                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | plicable for the AC97 mode of operation. It is<br>ed read command (slot 1 & 2) has completed and<br>ble in the AC97 status register.                                                                                           | 0x0   |

| cmd_write_complete    | 11    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | plicable for the AC97 mode of operation. It is<br>ted write command (slot 1 & 2) has completed.                                                                                                                                | 0x0   |

| codec_ready           | 10    | asserted when the "cod                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | This interrupt is only applicable for the AC97 mode of operation. It is asserted when the "codec ready" bit in the incoming TAG channel has transitioned from "0" to "1" indicating that the codec is now ready for operation. |       |

| tx_pop_error          | 9     | asserted when the receive fifo experiences an overrun condition or<br>mis-aligned access. This error is from the perspective of the external<br>interface.                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                | 0x0   |

| rx_push_error         | 8     | asserted when the transmit fifo experiences an underrun condition or<br>mis-aligned access. This error is from the perspective of the external<br>interface.                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                | 0x0   |

| bus_pop_error         | 7     | asserted when the receive fifo experiences an underrun condition or<br>mis-aligned access. This error is from the perspective of the internal APB<br>bus.                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                | 0x0   |

| bus_push_error        | 6     | asserted when the transmit fifo experiences an overrun condition or<br>mis-aligned access. A mis-aligned access can occur if the width of the<br>write has changed from a previous access. For example, if byte writes<br>have previously been used, the number of writes may be non-multiples of<br>32 bits. If a 32 bit write now occurs, this is a misaligned access because<br>the byte pointers in the fifo are not pointing to byte '0'. This error is from<br>the perspective of the internal APB bus. |                                                                                                                                                                                                                                | 0x0   |

| rx_ff                 | 5     | asserted when the receive fifo has become full                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                | 0x0   |

| rx_hf                 | 4     | asserted when the receive fifo level has risen above the software configured "half" empty level.                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                | 0x0   |

| rx_fe                 | 3     | asserted when the rece                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ive fifo has become NOT empty                                                                                                                                                                                                  | 0x0   |

| txd_word_length | 21-16 | Number of bits serialized in each active channel on the transmit interface.<br>Maximum value is 32 for the I2S mode of operation and 20 bits for the AC97<br>mode of operation. If this field has been changed after the fifos have been<br>used, the fifo must be flushed for proper operation.                                                                                                                                                                                                         |     |  |

|-----------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|--|

| rx_stereo       | 15    | This field enables whether or not the stereo mode is enabled for the receive<br>path. When the stereo mode is enabled the frame is organized as a left and<br>right channel where one channel is transmitted during the first half of frame<br>period and the second channel is transmitted during the second half of the<br>frame period. This setting is only applicable when the interface operates in<br>the I2S mode.<br>0 = mono operation (single channel)<br>1 = stereo operation (two channels) |     |  |

| loop_back       | 14    | When "1" the transmit data is looped back to the receive data.                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0x0 |  |

| common_sync     | 13    | The audio interface can utilize a common frame synchronization signal for<br>both the transmit and receive datapath or can use separate synchronization<br>signals. If a common synchronization signal is selected, then the bit clocks<br>must also be configured as common. The transmit frame signal (fsx) is used<br>if common_sync is enabled<br>1 = receive frame sync is shared with the transmit.<br>0 = receive frame sync is separate and unique from the transmit.                            | 0x0 |  |

| rx_bitclk_src   | 12    | The receive interface can operate with its own bit clock or it can share the transmit bit clock. For applications that have a single bit clock, the receive bit clock must be shared with the transmit bit clock. When the receive and transmit share a bit clock, that bit clock is the transmit bit clock. $0 = \text{receive}$ bit clock is shared with the transmit. $1 = \text{receive}$ bit clock is separate and unique from the transmit.                                                        |     |  |

| fsx_polarity    | 11    | <ul> <li>This bit sets the polarity of the transmit frame clock. If the external device sources the frame sync, this bit should be set such that the asic receives an active high frame sync.</li> <li>0 = internally generated frame sync is active high or external frame sync is NOT inverted.</li> <li>1 = internally generated frame sync is active low or external frame sync is inverted.</li> </ul>                                                                                              |     |  |

| fsr_polarity    | 10    | <ul> <li>This bit sets the polarity of the receive frame clock If the external device sources the frame sync, this bit should be set such that the asic receives an active high frame sync.</li> <li>0 = internally generated frame sync is active high or external frame sync is NOT inverted.</li> <li>1 = internally generated frame sync is active low or external frame sync is inverted.</li> </ul>                                                                                                |     |  |