Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

E·XFl

| Product Status          | Active                                                                                      |

|-------------------------|---------------------------------------------------------------------------------------------|

| Туре                    | Floating Point                                                                              |

| Interface               | CAN, EBI/EMI, Ethernet, DAI, I <sup>2</sup> C, MMC/SD/SDIO, SPI, SPORT, UART/USART, USB OTG |

| Clock Rate              | 450MHz                                                                                      |

| Non-Volatile Memory     | ROM (512kB)                                                                                 |

| On-Chip RAM             | 384kB                                                                                       |

| Voltage - I/O           | 3.30V                                                                                       |

| Voltage - Core          | 1.10V                                                                                       |

| Operating Temperature   | -40°C ~ 85°C (TA)                                                                           |

| Mounting Type           | Surface Mount                                                                               |

| Package / Case          | 349-LFBGA, CSPBGA                                                                           |

| Supplier Device Package | 349-CSPBGA (19x19)                                                                          |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-sc583bbcz-4a                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Table 7. Memory Map of Mapped I/Os

|                      | Byte Address Space                                                           |                                                     | SHARC+ Core Instruction Fetch |                       |  |

|----------------------|------------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------|-----------------------|--|

|                      | ARM Cortex-A5 – Data Access<br>and Instruction Fetch<br>SHARC+ – Data Access | Normal Word Address<br>Space for Data Access SHARC+ | VISA Space                    | ISA Space             |  |

| SMC Bank 0 (64 MB)   | 0x40000000-0x43FFFFFF                                                        | 0x01000000-0x01FFFFFF                               | 0x00F00000-0x00F3FFFF         | 0x00700000-0x0073FFFF |  |

| SMC Bank 1 (64 MB)   | 0x44000000-0x47FFFFF                                                         | Not applicable                                      | Not applicable                | Not applicable        |  |

| SMC Bank 2 (64 MB)   | 0x48000000-0x4BFFFFFF                                                        | Not applicable                                      | Not applicable                | Not applicable        |  |

| SMC Bank 3 (64 MB)   | 0x4C000000-0x4FFFFFF                                                         | Not applicable                                      | Not applicable                | Not applicable        |  |

| PCIe Data (256 MB)   | 0x50000000-0x5FFFFFF                                                         | 0x02000000-0x03FFFFFF                               | 0x00F40000-0x00F7FFFF         | 0x00740000-0x0077FFFF |  |

| SPI2 Memory (512 MB) | 0x6000000-0x7FFFFFF                                                          | 0x04000000-0x07FFFFFF                               | 0x00F80000-0x00FFFFF          | 0x00780000-0x007FFFFF |  |

#### Table 8. DMC Memory Map

|             | Byte Address Space                                                           |                                                     | SHARC+ Core Instruction Fetch |                       |  |

|-------------|------------------------------------------------------------------------------|-----------------------------------------------------|-------------------------------|-----------------------|--|

|             | ARM Cortex-A5 – Data Access and<br>Instruction Fetch<br>SHARC+ – Data Access | Normal Word Address<br>Space for Data Access SHARC+ |                               | ISA Space             |  |

| DMC0 (1 GB) | 0x80000000–0xBFFFFFF                                                         | -                                                   | 0x00800000-0x00AFFFF          |                       |  |

| DMC1 (1 GB) | 0xC0000000-0xFFFFFFF                                                         | 0x18000000-0x1FFFFFFF                               | 0x00C00000-0x00EFFFF          | 0x00600000-0x006FFFFF |  |

### System Crossbars (SCBs)

The system crossbars (SCBs) are the fundamental building blocks of a switch-fabric style for on-chip system bus interconnection. The SCBs connect system bus masters to system bus slaves, providing concurrent data transfer between multiple bus masters and multiple bus slaves. A hierarchical model—built from multiple SCBs—provides a power and area efficient system interconnection.

The SCBs provide the following features:

- Highly efficient, pipelined bus transfer protocol for sustained throughput

- Full-duplex bus operation for flexibility and reduced latency

- Concurrent bus transfer support to allow multiple bus masters to access bus slaves simultaneously

- Protection model (privileged/secure) support for selective bus interconnect protection

### Direct Memory Access (DMA)

The processors use direct memory access (DMA) to transfer data within memory spaces or between a memory space and a peripheral. The processors can specify data transfer operations and return to normal processing while the fully integrated DMA controller carries out the data transfers independent of processor activity.

DMA transfers can occur between memory and a peripheral or between one memory and another memory. Each memory to memory DMA stream uses two channels: one channel is the source channel and the second is the destination channel.

All DMA channels can transport data to and from all on-chip and off-chip memories. Programs can use two types of DMA transfers: descriptor-based or register-based. Register-based DMA allows the processors to program DMA control registers directly to initiate a DMA transfer. On completion, the DMA control registers automatically update with original setup values for continuous transfer. Descriptor-based DMA transfers require a set of parameters stored within memory to initiate a DMA sequence. Descriptor-based DMA transfers allow multiple DMA sequences to be chained together. Program a DMA channel to set up and start another DMA transfer automatically after the current sequence completes.

The DMA engine supports the following DMA operations:

- A single linear buffer that stops on completion

- A linear buffer with negative, positive, or zero stride length

- A circular autorefreshing buffer that interrupts when each buffer becomes full

- A similar circular buffer that interrupts on fractional buffers, such as at the halfway point

- The 1D DMA uses a set of identical ping pong buffers defined by a linked ring of two-word descriptor sets, each containing a link pointer and an address

- The 1D DMA uses a linked list of four-word descriptor sets containing a link pointer, an address, a length, and a configuration

- The 2D DMA uses an array of one-word descriptor sets, specifying only the base DMA address

- The 2D DMA uses a linked list of multiword descriptor sets, specifying all configurable parameters

CRC checksums can be calculated or compared automatically during memory transfers, or one or multiple memory regions can be continuously scrubbed by a single DMA work unit as per DMA descriptor chain instructions. The CRC engine also protects data loaded during the boot process.

## Signal Watchdogs

The eight general-purpose timers feature modes to monitor offchip signals. The watchdog period mode monitors whether external signals toggle with a period within an expected range. The watchdog width mode monitors whether the pulse widths of external signals are within an expected range. Both modes help to detect undesired toggling or lack of toggling of system level signals.

### System Event Controller (SEC)

Besides system events, the system event controller (SEC) further supports fault management including fault action configuration as timeout, internal indication by system interrupt, or external indication through the SYS\_FAULT pin and system reset.

## **PROCESSOR PERIPHERALS**

The following sections describe the peripherals of the ADSP-SC58x/ADSP-2158x processors.

## Dynamic Memory Controller (DMC)

The 16-bit dynamic memory controller (DMC) interfaces to:

- LPDDR1 (JESD209A) maximum frequency 200 MHz, DDRCLK (64 Mb to 2 Gb)

- DDR2 (JESD79-2E) maximum frequency 400 MHz, DDRCLK (256 Mb to 4 Gb)

- DDR3 (JESD79-3E) maximum frequency 450 MHz, DDRCLK (512 Mb to 8 Gb)

- DDR3L (1.5 V compatible only) maximum frequency 450 MHz, DDRCLK (512 Mb to 8 Gb)

See Table 8 for the DMC memory map.

### Digital Audio Interface (DAI)

The processors support two mirrored digital audio interface (DAI) units. Each DAI can connect various peripherals to any of the DAI pins (DAI\_PIN20-DAI\_PIN01).

The application code makes these connections using the signal routing unit (SRU), shown in Figure 1.

The SRU is a matrix routing unit (or group of multiplexers) that enables the peripherals provided by the DAI to interconnect under software control. This functionality allows easy use of the DAI associated peripherals for a wider variety of applications by using a larger set of algorithms than is possible with nonconfigurable signal paths.

The DAI includes the peripherals described in the following sections (SPORTs, ASRC, S/PDIF, and PCG). DAI pin buffers 20 and 19 can change the polarity of the input signals. Most signals of the peripherals belonging to different DAIs cannot be interconnected, with few exceptions. The DAI\_PINx pin buffers may also be used as GPIO pins. DAI input signals allow the triggering of interrupts on the rising edge, the falling edge, or both edges.

See the Digital Audio Interface (DAI) chapter of the ADSP-SC58x/ADSP-2158x SHARC+ Processor Hardware Reference for complete information on the use of the DAIs and SRUs.

### Serial Ports (SPORTs)

The processors feature eight synchronous full serial ports. These ports provide an inexpensive interface to a wide variety of digital and mixed-signal peripheral devices. These devices include Analog Devices AD19xx/ADAU19xx family of audio codecs, analog-to-digital converters (ADCs) and digital-to-analog converters (DACs). Two data lines, a clock, and frame sync make up the serial ports. The data lines can be programmed to either transmit or receive data and each data line has a dedicated DMA channel.

An individual full SPORT module consists of two independently configurable SPORT halves with identical functionality. Two bidirectional data lines—primary (0) and secondary (1)—are available per SPORT half and are configurable as either transmitters or receivers. Therefore, each SPORT half permits two unidirectional streams into or out of the same SPORT. This bidirectional functionality provides greater flexibility for serial communications. For full-duplex configuration, one half SPORT provides two transmit signals, while the other half SPORT provides the two receive signals. The frame sync and clock are shared.

Serial ports operate in the following six modes:

- Standard DSP serial mode

- Multichannel time division multiplexing (TDM) mode

- I<sup>2</sup>S mode

- Packed I<sup>2</sup>S mode

- Left justified mode

- Right justified mode

### Asynchronous Sample Rate Converter (ASRC)

The asynchronous sample rate converter (ASRC) contains eight ASRC blocks. It is the same core in the AD1896 192 kHz stereo asynchronous sample rate converter. The ASRC provides up to 140 dB signal-to-noise ratio (SNR). The ASRC block performs synchronous or asynchronous sample rate conversion across independent stereo channels, without using internal processor resources. The ASRC blocks can also be configured to operate together to convert multichannel audio data without phase mismatches. Finally, the ASRC can clean up audio data from jittery clock sources such as the S/PDIF receiver.

### S/PDIF-Compatible Digital Audio Receiver/Transmitter

The Sony/Philips Digital Interface Format (S/PDIF) is a standard audio data transfer format that allows the transfer of digital audio signals from one device to another without converting them to an analog signal. There are two S/PDIF transmit/receive

- DMC (VDD\_DMC)

- PCIe (VDD\_PCIE, VDD\_PCIE\_TX and VDD\_PCIE\_RX)

All power supplies must meet the specifications provided in the Operating Conditions section. All external supply pins must be connected to the same power supply.

### **Power Management**

As shown in Table 10, the processors support four different power domains, which maximizes flexibility while maintaining compliance with industry standards and conventions. There are no sequencing requirements for the various power domains, but all domains must be powered according to the appropriate specifications (see the Specifications section for processor operating conditions). If the feature or the peripheral is not used, refer to Table 27.)

#### Table 10. Power Domains

| Power Domain                                      | V <sub>DD</sub> Range   |

|---------------------------------------------------|-------------------------|

| All internal logic                                | V <sub>DD_INT</sub>     |

| DDR3/DDR2/LPDDR                                   | V <sub>DD_DMC</sub>     |

| USB                                               | V <sub>DD_USB</sub>     |

| HADC                                              | V <sub>DD_HADC</sub>    |

| RTC                                               | V <sub>DD_RTC</sub>     |

| PCIe_TX                                           | V <sub>DD_PCIE_TX</sub> |

| PCIe_RX                                           | V <sub>DD_PCIE_RX</sub> |

| PCIe                                              | V <sub>DD_PCIE</sub>    |

| All other I/O (includes SYS, JTAG, and port pins) | V <sub>DD_EXT</sub>     |

The power dissipated by the processors is largely a function of the clock frequency and the square of the operating voltage. For example, reducing the clock frequency by 25% results in a 25% reduction in dynamic power dissipation.

## Target Board JTAG Emulator Connector

The Analog Devices DSP tools product line of JTAG emulators uses the IEEE 1149.1 JTAG test access port of the processors to monitor and control the target board processor during emulation. The Analog Devices DSP tools product line of JTAG emulators provides emulation at full processor speed, allowing inspection and modification of memory, registers, and processor stacks. The processor JTAG interface ensures the emulator does not affect target system loading or timing.

For information on JTAG emulator operation, see the appropriate emulator hardware user's guide at SHARC Processors Software and Tools.

## SYSTEM DEBUG

The processors include various features that allow easy system debug. These are described in the following sections.

### System Watchpoint Unit (SWU)

The system watchpoint unit (SWU) is a single module that connects to a single system bus and provides transaction monitoring. One SWU is attached to the bus going to each system slave. The SWU provides ports for all system bus address channel signals. Each SWU contains four match groups of registers with associated hardware. These four SWU match groups operate independently but share common event (for example, interrupt and trigger) outputs.

## Debug Access Port (DAP)

Debug access port (DAP) provides IEEE 1149.1 JTAG interface support through the JTAG debug. The DAP provides an optional instrumentation trace for both the core and system. It provides a trace stream that conforms to *MIPI System Trace Protocol version 2 (STPv2)*.

## **DEVELOPMENT TOOLS**

Analog Devices supports its processors with a complete line of software and hardware development tools, including an integrated development environment (CrossCore<sup>®</sup> Embedded Studio), evaluation products, emulators, and a variety of software add-ins.

### Integrated Development Environments (IDEs)

For C/C++ software writing and editing, code generation, and debug support, Analog Devices offers the CrossCore Embedded Studio integrated development environment (IDE).

CrossCore Embedded Studio is based on the Eclipse framework. Supporting most Analog Devices processor families, it is the IDE of choice for processors, including multicore devices. CrossCore Embedded Studio seamlessly integrates available software add-ins to support real time operating systems, file systems, TCP/IP stacks, USB stacks, algorithmic software modules, and evaluation hardware board support packages. For more information, visit www.analog.com/cces.

## EZ-KIT Lite Evaluation Board

For processor evaluation, Analog Devices provides a wide range of EZ-KIT Lite<sup>®</sup> evaluation boards. Including the processor and key peripherals, the evaluation board also supports on-chip emulation capabilities and other evaluation and development features. Various EZ-Extenders<sup>®</sup> are also available, which are daughter cards that deliver additional specialized functionality, including audio and video processing. For more information visit www.analog.com.

## **EZ-KIT Lite Evaluation Kits**

For a cost-effective way to learn more about developing with Analog Devices processors, Analog Devices offer a range of EZ-KIT Lite evaluation kits. Each evaluation kit includes an EZ-KIT Lite evaluation board, directions for downloading an evaluation version of the available IDE(s), a USB cable, and a power supply. The USB controller on the EZ-KIT Lite board connects to the USB port of the user PC, enabling the chosen IDE evaluation suite to emulate the on-board processor in-circuit.

This permits the customer to download, execute, and debug programs for the EZ-KIT Lite system. It also supports in circuit programming of the on-board Flash device to store user specific boot code, enabling standalone operation. With the full version of CrossCore Embedded Studio installed (sold separately), engineers can develop software for supported EZ-KITs or any custom system utilizing supported Analog Devices processors.

### Software Add-Ins for CrossCore Embedded Studio

Analog Devices offers software add-ins which seamlessly integrate with CrossCore Embedded Studio to extend the capabilities and reduce development time. Add-ins include board support packages for evaluation hardware, various middleware packages, and algorithmic modules. Documentation, help, configuration dialogs, and coding examples present in these add-ins are viewable through the CrossCore Embedded Studio IDE once the add-in is installed.

### **Board Support Packages for Evaluation Hardware**

Software support for the EZ-KIT Lite evaluation boards and EZ-Extender daughter cards is provided by software add-ins called board support packages (BSPs). The BSPs contain the required drivers, pertinent release notes, and select example code for the given evaluation hardware. A download link for a specific BSP is located on the web page for the associated EZ-KIT or EZ-Extender product.

### **Middleware Packages**

Analog Devices offers middleware add-ins such as real time operating systems, file systems, USB stacks, and TCP/IP stacks. For more information, see the following web pages:

- www.analog.com/ucos2

- www.analog.com/ucos3

- www.analog.com/ucfs

- www.analog.com/ucusbd

- www.analog.com/ucusbh

- www.analog.com/lwip

## **Algorithmic Modules**

To speed development, Analog Devices offers add-ins that perform popular audio and video processing algorithms. These are available for use with CrossCore Embedded Studio. For more information visit www.analog.com.

## Designing an Emulator-Compatible DSP Board (Target)

For embedded system test and debug, Analog Devices provides a family of emulators. On each JTAG DSP, Analog Devices supplies an IEEE 1149.1 JTAG test access port (TAP). In-circuit emulation is facilitated by use of this JTAG interface. The emulator accesses the internal features of the processor via the TAP, allowing the developer to load code, set breakpoints, and view variables, memory, and registers. The processor must be halted to send data and commands, but once an operation is completed by the emulator, the DSP system is set to run at full speed with no impact on system timing. The emulators require the target board to include a header that supports connection of the JTAG port of the DSP to the emulator.

For details on target board design issues including mechanical layout, single processor connections, signal buffering, signal termination, and emulator pod logic, see "Analog Devices JTAG Emulation Technical Reference" (EE-68).

## **ADDITIONAL INFORMATION**

This data sheet provides a general overview of the ADSP-SC58x/ADSP-2158x architecture and functionality. For detailed information on the core architecture and instruction set, refer to the SHARC+ Core Programming Reference.

## **RELATED SIGNAL CHAINS**

A signal chain is a series of signal-conditioning electronic components that receive input (data acquired from sampling either real-time phenomena or from stored data) in tandem, with the output of one portion of the chain supplying input to the next. Signal chains are often used in signal processing applications to gather and process data or to apply system controls based on analysis of real-time phenomena.

Analog Devices eases signal processing system development by providing signal processing components that are designed to work together well. A tool for viewing relationships between specific applications and related components is available on the www.analog.com website.

The application signal chains page in the Circuits from the Lab<sup>®</sup> site (http://www.analog.com/circuits) provides the following:

- Graphical circuit block diagram presentation of signal chains for a variety of circuit types and applications

- Drill down links for components in each chain to selection guides and application information

- Reference designs applying best practice design techniques

## SECURITY FEATURES DISCLAIMER

To our knowledge, the Security Features, when used in accordance with the data sheet and hardware reference manual specifications, provide a secure method of implementing code and data safeguards. However, Analog Devices does not guarantee that this technology provides absolute security. ACCORDINGLY, ANALOG DEVICES HEREBY DISCLAIMS ANY AND ALL EXPRESS AND IMPLIED WARRANTIES THAT THE SECURITY FEATURES CANNOT BE BREACHED, COMPROMISED, OR OTHERWISE CIRCUM-VENTED AND IN NO EVENT SHALL ANALOG DEVICES BE LIABLE FOR ANY LOSS, DAMAGE, DESTRUCTION, OR RELEASE OF DATA, INFORMATION, PHYSICAL PROP-ERTY, OR INTELLECTUAL PROPERTY.

| Signal Name | Description                           | Port      | Pin Name    |

|-------------|---------------------------------------|-----------|-------------|

| HADC0_VIN5  | HADC0 Analog Input at channel 5       | Not Muxed | HADC0_VIN5  |

| HADC0_VIN6  | HADC0 Analog Input at channel 6       | Not Muxed | HADC0_VIN6  |

| HADC0_VIN7  | HADC0 Analog Input at channel 7       | Not Muxed | HADC0_VIN7  |

| HADC0_VREFN | HADC0 Ground Reference for ADC        | Not Muxed | HADC0_VREFN |

| HADC0_VREFP | HADC0 External Reference for ADC      | Not Muxed | HADC0_VREFP |

| JTG_TCK     | TAPC JTAG Clock                       | Not Muxed | JTG_TCK     |

| JTG_TDI     | TAPC JTAG Serial Data In              | Not Muxed | JTG_TDI     |

| JTG_TDO     | TAPC JTAG Serial Data Out             | Not Muxed | JTG_TDO     |

| JTG_TMS     | TAPC JTAG Mode Select                 | Not Muxed | JTG_TMS     |

| JTG_TRST    | TAPC JTAG Reset                       | Not Muxed | JTG_TRST    |

| LP0_ACK     | LP0 Acknowledge                       | D         | PD_11       |

| LP0_CLK     | LP0 Clock                             | D         | PD_10       |

| LP0_D0      | LP0 Data 0                            | D         | PD_02       |

| LP0_D1      | LP0 Data 1                            | D         | PD_03       |

| LP0_D2      | LP0 Data 2                            | D         | PD_04       |

| LP0_D3      | LP0 Data 3                            | D         | <br>PD_05   |

| LP0_D4      | LP0 Data 4                            | D         | PD_06       |

| LP0_D5      | LP0 Data 5                            | D         | PD_07       |

| LP0_D6      | LP0 Data 6                            | D         | PD_08       |

| LP0_D7      | LP0 Data 7                            | D         | PD_09       |

| LP1_ACK     | LP1 Acknowledge                       | В         | PB_15       |

| LP1_CLK     | LP1 Clock                             | C         | PC_00       |

| LP1_D0      | LP1 Data 0                            | В         | PB_07       |

| LP1_D1      | LP1 Data 1                            | В         | PB_08       |

| LP1_D2      | LP1 Data 2                            | В         | PB_09       |

| LP1_D3      | LP1 Data 3                            | В         | PB_10       |

| LP1_D4      | LP1 Data 4                            | В         | PB_11       |

| LP1_D5      | LP1 Data 5                            | В         | PB_12       |

| LP1_D6      | LP1 Data 6                            | В         | PB_13       |

| LP1_D7      | LP1 Data 7                            | В         | PB_14       |

| MLB0_CLKN   | MLB0 Negative Differential Clock (–)  | Not Muxed | MLB0_CLKN   |

| MLB0_CLKP   | MLB0 Positive Differential Clock (+)  | Not Muxed | MLB0_CLKP   |

| MLB0_DATN   | MLB0 Negative Differential Data (–)   | Not Muxed | MLB0_DATN   |

| MLB0_DATP   | MLB0 Positive Differential Data (+)   | Not Muxed | MLB0_DATP   |

| MLB0_SIGN   | MLB0 Negative Differential Signal (–) | Not Muxed | MLB0_SIGN   |

| MLB0_SIGP   | MLB0 Positive Differential Signal (+) | Not Muxed | MLB0_SIGP   |

| MLB0_CLK    | MLB0 Single-Ended Clock               | B         | PB_04       |

| MLB0_DAT    | MLB0 Single-Ended Data                | B         | PB_06       |

| MLB0_SIG    | MLB0 Single-Ended Signal              | B         | PB_05       |

| MLB0_CLKOUT | MLB0 Single-Ended Signal              | D         | PD_14       |

|             | _                                     |           |             |

| PA_00-15    | PORTA Position 00 through Position 15 | A         | PA_00-15    |

| PB_00-15    | PORTB Position 00 through Position 15 | B         | PB_00-15    |

| PC_00-15    | PORTC Position 00 through Position 15 | C         | PC_00-15    |

| PD_00-15    | PORTD Position 00 through Position 15 | D         | PD_00-15    |

| PE_00-15    | PORTE Position 00 through Position 15 | E         | PE_00-15    |

| PPIO_CLK    | EPPIO Clock                           | E         | PE_03       |

| PPI0_D00    | EPPIO Data 0                          | E         | PE_12       |

| PPI0_D01    | EPPI0 Data 1                          | E         | PE_11       |

## Table 12. ADSP-SC58x/ADSP-2158x 349-Ball CSP\_BGA Signal Descriptions (Continued)

| Signal Name              | Description                      | Port      | Pin Name       |

|--------------------------|----------------------------------|-----------|----------------|

| SYS_BMODE0               | Boot Mode Control n              | Not Muxed | SYS_BMODE0     |

| SYS_BMODE1               | Boot Mode Control n              | Not Muxed | SYS_BMODE1     |

| SYS_BMODE2               | Boot Mode Control n              | Not Muxed | SYS_BMODE2     |

| SYS_CLKIN0               | Clock/Crystal Input              | Not Muxed | SYS_CLKIN0     |

| SYS_CLKIN1               | Clock/Crystal Input              | Not Muxed | SYS_CLKIN1     |

| SYS_CLKOUT               | Processor Clock Output           | Not Muxed | SYS_CLKOUT     |

| SYS_FAULT                | Active High Fault Output         | Not Muxed | SYS_FAULT      |

| SYS_FAULT                | Active Low Fault Output          | Not Muxed | SYS_FAULT      |

| SYS_HWRST                | Processor Hardware Reset Control | Not Muxed | SYS_HWRST      |

| SYS_RESOUT               | Reset Output                     | Not Muxed | SYS_RESOUT     |

| SYS_XTAL0                | Crystal Output                   | Not Muxed | SYS_XTAL0      |

| SYS_XTAL1                | Crystal Output                   | Not Muxed | SYS_XTAL1      |

| M0_ACI0                  | TIMER0 Alternate Capture Input 0 | С         | PC_14          |

| ۲M0_ACI1                 | TIMERO Alternate Capture Input 1 | В         | PB_03          |

| TM0_ACI2                 | TIMERO Alternate Capture Input 2 | D         | PD_13          |

|                          | TIMERO Alternate Capture Input 3 | С         | <br>PC_07      |

| ΓM0_ACI4                 | TIMER0 Alternate Capture Input 4 | В         | PB_10          |

| FM0_ACLK1                | TIMER0 Alternate Clock 1         | D         | PD_08          |

| FM0_ACLK2                | TIMERO Alternate Clock 2         | D         | PD_09          |

| TM0_ACLK3                | TIMERO Alternate Clock 3         | В         | PB_00          |

| TM0_ACLK4                | TIMERO Alternate Clock 4         | В         | PB_01          |

| MO_CLK                   | TIMER0 Clock                     | C         | PC_11          |

| TM0_TMR0                 | TIMERO Timer 0                   | E         | PE_09          |

| M0_TMR1                  | TIMERO Timer 1                   | В         | PB_15          |

| TM0_TMR2                 | TIMERO Timer 2                   | В         | PB_10          |

| FM0_TMR3                 | TIMERO Timer 3                   | В         | PB_07          |

| TM0_TMR4                 | TIMERO Timer 4                   | В         | PB_08          |

| FM0_TMR5                 | TIMERO Timer 5                   | B         | PB_14          |

| TRACE0_CLK               | TRACE0 Trace Clock               | D         | PD_10          |

| TRACE0_CER               | TRACEO Trace Data 0              | D         | PD_02          |

| TRACE0_D00               | TRACEO Trace Data 0              | D         | PD_02<br>PD_03 |

|                          | TRACEO Trace Data 1              |           | PD_03          |

| FRACE0_D02<br>FRACE0_D03 |                                  | D         |                |

|                          | TRACEO Trace Data 3              | D         | PD_05          |

| TRACE0_D04               | TRACEO Trace Data 4              | D         | PD_06          |

| RACE0_D05                | TRACEO Trace Data 5              | D         | PD_07          |

| RACE0_D06                | TRACEO Trace Data 6              | D         | PD_08          |

| TRACE0_D07               | TRACE0 Trace Data 7              | D         | PD_09          |

| TWI0_SCL                 | TWI0 Serial Clock                | Not Muxed | TWI0_SCL       |

| TWI0_SDA                 | TWI0 Serial Data                 | Not Muxed | TWI0_SDA       |

| WI1_SCL                  | TWI1 Serial Clock                | Not Muxed | TWI1_SCL       |

| WI1_SDA                  | TWI1 Serial Data                 | Not Muxed | TWI1_SDA       |

| WI2_SCL                  | TWI2 Serial Clock                | Not Muxed | TWI2_SCL       |

| WI2_SDA                  | TWI2 Serial Data                 | Not Muxed | TWI2_SDA       |

| JARTO_CTS                | UARTO Clear to Send              | D         | PD_00          |

| JARTO_RTS                | UART0 Request to Send            | C         | PC_15          |

| JARTO_RX                 | UART0 Receive                    | C         | PC_14          |

| JARTO_TX                 | UARTO Transmit                   | С         | PC_13          |

| JART1_CTS                | UART1 Clear to Send              | E         | PE_01          |

## Table 12. ADSP-SC58x/ADSP-2158x 349-Ball CSP\_BGA Signal Descriptions (Continued)

| Signal Name | Description            | Port      | Pin Name    |

|-------------|------------------------|-----------|-------------|

| VDD_PCIE    | PCIE Supply Voltage    | Not Muxed | VDD_PCIE    |

| VDD_PCIE_RX | PCIE RX Supply Voltage | Not Muxed | VDD_PCIE_RX |

| VDD_PCIE_TX | PCIE TX Supply Voltage | Not Muxed | VDD_PCIE_TX |

| VDD_RTC     | RTC VDD                | Not Muxed | VDD_RTC     |

| VDD_USB     | USB VDD                | Not Muxed | VDD_USB     |

Table 19. ADSP-SC58x/ADSP-2158x 529-Ball CSP\_BGA Signal Descriptions (Continued)

|             |       | Driver |          | Reset |       | Description  |                   |

|-------------|-------|--------|----------|-------|-------|--------------|-------------------|

| Signal Name | Туре  | Туре   | Term     | Term  | Drive | Power Domain | and Notes         |

| DAI0_PIN16  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI0 Pin 16 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI0_PIN17  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI0 Pin 17 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI0_PIN18  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI0 Pin 18 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI0_PIN19  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI0 Pin 19 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI0_PIN20  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI0 Pin 20 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN01  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 1  |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN02  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 2  |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN03  | InOut | A      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 3  |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN04  | InOut | A      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 4  |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN05  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 5  |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN06  | InOut | A      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 6  |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN07  | InOut | A      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 7  |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN08  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 8  |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN09  | InOut | A      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 9  |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN10  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 10 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN11  | InOut | A      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 11 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN12  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 12 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN13  | InOut | A      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 13 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN14  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 14 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN15  | InOut | A      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 15 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN16  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 16 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN17  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 17 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN18  | InOut | A      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 18 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN19  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 19 |

|             |       |        | 1        |       |       |              | Notes: No notes   |

| Signal Name | Туре  | Driver<br>Type | Int<br>Term | Reset<br>Term | Reset<br>Drive | Power Domain | Description<br>and Notes                                                                                                                                   |

|-------------|-------|----------------|-------------|---------------|----------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PA_02       | InOut | A              | PullDown    | none          | none           | VDD_EXT      | Desc: PORTA Position 2   EMAC0<br>Management Channel Clock  <br>SMC0 Address 24                                                                            |

|             |       |                |             |               |                |              | Notes: No notes                                                                                                                                            |

| PA_03       | InOut | A              | PullDown    | none          | none           | VDD_EXT      | Desc: PORTA Position 3   EMAC0<br>Management Channel Serial<br>Data   SMC0 Address 23<br>Notes: No notes                                                   |

| PA_04       | InOut | A              | PullDown    | none          | none           | VDD_EXT      | Desc: PORTA Position 4   EMAC0<br>Receive Data 0   SMC0 Address 19                                                                                         |

|             |       |                |             |               |                |              | Notes: No notes                                                                                                                                            |

| PA_05       | InOut | A              | PullDown    | none          | none           | VDD_EXT      | Desc: PORTA Position 5   EMAC0<br>Receive Data 1   SMC0 Address 18<br>Notes: No notes                                                                      |

| PA_06       | InOut | A              | PullDown    | none          | none           | VDD_EXT      | Desc: PORTA Position 6   EMAC0<br>RXCLK (GigE) or REFCLK (10/100)<br>  SMC0 Address 17                                                                     |

|             |       |                |             |               |                |              | Notes: No notes                                                                                                                                            |

| PA_07       | InOut | A              | PullDown    | none          | none           | VDD_EXT      | Desc: EMAC0 RXCTL (GigE) or<br>CRS (10/100)   PORTA Position 7  <br>EMAC0 Carrier Sense/RMII<br>Receive Data Valid   SMC0<br>Address 16<br>Notes: No notes |

| PA_08       | InOut | A              | PullDown    | none          | none           | VDD_EXT      | Desc: PORTA Position 8   EMAC0<br>Receive Data 2   SMC0 Address 12<br>Notes: No notes                                                                      |

| PA_09       | InOut | A              | PullDown    | none          | none           | VDD_EXT      | Desc: PORTA Position 9   EMAC0<br>Receive Data 3   SMC0 Address 11<br>Notes: No notes                                                                      |

| PA_10       | InOut | A              | PullDown    | none          | none           | VDD_EXT      | Desc: EMAC0 TXCTL (GigE) or<br>TXEN (10/100)   PORTA Position<br>10   EMAC0 Transmit Enable  <br>SMC0 Address 22<br>Notes: No notes                        |

| PA_11       | InOut | A              | PullDown    | none          | none           | VDD_EXT      | Desc: PORTA Position 11   EMAC0<br>Transmit Clock   SMC0 Address<br>15                                                                                     |

|             |       |                |             |               |                |              | Notes: No notes                                                                                                                                            |

| PA_12       | InOut | A              | PullDown    | none          | none           | VDD_EXT      | Desc: PORTA Position 12   EMAC0<br>Transmit Data 2   SMC0 Address<br>14                                                                                    |

|             |       |                |             |               |                |              | Notes: No notes                                                                                                                                            |

| PA_13       | InOut | A              | PullDown    | none          | none           | VDD_EXT      | Desc: PORTA Position 13   EMAC0<br>Transmit Data 3   SMC0 Address<br>13                                                                                    |

|             |       |                |             |               |                |              | Notes: No notes                                                                                                                                            |

| PA_14       | InOut | A              | PullDown    | none          | none           | VDD_EXT      | Desc: PORTA Position 14   EMAC0<br>PTP Pulse-Per-Second Output 3  <br>SINC0 Data 0   SMC0 Address 10<br>Notes: No notes                                    |

| Signal Name | Туре   | Driver<br>Type | Int<br>Term | Reset<br>Term | Reset<br>Drive | Power Domain | Description<br>and Notes                                                                                                                  |

|-------------|--------|----------------|-------------|---------------|----------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| PC_00       | InOut  | Н              | PullDown    |               |                | VDD_EXT      | Desc: PORTC Position 0   LP1                                                                                                              |

| 10_00       | mout   | п              | Puildown    | none          | none           | VDD_EXT      | Clock   PWM0 Channel B Low<br>Side   SMC0 Read Enable   SPI0                                                                              |

|             |        |                |             |               |                |              | Slave Select Output 4<br>Notes: No notes                                                                                                  |

| PC_01       | InOut  | А              | PullDown    | 2020          |                | VDD_EXT      | Desc: PORTC Position 1   SPI2                                                                                                             |

| PC_01       | mout   |                | FuilDown    | none          | none           | VDD_EXT      | Clock                                                                                                                                     |

| PC 02       |        |                | 0.110       |               |                |              | Notes: No notes                                                                                                                           |

| PC_02       | InOut  | A              | PullDown    | none          | none           | VDD_EXT      | Desc: PORTC Position 2   SPI2<br>Master In, Slave Out                                                                                     |

|             | In Out |                | DullDaura   |               |                |              | Notes: No notes                                                                                                                           |

| PC_03       | InOut  | A              | PullDown    | none          | none           | VDD_EXT      | Desc: PORTC Position 3   SPI2<br>Master Out, Slave In                                                                                     |

| DC 04       |        |                | 0.110       |               |                |              | Notes: No notes                                                                                                                           |

| PC_04       | InOut  | A              | PullDown    | none          | none           | VDD_EXT      | Desc: PORTC Position 4   SPI2<br>Data 2                                                                                                   |

|             |        |                |             |               |                |              | Notes: No notes                                                                                                                           |

| PC_05       | InOut  | A              | PullDown    | none          | none           | VDD_EXT      | Desc: PORTC Position 5   SPI2<br>Data 3                                                                                                   |

|             |        |                |             |               |                |              | Notes: No notes                                                                                                                           |

| PC_06       | InOut  | A              | PullDown    | none          | none           | VDD_EXT      | Desc: PORTC Position 6   SPI2<br>Slave Select Output 1   SPI2 Slave<br>Select Input                                                       |

|             |        |                |             |               |                |              | Notes: No notes                                                                                                                           |

| PC_07       | InOut  | A              | PullDown    | none          | none           | VDD_EXT      | Desc: PORTC Position 7   CAN0<br>Receive   SMC0 Memory Select 2<br>  SPI0 Slave Select Output 1  <br>TIMER0 Alternate Capture Input<br>3  |

|             |        |                |             |               |                |              | Notes: No notes                                                                                                                           |

| PC_08       | InOut  | A              | PullDown    | none          | none           | VDD_EXT      | Desc: PORTC Position 8   CAN0<br>Transmit   SMC0 Memory Select                                                                            |

|             |        |                |             |               |                |              | 3<br>Notes: No notes                                                                                                                      |

| PC_09       | InOut  | A              | PullDown    | none          | none           | VDD_EXT      | Desc: PORTC Position 9   SPI0<br>Clock                                                                                                    |

|             |        |                |             |               |                |              | Notes: No notes                                                                                                                           |

| PC_10       | InOut  | н              | PullDown    | none          | none           | VDD_EXT      | Desc: PORTC Position 10   SPI0<br>Master In, Slave Out                                                                                    |

|             |        |                |             |               |                |              | Notes: No notes                                                                                                                           |

| PC_11       | InOut  | А              | PullDown    | none          | none           | VDD_EXT      | Desc: PORTC Position 11   SPI0                                                                                                            |

|             | mout   |                |             | lione         | hone           | 100_00       | Master Out, Slave In   TIMER0<br>Clock                                                                                                    |

|             |        |                |             |               |                |              | Notes: No notes                                                                                                                           |

| PC_12       | InOut  | A              | PullDown    | none          | none           | VDD_EXT      | Desc: PORTC Position 12   ACM0<br>External Trigger n   SMC0<br>Address 25   SPI0 Ready   SPI0<br>Slave Select Output 3<br>Notes: No notes |

| c: 11:      | <b>_</b> | Driver | Int                                 | Reset | Reset |              | Description                                                                                                       |

|-------------|----------|--------|-------------------------------------|-------|-------|--------------|-------------------------------------------------------------------------------------------------------------------|

| Signal Name | Туре     | Туре   | Term                                | Term  | Drive | Power Domain | and Notes                                                                                                         |

| PE_12       | InOut    | A      | PullDown                            | none  | none  | VDD_EXT      | Desc: PORTE Position 12   EPPI0<br>Data 0   SMC0 Data 0   SPI1 Slave<br>Select Output 4   SPI2 Ready              |

|             |          |        |                                     |       |       |              | Notes: No notes                                                                                                   |

| PE_13       | InOut    | A      | PullDown                            | none  | none  | VDD_EXT      | Desc: PORTE Position 13   EPPI0<br>Data 20   SMC0 Memory Select 1<br>  SPI1 Clock                                 |

| DE 44       |          |        |                                     |       |       |              | Notes: No notes                                                                                                   |

| PE_14       | InOut    | A      | PullDown                            | none  | none  | VDD_EXT      | Desc: PORTE Position 14   EPPI0<br>Data 21   SMC0 Byte Enable 0  <br>SPI1 Master In, Slave Out<br>Notes: No notes |

| PE_15       | InOut    | А      | PullDown                            | none  | none  | VDD_EXT      | Desc: PORTE Position 15   EPPI0                                                                                   |

| 12_13       | mout     |        |                                     | none  | none  |              | Data 22   SMC0 Byte Enable 1  <br>SPI1 Master Out, Slave In                                                       |

|             |          |        |                                     |       |       |              | Notes: No notes                                                                                                   |

| PF_00       | InOut    | A      | PullDown                            | none  | none  | VDD_EXT      | Desc: PORTF Position 0   SPI1<br>Slave Select Output 6   TIMER0<br>Timer 6                                        |

|             |          |        |                                     |       |       |              | Notes: No notes                                                                                                   |

| PF_01       | InOut    | A      | PullDown                            | none  | none  | VDD_EXT      | Desc: PORTF Position 1   SPI1<br>Slave Select Output 7   TIMER0<br>Timer 7                                        |

|             |          |        |                                     |       |       |              | Notes: No notes                                                                                                   |

| PF_02       | InOut    | A      | PullDown/<br>Programmable<br>PullUp | none  | none  | VDD_EXT      | Desc: PORTF Position 2   HADC0<br>End of Conversion / Serial Data<br>Out   MSI0 Data 0                            |

|             |          |        |                                     |       |       |              | Notes: No notes                                                                                                   |

| PF_03       | InOut    | A      | PullDown/<br>Programmable<br>PullUp | none  | none  | VDD_EXT      | Desc: PORTF Position 3   HADC0<br>Controls to external multiplexer<br>  MSI0 Data 1                               |

|             |          |        |                                     |       |       |              | Notes: No notes                                                                                                   |

| PF_04       | InOut    | A      | PullDown/<br>Programmable<br>PullUp | none  | none  | VDD_EXT      | Desc: PORTF Position 4   HADC0<br>Controls to external multiplexer<br>  MSI0 Data 2<br>Notes: No notes            |

| PF_05       | InOut    | А      | PullDown/                           | none  | none  | VDD_EXT      | Desc: PORTF Position 5   HADC0                                                                                    |

| FT_05       | mout     |        | Programmable<br>PullUp              | none  | none  |              | Controls to external multiplexer<br>  MSI0 Data 3<br>Notes: No notes                                              |

| PF_06       | InOut    | А      | PullDown/                           | none  | none  | VDD_EXT      | Desc: PORTF Position 6   MSI0                                                                                     |

| PF_00       | mout     | A      | Programmable<br>PullUp              | none  | none  | VDD_EXT      | Data 4   PWM2 Channel A Low<br>Side                                                                               |

|             | InOut    |        |                                     |       |       |              | Notes: No notes                                                                                                   |

| PF_07       | InOut    | A      | PullDown/<br>Programmable<br>PullUp | none  | none  | VDD_EXT      | Desc: PORTF Position 7   MSI0<br>Data 5   PWM2 Channel A High<br>Side                                             |

|             |          |        |                                     |       |       |              | Notes: No notes                                                                                                   |

|             |       | Driver |                                     | Reset | Reset |              | Description                                                                                                                                             |

|-------------|-------|--------|-------------------------------------|-------|-------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Signal Name | Туре  | Туре   | Term                                | Term  | Drive | Power Domain | and Notes                                                                                                                                               |

| PF_08       | InOut | A      | PullDown/<br>Programmable<br>PullUp | none  | none  | VDD_EXT      | Desc: PORTF Position 8   MSI0<br>Data 6   PWM2 Channel B Low<br>Side<br>Notes: No notes                                                                 |

| PF_09       | InOut | A      | PullDown/<br>Programmable<br>PullUp | none  | none  | VDD_EXT      | Desc: PORTF Position 9   MSI0<br>Data 7   PWM2 Channel B High<br>Side                                                                                   |

| PF_10       | InOut | А      | PullDown/<br>Programmable<br>PullUp | none  | none  | VDD_EXT      | Notes: No notes<br>Desc: PORTF Position 10   MSI0<br>Command<br>Notes: No notes                                                                         |

| PF_11       | InOut | A      | PullDown                            | none  | none  | VDD_EXT      | Desc: PORTF Position 11   MSI0<br>Clock<br>Notes: No notes                                                                                              |

| PF_12       | InOut | A      | PullDown                            | none  | none  | VDD_EXT      | Desc: PORTF Position 12   MSI0<br>Card Detect<br>Notes: No notes                                                                                        |

| PF_13       | InOut | A      | PullDown                            | none  | none  | VDD_EXT      | Desc: PORTF Position 13   EMAC<br>Carrier Sense/RMII Receive Data<br>Valid   MSI0 eSDIO Interrupt<br>Input   TRACE0 Trace Data  <br>TRACE0 Trace Data 8 |

| PF_14       | InOut | A      | PullDown                            | none  | none  | VDD_EXT      | Notes: No notes<br>Desc: PORTF Position 14   EMAC <sup>7</sup><br>Management Channel Clock  <br>TRACE0 Trace Data   TRACE0<br>Trace Data 9              |

| PF_15       | InOut | A      | PullDown                            | none  | none  | VDD_EXT      | Notes: No notes<br>Desc: PORTF Position 15   EMAC <sup>7</sup><br>Management Channel Serial<br>Data   TRACE0 Trace Data  <br>TRACE0 Trace Data 10       |

| PG_00       | InOut | A      | PullDown                            | none  | none  | VDD_EXT      | Notes: No notes<br>Desc: PORTG Position 0   EMAC1<br>Reference Clock   TRACE0 Trace<br>Clock                                                            |

| PG_01       | InOut | A      | PullDown                            | none  | none  | VDD_EXT      | Notes: No notes<br>Desc: PORTG Position 1   EMAC1<br>Transmit Enable   TRACE0 Trace<br>Data   TRACE0 Trace Data 11<br>Notes: No notes                   |

| PG_02       | InOut | A      | PullDown                            | none  | none  | VDD_EXT      | Desc: PORTG Position 2   EMAC1<br>Transmit Data 0   TRACE0 Trace<br>Data   TRACE0 Trace Data 12<br>Notes: No notes                                      |

| PG_03       | InOut | A      | PullDown                            | none  | none  | VDD_EXT      | Desc: PORTG Position 3   EMAC1<br>Transmit Data 1   TRACE0 Trace<br>Data   TRACE0 Trace Data 13<br>Notes: No notes                                      |

| Signal Name | Туре  | Driver<br>Type | lnt<br>Term | Reset<br>Term | Reset<br>Drive | Power Domain | Description<br>and Notes                                                                                                     |

|-------------|-------|----------------|-------------|---------------|----------------|--------------|------------------------------------------------------------------------------------------------------------------------------|

| TWI0_SDA    | InOut | D              | none        | none          | none           | VDD_EXT      | Desc: TWI0 Serial Data<br>Notes: Add external pull-up if<br>used. Can be pulled low when<br>not used.                        |

| TWI1_SCL    | InOut | D              | none        | none          | none           | VDD_EXT      | Desc: TWI1 Serial Clock<br>Notes: Add external pull-up if<br>used. Can be pulled low when<br>not used.                       |

| TWI1_SDA    | InOut | D              | none        | none          | none           | VDD_EXT      | Desc: TWI1 Serial Data<br>Notes: Add external pull-up if<br>used. Can be pulled low when<br>not used.                        |

| TWI2_SCL    | InOut | D              | none        | none          | none           | VDD_EXT      | Desc: TWI2 Serial Clock<br>Notes: Add external pull-up if<br>used. Can be pulled low when<br>not used.                       |

| TWI2_SDA    | InOut | D              | none        | none          | none           | VDD_EXT      | Desc: TWI2 Serial Data<br>Notes: Add external pull-up if<br>used. Can be pulled low when<br>not used.                        |

| USB0_DM     | InOut | F              | none        | none          | none           | VDD_USB      | Desc: USB0 Data -<br>Notes: Add external pull-down if<br>not used <sup>1</sup>                                               |

| USB0_DP     | InOut | F              | none        | none          | none           | VDD_USB      | Desc: USB0 Data +<br>Notes: Add external pull-down if<br>not used <sup>1</sup>                                               |

| USB0_ID     | InOut |                | none        | none          | none           | VDD_USB      | Desc: USB0 OTG ID<br>Notes: Connect to GND when<br>USB is not used <sup>1</sup>                                              |

| USB0_VBC    | InOut | E              | none        | none          | none           | VDD_USB      | Desc: USB0 VBUS Control<br>Notes: Add external pull-down if<br>not used <sup>1</sup>                                         |

| USB0_VBUS   | InOut | G              | none        | none          | none           | VDD_USB      | Desc: USB0 Bus Voltage<br>Notes: Connect to GND if not<br>used <sup>1</sup>                                                  |

| USB1_DM     | InOut | F              | none        | none          | none           | VDD_USB      | Desc: USB1 Data -<br>Notes: Add external pull-down if<br>not used <sup>1</sup>                                               |

| USB1_DP     | InOut | F              | none        | none          | none           | VDD_USB      | Desc: USB1 Data +<br>Notes: Add external pull-down if<br>not used <sup>1</sup>                                               |

| USB1_VBUS   | InOut | G              | none        | none          | none           | VDD_USB      | Desc: USB1 Bus Voltage<br>Notes: Connect to GND if not<br>used <sup>1</sup>                                                  |

| USB_CLKIN   | a     |                | none        | none          | none           |              | Desc: USB0/USB1 Clock/Crystal<br>Input<br>Notes: Services both USB0 and<br>USB1. Connect to GND if not<br>used. <sup>1</sup> |

## HADC

## HADC Electrical Characteristics

### Table 37. HADC Electrical Characteristics

| Parameter          | Conditions                           | Тур | Unit |

|--------------------|--------------------------------------|-----|------|

| IDD_HADC_IDLE      | Current consumption on               | 2.0 | mA   |

|                    | V <sub>DD_HADC</sub> .               |     |      |

|                    | HADC is powered on, but not          |     |      |

|                    | converting.                          |     |      |

| IDD_HADC_ACTIVE    | Current consumption on               | 2.5 | mΑ   |

|                    | $V_{DD_{HADC}}$ during a conversion. |     |      |

| IDD_HADC_POWERDOWN | Current consumption on               | 10  | μA   |

|                    | V <sub>DD_HADC</sub> .               |     |      |

|                    | Analog circuitry of the HADC is      |     |      |

|                    | powered down.                        |     |      |

### HADC DC Accuracy

Table 38. HADC DC Accuracy<sup>1</sup>

| Parameter                       | Тур | Unit <sup>2</sup> |

|---------------------------------|-----|-------------------|

| Resolution                      | 12  | Bits              |

| No Missing Codes (NMC)          | 10  | Bits              |

| Integral Nonlinearity (INL)     | ±2  | LSB               |

| Differential Nonlinearity (DNL) | ±2  | LSB               |

| Offset Error                    | ±8  | LSB               |

| Offset Error Matching           | ±10 | LSB               |

| Gain Error                      | ±4  | LSB               |

| Gain Error Matching             | ±4  | LSB               |

<sup>1</sup>See the Operating Conditions section for the HADC0\_VINx specification. <sup>2</sup>LSB = HADC0\_VREFP  $\div$  4096.

### HADC Timing Specifications

#### Table 39. HADC Timing Specifications

| Parameter           | Тур Мах                |     | Unit |

|---------------------|------------------------|-----|------|

| Conversion Time     | $20 \times T_{SAMPLE}$ |     | μs   |

| Throughput Range    |                        | 1   | MSPS |

| T <sub>WAKEUP</sub> |                        | 100 | μs   |

## TMU

#### **TMU Characteristics**

Table 40. TMU Characteristics

| Parameter  | Тур | Unit |

|------------|-----|------|

| Resolution | 1   | °C   |

| Accuracy   | ±6  | °C   |

#### Asynchronous Flash Write

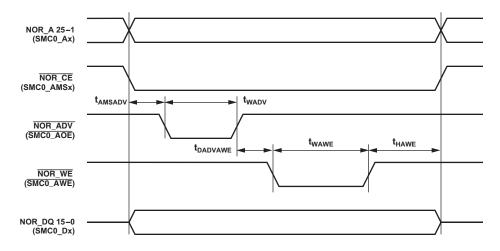

Table 49 and Figure 16 show asynchronous flash memory write timing, related to the SMC.

#### Table 49. Asynchronous Flash Write

| Parameter Switching Characteristics |                                                                  | Min Max                               | Unit |

|-------------------------------------|------------------------------------------------------------------|---------------------------------------|------|

|                                     |                                                                  |                                       |      |

| t <sub>AMSADV</sub>                 | SMC0_Ax/SMC0_AMSx Assertion Before ADV Low <sup>1</sup>          | $PREST \times t_{SCLK0} - 2$          | ns   |

| t <sub>DADVAWE</sub>                | SMC0_AWE Low Delay From ADV High <sup>2</sup>                    | $PREAT \times t_{SCLK0} - 2$          | ns   |

| t <sub>WADV</sub>                   | NR_ADV Active Low Width <sup>3</sup>                             | WST $\times$ t <sub>SCLK0</sub> – 2   | ns   |

| t <sub>HAWE</sub>                   | Output <sup>4</sup> Hold After <u>SMC0_AWE</u> High <sup>5</sup> | WHT $\times$ t <sub>SCLK0</sub> – 3.5 | ns   |

| t <sub>WAWE</sub> 6                 | SMC0_AWE Active Low Width <sup>7</sup>                           | WAT $\times$ t <sub>SCLK0</sub> – 2   | ns   |

<sup>1</sup>PREST value set using the SMC\_BxETIM.PREST bits.

<sup>2</sup>PREAT value set using the SMC\_BxETIM.PREAT bits.

<sup>3</sup>WST value set using the SMC\_BxTIM.WST bits.

<sup>4</sup>Output signals are DATA, SMC0\_Ax, <u>SMC0\_AMSx</u>, <u>SMC0\_ABEx</u>.

<sup>5</sup>WHT value set using the SMC\_BxTIM.WHT bits.

<sup>6</sup>SMC\_BxCTL.ARDYEN bit = 0.

<sup>7</sup>WAT value set using the SMC\_BxTIM.WAT bits.

Figure 16. Asynchronous Flash Write

### All Accesses

Table 50 describes timing that applies to all memory accesses, related to the SMC.

#### Table 50. All Accesses

| Parameter                                  |  | Min                              | Max | Unit |

|--------------------------------------------|--|----------------------------------|-----|------|

| Switching Characteristic                   |  |                                  |     |      |

| t <sub>TURN</sub> SMC0_AMSx Inactive Width |  | $(IT + TT) \times t_{SCLK0} - 2$ |     | ns   |

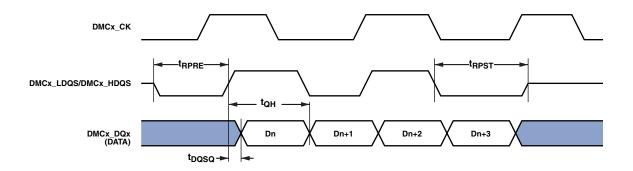

#### Mobile DDR SDRAM Read Cycle Timing

Table 55 and Figure 21 show mobile DDR SDRAM read cycle timing, related to the DMC.

### Table 55. Mobile DDR SDRAM Read Cycle Timing, V<sub>DD\_DMCx</sub> Nominal 1.8 V<sup>1</sup>

|                   |                                                                         |      | 200 MHz <sup>2</sup> |                 |

|-------------------|-------------------------------------------------------------------------|------|----------------------|-----------------|

| Parameter         |                                                                         | Min  | Max                  | Unit            |

| Timing Require    | ements                                                                  |      |                      |                 |

| t <sub>QH</sub>   | DMCx_DQ, DMCx_DQS Output Hold Time From DMCx_DQS                        | 1.75 |                      | ns              |

| t <sub>DQSQ</sub> | DMCx_DQS to DMCx_DQ Skew for DMCx_DQS and Associated<br>DMCx_DQ Signals |      | 0.4                  | ns              |

| t <sub>RPRE</sub> | Read Preamble                                                           | 0.9  | 1.1                  | t <sub>CK</sub> |

| t <sub>RPST</sub> | Read Postamble                                                          | 0.4  | 0.6                  | t <sub>CK</sub> |

<sup>1</sup>Specifications apply to both DMC0 and DMC1.

<sup>2</sup>To ensure proper operation of LPDDR, all the LPDDR guidelines must be strictly followed. See "Interfacing DDR3/DDR2/LPDDR Memory to ADSP-SC5xx/215xx Processors" (EE-387).

Figure 21. Mobile DDR SDRAM Controller Input AC Timing

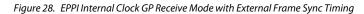

Figure 35. Link Ports—Receive

#### **Example System Hold Time Calculation**

To determine the data output hold time in a particular system, first calculate  $t_{DECAY}$  using the previous equation. Choose  $\Delta V$  to be the difference between the output voltage of the processor and the input threshold for the device requiring the hold time.  $C_L$  is the total bus capacitance (per data line) and  $I_L$  is the total leakage or three-state current (per data line). The hold time will be  $t_{DECAY}$  plus the various output disable times as specified in the Timing Specifications section.

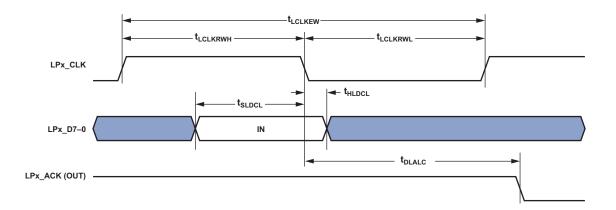

### **Capacitive Loading**

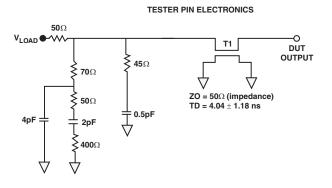

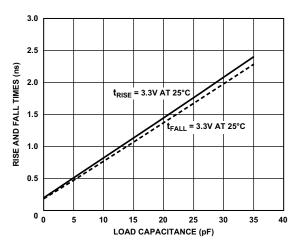

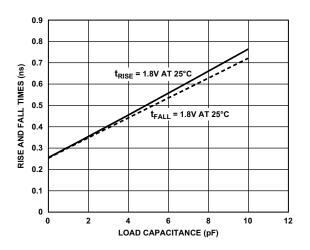

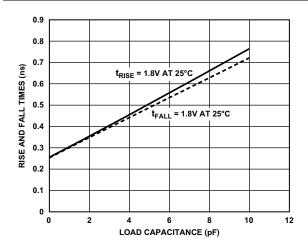

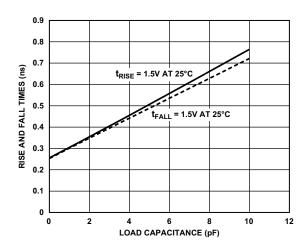

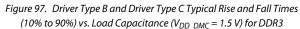

Output delays and holds are based on standard capacitive loads of an average of 6 pF on all balls (see Figure 92).  $V_{LOAD}$  is equal to  $V_{DD\_EXT}/2$ . Figure 93 through Figure 97 show how output rise time varies with capacitance. The delay and hold specifications given must be derated by a factor derived from these figures. The graphs in these figures may not be linear outside the ranges shown.

#### NOTES:

THE WORST CASE TRANSMISSION LINE DELAY IS SHOWN AND CAN BE USED FOR THE OUTPUT TIMING ANALYSIS TO REFELECT THE TRANSMISSION LINE EFFECT AND MUST BE CONSIDERED. THE TRANSMISSION LINE (TD) IS FOR LOAD ONLY AND DOES NOT AFFECT THE DATA SHEET TIMING SPECIFICATIONS.

ANALOG DEVICES RECOMMENDS USING THE IBIS MODEL TIMING FOR A GIVEN SYSTEM REQUIREMENT. IF NECESSARY, A SYSTEM MAY INCORPORATE EXTERNAL DRIVERS TO COMPENSATE FOR ANY TIMING DIFFERENCES.

Figure 92. Equivalent Device Loading for AC Measurements (Includes All Fixtures)

Figure 93. Driver Type A Typical Rise and Fall Times (10% to 90%) vs. Load Capacitance (V<sub>DD EXT</sub> = 3.3 V)

Figure 94. Driver Type H Typical Rise and Fall Times (10% to 90%) vs. Load Capacitance ( $V_{DD_EXT} = 3.3 V$ )

Figure 95. Driver Type B and Driver Type C Typical Rise and Fall Times (10% to 90%) vs. Load Capacitance ( $V_{DD}$  DMC = 1.8 V) for LPDDR

Figure 96. Driver Type B and Driver Type C Typical Rise and Fall Times (10% to 90%) vs. Load Capacitance (V<sub>DD\_DMC</sub> = 1.8 V) for DDR2

### **ENVIRONMENTAL CONDITIONS**

To determine the junction temperature on the application PCB, use the following equation:

$$T_J = T_{CASE} + (\Psi_{JT} \times P_D)$$

where:

$T_J$  = junction temperature (°C).  $T_{CASE}$  = case temperature (°C) measured at top center of package.

$\Psi_{IT}$  = from Table 104 and Table 105.

$P_D$  = power dissipation (see the Total Internal Power Dissipation section for the method to calculate  $P_D$ ).

Values of  $\theta_{JA}$  are provided for package comparison and PCB design considerations.  $\theta_{JA}$  can be used for a first order approximation of  $T_J$  by the following equation:

$$T_J = T_A + (\theta_{JA} \times P_D)$$

where  $T_A$  = ambient temperature (°C).

Values of  $\theta_{JC}$  are provided for package comparison and PCB design considerations when an external heat sink is required.

In Table 104 and Table 105, airflow measurements comply with JEDEC standards JESD51-2 and JESD51-6. The junction to case measurement complies with MIL-STD-883 (Method 1012.1). All measurements use a 6-layer PCB with 101.6 mm  $\times$  152.4 mm dimensions.

Table 104. Thermal Characteristics for 349 CSP\_BGA

| Parameter       | Conditions            | Тур  | Unit |

|-----------------|-----------------------|------|------|

| $\theta_{JA}$   | 0 linear m/s air flow | 13.3 | °C/W |

| $\theta_{JA}$   | 1 linear m/s air flow | 12.1 | °C/W |

| $\theta_{JA}$   | 2 linear m/s air flow | 11.6 | °C/W |

| θ <sub>JC</sub> |                       | 3.65 | °C/W |

| $\Psi_{JT}$     | 0 linear m/s air flow | 0.08 | °C/W |

| $\Psi_{T}$      | 1 linear m/s air flow | 0.12 | °C/W |

| $\Psi_{T}$      | 2 linear m/s air flow | 0.14 | °C/W |

| Table 105. | Thermal | Characteristics | for 529 | CSP_BGA |

|------------|---------|-----------------|---------|---------|

|------------|---------|-----------------|---------|---------|

| Parameter       | Conditions            | Тур  | Unit |  |

|-----------------|-----------------------|------|------|--|

| $\theta_{JA}$   | 0 linear m/s air flow | 13.4 | °C/W |  |

| $\theta_{JA}$   | 1 linear m/s air flow | 12.1 | °C/W |  |

| $\theta_{JA}$   | 2 linear m/s air flow | 11.6 | °C/W |  |

| θ <sub>JC</sub> |                       | 3.63 | °C/W |  |

| TιΨ             | 0 linear m/s air flow | 0.08 | °C/W |  |

| Ψ <sub>JT</sub> | 1 linear m/s air flow | 0.11 | °C/W |  |

| Ψ <sub>JT</sub> | 2 linear m/s air flow | 0.13 | °C/W |  |