Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

E·XFl

| Product Status          | Active                                                                                      |

|-------------------------|---------------------------------------------------------------------------------------------|

| Туре                    | Floating Point                                                                              |

| Interface               | CAN, EBI/EMI, Ethernet, DAI, I <sup>2</sup> C, MMC/SD/SDIO, SPI, SPORT, UART/USART, USB OTG |

| Clock Rate              | 300MHz                                                                                      |

| Non-Volatile Memory     | ROM (512kB)                                                                                 |

| On-Chip RAM             | 384kB                                                                                       |

| Voltage - I/O           | 3.30V                                                                                       |

| Voltage - Core          | 1.10V                                                                                       |

| Operating Temperature   | 0°C ~ 70°C (TA)                                                                             |

| Mounting Type           | Surface Mount                                                                               |

| Package / Case          | 349-LFBGA, CSPBGA                                                                           |

| Supplier Device Package | 349-CSPBGA (19x19)                                                                          |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-sc583kbcz-3a                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Single external reference with analog inputs between 0 V and 3.3 V.

- Selectable ADC clock frequency including the ability to program a prescaler.

- Adaptable conversion type; allows single or continuous conversion with option of autoscan.

- Auto sequencing capability with up to 15 autoconversions in a single session. Each conversion can be programmed to select 1 to 15 input channels.

- 16 data registers (individually addressable) to store conversion values.

### USB 2.0 On the Go (OTG) Dual-Role Device Controller

There are two USB modules + PHY. USB0 supports HS/FS/LS USB 2.0 on the go (OTG) and USB1 supports HS/FS USB 2.0 only and can be programmed to be a host or device.

The USB 2.0 OTG dual-role device controller provides a low cost connectivity solution in industrial applications, as well as consumer mobile devices such as cell phones, digital still cameras, and MP3 players. The USB 2.0 controller allows these devices to transfer data using a point to point USB connection without the need for a PC host. The module can operate in a traditional USB peripheral only mode as well as the host mode presented in the OTG supplement to the USB 2.0 specification.

The USB clock is provided through a dedicated external crystal or crystal oscillator.

The USB OTG dual-role device controller includes a PLL with programmable multipliers to generate the necessary internal clocking frequency for the USB.

#### Media Local Bus (MLB)

The automotive model has a media local bus (MLB) slave interface that allows the processors to function as a media local bus device. It includes support for both 3-pin and 6-pin media local bus protocols. The MLB 3-pin configuration supports speeds up to  $1024 \times FS$ . The MLB 6-pin configuration supports speed of  $4096 \times FS$ . The MLB also supports up to 63 logical channels with up to 468 bytes of data per MLB frame.

The MLB interface supports MOST25/MOST50/MOST150 data rates and operates in slave mode only.

#### 2-Wire Controller Interface (TWI)

The processors include three 2-wire interface (TWI) modules that provide a simple exchange method of control data between multiple devices. The TWI module is compatible with the widely used I<sup>2</sup>C bus standard. The TWI module offers the capabilities of simultaneous master and slave operation and support for both 7-bit addressing and multimedia data arbitration. The TWI interface utilizes two pins for transferring clock (TWI\_SCL) and data (TWI\_SDA) and supports the protocol at speeds up to 400 kb/sec. The TWI interface pins are compatible with 5 V logic levels.

Additionally, the TWI module is fully compatible with serial camera control bus (SCCB) functionality for easier control of various CMOS camera sensor devices.

#### General-Purpose I/O (GPIO)

Each general-purpose port pin can be individually controlled by manipulating the port control, status, and interrupt registers:

- GPIO direction control register specifies the direction of each individual GPIO pin as input or output.

- GPIO control and status registers have a write one to modify mechanism that allows any combination of individual GPIO pins to be modified in a single instruction, without affecting the level of any other GPIO pins.

- GPIO interrupt mask registers allow each individual GPIO pin to function as an interrupt to the processors. GPIO pins defined as inputs can be configured to generate hardware interrupts, while output pins can be triggered by software interrupts.

- GPIO interrupt sensitivity registers specify whether individual pins are level or edge sensitive and specify, if edge sensitive, whether the rising edge or both the rising and falling edges of the signal are significant.

### Pin Interrupts

Every port pin on the processors can request interrupts in either an edge sensitive or a level sensitive manner with programmable polarity. Interrupt functionality is decoupled from GPIO operation. Six system-level interrupt channels (PINT0–PINT5) are reserved for this purpose. Each of these interrupt channels can manage up to 32 interrupt pins. The assignment from pin to interrupt is not performed on a pin by pin basis. Rather, groups of eight pins (half ports) can be flexibly assigned to interrupt channels.

Every pin interrupt channel features a special set of 32-bit memory-mapped registers that enable half-port assignment and interrupt management. This includes masking, identification, and clearing of requests. These registers also enable access to the respective pin states and use of the interrupt latches, regardless of whether the interrupt is masked or not. Most control registers feature multiple MMR address entries to write-one-to-set or write-one-to-clear them individually.

### Mobile Storage Interface (MSI)

The mobile storage interface (MSI) controller acts as the host interface for multimedia cards (MMC), secure digital memory cards (SD), and secure digital input/output cards (SDIO). The MSI controller has the following features:

- Support for a single MMC, SD memory, and SDIO card

- Support for 1-bit and 4-bit SD modes

- Support for 1-bit, 4-bit, and 8-bit MMC modes

- Support for eMMC 4.3 embedded NAND flash devices

- An eleven-signal external interface with clock, command, optional interrupt, and up to eight data lines

- Integrated DMA controller

- Card interface clock generation in the clock distribution unit (CDU)

- SDIO interrupt and read wait features

| Signal Name   | Direction | Description                                                                                                                                                                                                                                               |

|---------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMC_ABE[n]    | Output    | Byte Enable n. Indicates whether the lower or upper byte of a memory is being accessed. When an                                                                                                                                                           |

|               |           | asynchronous write is made to the upper byte of a 16-bit memory, $\overline{SMC}ABE1 = 0$ and $\overline{SMC}ABE0 = 1$ . When an asynchronous write is made to the lower byte of a 16-bit memory, $\overline{SMC}ABE1 = 1$ and $\overline{SMC}ABE0 = 0$ . |

| SMC_AMS[n]    | Output    | Memory Select n. Typically connects to the chip select of a memory device.                                                                                                                                                                                |

| SMC_AOE       | Output    | Output Enable. Asserts at the beginning of the setup period of a read access.                                                                                                                                                                             |

| SMC_ARDY      | Input     | <b>Asynchronous Ready.</b> Flow control signal used by memory devices to indicate to the SMC when further transactions may proceed.                                                                                                                       |

| SMC_ARE       | Output    | Read Enable. Asserts at the beginning of a read access.                                                                                                                                                                                                   |

| SMC_AWE       | Output    | Write Enable. Asserts for the duration of a write access period.                                                                                                                                                                                          |

| SMC_A[nn]     | Output    | Address n. Address bus.                                                                                                                                                                                                                                   |

| SMC_D[nn]     | InOut     | Data n. Bidirectional data bus.                                                                                                                                                                                                                           |

| SPI_CLK       | InOut     | Clock. Input in slave mode, output in master mode.                                                                                                                                                                                                        |

| SPI_D2        | InOut     | Data 2. Transfers serial data in quad mode. Open-drain when ODM mode is enabled.                                                                                                                                                                          |

| SPI_D3        | InOut     | Data 3. Transfers serial data in quad mode. Open-drain when ODM mode is enabled.                                                                                                                                                                          |

| SPI_MISO      | InOut     | <b>Master In, Slave Out.</b> Transfers serial data. Operates in the same direction as SPI_MOSI in dual and quad modes. Open-drain when ODM mode is enabled.                                                                                               |

| SPI_MOSI      | InOut     | <b>Master Out, Slave In.</b> Transfers serial data. Operates in the same direction as SPI_MISO in dual and quad modes. Open-drain when ODM mode is enabled.                                                                                               |

| SPI_RDY       | InOut     | Ready. Optional flow signal. Output in slave mode, input in master mode.                                                                                                                                                                                  |

| SPI_SEL[n]    | Output    | Slave Select Output n. Used in master mode to enable the desired slave.                                                                                                                                                                                   |

| <u>SPI_SS</u> | Input     | Slave Select Input.<br>Slave mode—acts as the slave select input.<br>Master mode—optionally serves as an error detection input for the SPI when there are multiple<br>masters.                                                                            |

| SPT_ACLK      | InOut     | <b>Channel A Clock.</b> Data and frame sync are driven/sampled with respect to this clock. This signal can be either internally or externally generated.                                                                                                  |

| SPT_AD0       | InOut     | <b>Channel A Data 0.</b> Primary bidirectional data I/O. This signal can be configured as an output to transmit serial data or as an input to receive serial data.                                                                                        |

| SPT_AD1       | InOut     | <b>Channel A Data 1.</b> Secondary bidirectional data I/O. This signal can be configured as an output to transmit serial data or as an input to receive serial data.                                                                                      |

| SPT_AFS       | InOut     | <b>Channel A Frame Sync.</b> The frame sync pulse initiates shifting of the serial data. This signal is either generated internally or externally.                                                                                                        |

| SPT_ATDV      | Output    | <b>Channel A Transmit Data Valid.</b> This signal is optional and only active when SPORT is configured in multichannel transmit mode. It is asserted during enabled slots.                                                                                |

| SPT_BCLK      | InOut     | <b>Channel B Clock.</b> Data and frame sync are driven/sampled with respect to this clock. This signal can be either internally or externally generated.                                                                                                  |

| SPT_BD0       | InOut     | <b>Channel B Data 0.</b> Primary bidirectional data I/O. This signal can be configured as an output to transmit serial data or as an input to receive serial data.                                                                                        |

| SPT_BD1       | InOut     | <b>Channel B Data 1.</b> Secondary bidirectional data I/O. This signal can be configured as an output to transmit serial data or as an input to receive serial data.                                                                                      |

| SPT_BFS       | InOut     | <b>Channel B Frame Sync.</b> The frame sync pulse initiates shifting of serial data. This signal is either generated internally or externally.                                                                                                            |

| SPT_BTDV      | Output    | <b>Channel B Transmit Data Valid.</b> This signal is optional and only active when SPORT is configured in multichannel transmit mode. It is asserted during enabled slots.                                                                                |

| SYS_BMODE[n]  | Input     | Boot Mode Control n. Selects the boot mode of the processor.                                                                                                                                                                                              |

| SYS_CLKIN0    | Input     | Clock/Crystal Input.                                                                                                                                                                                                                                      |

| SYS_CLKIN1    | Input     | Clock/Crystal Input.                                                                                                                                                                                                                                      |

| SYS_CLKOUT    | Output    | <b>Processor Clock Output.</b> Outputs internal clocks. Clocks may be divided down. See the CGU chapter of the ADSP-SC58x/ADSP-2158x SHARC+ Processor Hardware Reference for more details.                                                                |

### Table 11. ADSP-SC58x/ADSP-2158x Detailed Signal Descriptions (Continued)

| Signal Name            | Description                                | Port      | Pin Name       |

|------------------------|--------------------------------------------|-----------|----------------|

| PWM2_DL                | PWM2 Channel D Low Side                    | E         | PE_10          |

| PWM2_SYNC              | PWM2 PWMTMR Grouped                        | E         | PE_05          |

| PWM2_TRIP0             | PWM2 Shutdown Input 0                      | D         | PD_14          |

| GND                    | Ground                                     | Not Muxed | GND            |

| VDD_EXT                | External Voltage Domain                    | Not Muxed | VDD_EXT        |

| VDD_INT                | Internal Voltage Domain                    | Not Muxed | VDD_INT        |

| SINC0_CLK0             | SINC0 Clock 0                              | В         | PB_01          |

| SINC0_D0               | SINC0 Data 0                               | А         | PA_14          |

| SINC0_D1               | SINC0 Data 1                               | А         | PA_15          |

| SINC0_D2               | SINC0 Data 2                               | В         | PB_00          |

| SINC0_D3               | SINC0 Data 3                               | В         | PB_04          |

| SMC0_A01               | SMC0 Address 1                             | В         | PB_05          |

| 5MC0_A02               | SMC0 Address 2                             | В         | PB_06          |

| SMC0_A03               | SMC0 Address 3                             | В         | PB_03          |

| SMC0_A04               | SMC0 Address 4                             | В         | PB_02          |

| SMC0_A05               | SMC0 Address 5                             | D         | PD_13          |

| SMC0_A06               | SMC0 Address 6                             | D         | PD_12          |

|                        | SMC0 Address 7                             | В         | <br>PB_01      |

|                        | SMC0 Address 8                             | В         | <br>PB_00      |

| SMC0_A09               | SMC0 Address 9                             | A         | PA_15          |

| SMC0_A10               | SMC0 Address 10                            | А         | <br>PA_14      |

| SMC0_A11               | SMC0 Address 11                            | A         | PA_09          |

| 5MC0_A12               | SMC0 Address 12                            | A         | PA_08          |

| 5MC0_A13               | SMC0 Address 13                            | A         | PA_13          |

| 5MC0_A14               | SMC0 Address 14                            | A         | PA_12          |

| SMC0_A15               | SMC0 Address 15                            | A         | PA_11          |

| 5MC0_A16               | SMC0 Address 16                            | A         | PA_07          |

| 5MC0_A17               | SMC0 Address 17                            | A         | PA_06          |

| 5MC0_A18               | SMC0 Address 18                            | A         | PA_05          |

| 5MC0_A19               | SMC0 Address 19                            | A         | PA_04          |

| 5MC0_A20               | SMC0 Address 20                            | A         | PA_01          |

| 5MC0_A21               | SMC0 Address 21                            | A         | PA_00          |

| 5MC0_A21               | SMC0 Address 22                            | A         | PA_10          |

| 5MC0_A22               | SMC0 Address 22                            |           | PA_03          |

| 5MC0_A23<br>5MC0_A24   | SMC0 Address 23                            | A         | PA_02          |

| SMC0_A24<br>SMC0_A25   | SMC0 Address 24                            | C         | PC_12          |

| SMC0_A25               | SMC0 Address 25<br>SMC0 Byte Enable 0      | E         | PC_12<br>PE_14 |

| SMC0_ABE1              | SMC0 Byte Enable 0                         |           | PE_14<br>PE_15 |

| SMC0_ABET              | SMC0 Byte Enable 1<br>SMC0 Memory Select 0 | E         | PC_15          |

| SMC0_AMS0<br>SMC0_AMS1 |                                            | C         |                |

|                        | SMC0 Memory Select 1                       | E         | PE_13          |

| SMC0_AMS2              | SMC0 Memory Select 2                       | С         | PC_07          |

| SMC0_AMS3              | SMC0 Memory Select 3                       | C         | PC_08          |

| SMC0_AOE               | SMC0 Output Enable                         | D         | PD_01          |

| SMC0_ARDY              | SMC0 Asynchronous Ready                    | В         | PB_04          |

| SMC0_ARE               | SMC0 Read Enable                           | C         | PC_00          |

| SMC0_AWE               | SMC0 Write Enable                          | В         | PB_15          |

| SMC0_D00               | SMC0 Data 0                                | E         | PE_12          |

| SMC0_D01               | SMC0 Data 1                                | E         | PE_11          |

Table 12. ADSP-SC58x/ADSP-2158x 349-Ball CSP\_BGA Signal Descriptions (Continued)

|             | Multiplexed | Multiplexed | Multiplexed | Multiplexed | Multiplexed               |

|-------------|-------------|-------------|-------------|-------------|---------------------------|

| Signal Name | Function 0  | Function 1  | Function 2  | Function 3  | <b>Function Input Tap</b> |

| PE_00       | PPI0_D09    | PWM2_CL     |             | SMC0_D04    |                           |

| PE_01       | PPI0_FS2    | SPI0_SEL5   | UART1_CTS   | C1_FLG0     |                           |

| PE_02       | PPI0_FS1    | SPI0_SEL6   | UART1_RTS   | C2_FLG0     |                           |

| PE_03       | PPI0_CLK    | SPI0_SEL7   | SPI2_SEL2   | C1_FLG1     |                           |

| PE_04       | PPI0_D08    | PWM2_DH     | SPI2_SEL3   | C2_FLG1     |                           |

| PE_05       | PPI0_D07    | PWM2_SYNC   | SPI2_SEL4   | C1_FLG2     |                           |

| PE_06       | PPI0_D06    |             | SPI2_SEL5   | C2_FLG2     |                           |

| PE_07       | PPI0_D05    |             | SPI1_SEL2   | C1_FLG3     |                           |

| PE_08       | PPI0_D04    | SPI1_SEL5   | SPI1_RDY    | C2_FLG3     |                           |

| PE_09       | PPI0_D03    | PWM0_SYNC   | TM0_TMR0    | SMC0_D03    |                           |

| PE_10       | PPI0_D02    | PWM2_DL     | UART2_RTS   | SMC0_D02    |                           |

| PE_11       | PPI0_D01    | SPI1_SEL3   | UART2_CTS   | SMC0_D01    | SPI1_SS                   |

| PE_12       | PPI0_D00    | SPI1_SEL4   | SPI2_RDY    | SMC0_D00    |                           |

| PE_13       | SPI1_CLK    |             | PPI0_D20    | SMC0_AMS1   |                           |

| PE_14       | SPI1_MISO   |             | PPI0_D21    | SMC0_ABE0   |                           |

| PE_15       | SPI1_MOSI   |             | PPI0_D22    | SMC0_ABE1   |                           |

Table 17. Signal Multiplexing for Port E

Table 18 shows the internal timer signal routing. This table applies to both the 349-ball and 529-ball CSP\_BGA packages.

#### Table 18. Internal Timer Signal Routing

| Timer Input Signal | Internal Source |  |

|--------------------|-----------------|--|

| TM0_ACLK0          | SYS_CLKIN1      |  |

| TM0_ACI5           | DAI0_CRS_PB04_O |  |

| TM0_ACLK5          | DAI0_CRS_PB03_O |  |

| TM0_ACI6           | DAI1_CRS_PB04_O |  |

| TM0_ACLK6          | DAI1_CRS_PB03_O |  |

| TM0_ACI7           | CNT0_TO         |  |

| TM0_ACLK7          | SYS_CLKIN0      |  |

| Signal Name | Description            | Port      | Pin Name    |

|-------------|------------------------|-----------|-------------|

| VDD_PCIE    | PCIE Supply Voltage    | Not Muxed | VDD_PCIE    |

| VDD_PCIE_RX | PCIE RX Supply Voltage | Not Muxed | VDD_PCIE_RX |

| VDD_PCIE_TX | PCIE TX Supply Voltage | Not Muxed | VDD_PCIE_TX |

| VDD_RTC     | RTC VDD                | Not Muxed | VDD_RTC     |

| VDD_USB     | USB VDD                | Not Muxed | VDD_USB     |

Table 19. ADSP-SC58x/ADSP-2158x 529-Ball CSP\_BGA Signal Descriptions (Continued)

### **GPIO MULTIPLEXING FOR THE 529-BALL CSP\_BGA PACKAGE**

Table 20 through Table 26 identify the pin functions that are multiplexed on the general-purpose I/O pins of the 529-ball CSP\_BGA package.

### Table 20. Signal Multiplexing for Port A

|             | Multiplexed       | Multiplexed | Multiplexed | Multiplexed | Multiplexed        |

|-------------|-------------------|-------------|-------------|-------------|--------------------|

| Signal Name | Function 0        | Function 1  | Function2   | Function 3  | Function Input Tap |

| PA_00       | ETH0_TXD0         |             |             | SMC0_A21    |                    |

| PA_01       | ETH0_TXD1         |             |             | SMC0_A20    |                    |

| PA_02       | ETH0_MDC          |             |             | SMC0_A24    |                    |

| PA_03       | ETH0_MDIO         |             |             | SMC0_A23    |                    |

| PA_04       | ETH0_RXD0         |             |             | SMC0_A19    |                    |

| PA_05       | ETH0_RXD1         |             |             | SMC0_A18    |                    |

| PA_06       | ETH0_RXCLK_REFCLK |             |             | SMC0_A17    |                    |

| PA_07       | ETH0_CRS          |             |             | SMC0_A16    |                    |

| PA_08       | ETH0_RXD2         |             |             | SMC0_A12    |                    |

| PA_09       | ETH0_RXD3         |             |             | SMC0_A11    |                    |

| PA_10       | ETH0_TXEN         |             |             | SMC0_A22    |                    |

| PA_11       | ETH0_TXCLK        |             |             | SMC0_A15    |                    |

| PA_12       | ETH0_TXD2         |             |             | SMC0_A14    |                    |

| PA_13       | ETH0_TXD3         |             |             | SMC0_A13    |                    |

| PA_14       | ETH0_PTPPPS3      | SINC0_D0    |             | SMC0_A10    |                    |

| PA_15       | ETH0_PTPPPS2      | SINC0_D1    |             | SMC0_A09    |                    |

#### Table 21. Signal Multiplexing for Port B

|             | Multiplexed    | Multiplexed | Multiplexed | Multiplexed | Multiplexed               |

|-------------|----------------|-------------|-------------|-------------|---------------------------|

| Signal Name | Function 0     | Function 1  | Function 2  | Function 3  | <b>Function Input Tap</b> |

| PB_00       | ETH0_PTPPPS1   | SINC0_D2    | PPI0_D14    | SMC0_A08    | TM0_ACLK3                 |

| PB_01       | ETH0_PTPPPS0   | SINC0_CLK0  | PPI0_D15    | SMC0_A07    | TM0_ACLK4                 |

| PB_02       | ETH0_PTPCLKIN0 | UART1_TX    | PPI0_D16    | SMC0_A04    |                           |

| PB_03       | ETH0_PTPAUXIN0 | UART1_RX    | PPI0_D17    | SMC0_A03    | TM0_ACI1                  |

| PB_04       | MLB0_CLK       | SINC0_D3    | PPI0_D12    | SMC0_ARDY   | ETH0_PTPAUXIN1            |

| PB_05       | MLB0_SIG       |             | PPI0_D13    | SMC0_A01    | ETH0_PTPAUXIN2            |

| PB_06       | MLB0_DAT       |             | PWM0_BH     | SMC0_A02    | ETH0_PTPAUXIN3            |

| PB_07       | LP1_D0         | PWM0_AH     | TM0_TMR3    | SMC0_D15    |                           |

| PB_08       | LP1_D1         | PWM0_AL     | TM0_TMR4    | SMC0_D14    |                           |

| PB_09       | LP1_D2         |             | CAN1_TX     | SMC0_D13    |                           |

| PB_10       | LP1_D3         | TM0_TMR2    | CAN1_RX     | SMC0_D12    | TM0_ACI4                  |

| PB_11       | LP1_D4         |             | PWM0_DH     | SMC0_D11    | CNT0_ZM                   |

| PB_12       | LP1_D5         |             | PWM0_DL     | SMC0_D10    | CNT0_UD                   |

| PB_13       | LP1_D6         |             | PWM0_CH     | SMC0_D09    |                           |

| PB_14       | LP1_D7         | TM0_TMR5    | PWM0_CL     | SMC0_D08    | CNT0_DG                   |

| PB_15       | LP1_ACK        | PWM0_TRIP0  | TM0_TMR1    | SMC0_AWE    |                           |

|             | Multiplexed | Multiplexed | Multiplexed | Multiplexed | Multiplexed               |

|-------------|-------------|-------------|-------------|-------------|---------------------------|

| Signal Name | Function 0  | Function 1  | Function 2  | Function 3  | <b>Function Input Tap</b> |

| PC_00       | LP1_CLK     | PWM0_BL     | SPI0_SEL4   | SMC0_ARE    |                           |

| PC_01       | SPI2_CLK    |             |             |             |                           |

| PC_02       | SPI2_MISO   |             |             |             |                           |

| PC_03       | SPI2_MOSI   |             |             |             |                           |

| PC_04       | SPI2_D2     |             |             |             |                           |

| PC_05       | SPI2_D3     |             |             |             |                           |

| PC_06       | SPI2_SEL1   |             |             |             | SPI2_SS                   |

| PC_07       | CAN0_RX     | SPI0_SEL1   |             | SMC0_AMS2   | TM0_ACI3                  |

| PC_08       | CAN0_TX     |             |             | SMC0_AMS3   |                           |

| PC_09       | SPI0_CLK    |             |             |             |                           |

| PC_10       | SPI0_MISO   |             |             |             |                           |

| PC_11       | SPI0_MOSI   |             |             |             | TM0_CLK                   |

| PC_12       | SPI0_SEL3   | SPI0_RDY    | ACM0_T0     | SMC0_A25    |                           |

| PC_13       | UART0_TX    | SPI1_SEL1   | ACM0_A0     |             |                           |

| PC_14       | UART0_RX    |             | ACM0_A1     |             | TM0_ACI0                  |

| PC_15       | UART0_RTS   | PPI0_FS3    | ACM0_A2     | SMC0_AMS0   |                           |

Table 22. Signal Multiplexing for Port C

### Table 23. Signal Multiplexing for Port D

|             | Multiplexed | Multiplexed | Multiplexed | Multiplexed | Multiplexed        |

|-------------|-------------|-------------|-------------|-------------|--------------------|

| Signal Name | Function 0  | Function 1  | Function 2  | Function 3  | Function Input Tap |

| PD_00       | UART0_CTS   | PPI0_D23    | ACM0_A3     | SMC0_D07    |                    |

| PD_01       | SPI0_SEL2   |             | ACM0_A4     | SMC0_AOE    | SPI0_SS            |

| PD_02       | LP0_D0      | PWM1_TRIP0  | TRACE0_D00  |             |                    |

| PD_03       | LP0_D1      | PWM1_AH     | TRACE0_D01  |             |                    |

| PD_04       | LP0_D2      | PWM1_AL     | TRACE0_D02  |             |                    |

| PD_05       | LP0_D3      | PWM1_BH     | TRACE0_D03  |             |                    |

| PD_06       | LP0_D4      | PWM1_BL     | TRACE0_D04  |             |                    |

| PD_07       | LP0_D5      | PWM1_CH     | TRACE0_D05  |             |                    |

| PD_08       | LP0_D6      | PWM1_CL     | TRACE0_D06  |             | TM0_ACLK1          |

| PD_09       | LP0_D7      | PWM1_DH     | TRACE0_D07  |             | TM0_ACLK2          |

| PD_10       | LP0_CLK     | PWM1_DL     | TRACE0_CLK  |             |                    |

| PD_11       | LP0_ACK     | PWM1_SYNC   |             |             |                    |

| PD_12       | UART2_TX    |             | PPI0_D19    | SMC0_A06    |                    |

| PD_13       | UART2_RX    |             | PPI0_D18    | SMC0_A05    | TM0_ACI2           |

| PD_14       | PPI0_D11    | PWM2_TRIP0  | MLB0_CLKOUT | SMC0_D06    |                    |

| PD_15       | PPI0_D10    | PWM2_CH     |             | SMC0_D05    |                    |

### Table 24. Signal Multiplexing for Port E

|             | Multiplexed | Multiplexed | Multiplexed | Multiplexed | Multiplexed        |

|-------------|-------------|-------------|-------------|-------------|--------------------|

| Signal Name | Function 0  | Function 1  | Function 2  | Function 3  | Function Input Tap |

| PE_00       | PPI0_D09    | PWM2_CL     |             | SMC0_D04    |                    |

| PE_01       | PPI0_FS2    | SPI0_SEL5   | UART1_CTS   | C1_FLG0     |                    |

| PE_02       | PPI0_FS1    | SPI0_SEL6   | UART1_RTS   | C2_FLG0     |                    |

### ADSP-SC58X/ADSP-2158X DESIGNER QUICK REFERENCE

Table 27 provides a quick reference summary of pin related information for circuit board design. The columns in this table provide the following information:

- The signal name column includes the signal name for every pin and the GPIO multiplexed pin function, where applicable.

- The type column identifies the I/O type or supply type of the pin. The abbreviations used in this column are a (analog), s (supply), g (ground) and Input, Output, and InOut.

- The driver type column identifies the driver type used by the corresponding pin. The driver types are defined in the Output Drive Currents section of this data sheet.

- The int term column specifies the termination present when the processor is not in the reset state.

- The reset term column specifies the termination present when the processor is in the reset state.

- The reset drive column specifies the active drive on the signal when the processor is in the reset state.

- The power domain column specifies the power supply domain in which the signal resides.

- The description and notes column identifies any special requirements or characteristics for a signal. These recommendations apply whether or not the hardware block associated with the signal is featured on the product. If no special requirements are listed, the signal can be left unconnected if it is not used. For multiplexed general-purpose I/O pins, this column identifies the functions available on the pin.

|             |       | Driver | Int      | Reset | Reset |              | Description       |

|-------------|-------|--------|----------|-------|-------|--------------|-------------------|

| Signal Name | Туре  | Туре   | Term     | Term  | Drive | Power Domain | and Notes         |

| DAI0_PIN01  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI0 Pin 1  |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI0_PIN02  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI0 Pin 2  |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI0_PIN03  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI0 Pin 3  |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI0_PIN04  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI0 Pin 4  |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI0_PIN05  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI0 Pin 5  |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI0_PIN06  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI0 Pin 6  |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI0_PIN07  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI0 Pin 7  |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI0_PIN08  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI0 Pin 8  |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI0_PIN09  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI0 Pin 9  |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI0_PIN10  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI0 Pin 10 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI0_PIN11  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI0 Pin 11 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI0_PIN12  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI0 Pin 12 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI0_PIN13  | InOut | A      | PullDown | none  | none  | VDD_EXT      | Desc: DAI0 Pin 13 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI0_PIN14  | InOut | A      | PullDown | none  | none  | VDD_EXT      | Desc: DAI0 Pin 14 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI0_PIN15  | InOut | A      | PullDown | none  | none  | VDD_EXT      | Desc: DAI0 Pin 15 |

|             |       |        |          |       |       |              | Notes: No notes   |

#### Table 27. ADSP-SC58x/ADSP-2158x Designer Quick Reference

|                                   |                                     |                                                                                                                                                                                                                                                                                                                                                    |     | 450 N | lHz                                                                                                 |      |

|-----------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|-----------------------------------------------------------------------------------------------------|------|

| Parameter                         |                                     | Conditions                                                                                                                                                                                                                                                                                                                                         | Min | Тур   | Max                                                                                                 | Unit |

| I <sub>DD_IDLE</sub>              | V <sub>DD_INT</sub> Current in Idle | $\label{eq:fcclk} \begin{aligned} f_{CCLK} &= 450 \text{ MHz} \\ ASF_{SHARC1} &= 0.31 \\ ASF_{SHARC2} &= 0.31 \\ ASF_{A5} &= 0.29 \\ f_{SYSCLK} &= 225 \text{ MHz} \\ f_{SCLK0/1} &= 112.5 \text{ MHz} \\ (Other clocks are disabled) \\ No peripheral or DMA activity \\ T_J &= 25^{\circ}\text{C} \\ V_{DD\_INT} &= 1.1 \text{ V} \end{aligned}$ |     | 495   |                                                                                                     | mA   |

| I <sub>DD_TYP</sub>               | V <sub>DD_INT</sub> Current         | $f_{CCLK} = 450 \text{ MHz}$ $ASF_{SHARC1} = 1.0$ $ASF_{SHARC2} = 1.0$ $ASF_{AS} = 0.73$ $f_{SYSCLK} = 225 \text{ MHz}$ $f_{SCLK0/1} = 112.5 \text{ MHz}$ (Other clocks are disabled) FFT accelerator operating at f_{SYSCLK/4} DMA data rate = 600 MB/s $T_J = 25^{\circ}C$ $V_{DDINT} = 1.1 \text{ V}$                                           |     | 1112  |                                                                                                     | mA   |

| I <sub>DD_INT</sub> <sup>11</sup> | V <sub>DD_INT</sub> Current         | $f_{CCLK} > 0 \text{ MHz}$<br>$f_{SCLK0/1} \ge 0 \text{ MHz}$                                                                                                                                                                                                                                                                                      |     |       | See I <sub>DD_INT_TOT</sub><br>equation in the<br>Total Internal<br>Power Dissi-<br>pation section. |      |

<sup>1</sup>Applies to all output and bidirectional pins except TWI, DMC, USB, PCIe, and MLB.

<sup>2</sup>See the Output Drive Currents section for typical drive current capabilities.

<sup>3</sup>Applies to all DMC output and bidirectional signals in DDR2 mode.

<sup>4</sup>Applies to all DMC output and bidirectional signals in DDR3 mode.

<sup>5</sup> Applies to all DMC output and bidirectional signals in LPDDR mode.

<sup>6</sup>Applies to input pins SYS\_BMODE0-2, SYS\_CLKIN0, SYS\_CLKIN1, <u>SYS\_HWRST</u>, JTG\_TDI, JTG\_TMS, and USB0\_CLKIN.

<sup>7</sup> Applies to input pins with internal pull-ups including JTG\_TDI, JTG\_TMS, and JTG\_TCK. <sup>8</sup> Applies to signals JTAG\_TRST, USB0\_VBUS, USB1\_VBUS.

<sup>9</sup> Applies to signals PA0-15, PB0-15, PC0-15, PD0-15, PE0-15, PG0-5, DAI0\_PINx, DAI1\_PINx, DMC0\_DQx, DMC0\_LDQS, DMC0\_UDQS, DMC0\_LDQS, DMC0\_LDQS, DMC0\_LDQS, DMC0\_LDQS, SYS\_FAULT, JTG\_TDO, USB0\_ID, USBx\_DP, and USBx\_VBC.

<sup>10</sup>Applies to all signal pins.

<sup>11</sup>See "Estimating Power for ADSP-SC58x/2158x SHARC+ Processors" (EE-392) for further information.

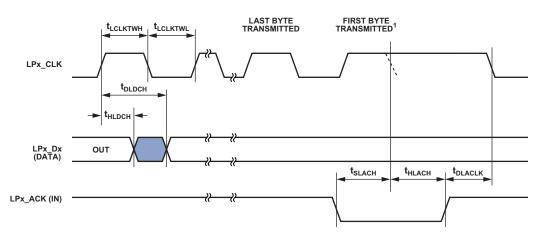

Figure 35. Link Ports—Receive

#### Table 63. Link Ports—Transmit<sup>1</sup>

| Parameter                         |                                      | Min                            | Мах                                            | Unit |

|-----------------------------------|--------------------------------------|--------------------------------|------------------------------------------------|------|

| Timing Require                    | ements                               |                                |                                                |      |

| t <sub>SLACH</sub>                | LPx_ACK Setup Before LPx_CLK Low     | $2 \times t_{CLKO8} + 13.5$    |                                                | ns   |

| t <sub>HLACH</sub>                | LPx_ACK Hold After LPx_CLK Low       | -5.5                           |                                                | ns   |

| Switching Cha                     | racteristics                         |                                |                                                |      |

| t <sub>DLDCH</sub>                | Data Delay After LPx_CLK High        |                                | 1.6                                            | ns   |

| t <sub>HLDCH</sub>                | Data Hold After LPx_CLK High         | -0.8                           |                                                | ns   |

| t <sub>LCLKTWL</sub> <sup>2</sup> | LPx_CLK Width Low                    | $0.33 \times t_{LCLKTPROG}$    | $0.6 \times t_{LCLKTPROG}$                     | ns   |

| t <sub>LCLKTWH</sub> 2            | LPx_CLK Width High                   | $0.45 \times t_{LCLKTPROG}$    | $0.66 \times t_{LCLKTPROG}$                    | ns   |

| t <sub>LCLKTW</sub> <sup>2</sup>  | LPx_CLK Period                       | $N \times t_{LCLKTPROG} - 0.5$ |                                                | ns   |

| t <sub>DLACLK</sub>               | LPx_CLK Low Delay After LPx_ACK High | t <sub>CLKO8</sub> + 4         | $2 \times t_{CLKO8} + 1 \times t_{LPCLK} + 10$ | ns   |

<sup>1</sup>Specifications apply to LP0 and LP1.

$^2$  See Table 29 for details on the minimum period that can be programmed for t<sub>LCLKTPROG</sub>.

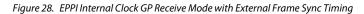

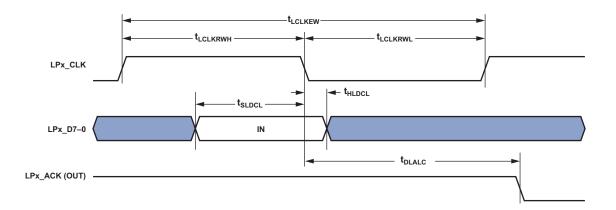

The t<sub>sLACH</sub> and t<sub>HLACH</sub> specifications apply only to the LPx\_CLK falling edge. If these specifications are met, LPx\_CLK would extend and the dotted LPx\_CLK falling edge would not occur as shown. The position of the dotted falling edge can be calculated using the t<sub>LCLKTWH</sub> specification. t<sub>LCLKTWH</sub> Min should be used for t<sub>sLACH</sub> and t<sub>LCLKTWH</sub> Max for t<sub>HLACH</sub>.

Figure 36. Link Ports—Transmit

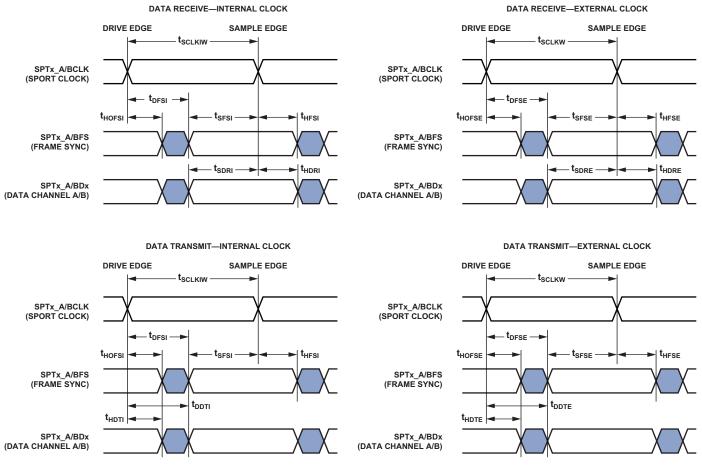

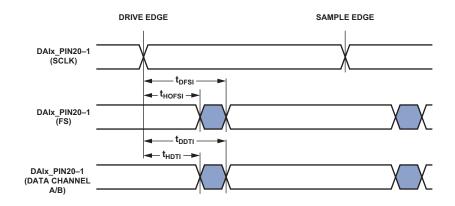

### Table 65. Serial Ports—Internal Clock<sup>1</sup>

| Parameter           |                                                                                                                          | Min                           | Мах                | Unit |

|---------------------|--------------------------------------------------------------------------------------------------------------------------|-------------------------------|--------------------|------|

| Timing Requir       | ements                                                                                                                   |                               |                    |      |

| t <sub>SFSI</sub>   | Frame Sync Setup Before SPTx_CLK<br>(Externally Generated Frame Sync in either Transmit or<br>Receive Mode) <sup>2</sup> | 12                            |                    | ns   |

| t <sub>HFSI</sub>   | Frame Sync Hold After SPTx_CLK<br>(Externally Generated Frame Sync in either Transmit or<br>Receive Mode) <sup>2</sup>   | -0.5                          |                    | ns   |

| t <sub>SDRI</sub>   | Receive Data Setup Before SPTx_CLK <sup>2</sup>                                                                          | 3.4                           |                    | ns   |

| t <sub>HDRI</sub>   | Receive Data Hold After SPTx_CLK <sup>2</sup>                                                                            | 1.5                           |                    | ns   |

| Switching Cha       | aracteristics                                                                                                            |                               |                    |      |

| t <sub>DFSI</sub>   | Frame Sync Delay After SPTx_CLK (Internally Generated<br>Frame Sync in Transmit or Receive Mode) <sup>3</sup>            |                               | 3.5                | ns   |

| t <sub>HOFSI</sub>  | Frame Sync Hold After SPTx_CLK (Internally Generated<br>Frame Sync in Transmit or Receive Mode) <sup>3</sup>             | -2.5                          |                    | ns   |

| t <sub>DDTI</sub>   | Transmit Data Delay After SPTx_CLK <sup>3</sup>                                                                          |                               | 3.5                | ns   |

| t <sub>HDTI</sub>   | Transmit Data Hold After SPTx_CLK <sup>3</sup>                                                                           | -2.5                          |                    | ns   |

| t <sub>SCLKIW</sub> | SPTx_CLK Width <sup>4</sup>                                                                                              | $0.5 \times t_{SPTCLKPROO}$   | <sub>5</sub> – 1.5 | ns   |

| t <sub>SPTCLK</sub> | SPTx_CLK Period <sup>4</sup>                                                                                             | t <sub>SPTCLKPROG</sub> – 1.5 | i                  | ns   |

<sup>1</sup>Specifications apply to all eight SPORTs.

<sup>2</sup>Referenced to the sample edge.

<sup>3</sup>Referenced to drive edge.

<sup>4</sup>See Table 29 for details on the minimum period that can be programmed for t<sub>SPTCLKPROG</sub>.

Figure 37. Serial Ports

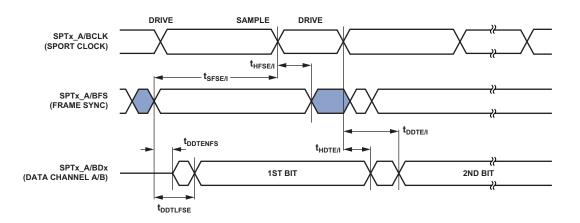

### Table 68. Serial Ports—External Late Frame Sync<sup>1</sup>

| Parameter           Switching Characteristics |                                                                                                            | Min | Мах | Unit |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------|-----|-----|------|

|                                               |                                                                                                            |     |     |      |

| t <sub>DDTLFSE</sub>                          | Data Delay from Late External Transmit Frame Sync or External Receive Frame Sync with MCE = 1, MFD = $0^2$ |     | 14  | ns   |

| t <sub>DDTENFS</sub>                          | Data Enable for MCE = 1, MFD = $0^2$                                                                       | 0.5 |     | ns   |

<sup>1</sup>Specifications apply to all eight SPORTs.

<sup>2</sup> The  $t_{DDTLFSE}$  and  $t_{DDTENFS}$  parameters apply to left justified as well as standard serial mode and MCE = 1, MFD = 0.

Figure 40. External Late Frame Sync

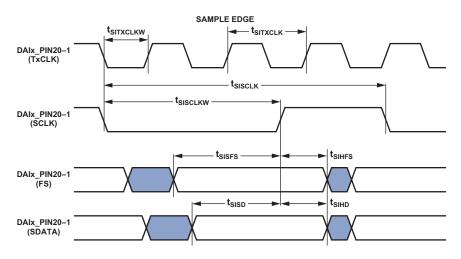

#### S/PDIF Transmitter Input Data Timing

The timing requirements for the S/PDIF transmitter are given in Table 96. Input signals are routed to the DAIx\_PINx pins using the SRU. Therefore, the timing specifications provided below are valid at the DAIx\_PINx pins.

| Table 96. | S/PDIF | Transmitter | Input | Data | Timing |

|-----------|--------|-------------|-------|------|--------|

|-----------|--------|-------------|-------|------|--------|

| Paramete                        | Parameter                                        |    | Max | Unit |

|---------------------------------|--------------------------------------------------|----|-----|------|

| Timing Req                      | uirements                                        |    |     |      |

| t <sub>SISFS</sub> <sup>1</sup> | Frame Sync Setup Before Serial Clock Rising Edge | 3  |     | ns   |

| t <sub>SIHFS</sub> 1            | Frame Sync Hold After Serial Clock Rising Edge   | 3  |     | ns   |

| t <sub>SISD</sub> 1             | Data Setup Before Serial Clock Rising Edge       | 3  |     | ns   |

| t <sub>SIHD</sub> 1             | Data Hold After Serial Clock Rising Edge         | 3  |     | ns   |

| t <sub>SITXCLKW</sub>           | Transmit Clock Width                             | 9  |     | ns   |

| t <sub>SITXCLK</sub>            | Transmit Clock Period                            | 20 |     | ns   |

| t <sub>SISCLKW</sub>            | Clock Width                                      | 36 |     | ns   |

| t <sub>SISCLK</sub>             | Clock Period                                     | 80 |     | ns   |

<sup>1</sup>The serial clock, data, and frame sync signals can come from any of the DAI pins. The serial clock and frame sync signals can also come via PCG or SPORTs. The input of the PCG can be either CLKIN or any of the DAI pins.

Figure 67. S/PDIF Transmitter Input Timing

### **Oversampling Clock (TxCLK) Switching Characteristics**

The S/PDIF transmitter requires an oversampling clock input. This high frequency clock (TxCLK) input is divided down to generate the internal biphase clock.

| Table 97. | Oversampling | Clock (TxCLK) | Switching Characteristics |

|-----------|--------------|---------------|---------------------------|

|-----------|--------------|---------------|---------------------------|

| Parameter              |                                               | Мах                                                  | Unit |

|------------------------|-----------------------------------------------|------------------------------------------------------|------|

| Switching Cha          | racteristics                                  |                                                      |      |

| f <sub>TXCLK_384</sub> | Frequency for TxCLK = $384 \times$ Frame Sync | Oversampling ratio × frame sync $\leq 1/t_{SITXCLK}$ | MHz  |

| f <sub>TXCLK_256</sub> | Frequency for TxCLK = $256 \times$ Frame Sync | 49.2                                                 | MHz  |

| f <sub>FS</sub>        | Frame Rate (FS)                               | 192.0                                                | kHz  |

### S/PDIF Receiver

The following section describes timing as it relates to the S/PDIF receiver.

#### Internal Digital PLL Mode

In the internal digital PLL mode, the internal digital PLL generates the 512  $\times$  FS clock.

### Table 98. S/PDIF Receiver Internal Digital PLL Mode Timing

| Parameter          |                                        | Min | Мах | Unit |

|--------------------|----------------------------------------|-----|-----|------|

| Switching Charac   | teristics                              |     |     |      |

| t <sub>DFSI</sub>  | Frame Sync Delay After Serial Clock    |     | 5   | ns   |

| t <sub>HOFSI</sub> | Frame Sync Hold After Serial Clock     | -2  |     | ns   |

| t <sub>DDTI</sub>  | Transmit Data Delay After Serial Clock |     | 5   | ns   |

| t <sub>HDTI</sub>  | Transmit Data Hold After Serial Clock  | -2  |     | ns   |

Figure 68. S/PDIF Receiver Internal Digital PLL Mode Timing

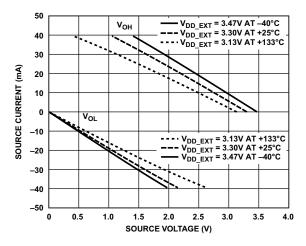

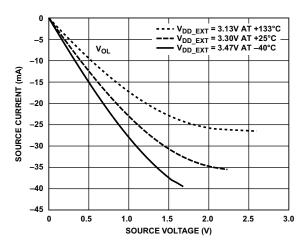

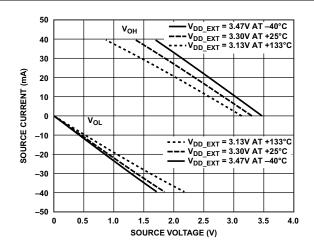

### **OUTPUT DRIVE CURRENTS**

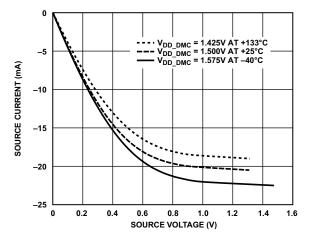

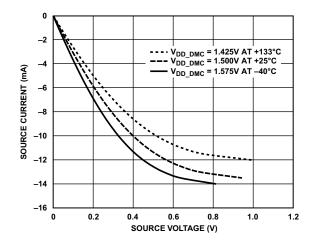

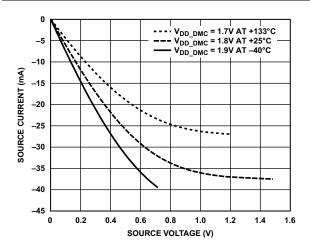

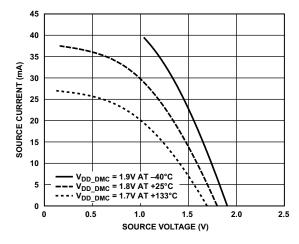

Figure 77 through Figure 89 show typical current-voltage characteristics for the output drivers of the ADSP-SC58x and ADSP-2158x processors. The curves represent the current drive capability of the output drivers as a function of output voltage.

Output drive currents for PCIe pins are compliant with PCIe Gen1 and Gen2 x1 lane data rate specifications. Output drive currents for MLB pins are compliant with MOST150 LVDS specifications. Output drive currents for USB pins are compliant with the USB 2.0 specifications.

Figure 77. Driver Type A Current (3.3 V V<sub>DD\_EXT</sub>)

Figure 78. Driver Type D Current (3.3 V V<sub>DD\_EXT</sub>)

Figure 79. Driver Type H Current (3.3 V V<sub>DD\_EXT</sub>)

Figure 80. Driver Type B and Driver Type C (DDR3 Drive Strength 40  $\Omega$ )

Figure 81. Driver Type B and Driver Type C (DDR3 Drive Strength  $60 \Omega$ )

Figure 88. Driver Type B and Device Driver C (LPDDR)

Figure 89. Driver Type B and Device Driver C (LPDDR)

### **TEST CONDITIONS**

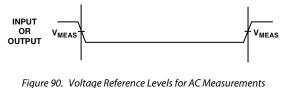

All timing requirements appearing in this data sheet were measured under the conditions described in this section. Figure 90 shows the measurement point for ac measurements (except output enable/disable). The measurement point,  $V_{MEAS}$ , is  $V_{DD}$  EXT/2 for  $V_{DD}$  EXT (nominal) = 3.3 V.

(Except Output Enable/Disable)

#### **Output Enable Time Measurement**

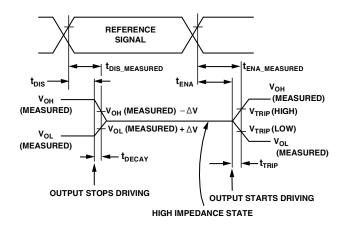

Output balls are considered enabled when they make a transition from a high impedance state to the point when they start driving. The output enable time,  $t_{ENA}$ , is the interval from the point when a reference signal reaches a high or low voltage level to the point when the output starts driving (see Figure 91).

Figure 91. Output Enable/Disable

The time t<sub>ENA\_MEASURED</sub> is the interval from when the reference signal switches to when the output voltage reaches  $V_{TRIP}$  (high) or  $V_{TRIP}$  (low). For  $V_{DD_EXT}$  (nominal) = 3.3 V,  $V_{TRIP}$  (high) is 1.9 V, and  $V_{TRIP}$  (low) is 1.4 V. Time, t<sub>TRIP</sub>, is the interval from when the output starts driving to when the output reaches the  $V_{TRIP}$  (high) or  $V_{TRIP}$  (low) trip voltage.

Time t<sub>ENA</sub> is calculated as shown in the equation:

$$t_{ENA} = t_{ENA\_MEASURED} - t_{TRIP}$$

If multiple balls (such as the data bus) are enabled, the measurement value is that of the first ball to start driving.

#### **Output Disable Time Measurement**

Output balls are considered disabled when they stop driving, go into a high impedance state, and start to decay from the output high or low voltage. The output disable time,  $t_{DIS}$ , is the difference between  $t_{DIS}$  MEASURED and  $t_{DECAY}$  (see Figure 91).

$$t_{DIS} = t_{DIS\_MEASURED} - t_{DECAS}$$

The time for the voltage on the bus to decay by  $\Delta V$  is dependent on the capacitive load,  $C_{L_2}$  and the load current,  $I_L$ . This decay time can be approximated by the following equation:

$$t_{DECAY} = (C_L \Delta V) / I_L$$

The time t<sub>DECAY</sub> is calculated with test loads  $C_L$  and  $I_L$ , with  $\Delta V$  equal to 0.25 V for V<sub>DD EXT</sub> (nominal) = 3.3 V.

The time  $t_{DIS\_MEASURED}$  is the interval from when the reference signal switches, to when the output voltage decays  $\Delta V$  from the measured output high or output low voltage.

#### **Example System Hold Time Calculation**

To determine the data output hold time in a particular system, first calculate  $t_{DECAY}$  using the previous equation. Choose  $\Delta V$  to be the difference between the output voltage of the processor and the input threshold for the device requiring the hold time.  $C_L$  is the total bus capacitance (per data line) and  $I_L$  is the total leakage or three-state current (per data line). The hold time will be  $t_{DECAY}$  plus the various output disable times as specified in the Timing Specifications section.

### **Capacitive Loading**

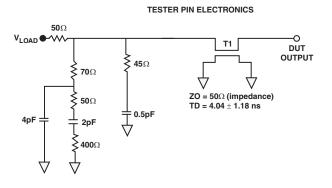

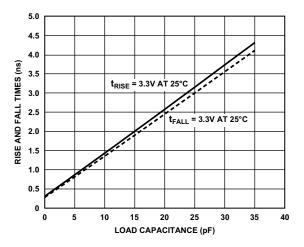

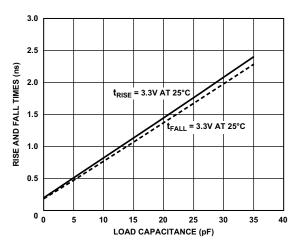

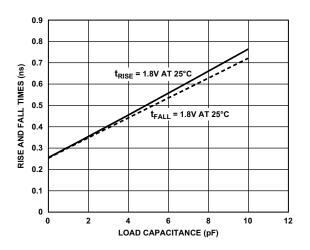

Output delays and holds are based on standard capacitive loads of an average of 6 pF on all balls (see Figure 92).  $V_{LOAD}$  is equal to  $V_{DD\_EXT}/2$ . Figure 93 through Figure 97 show how output rise time varies with capacitance. The delay and hold specifications given must be derated by a factor derived from these figures. The graphs in these figures may not be linear outside the ranges shown.

#### NOTES:

THE WORST CASE TRANSMISSION LINE DELAY IS SHOWN AND CAN BE USED FOR THE OUTPUT TIMING ANALYSIS TO REFELECT THE TRANSMISSION LINE EFFECT AND MUST BE CONSIDERED. THE TRANSMISSION LINE (TD) IS FOR LOAD ONLY AND DOES NOT AFFECT THE DATA SHEET TIMING SPECIFICATIONS.

ANALOG DEVICES RECOMMENDS USING THE IBIS MODEL TIMING FOR A GIVEN SYSTEM REQUIREMENT. IF NECESSARY, A SYSTEM MAY INCORPORATE EXTERNAL DRIVERS TO COMPENSATE FOR ANY TIMING DIFFERENCES.

Figure 92. Equivalent Device Loading for AC Measurements (Includes All Fixtures)

Figure 93. Driver Type A Typical Rise and Fall Times (10% to 90%) vs. Load Capacitance (V<sub>DD EXT</sub> = 3.3 V)

Figure 94. Driver Type H Typical Rise and Fall Times (10% to 90%) vs. Load Capacitance ( $V_{DD_EXT} = 3.3 V$ )

Figure 95. Driver Type B and Driver Type C Typical Rise and Fall Times (10% to 90%) vs. Load Capacitance ( $V_{DD}$  DMC = 1.8 V) for LPDDR