Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

E·XFl

| 2000                    |                                                                                             |

|-------------------------|---------------------------------------------------------------------------------------------|

| Product Status          | Active                                                                                      |

| Туре                    | Floating Point                                                                              |

| Interface               | CAN, EBI/EMI, Ethernet, DAI, I <sup>2</sup> C, MMC/SD/SDIO, SPI, SPORT, UART/USART, USB OTG |

| Clock Rate              | 300MHz                                                                                      |

| Non-Volatile Memory     | ROM (512kB)                                                                                 |

| On-Chip RAM             | 640kB                                                                                       |

| Voltage - I/O           | 3.30V                                                                                       |

| Voltage - Core          | 1.10V                                                                                       |

| Operating Temperature   | 0°C ~ 70°C (TA)                                                                             |

| Mounting Type           | Surface Mount                                                                               |

| Package / Case          | 349-LFBGA, CSPBGA                                                                           |

| Supplier Device Package | 349-CSPBGA (19x19)                                                                          |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-sc584kbcz-3a                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

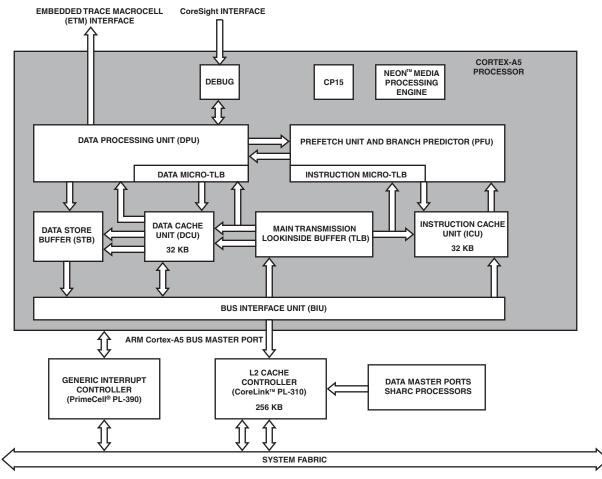

## **ARM CORTEX-A5 PROCESSOR**

The ARM Cortex-A5 processor (see Figure 2) is a high performance processor with the following features:

- Instruction cache unit (32 Kb) and data L1 cache unit (32 Kb)

- In order pipeline with dynamic branch prediction

- ARM, Thumb, and ThumbEE instruction set support

- ARM TrustZone<sup>®</sup> security extensions

- Harvard L1 memory system with a memory management unit (MMU)

- ARM v7 debug architecture

- Trace support through an embedded trace macrocell (ETM) interface

- Extension—vector floating-point unit (IEEE 754) with trapless execution

- Extension—media processing engine (MPE) with NEON<sup>™</sup> technology

- Extension—Jazelle hardware acceleration

TO OTHER CORES

Figure 2. ARM Cortex-A5 Processor Block Diagram

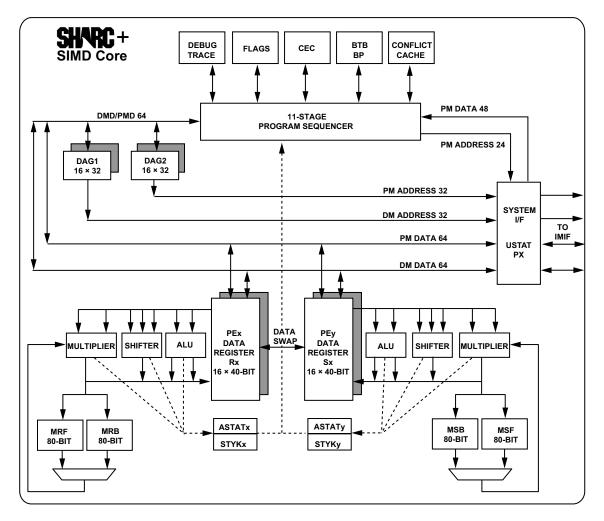

Figure 4. SHARC+ SIMD Core Block Diagram

### L1 Memory

Figure 5 shows the ADSP-SC58x/ADSP-2158x memory map. Each SHARC+ core has a tightly coupled L1 SRAM of up to 5 Mb. Each SHARC+ core can access code and data in a single cycle from this memory space. The ARM Cortex-A5 core can also access this memory space with multicycle accesses.

In the SHARC+ core private address space, both cores have L1 memory.

SHARC+ core memory-mapped register (CMMR) address space is 0x 0000 0000 through 0x 0003 FFFF in Normal Word (32-bit). Each block can be configured for different combinations of code and data storage. Of the 5 Mb SRAM, up to 1024 Kb can be configured for data memory (DM), program memory (PM), and instruction cache. Each memory block supports single-cycle, independent accesses by the core processor and I/O processor. The memory architecture, in combination with its separate on-chip buses, allows two data transfers from the core and one from the DMA engine in a single cycle. The SRAM of the processor can be configured as a maximum of 160k words of 32-bit data, 320k words of 16-bit data, 106.7k words of 48-bit instructions (or 40-bit data), or combinations of different word sizes up to 5 Mb. All of the memory can be accessed as 8-bit, 16-bit, 32-bit, 48-bit, or 64-bit words. Support of a 16-bit floating-point storage format doubles the amount of data that can be stored on chip.

Conversion between the 32-bit floating-point and 16-bit floating-point formats is performed in a single instruction. While each memory block can store combinations of code and data, accesses are most efficient when one block stores data using the DM bus for transfers, and the other block stores instructions and data using the PM bus for transfers.

Using the DM and PM buses, with each bus dedicated to a memory block, assures single-cycle execution with two data transfers. In this case, the instruction must be available in the cache. The system configuration is flexible, but a typical configuration is 512 Kb DM, 128 Kb PM, and 128 Kb of instruction cache, with the remaining L1 memory configured as SRAM. Each addressable memory space outside the L1 memory can be accessed either directly or via cache.

The processing elements are referred to as PEx and PEy data registers and each contain an arithmetic logic unit (ALU), multiplier, shifter, and register file. PEx is always active and PEy is enabled by setting the PEYEN mode bit in the mode control register (MODE1).

Single instruction multiple data (SIMD) mode allows the processors to execute the same instruction in both processing elements, but each processing element operates on different data. This architecture efficiently executes math intensive DSP algorithms. In addition to all the features of previous generation SHARC cores, the SHARC+ core also provides a new and simpler way to execute an instruction only on the PEy data register.

SIMD mode also affects the way data transfers between memory and processing elements because to sustain computational operation in the processing elements requires twice the data bandwidth. Therefore, entering SIMD mode doubles the bandwidth between memory and the processing elements. When using the DAGs to transfer data in SIMD mode, two data values transfer with each memory or register file access.

### Independent, Parallel Computation Units

Within each processing element is a set of pipelined computational units. The computational units consist of a multiplier, arithmetic/logic unit (ALU), and shifter. These units are arranged in parallel, maximizing computational throughput. These computational units support IEEE 32-bit single-precision floating-point, 40-bit extended-precision floating-point, IEEE 64-bit double-precision floating-point, and 32-bit fixed-point data formats.

A multifunction instruction set supports parallel execution of ALU and multiplier operations. In SIMD mode, the parallel ALU and multiplier operations occur in both processing elements per core.

All processing operations take one cycle to complete. For all floating-point operations, the processor takes two cycles to complete in case of data dependency. Double-precision floating-point data take two to six cycles to complete. The processor stalls for the appropriate number of cycles for an interlocked pipeline plus data dependency check.

### Core Timer

Each SHARC+ processor core also has a timer. This extra timer is clocked by the internal processor clock and is typically used as a system tick clock for generating periodic operating system interrupts.

#### Data Register File

Each processing element contains a general-purpose data register file. The register files transfer data between the computation units and the data buses, and store intermediate results. These 10-port, 32-register register files (16 primary, 16 secondary), combined with the enhanced Harvard architecture of the processor, allow unconstrained data flow between computation units and internal memory. The registers in the PEx data register file are referred to as R0–R15 and in the PEy data register file as S0–S15.

#### **Context Switch**

Many of the registers of the processor have secondary registers that can activate during interrupt servicing for a fast context switch. The data, DAG, and multiplier result registers have secondary registers. The primary registers are active at reset, while control bits in MODE1 activate the secondary registers.

#### Universal Registers (USTAT)

General-purpose tasks use the universal registers. The four USTAT registers allow easy bit manipulations (set, clear, toggle, test, XOR) for all control and status peripheral registers.

The data bus exchange register (PX) permits data to pass between the 64-bit PM data bus and the 64-bit DM data bus or between the 40-bit register file and the PM or DM data bus. These registers contain hardware to handle the data width difference.

#### Data Address Generators With Zero-Overhead Hardware Circular Buffer Support

For indirect addressing and implementing circular data buffers in hardware, the ADSP-SC58x/ADSP-2158x processor uses the two data address generators (DAGs). Circular buffers allow efficient programming of delay lines and other data structures required in digital signal processing, and are commonly used in digital filters and Fourier transforms. The two DAGs of the processors contain sufficient registers to allow the creation of up to 32 circular buffers (16 primary register sets and 16 secondary sets). The DAGs automatically handle address pointer wraparound, reduce overhead, increase performance, and simplify implementation. Circular buffers can start and end at any memory location.

#### Flexible Instruction Set Architecture (ISA)

The ISA, a 48-bit instruction word, accommodates various parallel operations for concise programming. For example, the processors can conditionally execute a multiply, an add, and a subtract in both processing elements while branching and fetching up to four 32-bit values from memory—all in a single instruction. Additionally, the double-precision floating-point instruction set is an addition to the SHARC+ core.

#### Variable Instruction Set Architecture (VISA)

In addition to supporting the standard 48-bit instructions from previous SHARC processors, the SHARC+ core processors support 16-bit and 32-bit opcodes for many instructions, formerly 48-bit in the ISA. This feature, called variable instruction set architecture (VISA), drops redundant or unused bits within the 48-bit instruction to create more efficient and compact code. The program sequencer supports fetching these 16-bit and 32bit instructions from both internal and external memories. VISA is not an operating mode; it is only address dependent (refer to memory map ISA/VISA address spaces in Table 7). Furthermore, it allows jumps between ISA and VISA instruction fetches.

# **SECURITY FEATURES**

The following sections describe the security features of the ADSP-SC58x/ADSP-2158x processors.

### ARM TrustZone

The ADSP-SC58x processors provide TrustZone technology that is integrated into the ARM Cortex-A5 processors. The TrustZone technology enables a secure state that is extended throughout the system fabric.

### Cryptographic Hardware Accelerators

The ADSP-SC58x/ADSP-2158x processors support standardsbased hardware accelerated encryption, decryption, authentication, and true random number generation.

Support for the hardware-accelerated cryptographic ciphers includes the following:

- AES in ECB, CBC, ICM, and CTR modes with 128-bit, 192-bit, and 256-bit keys

- DES in ECB and CBC mode with 56-bit key

- 3DES in ECB and CBC mode with 3x 56-bit key

- ARC4 in stateful, stateless mode, up to 128-bit key

Support for the hardware accelerated hash functions includes the following:

- SHA-1

- SHA-2 with 224-bit and 256-bit digests

- HMAC transforms for SHA-1 and SHA-2

- MD5

Public key accelerator (PKA) is available to offload computation intensive public key cryptography operations.

Both a hardware-based nondeterministic random number generator and pseudorandom number generator are available.

Secure boot is also available with 224-bit elliptic curve digital signatures ensuring integrity and authenticity of the boot stream. Optionally, ensuring confidentiality through AES-128 encryption is available.

Employ secure debug to allow only trusted users to access the system with debug tools.

### CAUTION

This product includes security features that can be used to protect embedded nonvolatile memory contents and prevent execution of unauthorized code. When security is enabled on this device (either by the ordering party or the subsequent receiving parties), the ability of Analog Devices to conduct failure analysis on returned devices is limited. Contact Analog Devices for details on the failure analysis limitations for this device.

### System Protection Unit (SPU)

The system protection unit (SPU) guards against accidental or unwanted access to an MMR space of the peripheral by providing a write protection mechanism. The user can choose and configure the protected peripherals as well as configure which of the four system MMR masters (two SHARC+ cores, memory DMA, and CoreSight debug) the peripherals are guarded against.

The SPU is also part of the security infrastructure. Along with providing write protection functionality, the SPU is employed to define which resources in the system are secure or nonsecure and to block access to secure resources from nonsecure masters.

### System Memory Protection Unit (SMPU)

Synonymously, the system memory protection unit (SMPU) provides memory protection against read and/or write transactions to defined regions of memory. There are SMPU units in the ADSP-SC58x/ADSP-2158x processors for each memory space, except for SHARC L1 and SPI direct memory slave.

The SMPU is also part of the security infrastructure. It allows the user to protect against arbitrary read and/or write transactions and allows regions of memory to be defined as secure and prevent nonsecure masters from accessing those memory regions.

# **SAFETY FEATURES**

The ADSP-SC58x/ADSP-2158x processors are designed to support functional safety applications. While the level of safety is mainly dominated by the system concept, the following primitives are provided by the processors to build a robust safety concept.

### Multiparity Bit Protected SHARC+ Core L1 Memories

In the SHARC+ core L1 memory space, whether SRAM or cache, multiple parity bits protect each word to detect the single event upsets that occur in all RAMs. Parity does not protect the cache tags.

### Error Correcting Codes (ECC) Protected L2 Memories

Error correcting codes (ECC) correct single event upsets. A single error correct-double error detect (SEC-DED) code protects the L2 memory. By default, ECC is enabled, but it can be disabled on a per bank basis. Single-bit errors correct transparently. If enabled, dual-bit errors can issue a system event or fault. ECC protection is fully transparent to the user, even if L2 memory is read or written by 8-bit or 16-bit entities.

### Cyclic Redundant Code (CRC) Protected Memories

While parity bit and ECC protection mainly protect against random soft errors in L1 and L2 memory cells, the cyclic redundant code (CRC) engines can protect against systematic errors (pointer errors) and static content (instruction code) of L1, L2, and even L3 memories (DDR2, LPDDR). The processors feature two CRC engines that are embedded in the memory to memory DMA controllers.

| Signal Name   | Direction | Description                                                                                                                                                                                                                                               |

|---------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMC_ABE[n]    | Output    | Byte Enable n. Indicates whether the lower or upper byte of a memory is being accessed. When an                                                                                                                                                           |

|               |           | asynchronous write is made to the upper byte of a 16-bit memory, $\overline{SMC}ABE1 = 0$ and $\overline{SMC}ABE0 = 1$ . When an asynchronous write is made to the lower byte of a 16-bit memory, $\overline{SMC}ABE1 = 1$ and $\overline{SMC}ABE0 = 0$ . |

| SMC_AMS[n]    | Output    | Memory Select n. Typically connects to the chip select of a memory device.                                                                                                                                                                                |

| SMC_AOE       | Output    | Output Enable. Asserts at the beginning of the setup period of a read access.                                                                                                                                                                             |

| SMC_ARDY      | Input     | <b>Asynchronous Ready.</b> Flow control signal used by memory devices to indicate to the SMC when further transactions may proceed.                                                                                                                       |

| SMC_ARE       | Output    | Read Enable. Asserts at the beginning of a read access.                                                                                                                                                                                                   |

| SMC_AWE       | Output    | Write Enable. Asserts for the duration of a write access period.                                                                                                                                                                                          |

| SMC_A[nn]     | Output    | Address n. Address bus.                                                                                                                                                                                                                                   |

| SMC_D[nn]     | InOut     | Data n. Bidirectional data bus.                                                                                                                                                                                                                           |

| SPI_CLK       | InOut     | Clock. Input in slave mode, output in master mode.                                                                                                                                                                                                        |

| SPI_D2        | InOut     | Data 2. Transfers serial data in quad mode. Open-drain when ODM mode is enabled.                                                                                                                                                                          |

| SPI_D3        | InOut     | Data 3. Transfers serial data in quad mode. Open-drain when ODM mode is enabled.                                                                                                                                                                          |

| SPI_MISO      | InOut     | <b>Master In, Slave Out.</b> Transfers serial data. Operates in the same direction as SPI_MOSI in dual and quad modes. Open-drain when ODM mode is enabled.                                                                                               |

| SPI_MOSI      | InOut     | <b>Master Out, Slave In.</b> Transfers serial data. Operates in the same direction as SPI_MISO in dual and quad modes. Open-drain when ODM mode is enabled.                                                                                               |

| SPI_RDY       | InOut     | Ready. Optional flow signal. Output in slave mode, input in master mode.                                                                                                                                                                                  |

| SPI_SEL[n]    | Output    | Slave Select Output n. Used in master mode to enable the desired slave.                                                                                                                                                                                   |

| <u>SPI_SS</u> | Input     | Slave Select Input.<br>Slave mode—acts as the slave select input.<br>Master mode—optionally serves as an error detection input for the SPI when there are multiple<br>masters.                                                                            |

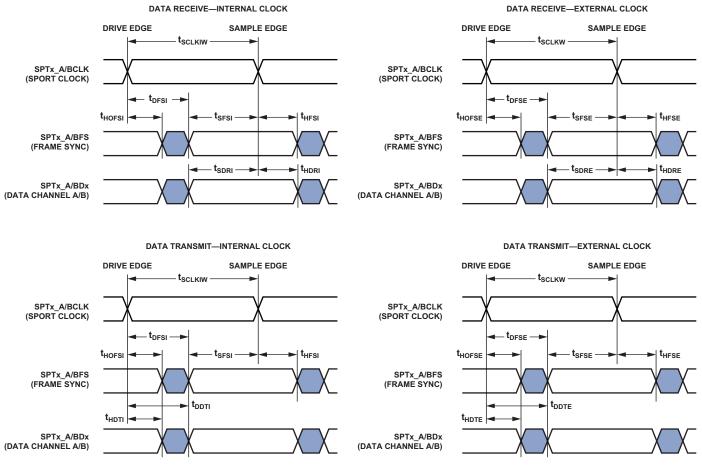

| SPT_ACLK      | InOut     | <b>Channel A Clock.</b> Data and frame sync are driven/sampled with respect to this clock. This signal can be either internally or externally generated.                                                                                                  |

| SPT_AD0       | InOut     | <b>Channel A Data 0.</b> Primary bidirectional data I/O. This signal can be configured as an output to transmit serial data or as an input to receive serial data.                                                                                        |

| SPT_AD1       | InOut     | <b>Channel A Data 1.</b> Secondary bidirectional data I/O. This signal can be configured as an output to transmit serial data or as an input to receive serial data.                                                                                      |

| SPT_AFS       | InOut     | <b>Channel A Frame Sync.</b> The frame sync pulse initiates shifting of the serial data. This signal is either generated internally or externally.                                                                                                        |

| SPT_ATDV      | Output    | <b>Channel A Transmit Data Valid.</b> This signal is optional and only active when SPORT is configured in multichannel transmit mode. It is asserted during enabled slots.                                                                                |

| SPT_BCLK      | InOut     | <b>Channel B Clock.</b> Data and frame sync are driven/sampled with respect to this clock. This signal can be either internally or externally generated.                                                                                                  |

| SPT_BD0       | InOut     | <b>Channel B Data 0.</b> Primary bidirectional data I/O. This signal can be configured as an output to transmit serial data or as an input to receive serial data.                                                                                        |

| SPT_BD1       | InOut     | <b>Channel B Data 1.</b> Secondary bidirectional data I/O. This signal can be configured as an output to transmit serial data or as an input to receive serial data.                                                                                      |

| SPT_BFS       | InOut     | <b>Channel B Frame Sync.</b> The frame sync pulse initiates shifting of serial data. This signal is either generated internally or externally.                                                                                                            |

| SPT_BTDV      | Output    | <b>Channel B Transmit Data Valid.</b> This signal is optional and only active when SPORT is configured in multichannel transmit mode. It is asserted during enabled slots.                                                                                |

| SYS_BMODE[n]  | Input     | Boot Mode Control n. Selects the boot mode of the processor.                                                                                                                                                                                              |

| SYS_CLKIN0    | Input     | Clock/Crystal Input.                                                                                                                                                                                                                                      |

| SYS_CLKIN1    | Input     | Clock/Crystal Input.                                                                                                                                                                                                                                      |

| SYS_CLKOUT    | Output    | <b>Processor Clock Output.</b> Outputs internal clocks. Clocks may be divided down. See the CGU chapter of the ADSP-SC58x/ADSP-2158x SHARC+ Processor Hardware Reference for more details.                                                                |

## Table 11. ADSP-SC58x/ADSP-2158x Detailed Signal Descriptions (Continued)

| Signal Name | Direction | Description                                                                                                                                                                                                                                                                          |

|-------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYS_FAULT   | InOut     | Active-High Fault Output. Indicates internal faults or senses external faults depending on the                                                                                                                                                                                       |

|             |           | operating mode.                                                                                                                                                                                                                                                                      |

| SYS_FAULT   | InOut     | Active-Low Fault Output. Indicates internal faults or senses external faults depending on the                                                                                                                                                                                        |

|             |           | operating mode.                                                                                                                                                                                                                                                                      |

| SYS_HWRST   | Input     | Processor Hardware Reset Control. Resets the device when asserted.                                                                                                                                                                                                                   |

| SYS_RESOUT  | Output    | <b>Reset Output.</b> Indicates the device is in the reset state.                                                                                                                                                                                                                     |

| SYS_XTAL0   | Output    | Crystal Output.                                                                                                                                                                                                                                                                      |

| SYS_XTAL1   | Output    | Crystal Output.                                                                                                                                                                                                                                                                      |

| TM_ACI[n]   | Input     | Alternate Capture Input n. Provides an additional input for WIDCAP, WATCHDOG, and PININT modes.                                                                                                                                                                                      |

| TM_ACLK[n]  | Input     | Alternate Clock n. Provides an additional time base for an individual timer.                                                                                                                                                                                                         |

| TM_CLK      | Input     | <b>Clock.</b> Provides an additional global time base for all GP timers.                                                                                                                                                                                                             |

| TM_TMR[n]   | InOut     | Timer n. The main input/output signal for each timer.                                                                                                                                                                                                                                |

| TRACE_CLK   | Output    | Trace Clock. Clock output.                                                                                                                                                                                                                                                           |

| TRACE_D[nn] | Output    | Trace Data n. Unidirectional data bus.                                                                                                                                                                                                                                               |

| TWI_SCL     | InOut     | Serial Clock. Clock output when master, clock input when slave.                                                                                                                                                                                                                      |

| TWI_SDA     | InOut     | Serial Data. Receives or transmits data.                                                                                                                                                                                                                                             |

| UART_CTS    | Input     | Clear to Send. Flow control signal.                                                                                                                                                                                                                                                  |

| UART_RTS    | Output    | Request to Send. Flow control signal.                                                                                                                                                                                                                                                |

| UART_RX     | Input     | <b>Receive.</b> Receives input. Typically connects to a transceiver that meets the electrical requirements of the device being communicated with.                                                                                                                                    |

| UART_TX     | Output    | <b>Transmit.</b> Transmits output. Typically connects to a transceiver that meets the electrical requirements of the device being communicated with.                                                                                                                                 |

| USB_CLKIN   | Input     | <b>Clock/Crystal Input.</b> This clock input is multiplied by a PLL to form the USB clock. See data sheet specifications for frequency/tolerance information.                                                                                                                        |

| USB_DM      | InOut     | Data –. Bidirectional differential data line.                                                                                                                                                                                                                                        |

| USB_DP      | InOut     | Data +. Bidirectional differential data line.                                                                                                                                                                                                                                        |

| USB_ID      | Input     | <b>OTG ID.</b> Senses whether the controller is a host or device. This signal is pulled low when an A-type plug is sensed (signifying that the USB controller is the A device). The input is high when a B-type plug is sensed (signifying that the USB controller is the B device). |

| USB_VBC     | Output    | <b>VBUS Control.</b> Controls an external voltage source to supply VBUS when in host mode. Can be configured as open-drain. Polarity is configurable as well.                                                                                                                        |

| USB_VBUS    | InOut     | Bus Voltage. Connects to bus voltage in host and device modes.                                                                                                                                                                                                                       |

| USB_XTAL    | Output    | <b>Crystal.</b> Drives an external crystal. Must be left unconnected if an external clock is driving USB_CLKIN.                                                                                                                                                                      |

# Table 11. ADSP-SC58x/ADSP-2158x Detailed Signal Descriptions (Continued)

| Signal Name | Description              | Port      | Pin Name  |

|-------------|--------------------------|-----------|-----------|

| UART1_RTS   | UART1 Request to Send    | E         | PE_02     |

| UART1_RX    | UART1 Receive            | В         | PB_03     |

| UART1_TX    | UART1 Transmit           | В         | PB_02     |

| UART2_CTS   | UART2 Clear to Send      | E         | PE_11     |

| UART2_RTS   | UART2 Request to Send    | E         | PE_10     |

| UART2_RX    | UART2 Receive            | D         | PD_13     |

| UART2_TX    | UART2 Transmit           | D         | PD_12     |

| USB0_CLKIN  | USB0 Clock/Crystal Input | Not Muxed | USB_CLKIN |

| USB0_DM     | USB0 Negative Data (–)   | Not Muxed | USB0_DM   |

| USB0_DP     | USB0 Positive Data (+)   | Not Muxed | USB0_DP   |

| USB0_ID     | USB0 OTG ID              | Not Muxed | USB0_ID   |

| USB0_VBC    | USB0 VBUS Control        | Not Muxed | USB0_VBC  |

| USB0_VBUS   | USB0 Bus Voltage         | Not Muxed | USB0_VBUS |

| USB0_XTAL   | USB0 Crystal             | Not Muxed | USB_XTAL  |

| VDD_DMC     | DMC VDD                  | Not Muxed | VDD_DMC   |

| VDD_HADC    | HADC VDD                 | Not Muxed | VDD_HADC  |

| VDD_USB     | USB VDD                  | Not Muxed | VDD_USB   |

## Table 12. ADSP-SC58x/ADSP-2158x 349-Ball CSP\_BGA Signal Descriptions (Continued)

| Signal Name | Description                | Port | Pin Name  |

|-------------|----------------------------|------|-----------|

| PI0_D00     | EPPIO Data 0               | E    | PE_12     |

| PI0_D01     | EPPI0 Data 1               | E    | PE_11     |

| PI0_D02     | EPPI0 Data 2               | E    | PE_10     |

| PI0_D03     | EPPIO Data 3               | E    | PE_09     |

| PI0_D04     | EPPIO Data 4               | E    | PE_08     |

| PI0_D05     | EPPIO Data 5               | E    | PE_07     |

| PI0_D06     | EPPIO Data 6               | E    | PE_06     |

| PI0_D07     | EPPIO Data 7               | E    | PE_05     |

| PI0_D08     | EPPIO Data 8               | E    | PE_04     |

| PI0_D09     | EPPIO Data 9               | E    | PE_00     |

| PI0_D10     | EPPIO Data 10              | D    | PD_15     |

| PI0_D11     | EPPIO Data 11              | D    | PD_14     |

| PI0_D12     | EPPIO Data 12              | В    | PB_04     |

| PI0_D13     | EPPIO Data 13              | В    | PB_05     |

| <br>PI0_D14 | EPPI0 Data 14              | В    | <br>PB_00 |

| <br>PI0_D15 | EPPIO Data 15              | В    | <br>PB_01 |

| PI0_D16     | EPPI0 Data 16              | В    | PB_02     |

| PI0_D17     | EPPIO Data 17              | В    | PB_03     |

| PI0_D18     | EPPIO Data 18              | D    | PD_13     |

| PI0_D19     | EPPIO Data 19              | D    | PD_12     |

| PI0_D20     | EPPIO Data 20              | E    | PE_13     |

| PI0_D21     | EPPIO Data 21              | E    | PE_14     |

| PI0_D22     | EPPIO Data 22              | E    | PE_15     |

| PI0_D23     | EPPIO Data 23              | D    | PD_00     |

| PI0_FS1     | EPPI0 Frame Sync 1 (HSYNC) | E    | PE_02     |

| PI0_FS2     | EPPI0 Frame Sync 2 (VSYNC) | E    | PE_01     |

| PI0_FS3     | EPPIO Frame Sync 3 (FIELD) | C    | PC_15     |

| WM0_AH      | PWM0 Channel A High Side   | В    | PB_07     |

| WM0_AL      | PWM0 Channel A Low Side    | В    | PB_08     |

| WM0_BH      | PWM0 Channel B High Side   | В    | PB_06     |

| WM0_BL      | PWM0 Channel B Low Side    | C    | PC_00     |

| WM0_CH      | PWM0 Channel C High Side   | В    | PB_13     |

| WM0_CL      | PWM0 Channel C Low Side    | В    |           |

|             | PWM0 Channel D High Side   |      | PB_14     |

| WM0_DH      | 5                          | В    | PB_11     |

| WM0_DL      | PWM0 Channel D Low Side    | В    | PB_12     |

| WM0_SYNC    | PWM0 PWMTMR Grouped        | E    | PE_09     |

| WM0_TRIP0   | PWM0 Shutdown Input 0      | В    | PB_15     |

| WM1_AH      | PWM1 Channel A High Side   | D    | PD_03     |

| WM1_AL      | PWM1 Channel A Low Side    | D    | PD_04     |

| WM1_BH      | PWM1 Channel B High Side   | D    | PD_05     |

| WM1_BL      | PWM1 Channel B Low Side    | D    | PD_06     |

| WM1_CH      | PWM1 Channel C High Side   | D    | PD_07     |

| WM1_CL      | PWM1 Channel C Low Side    | D    | PD_08     |

| WM1_DH      | PWM1 Channel D High Side   | D    | PD_09     |

| WM1_DL      | PWM1 Channel D Low Side    | D    | PD_10     |

| WM1_SYNC    | PWM1 PWMTMR Grouped        | D    | PD_11     |

| WM1_TRIP0   | PWM1 Shutdown Input 0      | D    | PD_02     |

| WM2_AH      | PWM2 Channel A High Side   | F    | PF_07     |

## Table 19. ADSP-SC58x/ADSP-2158x 529-Ball CSP\_BGA Signal Descriptions (Continued)

|             |       | Driver | Int      | Reset | Reset |              | Description       |

|-------------|-------|--------|----------|-------|-------|--------------|-------------------|

| Signal Name | Туре  | Туре   | Term     | Term  | Drive | Power Domain | and Notes         |

| DAI0_PIN16  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI0 Pin 16 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI0_PIN17  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI0 Pin 17 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI0_PIN18  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI0 Pin 18 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI0_PIN19  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI0 Pin 19 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI0_PIN20  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI0 Pin 20 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN01  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 1  |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN02  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 2  |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN03  | InOut | A      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 3  |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN04  | InOut | A      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 4  |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN05  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 5  |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN06  | InOut | A      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 6  |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN07  | InOut | A      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 7  |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN08  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 8  |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN09  | InOut | A      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 9  |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN10  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 10 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN11  | InOut | A      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 11 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN12  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 12 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN13  | InOut | A      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 13 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN14  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 14 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN15  | InOut | A      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 15 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN16  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 16 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN17  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 17 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN18  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 18 |

|             |       |        |          |       |       |              | Notes: No notes   |

| DAI1_PIN19  | InOut | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 19 |

|             |       |        | 1        |       |       |              | Notes: No notes   |

|              |          | Driver | Int      | Reset | Reset |              | Description                              |

|--------------|----------|--------|----------|-------|-------|--------------|------------------------------------------|

| Signal Name  | Туре     | Туре   | Term     | Term  | Drive | Power Domain | and Notes                                |

| DAI1_PIN20   | InOut    | А      | PullDown | none  | none  | VDD_EXT      | Desc: DAI1 Pin 20                        |

|              |          |        |          |       |       |              | Notes: No notes                          |

| DMC0_A00     | Output   | В      | none     | none  | none  | VDD_DMC      | Desc: DMC0 Address 0                     |

|              |          | -      |          |       |       |              | Notes: No notes                          |

| DMC0_A01     | Output   | В      | none     | none  | none  | VDD_DMC      | Desc: DMC0 Address 1                     |

|              | Output   | D      |          |       |       |              | Notes: No notes<br>Desc: DMC0 Address 2  |

| DMC0_A02     | Output   | В      | none     | none  | none  | VDD_DMC      | Notes: No notes                          |

| DMC0_A03     | Output   | В      | none     | none  | none  | VDD_DMC      | Desc: DMC0 Address 3                     |

| DIVICO_A03   | Output   | D      | none     | none  | none  | VDD_DIVIC    | Notes: No notes                          |

| DMC0_A04     | Output   | В      | none     | none  | none  | VDD_DMC      | Desc: DMC0 Address 4                     |

| Diffeo_rio i | output   | U      | none     | none  | none  | VDD_DIMC     | Notes: No notes                          |

| DMC0_A05     | Output   | В      | none     | none  | none  | VDD_DMC      | Desc: DMC0 Address 5                     |

|              |          | -      |          |       |       |              | Notes: No notes                          |

| DMC0_A06     | Output   | В      | none     | none  | none  | VDD_DMC      | Desc: DMC0 Address 6                     |

| _            |          |        |          |       |       | _            | Notes: No notes                          |

| DMC0_A07     | Output   | В      | none     | none  | none  | VDD_DMC      | Desc: DMC0 Address 7                     |

|              |          |        |          |       |       |              | Notes: No notes                          |

| DMC0_A08     | Output   | В      | none     | none  | none  | VDD_DMC      | Desc: DMC0 Address 8                     |

|              |          |        |          |       |       |              | Notes: No notes                          |

| DMC0_A09     | Output   | В      | none     | none  | none  | VDD_DMC      | Desc: DMC0 Address 9                     |

|              |          |        |          |       |       |              | Notes: No notes                          |

| DMC0_A10     | Output   | В      | none     | none  | none  | VDD_DMC      | Desc: DMC0 Address 10                    |

|              |          |        |          |       |       |              | Notes: No notes                          |

| DMC0_A11     | Output   | В      | none     | none  | none  | VDD_DMC      | Desc: DMC0 Address 11                    |

|              |          |        |          |       |       |              | Notes: No notes                          |

| DMC0_A12     | Output   | В      | none     | none  | none  | VDD_DMC      | Desc: DMC0 Address 12                    |

|              | <b>.</b> |        |          |       |       |              | Notes: No notes                          |

| DMC0_A13     | Output   | В      | none     | none  | none  | VDD_DMC      | Desc: DMC0 Address 13<br>Notes: No notes |

|              | Output   | В      | nono     | nono  | nono  | VDD_DMC      | Desc: DMC0 Address 14                    |

| DMC0_A14     | Output   | D      | none     | none  | none  | VDD_DIVIC    | Notes: No notes                          |

| DMC0_A15     | Output   | В      | none     | none  | none  | VDD_DMC      | Desc: DMC0 Address 15                    |

| Diffeo_/rits | output   | U      | none     | none  | none  | VDD_DIMC     | Notes: No notes                          |

| DMC0_BA0     | Output   | В      | none     | none  | none  | VDD_DMC      | Desc: DMC0 Bank Address Input            |

|              |          | -      |          |       |       |              | 0                                        |

|              |          |        |          |       |       |              | Notes: No notes                          |

| DMC0_BA1     | Output   | В      | none     | none  | none  | VDD_DMC      | Desc: DMC0 Bank Address Input            |

|              |          |        |          |       |       |              | 1                                        |

|              |          |        |          |       |       |              | Notes: No notes                          |

| DMC0_BA2     | Output   | В      | none     | none  | none  | VDD_DMC      | Desc: DMC0 Bank Address Input            |

|              |          |        |          |       |       |              | 2<br>Notos: No notos                     |

|              | 0        | P      | nonc     |       | n     |              | Notes: No notes                          |

| DMC0_CAS     | Output   | В      | none     | none  | none  | VDD_DMC      | Desc: DMC0 Column Address<br>Strobe      |

|              |          |        |          |       |       |              | Notes: No notes                          |

| DMC0_CK      | Output   | с      | none     | none  | L     | VDD_DMC      | Desc: DMC0 Clock                         |

|              |          | -      |          |       |       |              | Notes: No notes                          |

Table 27. ADSP-SC58x/ADSP-2158x Designer Quick Reference (Continued)

| Signal Name | Туре   | Driver<br>Type | Int<br>Term                                                      | Reset<br>Term | Reset<br>Drive | Power Domain | Description<br>and Notes                                                 |

|-------------|--------|----------------|------------------------------------------------------------------|---------------|----------------|--------------|--------------------------------------------------------------------------|

| DMC0_UDQS   | InOut  | С              | Internal logic<br>ensures that<br>input signal does<br>not float | none          | none           | VDD_DMC      | Desc: DMC0 Data Strobe for<br>Upper Byte (complement)<br>Notes: No notes |

| DMC0_VREF   | а      |                | none                                                             | none          | none           | VDD_DMC      | Desc: DMC0 Voltage Reference<br>Notes: No notes                          |

| DMC0_WE     | Output | В              | none                                                             | none          | none           | VDD_DMC      | Desc: DMC0 Write Enable<br>Notes: No notes                               |

| DMC1_A00    | Output | В              | none                                                             | none          | none           | VDD_DMC      | Desc: DMC1 Address 0<br>Notes: No notes                                  |

| DMC1_A01    | Output | В              | none                                                             | none          | none           | VDD_DMC      | Desc: DMC1 Address 1<br>Notes: No notes                                  |

| DMC1_A02    | Output | В              | none                                                             | none          | none           | VDD_DMC      | Desc: DMC1 Address 2<br>Notes: No notes                                  |

| DMC1_A03    | Output | В              | none                                                             | none          | none           | VDD_DMC      | Desc: DMC1 Address 3<br>Notes: No notes                                  |

| DMC1_A04    | Output | В              | none                                                             | none          | none           | VDD_DMC      | Desc: DMC1 Address 4<br>Notes: No notes                                  |

| DMC1_A05    | Output | В              | none                                                             | none          | none           | VDD_DMC      | Desc: DMC1 Address 5<br>Notes: No notes                                  |

| DMC1_A06    | Output | В              | none                                                             | none          | none           | VDD_DMC      | Desc: DMC1 Address 6                                                     |

| DMC1_A07    | Output | В              | none                                                             | none          | none           | VDD_DMC      | Notes: No notes<br>Desc: DMC1 Address 7                                  |

| DMC1_A08    | Output | В              | none                                                             | none          | none           | VDD_DMC      | Notes: No notes<br>Desc: DMC1 Address 8                                  |

| DMC1_A09    | Output | В              | none                                                             | none          | none           | VDD_DMC      | Notes: No notes<br>Desc: DMC1 Address 9                                  |

| DMC1_A10    | Output | В              | none                                                             | none          | none           | VDD_DMC      | Notes: No notes<br>Desc: DMC1 Address 10                                 |

| DMC1_A11    | Output | В              | none                                                             | none          | none           | VDD_DMC      | Notes: No notes<br>Desc: DMC1 Address 11                                 |

| DMC1_A12    | Output | В              | none                                                             | none          | none           | VDD_DMC      | Notes: No notes<br>Desc: DMC1 Address 12                                 |

| DMC1_A13    | Output | В              | none                                                             | none          | none           | VDD_DMC      | Notes: No notes<br>Desc: DMC1 Address 13<br>Notes: No notes              |

| DMC1_A14    | Output | В              | none                                                             | none          | none           | VDD_DMC      | Desc: DMC1 Address 14                                                    |

| DMC1_A15    | Output | В              | none                                                             | none          | none           | VDD_DMC      | Notes: No notes<br>Desc: DMC1 Address 15                                 |

| DMC1_BA0    | Output | В              | none                                                             | none          | none           | VDD_DMC      | Notes: No notes<br>Desc: DMC1 Bank Address Input                         |

| DMC1_BA1    | Output | В              | none                                                             | none          | none           | VDD_DMC      | 0<br>Notes: No notes<br>Desc: DMC1 Bank Address Input                    |

| _           |        |                |                                                                  |               |                |              | 1<br>Notes: No notes                                                     |

Table 27. ADSP-SC58x/ADSP-2158x Designer Quick Reference (Continued)

### **ABSOLUTE MAXIMUM RATINGS**

Stresses at or above those listed in Table 41 may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### Table 41. Absolute Maximum Ratings

| Parameter                                             | Rating                          |

|-------------------------------------------------------|---------------------------------|

| Internal (Core) Supply Voltage (V <sub>DD_INT</sub> ) | -0.33 V to +1.26 V              |

| External (I/O) Supply Voltage                         | –0.33 V to +3.60 V              |

| (V <sub>DD_EXT</sub> )                                |                                 |

| DDR2/LPDDR Controller Supply                          | –0.33 V to +1.90 V              |

| Voltage (V <sub>DD_DMC</sub> )                        |                                 |

| DDR3 Controller Supply Voltage                        | –0.33 V to +1.60 V              |

| (V <sub>DD_DMC</sub> )                                |                                 |

| USB PHY Supply Voltage (V <sub>DD_USB</sub> )         | –0.33 V to +3.60 V              |

| Real Time Clock Supply Voltage                        | –0.33 V to +3.60 V              |

| (V <sub>DD_RTC</sub> )                                |                                 |

| PCIe Transmit Supply Voltage                          | –0.33 V to +1.20 V              |

| (V <sub>DD_PCIE_TX</sub> )                            |                                 |

| PCIe Receive Supply Voltage                           | –0.33 V to +1.20 V              |

| (V <sub>DD_PCIE_RX</sub> )                            |                                 |

| PCIe Supply Voltage (V <sub>DD_PCIE</sub> )           | –0.33 V to +3.60 V              |

| HADC Supply Voltage (V <sub>DD_HADC</sub> )           | –0.33 V to +3.60 V              |

| HADC Reference Voltage (V <sub>HADC_REF</sub> )       | –0.33 V to +3.60 V              |

| DDR2/LPDDR Input Voltage <sup>1</sup>                 | –0.33 V to +1.90 V              |

| DDR3 Input Voltage <sup>1</sup>                       | –0.33 V to +1.60 V              |

| Digital Input Voltage <sup>2, 3</sup>                 | –0.33 V to +3.60 V              |

| Output Voltage Swing                                  | –0.33 V to $V_{DD\_EXT}$ +0.5 V |

| Analog Input Voltage                                  | –0.2 V to V_DD_HADC +0.2 V      |

| Storage Temperature Range                             | –65°C to +150°C                 |

| Junction Temperature While Biased                     | 133°C                           |

$^1Applies only when V_{DD\_DMC}$  is within specifications. When  $_{VDD\_DMC}$  is outside specifications, the range is  $V_{DD\_DMC}\pm0.2$  V.

<sup>2</sup>Applies to 100% transient duty cycle.

$^3Applies only when V_{DD\_EXT}$  is within specifications. When  $V_{DD\_EXT}$  is outside specifications, the range is  $V_{DD\_EXT}\pm0.2$  V.

# **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

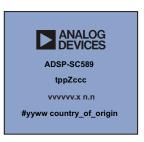

# **PACKAGE INFORMATION**

The information presented in Figure 9 and Table 42 provides details about the package branding for the processors. For a complete listing of product availability, see the Ordering Guide section.

Figure 9. Product Information on Package<sup>1</sup>

<sup>1</sup>Exact brand may differ, depending on package type.

### Table 42. Package Brand Information

| Brand Key  | Field Description                 |

|------------|-----------------------------------|

| ADSP-SC589 | Product name                      |

| t          | Temperature range                 |

| рр         | Package type                      |

| Z          | RoHS compliant option             |

| ссс        | See the Ordering Guide section    |

| VVVVV.X    | Assembly lot code                 |

| n.n        | Silicon revision                  |

| #          | <b>RoHS</b> compliant designation |

| yyww       | Date code                         |

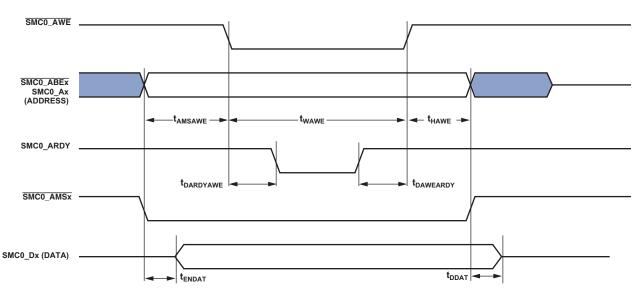

#### **Asynchronous Write**

Table 48 and Figure 15 show asynchronous memory write timing, related to the SMC.

#### Table 48. Asynchronous Memory Write

| Parameter               |                                                           | Min                                          | Max                                   | Unit |

|-------------------------|-----------------------------------------------------------|----------------------------------------------|---------------------------------------|------|

| Timing Requ             | lirement                                                  |                                              |                                       |      |

| t <sub>DARDYAWE</sub> 1 | SMC0_ARDY Valid After SMC0_AWE Low <sup>2</sup>           |                                              | $(WAT - 2.5) \times t_{SCLK0} - 17.5$ | ns   |

| Switching Cl            | haracteristics                                            |                                              |                                       |      |

| t <sub>ENDAT</sub>      | DATA Enable After SMC0_AMSx Assertion                     | -3.5                                         |                                       | ns   |

| t <sub>DDAT</sub>       | DATA Disable After SMC0_AMSx Deassertion                  |                                              | 2.5                                   | ns   |

| t <sub>AMSAWE</sub>     | ADDR/SMC0_AMSx Assertion Before SMC0_AWE Low <sup>3</sup> | $(PREST + WST + PREAT) \times t_{SCLK0} - 2$ |                                       | ns   |

| t <sub>HAWE</sub>       | Output <sup>4</sup> Hold After SMC0_AWE High <sup>5</sup> | WHT $\times$ t <sub>SCLK0</sub> – 3.5        |                                       | ns   |

| t <sub>WAWE</sub> 6     | SMC0_AWE Active Low Width <sup>2</sup>                    | WAT $\times$ t <sub>SCLK0</sub> – 2          |                                       | ns   |

| t <sub>DAWEARDY</sub> 1 | SMC0_AWE High Delay After SMC0_ARDY Assertion             | $2.5 \times t_{SCLKO}$                       | $3.5 \times t_{SCLK0} + 17.5$         | ns   |

<sup>1</sup>SMC\_BxCTL.ARDYEN bit = 1.

<sup>2</sup>WAT value set using the SMC\_BxTIM.WAT bits.

<sup>3</sup>PREST, WST, PREAT values set using the SMC\_BXETIM.PREST bits, SMC\_BXTIM.WST bits, SMC\_BXETIM.PREAT bits, and the SMC\_BXTIM.RAT bits.

<sup>4</sup>Output signals are DATA, SMC0\_Ax, <u>SMC0\_AMSx</u>, <u>SMC0\_ABEx</u>.

<sup>5</sup>WHT value set using the SMC\_BxTIM.WHT bits.

<sup>6</sup>SMC\_BxCTL.ARDYEN bit = 0.

Figure 15. Asynchronous Write

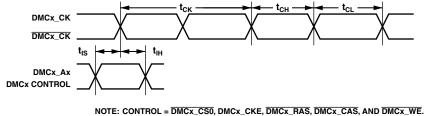

## Mobile DDR (LPDDR) SDRAM Clock and Control Cycle Timing

Table 54 and Figure 20 show mobile DDR SDRAM clock and control cycle timing, related to the DMC.

#### Table 54. Mobile DDR SDRAM Clock and Control Cycle Timing, V<sub>DD\_DMCx</sub> Nominal 1.8 V<sup>1</sup>

|                 |                                                |      | 200 MHz <sup>2</sup> |                 |

|-----------------|------------------------------------------------|------|----------------------|-----------------|

| Parameter       |                                                | Min  | Мах                  | Unit            |

| Switching       | Characteristics                                |      |                      |                 |

| t <sub>CK</sub> | Clock Cycle Time (CL = 2 Not Supported)        | 5    |                      | ns              |

| t <sub>CH</sub> | Minimum Clock Pulse Width                      | 0.45 | 0.55                 | t <sub>CK</sub> |

| t <sub>CL</sub> | Maximum Clock Pulse Width                      | 0.45 | 0.55                 | t <sub>CK</sub> |

| <sup>I</sup> IS | Control/Address Setup Relative to DMCx_CK Rise | 1    |                      | ns              |

| t <sub>IH</sub> | Control/Address Hold Relative to DMCx_CK Rise  | 1    |                      | ns              |

<sup>1</sup>Specifications apply to both DMC0 and DMC1.

<sup>2</sup>To ensure proper operation of LPDDR, all the LPDDR guidelines must be strictly followed. See "Interfacing DDR3/DDR2/LPDDR Memory to ADSP-SC5xx/215xx Processors" (EE-387).

DTE: CONTROL = DMCx\_CS0, DMCx\_CKE, DMCx\_RAS, DMCx\_CAS, AND DMC ADDRESS = DMCx\_A0-A15 AND DMCx\_BA0-BA2.

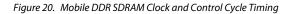

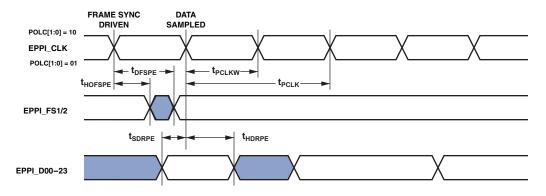

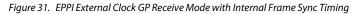

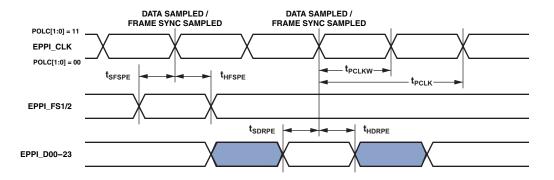

Figure 29. EPPI Internal Clock GP Transmit Mode with External Frame Sync Timing

Figure 30. Clock Gating Mode with Internal Clock and External Frame Sync Timing

| Parameter           |                                    | Min Max                    |      | Unit |

|---------------------|------------------------------------|----------------------------|------|------|

| Timing Re           | quirements                         |                            |      |      |

| t <sub>PCLKW</sub>  | EPPI_CLK Width <sup>1</sup>        | $0.5 \times t_{PCLKEXT}$ – | 0.5  | ns   |

| t <sub>PCLK</sub>   | EPPI_CLK Period <sup>1</sup>       | t <sub>PCLKEXT</sub> – 1   |      | ns   |

| t <sub>SFSPE</sub>  | External FS Setup Before EPPI_CLK  | 2                          |      | ns   |

| t <sub>HFSPE</sub>  | External FS Hold After EPPI_CLK    | 3.7                        |      | ns   |

| t <sub>SDRPE</sub>  | Receive Data Setup Before EPPI_CLK | 2                          |      | ns   |

| t <sub>HDRPE</sub>  | Receive Data Hold After EPPI_CLK   | 3.7                        |      | ns   |

| Switching           | Characteristics                    |                            |      |      |

| t <sub>DFSPE</sub>  | Internal FS Delay After EPPI_CLK   |                            | 15.3 | ns   |

| t <sub>HOFSPE</sub> | Internal FS Hold After EPPI_CLK    | 2.4                        |      | ns   |

| t <sub>DDTPE</sub>  | Transmit Data Delay After EPPI_CLK |                            | 15.3 | ns   |

| t <sub>HDTPE</sub>  | Transmit Data Hold After EPPI_CLK  | 2.4                        |      | ns   |

<sup>1</sup>This specification indicates the minimum instantaneous width or period that can be tolerated due to duty cycle variation or jitter on the external EPPI\_CLK. For the external EPPI\_CLK ideal maximum frequency see the f<sub>PCLKEXT</sub> specification in Table 29.

Figure 32. EPPI External Clock GP Transmit Mode with Internal Frame Sync Timing

Figure 33. EPPI External Clock GP Receive Mode with External Frame Sync Timing

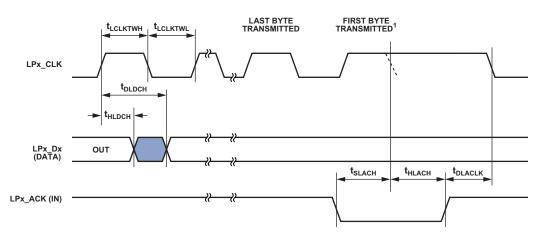

#### Table 63. Link Ports—Transmit<sup>1</sup>

| Parameter                         |                                      | Min                            | Мах                                            | Unit |

|-----------------------------------|--------------------------------------|--------------------------------|------------------------------------------------|------|

| Timing Require                    | ements                               |                                |                                                |      |

| t <sub>SLACH</sub>                | LPx_ACK Setup Before LPx_CLK Low     | $2 \times t_{CLKO8} + 13.5$    |                                                | ns   |

| t <sub>HLACH</sub>                | LPx_ACK Hold After LPx_CLK Low       | -5.5                           |                                                | ns   |

| Switching Cha                     | racteristics                         |                                |                                                |      |

| t <sub>DLDCH</sub>                | Data Delay After LPx_CLK High        |                                | 1.6                                            | ns   |

| t <sub>HLDCH</sub>                | Data Hold After LPx_CLK High         | -0.8                           |                                                | ns   |

| t <sub>LCLKTWL</sub> <sup>2</sup> | LPx_CLK Width Low                    | $0.33 \times t_{LCLKTPROG}$    | $0.6 \times t_{LCLKTPROG}$                     | ns   |

| t <sub>LCLKTWH</sub> 2            | LPx_CLK Width High                   | $0.45 \times t_{LCLKTPROG}$    | $0.66 \times t_{LCLKTPROG}$                    | ns   |

| t <sub>LCLKTW</sub> <sup>2</sup>  | LPx_CLK Period                       | $N \times t_{LCLKTPROG} - 0.5$ |                                                | ns   |

| t <sub>DLACLK</sub>               | LPx_CLK Low Delay After LPx_ACK High | t <sub>CLKO8</sub> + 4         | $2 \times t_{CLKO8} + 1 \times t_{LPCLK} + 10$ | ns   |

<sup>1</sup>Specifications apply to LP0 and LP1.

$^2$  See Table 29 for details on the minimum period that can be programmed for t<sub>LCLKTPROG</sub>.

The t<sub>sLACH</sub> and t<sub>HLACH</sub> specifications apply only to the LPx\_CLK falling edge. If these specifications are met, LPx\_CLK would extend and the dotted LPx\_CLK falling edge would not occur as shown. The position of the dotted falling edge can be calculated using the t<sub>LCLKTWH</sub> specification. t<sub>LCLKTWH</sub> Min should be used for t<sub>sLACH</sub> and t<sub>LCLKTWH</sub> Max for t<sub>HLACH</sub>.

Figure 36. Link Ports—Transmit

Figure 37. Serial Ports

#### General-Purpose I/O Port Timing

Table 78 and Figure 51 describe I/O timing, related to the general-purpose I/O port (PORT).

#### Table 78. General-Purpose Port Timing

| Paramete         | er                                         | Min                        | Мах | Unit |

|------------------|--------------------------------------------|----------------------------|-----|------|

| Timing Rea       | quirement                                  |                            |     |      |

| t <sub>WFI</sub> | General-Purpose Port Pin Input Pulse Width | $2 \times t_{SCLK0} - 1$ . | 5   | ns   |

Figure 51. General-Purpose Port Timing

## General-Purpose I/O Timer Cycle Timing

Table 79, Table 80, and Figure 52 describe timer expired operations related to the general-purpose timer (TIMER). The input signal is asynchronous in Width Capture Mode and External Clock Mode and has an absolute maximum input frequency of  $f_{SCLK}/4$  MHz. The Width Value value is the timer period assigned in the TMx\_TMRn\_WIDTH register and can range from 1 to  $2^{32} - 1$ . When externally generated, the TMx\_CLK clock is called  $f_{TMRCLKEXT}$ :

$t_{TMRCLKEXT} = \frac{1}{f_{TMRCLKEXT}}$

#### Table 79. Timer Cycle Timing (Internal Mode)

| Parameter                                                                           |                                                                    | Min                             | Мах                             | Unit |

|-------------------------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------|---------------------------------|------|

| Timing Re                                                                           | quirements                                                         |                                 |                                 |      |

| t <sub>WL</sub>                                                                     | Timer Pulse Width Input Low (Measured In SCLK Cycles) <sup>1</sup> | $2 \times t_{SCLK}$             |                                 | ns   |

| t <sub>WH</sub> Timer Pulse Width Input High (Measured In SCLK Cycles) <sup>1</sup> |                                                                    | $2 \times t_{SCLK}$             |                                 | ns   |

| Switching                                                                           | Characteristic                                                     |                                 |                                 |      |

| t <sub>HTO</sub>                                                                    | Timer Pulse Width Output (Measured In SCLK Cycles) <sup>2</sup>    | t <sub>SCLK</sub> × WIDTH – 1.5 | t <sub>SCLK</sub> × WIDTH + 1.5 | ns   |

<sup>1</sup>The minimum pulse width applies for timer signals in width capture and external clock modes.

<sup>2</sup>WIDTH refers to the value in the TMRx\_WIDTH register (it can vary from 1 to 2<sup>32</sup> - 1).

#### Table 80. Timer Cycle Timing (External Mode)

| Parameter            |                                                                        | Min                                | Max                                | Unit |  |

|----------------------|------------------------------------------------------------------------|------------------------------------|------------------------------------|------|--|

| Timing Requ          | Timing Requirements                                                    |                                    |                                    |      |  |

| t <sub>WL</sub>      | Timer Pulse Width Input Low (Measured In EXT_CLK Cycles) <sup>1</sup>  | $2 \times t_{EXT_{CLK}}$           |                                    | ns   |  |

| t <sub>WH</sub>      | Timer Pulse Width Input High (Measured In EXT_CLK Cycles) <sup>1</sup> | $2 \times t_{EXT_{CLK}}$           |                                    | ns   |  |

| t <sub>EXT_CLK</sub> | Timer External Clock Period <sup>2</sup>                               | t <sub>TMRCLKEXT</sub>             |                                    | ns   |  |

| Switching Ch         | naracteristic                                                          |                                    |                                    |      |  |

| t <sub>HTO</sub>     | Timer Pulse Width Output (Measured In EXT_CLK Cycles) <sup>3</sup>     | t <sub>EXT_CLK</sub> × WIDTH – 1.5 | t <sub>EXT_CLK</sub> × WIDTH + 1.5 | ns   |  |

<sup>1</sup>The minimum pulse width applies for timer signals in width capture and external clock modes.

<sup>2</sup> This specification indicates the minimum instantaneous width or period that can be tolerated due to duty cycle variation or jitter on the external TMR\_CLK. For the external TMR\_CLK maximum frequency see the f<sub>TMRCLKEXT</sub> specification in Table 29.

<sup>3</sup>WIDTH refers to the value in the TMRx\_WIDTH register (it can vary from 1 to  $2^{32} - 1$ ).

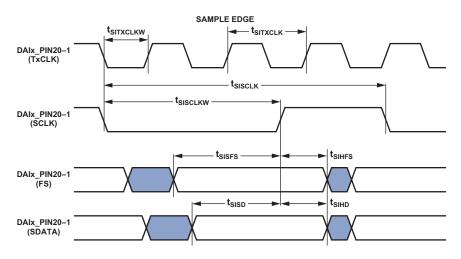

### S/PDIF Transmitter Input Data Timing

The timing requirements for the S/PDIF transmitter are given in Table 96. Input signals are routed to the DAIx\_PINx pins using the SRU. Therefore, the timing specifications provided below are valid at the DAIx\_PINx pins.

| Table 96. | S/PDIF | Transmitter | Input | Data | Timing |

|-----------|--------|-------------|-------|------|--------|

|-----------|--------|-------------|-------|------|--------|

| Paramete                        | Parameter                                        |    | Max | Unit |

|---------------------------------|--------------------------------------------------|----|-----|------|

| Timing Req                      | uirements                                        |    |     |      |

| t <sub>SISFS</sub> <sup>1</sup> | Frame Sync Setup Before Serial Clock Rising Edge | 3  |     | ns   |

| t <sub>SIHFS</sub> 1            | Frame Sync Hold After Serial Clock Rising Edge   | 3  |     | ns   |

| t <sub>SISD</sub> 1             | Data Setup Before Serial Clock Rising Edge       | 3  |     | ns   |

| t <sub>SIHD</sub> 1             | Data Hold After Serial Clock Rising Edge         | 3  |     | ns   |

| t <sub>SITXCLKW</sub>           | Transmit Clock Width                             | 9  |     | ns   |

| t <sub>SITXCLK</sub>            | Transmit Clock Period                            | 20 |     | ns   |

| t <sub>SISCLKW</sub>            | Clock Width                                      | 36 |     | ns   |

| t <sub>SISCLK</sub>             | Clock Period                                     | 80 |     | ns   |

<sup>1</sup>The serial clock, data, and frame sync signals can come from any of the DAI pins. The serial clock and frame sync signals can also come via PCG or SPORTs. The input of the PCG can be either CLKIN or any of the DAI pins.

Figure 67. S/PDIF Transmitter Input Timing

### **Oversampling Clock (TxCLK) Switching Characteristics**

The S/PDIF transmitter requires an oversampling clock input. This high frequency clock (TxCLK) input is divided down to generate the internal biphase clock.

| Table 97. | Oversampling | Clock (TxCLK) | Switching Characteristics |

|-----------|--------------|---------------|---------------------------|

|-----------|--------------|---------------|---------------------------|

| Parameter              |                                               | Мах                                                  | Unit |

|------------------------|-----------------------------------------------|------------------------------------------------------|------|

| Switching Cha          | racteristics                                  |                                                      |      |