### Renesas Electronics America Inc - R5F21272SNFP#V2 Datasheet

Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | R8C                                                                              |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 20MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, LINbus, SIO, SSU, UART/USART                                   |

| Peripherals                | LED, POR, Voltage Detect, WDT                                                    |

| Number of I/O              | 25                                                                               |

| Program Memory Size        | 8KB (8K x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | 2K x 8                                                                           |

| RAM Size                   | 512 x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.2V ~ 5.5V                                                                      |

| Data Converters            | A/D 12x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -20°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 32-LQFP                                                                          |

| Supplier Device Package    | 32-LQFP (7x7)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f21272snfp-v2 |

Email: info@E-XFL.COM

# R8C/26 Group, R8C/27 Group SINGLE-CHIP 16-BIT CMOS MCU

REJ03B0168-0210 Rev.2.10 Sep 26, 2008

#### 1. **Overview**

These MCUs are fabricated using a high-performance silicon gate CMOS process, embedding the R8C CPU core, and are packaged in a 32-pin molded-plastic LQFP. It implements sophisticated instructions for a high level of instruction efficiency. With 1 Mbyte of address space, they are capable of executing instructions at high speed.

Furthermore, the R8C/27 Group has on-chip data flash (1 KB  $\times$  2 blocks).

The difference between the R8C/26 Group and R8C/27 Group is only the presence or absence of data flash. Their peripheral functions are the same.

#### 1.1 **Applications**

Electronic household appliances, office equipment, audio equipment, consumer products, automotive, etc.

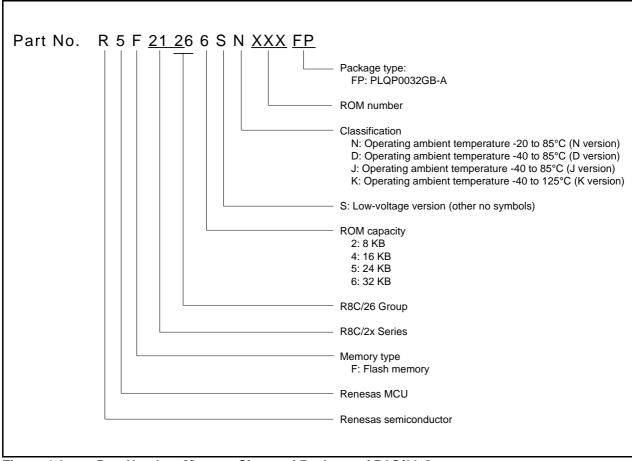

Figure 1.2 Part Number, Memory Size, and Package of R8C/26 Group

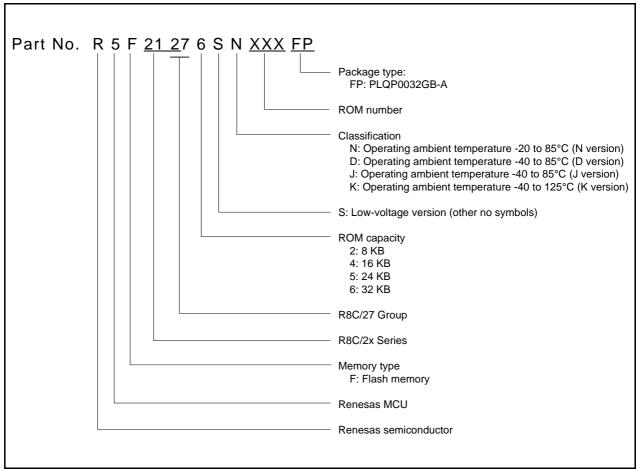

Figure 1.3 Part Number, Memory Size, and Package of R8C/27 Group

### 1.5 Pin Assignments

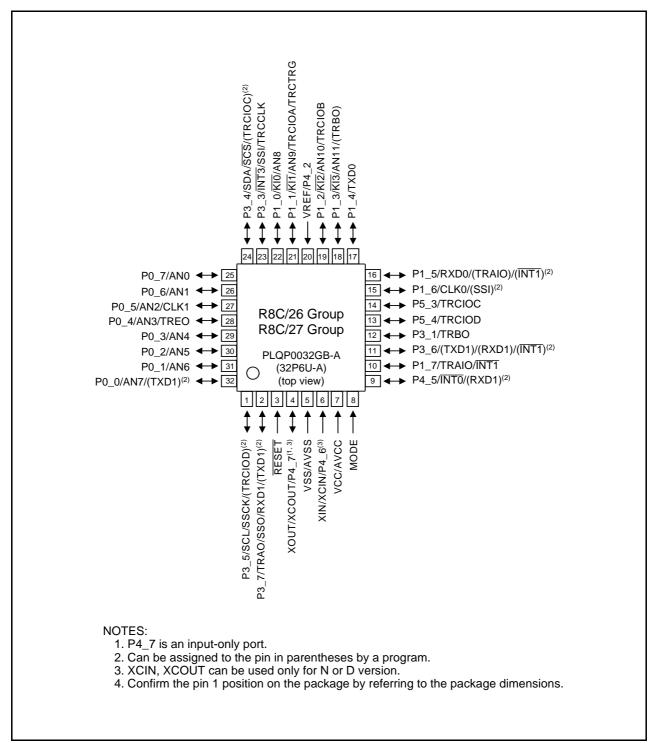

Figure 1.4 shows Pin Assignments (Top View).

Figure 1.4 Pin Assignments (Top View)

#### 2. **Central Processing Unit (CPU)**

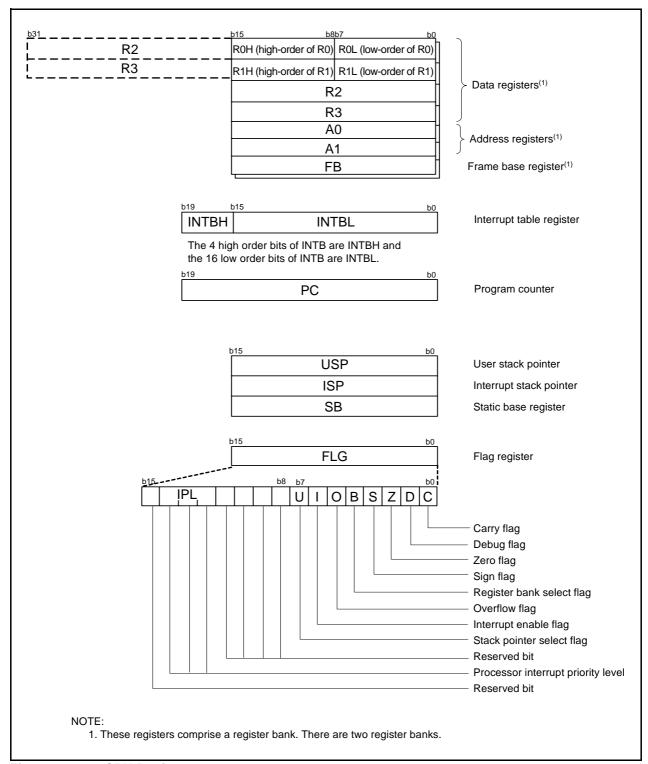

Figure 2.1 shows the CPU Registers. The CPU contains 13 registers. R0, R1, R2, R3, A0, A1, and FB configure a register bank. There are two sets of register bank.

Figure 2.1 **CPU Registers**

## 3. Memory

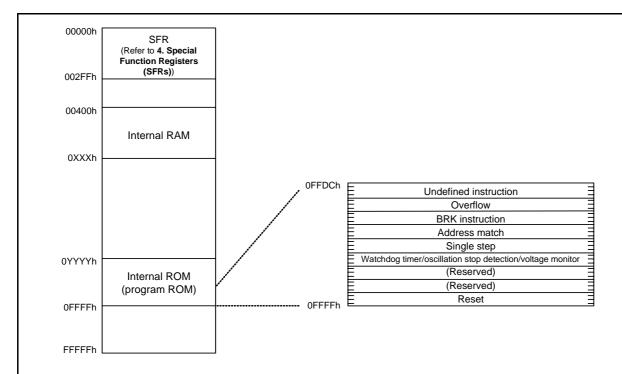

### 3.1 R8C/26 Group

Figure 3.1 is a Memory Map of R8C/26 Group. The R8C/26 group has 1 Mbyte of address space from addresses 00000h to FFFFFh.

The internal ROM is allocated lower addresses, beginning with address 0FFFFh. For example, a 16-Kbyte internal ROM area is allocated addresses 0C000h to 0FFFFh.

The fixed interrupt vector table is allocated addresses 0FFDCh to 0FFFFh. They store the starting address of each interrupt routine.

The internal RAM is allocated higher addresses beginning with address 00400h. For example, a 1-Kbyte internal RAM area is allocated addresses 00400h to 007FFh. The internal RAM is used not only for storing data but also for calling subroutines and as stacks when interrupt requests are acknowledged.

Special function registers (SFRs) are allocated addresses 00000h to 002FFh. The peripheral function control registers are allocated here. All addresses within the SFR, which have nothing allocated are reserved for future use and cannot be accessed by users.

#### NOTE:

1. The blank regions are reserved. Do not access locations in these regions.

| Part Number                       | Inte      | rnal ROM       | Internal RAM |                |  |

|-----------------------------------|-----------|----------------|--------------|----------------|--|

| Fait Number                       | Size      | Address 0YYYYh | Size         | Address 0XXXXh |  |

| R5F21262SNFP, R5F21262SDFP,       | 8 Kbytes  | 0E000h         | 512 bytes    | 005FFh         |  |

| R5F21262SNXXXFP, R5F21262SDXXXFP  | o Royles  | OLOGOTI        | 312 bytes    | 0031111        |  |

| R5F21264SNFP, R5F21264SDFP,       |           |                |              |                |  |

| R5F21264JFP, R5F21264KFP,         | 16 Kbytes | 0C000h         | 1 Kbyte      | 007FFh         |  |

| R5F21264SNXXXFP, R5F21264SDXXXFP, | TO Royles |                |              | 0071111        |  |

| R5F21264JXXXFP, R5F21264KXXXFP    |           |                |              |                |  |

| R5F21265SNFP, R5F21265SDFP        | 24 Kbytes | 0A000h         | 1.5 Kbytes   | 009FFh         |  |

| R5F21265SNXXXFP, R5F21265SDXXXFP  | 24 Noytes | UAUUUII        | 1.5 Rbytes   | 0091111        |  |

| R5F21266SNFP, R5F21266SDFP,       |           |                |              |                |  |

| R5F21266JFP, R5F21266KFP,         | 32 Kbytes | 08000h         | 1.5 Kbytes   | 009FFh         |  |

| R5F21266SNXXXFP, R5F21266SDXXXFP, | 32 Royles | 0000011        | 1.5 Rbytes   | 0031111        |  |

| R5F21266JXXXFP, R5F21266KXXXFP    |           |                |              |                |  |

Figure 3.1 Memory Map of R8C/26 Group

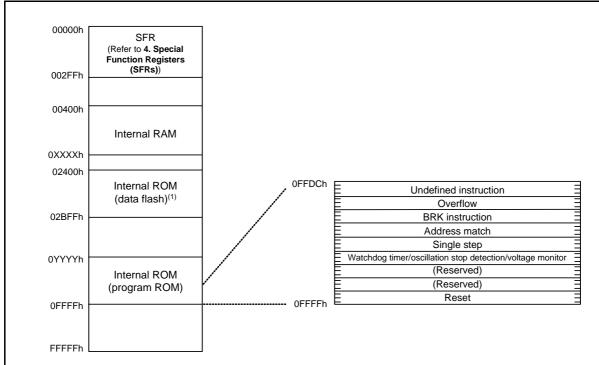

#### 3.2 R8C/27 Group

Figure 3.2 is a Memory Map of R8C/27 Group. The R8C/27 group has 1 Mbyte of address space from addresses 00000h to FFFFFh.

The internal ROM (program ROM) is allocated lower addresses, beginning with address 0FFFFh. For example, a 16-Kbyte internal ROM area is allocated addresses 0C000h to 0FFFFh.

The fixed interrupt vector table is allocated addresses 0FFDCh to 0FFFFh. They store the starting address of each interrupt routine.

The internal ROM (data flash) is allocated addresses 02400h to 02BFFh.

The internal RAM area is allocated higher addresses, beginning with address 00400h. For example, a 1-Kbyte internal RAM is allocated addresses 00400h to 007FFh. The internal RAM is used not only for storing data but also for calling subroutines and as stacks when interrupt requests are acknowledged.

Special function registers (SFRs) are allocated addresses 00000h to 002FFh. The peripheral function control registers are allocated here. All addresses within the SFR, which have nothing allocated are reserved for future use and cannot be accessed by users.

- 1. Data flash block A (1 Kbyte) and B (1 Kbyte) are shown.

- 2. The blank regions are reserved. Do not access locations in these regions.

| Dord Mosek en                     | Internal ROM |                | Internal RAM |                |  |

|-----------------------------------|--------------|----------------|--------------|----------------|--|

| Part Number                       | Size         | Address 0YYYYh | Size         | Address 0XXXXh |  |

| R5F21272SNFP, R5F21272SDFP,       | 0 Khyton     | 0E000h         | E12 bytes    | 005FFh         |  |

| R5F21272SNXXXFP, R5F21272SDXXXFP  | 8 Kbytes     | 000011         | 512 bytes    | 003FFII        |  |

| R5F21274SNFP, R5F21274SDFP,       |              |                |              |                |  |

| R5F21274JFP, R5F21274KFP,         | 16 Khytos    | 0C000h         | 1 Kbyte      | 007FFh         |  |

| R5F21274SNXXXFP, R5F21274SDXXXFP, | 16 Kbytes    |                |              | 0077711        |  |

| R5F21274JXXXFP, R5F21274KXXXFP    |              |                |              |                |  |

| R5F21275SNFP, R5F21275SDFP,       | 24 Kbytes    | 0A000h         | 1.5 Kbytes   | 009FFh         |  |

| R5F21275SNXXXFP, R5F21275SDXXXFP  | 24 Kbytes    | UAUUUII        | 1.5 Kbytes   | 009FFII        |  |

| R5F21276SNFP, R5F21276SDFP,       |              |                |              |                |  |

| R5F21276JFP, R5F21276KFP,         | 32 Kbytes    | 08000h         | 1 E Khyton   | 009FFh         |  |

| R5F21276SNXXXFP, R5F21276SDXXXFP, | 32 Kbytes    | 0000011        | 1.5 Kbytes   | 009FFII        |  |

| R5F21276JXXXFP, R5F21276KXXXFP    |              |                |              |                |  |

Figure 3.2 Memory Map of R8C/27 Group

| Table 5.3 A/I | Converter Converter | Characteristics |

|---------------|---------------------|-----------------|

|---------------|---------------------|-----------------|

| Cumbal  | Parameter          |                         | Conditions                        | Standard |      |      | Unit  |

|---------|--------------------|-------------------------|-----------------------------------|----------|------|------|-------|

| Symbol  | '                  | Parameter               | Conditions                        | Min.     | Тур. | Max. | Offic |

| -       | Resolution         |                         | Vref = AVCC                       | -        | -    | 10   | Bits  |

| _       | Absolute           | 10-bit mode             | φAD = 10 MHz, Vref = AVCC = 5.0 V | _        | -    | ±3   | LSB   |

|         | accuracy           | 8-bit mode              | φAD = 10 MHz, Vref = AVCC = 5.0 V | -        | -    | ±2   | LSB   |

|         |                    | 10-bit mode             | φAD = 10 MHz, Vref = AVCC = 3.3 V | -        | -    | ±5   | LSB   |

|         |                    | 8-bit mode              | φAD = 10 MHz, Vref = AVCC = 3.3 V | -        | -    | ±2   | LSB   |

|         |                    | 10-bit mode             | φAD = 5 MHz, Vref = AVCC = 2.2 V  | -        | -    | ±5   | LSB   |

|         |                    | 8-bit mode              | φAD = 5 MHz, Vref = AVCC = 2.2 V  | -        | -    | ±2   | LSB   |

| Rladder | Resistor ladder    |                         | Vref = AVCC                       | 10       | -    | 40   | kΩ    |

| tconv   | Conversion time    | 10-bit mode             | φAD = 10 MHz, Vref = AVCC = 5.0 V | 3.3      | =    | _    | μS    |

|         |                    | 8-bit mode              | φAD = 10 MHz, Vref = AVCC = 5.0 V | 2.8      | -    | _    | μS    |

| Vref    | Reference voltag   | e                       |                                   | 2.2      | -    | AVcc | V     |

| VIA     | Analog input volta | age <sup>(2)</sup>      |                                   | 0        | =    | AVcc | V     |

| -       | A/D operating      | Without sample and hold | Vref = AVCC = 2.7 to 5.5 V        | 0.25     | -    | 10   | MHz   |

|         | clock frequency    | With sample and hold    | Vref = AVCC = 2.7 to 5.5 V        | 1        | -    | 10   | MHz   |

|         |                    | Without sample and hold | Vref = AVCC = 2.2 to 5.5 V        | 0.25     | -    | 5    | MHz   |

|         |                    | With sample and hold    | Vref = AVCC = 2.2 to 5.5 V        | 1        | -    | 5    | MHz   |

- 1. AVcc = 2.2 to 5.5 V at Topr = -20 to 85°C (N version) / -40 to 85°C (D version), unless otherwise specified.

- 2. When the analog input voltage is over the reference voltage, the A/D conversion result will be 3FFh in 10-bit mode and FFh in 8-bit mode.

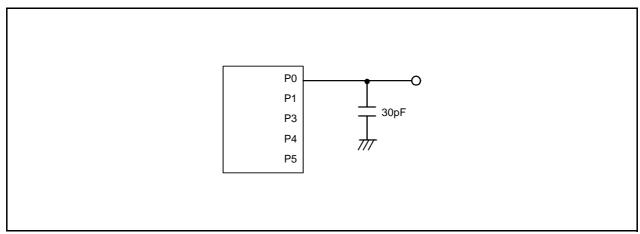

Figure 5.1 Ports P0, P1, and P3 to P5 Timing Measurement Circuit

Table 5.5 Flash Memory (Data flash Block A, Block B) Electrical Characteristics<sup>(4)</sup>

| Symbol     | Parameter                                                           | Conditions                 |                    | Unit |                              |       |

|------------|---------------------------------------------------------------------|----------------------------|--------------------|------|------------------------------|-------|

| Symbol     | Farameter                                                           | Conditions                 | Min.               | Тур. | Max.                         | Offic |

| =          | Program/erase endurance <sup>(2)</sup>                              |                            | 10,000(3)          | -    | _                            | times |

| _          | Byte program time (program/erase endurance ≤ 1,000 times)           |                            | -                  | 50   | 400                          | μS    |

| _          | Byte program time (program/erase endurance > 1,000 times)           |                            | -                  | 65   | _                            | μS    |

| _          | Block erase time (program/erase endurance ≤ 1,000 times)            |                            | -                  | 0.2  | 9                            | S     |

| _          | Block erase time (program/erase endurance > 1,000 times)            |                            | -                  | 0.3  | _                            | S     |

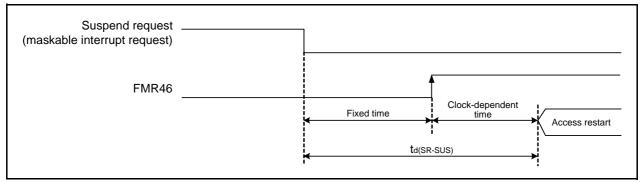

| td(SR-SUS) | Time delay from suspend request until suspend                       |                            | -                  | -    | 97 + CPU clock<br>× 6 cycles | μS    |

| _          | Interval from erase start/restart until following suspend request   |                            | 650                | =    | _                            | μS    |

| _          | Interval from program start/restart until following suspend request |                            | 0                  | -    | _                            | ns    |

| =          | Time from suspend until program/erase restart                       |                            | -                  | -    | 3 + CPU clock<br>× 4 cycles  | μS    |

| =          | Program, erase voltage                                              |                            | 2.7                | -    | 5.5                          | V     |

| =          | Read voltage                                                        |                            | 2.2                | -    | 5.5                          | V     |

| -          | Program, erase temperature                                          |                            | -20 <sup>(8)</sup> | _    | 85                           | °C    |

| _          | Data hold time <sup>(9)</sup>                                       | Ambient temperature = 55°C | 20                 | _    | _                            | year  |

- 1. Vcc = 2.7 to 5.5 V at Topr = -20 to 85°C (N version) / -40 to 85°C (D version), unless otherwise specified.

- 2. Definition of programming/erasure endurance

- The programming and erasure endurance is defined on a per-block basis.

If the programming and erasure endurance is n (n = 10,000), each block can be erased n times. For example, if 1,024 1-byte writes are performed to different addresses in block A, a 1 Kbyte block, and then the block is erased, the programming/erasure endurance still stands at one.

However, the same address must not be programmed more than once per erase operation (overwriting prohibited).

- 3. Endurance to guarantee all electrical characteristics after program and erase. (1 to Min. value can be guaranteed).

- 4. Standard of block A and block B when program and erase endurance exceeds 1,000 times. Byte program time to 1,000 times is the same as that in program ROM.

- 5. In a system that executes multiple programming operations, the actual erasure count can be reduced by writing to sequential addresses in turn so that as much of the block as possible is used up before performing an erase operation. For example, when programming groups of 16 bytes, the effective number of rewrites can be minimized by programming up to 128 groups before erasing them all in one operation. In addition, averaging the erasure endurance between blocks A and B can further reduce the actual erasure endurance. It is also advisable to retain data on the erasure endurance of each block and limit the number of erase operations to a certain number.

- 6. If an error occurs during block erase, attempt to execute the clear status register command, then execute the block erase command at least three times until the erase error does not occur.

- 7. Customers desiring program/erase failure rate information should contact their Renesas technical support representative.

- 8. -40°C for D version.

- 9. The data hold time includes time that the power supply is off or the clock is not supplied.

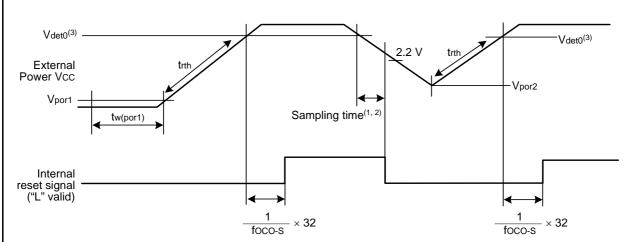

| Table 5.9 Power-on Reset Circuit, Voltage Monitor 0 Reset Electrical Characteristic |

|-------------------------------------------------------------------------------------|

|-------------------------------------------------------------------------------------|

| Svmbol | Parameter                                               | Condition |      | Unit |       |         |

|--------|---------------------------------------------------------|-----------|------|------|-------|---------|

| Symbol | Farameter                                               | Condition | Min. | Тур. | Max.  | Offic   |

| Vpor1  | Power-on reset valid voltage <sup>(4)</sup>             |           | -    | -    | 0.1   | V       |

| Vpor2  | Power-on reset or voltage monitor 0 reset valid voltage |           | 0    | _    | Vdet0 | V       |

| trth   | External power Vcc rise gradient(2)                     |           | 20   | -    | -     | mV/msec |

- 1. The measurement condition is  $T_{OPT}$  = -20 to 85°C (N version) / -40 to 85°C (D version), unless otherwise specified.

- 2. This condition (external power Vcc rise gradient) does not apply if Vcc ≥ 1.0 V.

- 3. To use the power-on reset function, enable voltage monitor 0 reset by setting the LVD0ON bit in the OFS register to 0, the VW0C0 and VW0C6 bits in the VW0C register to 1 respectively, and the VCA25 bit in the VCA2 register to 1.

- 4. tw(por1) indicates the duration the external power Vcc must be held below the effective voltage (Vpor1) to enable a power on reset. When turning on the power for the first time, maintain tw(por1) for 30 s or more if -20°C ≤ Topr ≤ 85°C, maintain tw(por1) for 3,000 s or more if -40°C ≤ Topr < -20°C.</p>

- 1. When using the voltage monitor 0 digital filter, ensure that the voltage is within the MCU operation voltage range (2.2 V or above) during the sampling time.

- 2. The sampling clock can be selected. Refer to 6. Voltage Detection Circuit of Hardware Manual for details.

- 3. Vdeto indicates the voltage detection level of the voltage detection 0 circuit. Refer to 6. Voltage Detection Circuit of Hardware Manual for details.

Figure 5.3 Reset Circuit Electrical Characteristics

**Table 5.10 High-speed On-Chip Oscillator Circuit Electrical Characteristics**

| Courada a l | Davarantas                                                                      | Condition                                                                               |                    | Standard |                    | I India |  |

|-------------|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------|----------|--------------------|---------|--|

| Symbol      | Parameter                                                                       | Condition                                                                               |                    | Тур.     | Max.               | Unit    |  |

| fOCO40M     | High-speed on-chip oscillator frequency temperature • supply voltage dependence | Vcc = 4.75  to  5.25  V<br>$0^{\circ}C \leq T_{opr} \leq 60^{\circ}C^{(2)}$             | 39.2               | 40       | 40.8               | MHz     |  |

|             |                                                                                 | Vcc = 3.0 to 5.5 V<br>-20°C $\leq$ Topr $\leq$ 85°C <sup>(2)</sup>                      | 38.8               | 40       | 41.2               | MHz     |  |

|             |                                                                                 | Vcc = 3.0 to 5.5 V<br>-40°C $\leq$ Topr $\leq$ 85°C <sup>(2)</sup>                      | 38.4               | 40       | 41.6               | MHz     |  |

|             |                                                                                 | Vcc = 2.7 to 5.5 V<br>-20°C $\leq$ Topr $\leq$ 85°C <sup>(2)</sup>                      | 38                 | 40       | 42                 | MHz     |  |

|             |                                                                                 | Vcc = 2.7 to 5.5 V<br>-40°C $\leq$ Topr $\leq$ 85°C(2)                                  | 37.6               | 40       | 42.4               | MHz     |  |

|             |                                                                                 | Vcc = 2.2 to 5.5 V<br>$-20^{\circ}$ C $\leq$ Topr $\leq$ 85 $^{\circ}$ C <sup>(3)</sup> | 35.2               | 40       | 44.8               | MHz     |  |

|             |                                                                                 | Vcc = 2.2 to 5.5 V<br>-40°C $\leq$ Topr $\leq$ 85°C(3)                                  | 34                 | 40       | 46                 | MHz     |  |

|             |                                                                                 | $Vcc = 5.0 V \pm 10\%$<br>-20°C \le Topr \le 85°C <sup>(2)</sup>                        | 38.8               | 40       | 40.8               | MHz     |  |

|             |                                                                                 | $Vcc = 5.0 V \pm 10\%$<br>-40°C \le Topr \le 85°C(2)                                    | 38.4               | 40       | 40.8               | MHz     |  |

|             | High-speed on-chip oscillator frequency when                                    | Vcc = 5.0 V, Topr = 25°C                                                                | -                  | 36.864   | _                  | MHz     |  |

|             | correction value in FRA7 register is written to FRA1 register <sup>(4)</sup>    | Vcc = 3.0  to  5.5  V<br>-20°C \le Topr \le 85°C                                        | -3%                | -        | 3%                 | %       |  |

| _           | Value in FRA1 register after reset                                              |                                                                                         | 08h <sup>(3)</sup> | -        | F7h <sup>(3)</sup> | -       |  |

| _           | Oscillation frequency adjustment unit of high-<br>speed on-chip oscillator      | Adjust FRA1 register (value after reset) to -1                                          | -                  | +0.3     | -                  | MHz     |  |

| _           | Oscillation stability time                                                      |                                                                                         | -                  | 10       | 100                | μS      |  |

| _           | Self power consumption at oscillation                                           | Vcc = 5.0 V, Topr = 25°C                                                                | -                  | 400      | _                  | μΑ      |  |

- 1. Vcc = 2.2 to 5.5 V,  $T_{opr} = -20$  to  $85^{\circ}C$  (N version) / -40 to  $85^{\circ}C$  (D version), unless otherwise specified.

- 2. These standard values show when the FRA1 register value after reset is assumed.

- 3. These standard values show when the corrected value of the FRA6 register is written to the FRA1 register.

- 4. This enables the setting errors of bit rates such as 9600 bps and 38400 bps to be 0% when the serial interface is used in UART mode.

**Table 5.11** Low-speed On-Chip Oscillator Circuit Electrical Characteristics

| Symbol | Parameter                              | Condition                |      | Unit |      |      |

|--------|----------------------------------------|--------------------------|------|------|------|------|

| Symbol | Farameter                              | Condition                | Min. | Тур. | Max. | Unit |

| fOCO-S | Low-speed on-chip oscillator frequency |                          | 30   | 125  | 250  | kHz  |

| _      | Oscillation stability time             |                          | -    | 10   | 100  | μS   |

| _      | Self power consumption at oscillation  | Vcc = 5.0 V, Topr = 25°C | -    | 15   | -    | μА   |

#### NOTE:

1. Vcc = 2.2 to 5.5 V,  $T_{opr} = -20$  to  $85^{\circ}C$  (N version) / -40 to  $85^{\circ}C$  (D version), unless otherwise specified.

**Table 5.12 Power Supply Circuit Timing Characteristics**

| Symbol   | Parameter                                                                   | Condition | ,    | Unit |      |       |

|----------|-----------------------------------------------------------------------------|-----------|------|------|------|-------|

| Syllibol | Symbol Parameter                                                            |           | Min. | Тур. | Max. | Offic |

| td(P-R)  | Time for internal power supply stabilization during power-on <sup>(2)</sup> |           | 1    | =    | 2000 | μS    |

| td(R-S)  | STOP exit time <sup>(3)</sup>                                               |           | =    | =    | 150  | μS    |

- 1. The measurement condition is Vcc = 2.2 to 5.5 V and Topr = 25°C.

- 2. Waiting time until the internal power supply generation circuit stabilizes during power-on.

- 3. Time until system clock supply starts after the interrupt is acknowledged to exit stop mode.

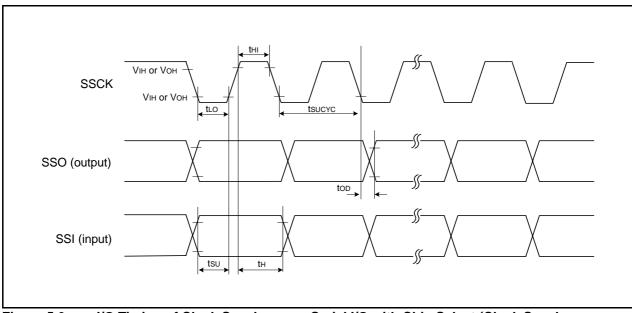

Figure 5.6 I/O Timing of Clock Synchronous Serial I/O with Chip Select (Clock Synchronous Communication Mode)

Table 5.17 Electrical Characteristics (3) [Vcc = 5 V] (Topr = -20 to 85°C (N version) / -40 to 85°C (D version), unless otherwise specified.)

| Symbol   | Parameter                                                                                               |           | Condition                                                                                                                                                                                                | ;    | Standar | d    | Unit  |

|----------|---------------------------------------------------------------------------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|------|-------|

| Syllibol | Farameter                                                                                               |           | Condition                                                                                                                                                                                                | Min. | Тур.    | Max. | Ullit |

| Icc      | Power supply current (Vcc = 3.3 to 5.5 V)<br>Single-chip mode, output pins are open, other pins are Vss | Wait mode | XIN clock off High-speed on-chip oscillator off Low-speed on-chip oscillator on = 125 kHz While a WAIT instruction is executed Peripheral clock operation VCA27 = VCA26 = VCA25 = 0 VCA20 = 1            | -    | 25      | 75   | μА    |

|          |                                                                                                         |           | XIN clock off High-speed on-chip oscillator off Low-speed on-chip oscillator on = 125 kHz While a WAIT instruction is executed Peripheral clock off VCA27 = VCA26 = VCA25 = 0 VCA20 = 1                  | _    | 23      | 60   | μА    |

|          |                                                                                                         |           | XIN clock off High-speed on-chip oscillator off Low-speed on-chip oscillator off XCIN clock oscillator on = 32 kHz (high drive) While a WAIT instruction is executed VCA27 = VCA26 = VCA25 = 0 VCA20 = 1 | _    | 4.0     | -    | μА    |

|          |                                                                                                         |           | XIN clock off High-speed on-chip oscillator off Low-speed on-chip oscillator off XCIN clock oscillator on = 32 kHz (low drive) While a WAIT instruction is executed VCA27 = VCA26 = VCA25 = 0 VCA20 = 1  | _    | 2.2     | -    | μА    |

|          |                                                                                                         | Stop mode | XIN clock off, Topr = 25°C High-speed on-chip oscillator off Low-speed on-chip oscillator off CM10 = 1 Peripheral clock off VCA27 = VCA26 = VCA25 = 0                                                    | _    | 0.8     | 3.0  | μА    |

|          |                                                                                                         |           | XIN clock off, Topr = 85°C High-speed on-chip oscillator off Low-speed on-chip oscillator off CM10 = 1 Peripheral clock off VCA27 = VCA26 = VCA25 = 0                                                    | _    | 1.2     | _    | μА    |

**Table 5.37** Flash Memory (Program ROM) Electrical Characteristics

| Symbol     | Parameter                                 | Conditions                 | Standa             |      | ard            | Unit  |  |

|------------|-------------------------------------------|----------------------------|--------------------|------|----------------|-------|--|

| Symbol     | Farameter                                 | Coriditions                | Min.               | Тур. | Max.           | Offic |  |

| =          | Program/erase endurance <sup>(2)</sup>    | R8C/26 Group               | 100 <sup>(3)</sup> | =    | =              | times |  |

|            |                                           | R8C/27 Group               | 1,000(3)           | -    | -              | times |  |

| _          | Byte program time                         |                            | -                  | 50   | 400            | μS    |  |

| _          | Block erase time                          |                            | -                  | 0.4  | 9              | S     |  |

| td(SR-SUS) | Time delay from suspend request until     |                            | =                  | -    | 97 + CPU clock | μS    |  |

|            | suspend                                   |                            |                    |      | × 6 cycles     |       |  |

| _          | Interval from erase start/restart until   |                            | 650                | _    | -              | μS    |  |

|            | following suspend request                 |                            |                    |      |                |       |  |

| _          | Interval from program start/restart until |                            | 0                  | _    | _              | ns    |  |

|            | following suspend request                 |                            |                    |      |                |       |  |

| _          | Time from suspend until program/erase     |                            | -                  | =    | 3 + CPU clock  | μS    |  |

|            | restart                                   |                            |                    |      | × 4 cycles     |       |  |

| =          | Program, erase voltage                    |                            | 2.7                | -    | 5.5            | V     |  |

| =          | Read voltage                              |                            | 2.7                | -    | 5.5            | V     |  |

| =          | Program, erase temperature                |                            | 0                  | =    | 60             | °C    |  |

| _          | Data hold time <sup>(7)</sup>             | Ambient temperature = 55°C | 20                 | _    | _              | year  |  |

- NOTES:

1. Vcc = 2.7 to 5.5 V at Topr = 0 to 60°C, unless otherwise specified.

- 2. Definition of programming/erasure endurance

The programming and erasure endurance is defined on a per-block basis.

If the programming and erasure endurance is n (n = 100 or 1,000), each block can be erased n times. For example, if 1,024 1-byte writes are performed to different addresses in block A, a 1 Kbyte block, and then the block is erased, the programming/erasure endurance still stands at one.

However, the same address must not be programmed more than once per erase operation (overwriting prohibited).

- 3. Endurance to guarantee all electrical characteristics after program and erase. (1 to Min. value can be guaranteed).

- 4. In a system that executes multiple programming operations, the actual erasure count can be reduced by writing to sequential addresses in turn so that as much of the block as possible is used up before performing an erase operation. For example, when programming groups of 16 bytes, the effective number of rewrites can be minimized by programming up to 128 groups before erasing them all in one operation. It is also advisable to retain data on the erasure endurance of each block and limit the number of erase operations to a certain number.

- 5. If an error occurs during block erase, attempt to execute the clear status register command, then execute the block erase command at least three times until the erase error does not occur.

- 6. Customers desiring program/erase failure rate information should contact their Renesas technical support representative.

- 7. The data hold time includes time that the power supply is off or the clock is not supplied.

Figure 5.21 Time delay until Suspend

Table 5.39 Voltage Detection 1 Circuit Electrical Characteristics

| Symbol      | Parameter                                                                    | Condition              |      | Standard |      |      |

|-------------|------------------------------------------------------------------------------|------------------------|------|----------|------|------|

| Syllibol    | Farameter                                                                    | Condition              | Min. | Тур.     | Max. | Unit |

| Vdet1       | Voltage detection level <sup>(2, 4)</sup>                                    |                        | 2.70 | 2.85     | 3.0  | V    |

| td(Vdet1-A) | Voltage monitor 1 reset generation time <sup>(5)</sup>                       |                        | _    | 40       | 200  | μS   |

| _           | Voltage detection circuit self power consumption                             | VCA26 = 1, Vcc = 5.0 V | _    | 0.6      | _    | μΑ   |

| td(E-A)     | Waiting time until voltage detection circuit operation starts <sup>(3)</sup> |                        | =    | -        | 100  | μS   |

| Vccmin      | MCU operating voltage minimum value                                          |                        | 2.70 | -        | -    | V    |

- 1. The measurement condition is Vcc = 2.7 to 5.5 V and Topr = -40 to 85°C (J version) / -40 to 125°C (K version).

- 2. Hold Vdet2 > Vdet1.

- 3. Necessary time until the voltage detection circuit operates when setting to 1 again after setting the VCA26 bit in the VCA2 register to 0.

- 4. This parameter shows the voltage detection level when the power supply drops. The voltage detection level when the power supply rises is higher than the voltage detection level when the power supply drops by approximately 0.1 V.

- 5. Time until the voltage monitor 1 reset is generated after the voltage passes V<sub>det1</sub> when V<sub>CC</sub> falls. When using the digital filter, its sampling time is added to t<sub>d</sub>(V<sub>det1</sub>-A). When using the voltage monitor 1 reset, maintain this time until V<sub>CC</sub> = 2.0 V after the voltage passes V<sub>det1</sub> when the power supply falls.

Table 5.40 Voltage Detection 2 Circuit Electrical Characteristics

| Symbol      | Parameter                                                                    | Condition              | Standard |      |      | Unit  |

|-------------|------------------------------------------------------------------------------|------------------------|----------|------|------|-------|

| Symbol      | Farameter                                                                    | Condition              | Min.     | Тур. | Max. | Offic |

| Vdet2       | Voltage detection level <sup>(2)</sup>                                       |                        | 3.3      | 3.6  | 3.9  | V     |

| td(Vdet2-A) | Voltage monitor 2 reset/interrupt request generation time <sup>(3, 5)</sup>  |                        | =        | 40   | 200  | μS    |

| =           | Voltage detection circuit self power consumption                             | VCA27 = 1, Vcc = 5.0 V | =        | 0.6  | _    | μΑ    |

| td(E-A)     | Waiting time until voltage detection circuit operation starts <sup>(4)</sup> |                        | I        | =    | 100  | μS    |

- 1. The measurement condition is Vcc = 2.7 to 5.5 V and Topr = -40 to 85°C (J version) / -40 to 125°C (K version).

- 2. Hold Vdet2 > Vdet1

- 3. Time until the voltage monitor 2 reset/interrupt request is generated after the voltage passes Vdet2.

- 4. Necessary time until the voltage detection circuit operates after setting to 1 again after setting the VCA27 bit in the VCA2 register to 0.

- 5. When using the digital filter, its sampling time is added to td(Vdet2-A). When using the voltage monitor 2 reset, maintain this time until Vcc = 2.0 V after the voltage passes Vdet2 when the power supply falls.

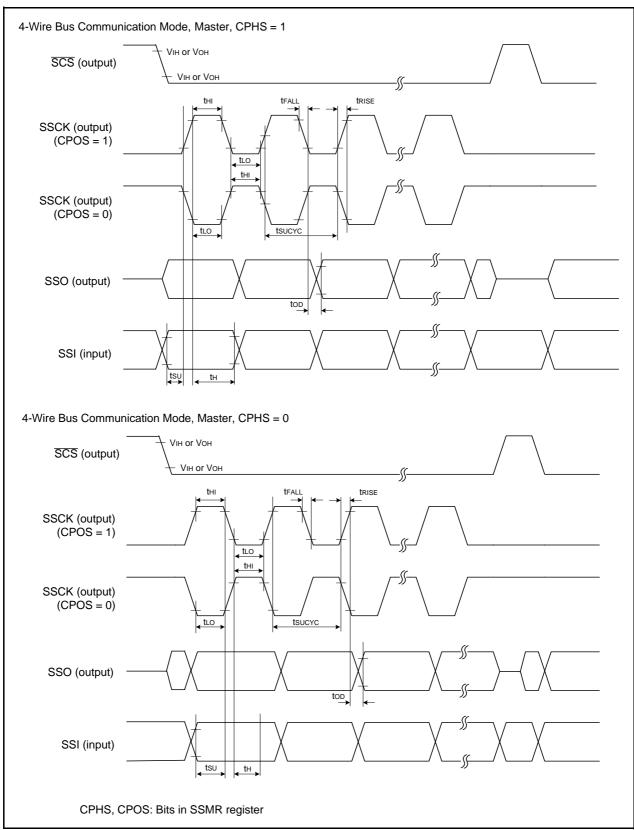

**Table 5.45** Timing Requirements of Clock Synchronous Serial I/O with Chip Select(1)

| Symbol | Parameter                       |          | Conditions |            | Stand | Unit          |         |

|--------|---------------------------------|----------|------------|------------|-------|---------------|---------|

| Symbol |                                 |          | Conditions | Min.       | Тур.  | Max.          |         |

| tsucyc | SSCK clock cycle time           |          |            | 4          | -     | -             | tcyc(2) |

| tHI    | SSCK clock "H" width            |          |            | 0.4        | -     | 0.6           | tsucyc  |

| tLO    | SSCK clock "L" width            |          |            | 0.4        | _     | 0.6           | tsucyc  |

| trise  | SSCK clock rising               | Master   |            | =          | =     | 1             | tcyc(2) |

|        | time                            | Slave    |            | =          | _     | 1             | μS      |

| tFALL  | SSCK clock falling time         | Master   |            | -          | -     | 1             | tcyc(2) |

|        |                                 | Slave    |            | =          | _     | 1             | μS      |

| tsu    | SSO, SSI data input setup time  |          |            | 100        | -     | -             | ns      |

| tH     | SSO, SSI data input h           | old time |            | 1          | =     | -             | tcyc(2) |

| tLEAD  | SCS setup time                  | Slave    |            | 1tcyc + 50 | -     | -             | ns      |

| tLAG   | SCS hold time                   | Slave    |            | 1tcyc + 50 | =     | -             | ns      |

| top    | SSO, SSI data output delay time |          |            | _          | -     | 1             | tcyc(2) |

| tsa    | SSI slave access time           |          |            | -          | _     | 1.5tcyc + 100 | ns      |

| tor    | SSI slave out open time         |          |            | _          | _     | 1.5tcyc + 100 | ns      |

- 1. Vcc = 2.7 to 5.5 V, Vss = 0 V at  $T_{opr} = -40$  to  $85^{\circ}C$  (J version) / -40 to  $125^{\circ}C$  (K version), unless otherwise specified. 2. 1tCyc = 1/f1(s)

Figure 5.23 I/O Timing of Clock Synchronous Serial I/O with Chip Select (Master)

#### **Timing requirements**

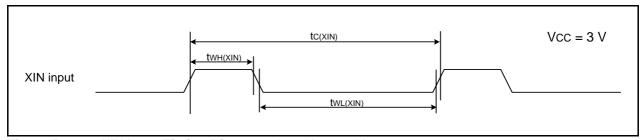

(Unless Otherwise Specified: Vcc = 3 V, Vss = 0 V at Topr = 25°C) [Vcc = 3 V]

Table 5.55 XIN Input

| Symbol   | Parameter            | Stan      | dard  | Unit |

|----------|----------------------|-----------|-------|------|

|          | Falanietei           | Min. Max. | Offic |      |

| tc(XIN)  | XIN input cycle time | 100       | -     | ns   |

| twh(xin) | XIN input "H" width  | 40        | =     | ns   |

| tWL(XIN) | XIN input "L" width  | 40        | =     | ns   |

Figure 5.31 XIN Input Timing Diagram when Vcc = 3 V

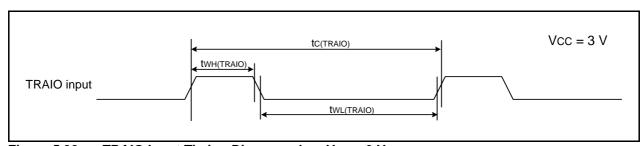

Table 5.56 TRAIO Input

| Symbol     | Parameter              | Stan      | Unit |    |

|------------|------------------------|-----------|------|----|

|            | r didilletei           | Min. Max. |      |    |

| tc(TRAIO)  | TRAIO input cycle time | 300       | -    | ns |

| tWH(TRAIO) | TRAIO input "H" width  | 120       | =    | ns |

| twl(traio) | TRAIO input "L" width  | 120       | =    | ns |

Figure 5.32 TRAIO Input Timing Diagram when Vcc = 3 V

# REVISION HISTORY

# R8C/26 Group, R8C/27 Group Datasheet

|      | 5.4          |           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------|--------------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. | Date         | Page      | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0.10 | Nov 14, 2005 | -         | First edition issued                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 0.20 | Feb 06, 2006 | 2, 3      | Table 1.1 Functions and Specifications for R8C/26Group and Table 1.2 Functions and Specifications for R8C/27 Group;  Minimum instruction execution time and Supply voltage revised                                                                                                                                                                                                                                                                                                                    |

|      |              | 9         | Table 1.6 Pin Name Information by Pin Number; "XOUT" $\rightarrow$ "XOUT/XCOUT" and "XIN" $\rightarrow$ "XIN/XCIN" revised                                                                                                                                                                                                                                                                                                                                                                            |

|      |              | 18        | Table 4.4 SFR Information (4);<br>00FEh: "DRR" → "P1DRR" revised                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|      |              | 19        | Table 4.5 SFR Information (5);  -0119h: "Timer RE Minute Data Register / Compare Register" →  "Timer RE Minute Data Register / Compare Data Register"  -011Ah: "Timer RE Time Data Register" →  "Timer RE Hour Data Register"  -011Bh: "Timer RE Day Data Register" →  "Timer RE Day of Week Data Register" revised                                                                                                                                                                                   |

|      |              | 22 to 45  | 5. Electrical Characteristics added                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1.00 | Nov 08, 2006 | All pages | "Preliminary" deleted                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|      |              | 2         | Table 1.1 revised                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |              | 3         | Table 1.2 revised                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |              | 4         | Figure 1.1 revised                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |              | 5         | Table 1.3 revised                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |              | 6         | Table 1.4 revised                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |              | 7         | Figure 1.4 revised                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|      |              | 9         | Table 1.6 revised                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |              | 15        | Table 4.1;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|      |              |           | <ul> <li>• 001Ch: "00h" → "00h, 10000000b" revised</li> <li>• 000Fh: "000XXXXXb" → "00X11111b" revised</li> <li>• 0029h: "High-Speed On-Chip Oscillator Control Register 4, FRA4, When shipping" added</li> <li>• 002Bh: "High-Speed On-Chip Oscillator Control Register 6, FRA6, When shipping" added</li> <li>• 0032h: "00h, 01000000b" → "00h, 00100000b" revised</li> <li>• 0038h: "00001000b, 01001001b" → "0000X000b, 0100X001b" revised</li> <li>• NOTE3 and 4 revised; NOTE6 added</li> </ul> |

|      |              | 18        | Table 4.4;  • 00E0h, 00E1h, 00E5h, 00E8h, 00E9h: "XXh" → "00h" revised  • 00FDh: "XX00000000b" → "00h" revised                                                                                                                                                                                                                                                                                                                                                                                        |

|      |              | 22        | Table 5.2 revised                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |              | 23        | Figure 5.1 title revised                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|      |              | 24        | Table 5.4 revised                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |              | 25        | Table 5.5 revised                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|      |              | 26        | Figure 5.2 title revised and Table 5.7 NOTE4 added                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Dov  | Data         |           | Description                                                                                                                                                          |

|------|--------------|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. | Date         | Page      | Summary                                                                                                                                                              |

| 1.00 | Nov 08, 2006 | 27        | Table 5.9, Figure 5.3 revised and Table 5.10 deleted                                                                                                                 |

|      |              | 28        | Table 5.10, Table 5.11 revised                                                                                                                                       |

|      |              | 34        | Table 5.15 revised                                                                                                                                                   |

|      |              | 35        | Table 5.16 revised                                                                                                                                                   |

|      |              | 36        | Table 5.17 revised                                                                                                                                                   |

|      |              | 39        | Table 5.22 revised                                                                                                                                                   |

|      |              | 40        | Table 5.23 revised                                                                                                                                                   |

|      |              | 44        | Table 5.29 revised                                                                                                                                                   |

|      |              | 47        | Package Dimensions; "Diagrams showing the latestwebsite." added                                                                                                      |

| 1.10 | Nov 29, 2006 | All pages | "J, K version" added                                                                                                                                                 |

|      |              | 1         | 1 "J and K versions are under developmentnotice." added                                                                                                              |

|      |              |           | 1.1 revised                                                                                                                                                          |

|      |              | 2         | Table 1.1 revised                                                                                                                                                    |

|      |              | 3         | Table 1.2 revised                                                                                                                                                    |

|      |              | 4         | Figure 1.1 NOTE3 added                                                                                                                                               |

|      |              | 5         | Table 1.3, Figure 1.2 revised                                                                                                                                        |

|      |              | 6         | Table 1.4, Figure 1.3 revised                                                                                                                                        |

|      |              | 7         | Figure 1.4 NOTE3 added                                                                                                                                               |

|      |              | 8         | Table 1.5 revised                                                                                                                                                    |

|      |              | 9         | Table 1.6 NOTE2 added                                                                                                                                                |

|      |              | 13        | Figure 3.1 revised                                                                                                                                                   |

|      |              | 14        | Figure 3.2 revised                                                                                                                                                   |

|      |              | 15        | Table 4.1; "0000h to 003Fh" → "0000h to 002Fh" revised  • NOTE3 added                                                                                                |

|      |              | 16        | Table 4.2; "0040h to 007Fh" → "0030h to 007Fh" revised  • 0032h, 0036h: "After reset" is revised  • 0038h: NOTE revised  • NOTES 2, 5, 6 revised and NOTE 7, 8 added |

|      |              | 19        | Table 4.5 NOTE2 added                                                                                                                                                |

|      |              | 28        | Table 5.10 revised                                                                                                                                                   |

|      |              | 48 to 66  | 5.2 J, K Version added                                                                                                                                               |

| 1.20 | Jan 17, 2007 | 18        | Table 4.4 NOTE2 added                                                                                                                                                |

| 1.30 | May 25, 2007 | 2         | Table 1.1 revised                                                                                                                                                    |

|      |              | 3         | Table 1.2 revised                                                                                                                                                    |

|      |              | 5         | Table 1.3 revised                                                                                                                                                    |

|      |              | 6         | Figure 1.2 revised                                                                                                                                                   |

|      |              | 7         | Table 1.4 revised                                                                                                                                                    |

|      |              | 8         | Figure 1.3 revised                                                                                                                                                   |

|      |              | 9         | Figure 1.4 NOTE4 added                                                                                                                                               |

|      |              | 15        | Figure 3.1 part number revised                                                                                                                                       |