#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                      |

|----------------------------|-------------------------------------------------------------------------------|

| Core Processor             | C166                                                                          |

| Core Size                  | 16-Bit                                                                        |

| Speed                      | 33MHz                                                                         |

| Connectivity               | CANbus, EBI/EMI, SPI, UART/USART                                              |

| Peripherals                | POR, PWM, WDT                                                                 |

| Number of I/O              | 113                                                                           |

| Program Memory Size        | - ·                                                                           |

| Program Memory Type        | ROMIess                                                                       |

| EEPROM Size                | · · · · · · · · · · · · · · · · · · ·                                         |

| RAM Size                   | 4K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                   |

| Data Converters            | A/D 16x10b                                                                    |

| Oscillator Type            | External                                                                      |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                 |

| Package / Case             | 144-BQFP                                                                      |

| Supplier Device Package    | P-MQFP-144-8                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/c167crl33mhakxuma2 |

|                            |                                                                               |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **General Device Information**

| Table 3    | Pir         | n Defini       | tions and F | Functions P-BGA-176-2 (cont'd)                                             |  |  |  |  |

|------------|-------------|----------------|-------------|----------------------------------------------------------------------------|--|--|--|--|

| Symbol     | Pin<br>Num. | Input<br>Outp. | Function    |                                                                            |  |  |  |  |

| P2         |             | IO             | Port 2 is a | 16-bit bidirectional I/O port. It is bit-wise                              |  |  |  |  |

|            |             |                | programm    | able for input or output via direction bits. For a pin                     |  |  |  |  |

|            |             |                | -           | as input, the output driver is put into high-                              |  |  |  |  |

|            |             |                | -           | e state. Port 2 outputs can be configured as                               |  |  |  |  |

|            |             |                |             | or open drain drivers. The input threshold of Port 2 ble (TTL or special). |  |  |  |  |

|            |             |                | The follow  | ring Port 2 pins also serve for alternate functions:                       |  |  |  |  |

| P2.0       | F3          | I/O            | CC0IO       | CAPCOM1: CC0 Capture Inp./Compare Output                                   |  |  |  |  |

| P2.1       | F2          | I/O            | CC1IO       | CAPCOM1: CC1 Capture Inp./Compare Output                                   |  |  |  |  |

| P2.2       | F4          | I/O            | CC2IO       | CAPCOM1: CC2 Capture Inp./Compare Output                                   |  |  |  |  |

| P2.3       | G4          | I/O            | CC3IO       | CAPCOM1: CC3 Capture Inp./Compare Output                                   |  |  |  |  |

| P2.4       | G3          | I/O            | CC4IO       | CAPCOM1: CC4 Capture Inp./Compare Output                                   |  |  |  |  |

| P2.5       | G2          | I/O            | CC5IO       | CAPCOM1: CC5 Capture Inp./Compare Output                                   |  |  |  |  |

| P2.6       | G1          | I/O            | CC6IO       | CAPCOM1: CC6 Capture Inp./Compare Output                                   |  |  |  |  |

| P2.7       | H1          | I/O            | CC7IO       | CAPCOM1: CC7 Capture Inp./Compare Output                                   |  |  |  |  |

| P2.8       | H4          | I/O            | CC8IO       | CAPCOM1: CC8 Capture Inp./Compare Output,                                  |  |  |  |  |

|            |             | I              | EX0IN       | Fast External Interrupt 0 Input                                            |  |  |  |  |

| P2.9       | J1          | I/O            | CC9IO       | CAPCOM1: CC9 Capture Inp./Compare Output,                                  |  |  |  |  |

|            |             | I              | EX1IN       | Fast External Interrupt 1 Input                                            |  |  |  |  |

| P2.10      | J2          | I/O            | CC10IO      | CAPCOM1: CC10 Capture Inp./Compare Outp.,                                  |  |  |  |  |

|            |             | I              | EX2IN       | Fast External Interrupt 2 Input                                            |  |  |  |  |

| P2.11      | J4          | I/O            | CC11IO      | CAPCOM1: CC11 Capture Inp./Compare Outp.,                                  |  |  |  |  |

|            |             | 1              | EX3IN       | Fast External Interrupt 3 Input                                            |  |  |  |  |

| P2.12      | J3          | I/O            | CC12IO      | CAPCOM1: CC12 Capture Inp./Compare Outp.,                                  |  |  |  |  |

|            |             | I              | EX4IN       | Fast External Interrupt 4 Input                                            |  |  |  |  |

| P2.13      | K1          | I/O            | CC13IO      | CAPCOM1: CC13 Capture Inp./Compare Outp.,                                  |  |  |  |  |

|            |             | I              | EX5IN       | Fast External Interrupt 5 Input                                            |  |  |  |  |

| P2.14      | K2          | I/O            | CC14IO      | CAPCOM1: CC14 Capture Inp./Compare Outp.,                                  |  |  |  |  |

|            |             | 1              | EX6IN       | Fast External Interrupt 6 Input                                            |  |  |  |  |

| P2.15      | L1          | I/O            | CC15IO      | CAPCOM1: CC15 Capture Inp./Compare Outp.,                                  |  |  |  |  |

|            |             | I              | EX7IN       | Fast External Interrupt 7 Input,                                           |  |  |  |  |

|            |             | I              | T7IN        | CAPCOM2: Timer T7 Count Input                                              |  |  |  |  |

| $V_{AREF}$ | B2          | -              | Reference   | e voltage for the A/D converter.                                           |  |  |  |  |

| $V_{AGND}$ | C2          | -              | Reference   | e ground for the A/D converter.                                            |  |  |  |  |

# 3.1 Memory Organization

The memory space of the C167CR is configured in a Von Neumann architecture which means that code memory, data memory, registers and I/O ports are organized within the same linear address space which includes 16 Mbytes. The entire memory space can be accessed bytewise or wordwise. Particular portions of the on-chip memory have additionally been made directly bitaddressable.

The C167CR incorporates 128/32 Kbytes (depending on the derivative) of on-chip maskprogrammable ROM for code or constant data. The lower 32 Kbytes of the on-chip ROM can be mapped either to segment 0 or segment 1.

2 Kbytes of on-chip Internal RAM (IRAM) are provided as a storage for user defined variables, for the system stack, general purpose register banks and even for code. A register bank can consist of up to 16 wordwide (R0 to R15) and/or bytewide (RL0, RH0, ..., RL7, RH7) so-called General Purpose Registers (GPRs).

1024 bytes ( $2 \times 512$  bytes) of the address space are reserved for the Special Function Register areas (SFR space and ESFR space). SFRs are wordwide registers which are used for controlling and monitoring functions of the different on-chip units. Unused SFR addresses are reserved for future members of the C166 Family.

2 Kbytes of on-chip Extension RAM (XRAM) are provided to store user data, user stacks, or code. The XRAM is accessed like external memory and therefore cannot be used for the system stack or for register banks and is not bitaddressable. The XRAM permits 16-bit accesses with maximum speed.

In order to meet the needs of designs where more memory is required than is provided on chip, up to 16 Mbytes of external RAM and/or ROM can be connected to the microcontroller.

# 3.2 External Bus Controller

All of the external memory accesses are performed by a particular on-chip External Bus Controller (EBC). It can be programmed either to Single Chip Mode when no external memory is required, or to one of four different external memory access modes, which are as follows:

- 16-/18-/20-/24-bit Addresses, 16-bit Data, Demultiplexed

- 16-/18-/20-/24-bit Addresses, 16-bit Data, Multiplexed

- 16-/18-/20-/24-bit Addresses, 8-bit Data, Multiplexed

- 16-/18-/20-/24-bit Addresses, 8-bit Data, Demultiplexed

In the demultiplexed bus modes, addresses are output on PORT1 and data is input/output on PORT0 or P0L, respectively. In the multiplexed bus modes both addresses and data use PORT0 for input/output.

Important timing characteristics of the external bus interface (Memory Cycle Time, Memory Tri-State Time, Length of ALE and Read Write Delay) have been made programmable to allow the user the adaption of a wide range of different types of memories and external peripherals.

In addition, up to 4 independent address windows may be defined (via register pairs ADDRSELx / BUSCONx) which control the access to different resources with different bus characteristics. These address windows are arranged hierarchically where BUSCON4 overrides BUSCON3 and BUSCON2 overrides BUSCON1. All accesses to locations not covered by these 4 address windows are controlled by BUSCON0.

Up to 5 external  $\overline{\text{CS}}$  signals (4 windows plus default) can be generated in order to save external glue logic. The C167CR offers the possibility to switch the  $\overline{\text{CS}}$  outputs to an unlatched mode. In this mode the internal filter logic is switched off and the  $\overline{\text{CS}}$  signals are directly generated from the address. The unlatched  $\overline{\text{CS}}$  mode is enabled by setting CSCFG (SYSCON.6).

Access to very slow memories or memories with varying access times is supported via a particular 'Ready' function.

A HOLD/HLDA protocol is available for bus arbitration and allows to share external resources with other bus masters. The bus arbitration is enabled by setting bit HLDEN in register PSW. After setting HLDEN once, pins P6.7 ... P6.5 (BREQ, HLDA, HOLD) are automatically controlled by the EBC. In Master Mode (default after reset) the HLDA pin is an output. By setting bit DP6.7 to '1' the Slave Mode is selected where pin HLDA is switched to input. This allows to directly connect the slave controller to another master controller without glue logic.

For applications which require less than 16 Mbytes of external memory space, this address space can be restricted to 1 Mbyte, 256 Kbyte, or to 64 Kbyte. In this case Port 4 outputs four, two, or no address lines at all. It outputs all 8 address lines, if an address space of 16 Mbytes is used.

# Table 4 C167CR Interrupt Nodes

| Source of Interrupt or PEC Service Request | Request<br>Flag | Enable<br>Flag | Interrupt<br>Vector | Vector<br>Location   | Trap<br>Number  |

|--------------------------------------------|-----------------|----------------|---------------------|----------------------|-----------------|

| CAPCOM Register 0                          | CC0IR           | CC0IE          | CC0INT              | 00'0040 <sub>H</sub> | 10 <sub>H</sub> |

| CAPCOM Register 1                          | CC1IR           | CC1IE          | CC1INT              | 00'0044 <sub>H</sub> | 11 <sub>H</sub> |

| CAPCOM Register 2                          | CC2IR           | CC2IE          | CC2INT              | 00'0048 <sub>H</sub> | 12 <sub>H</sub> |

| CAPCOM Register 3                          | CC3IR           | CC3IE          | CC3INT              | 00'004C <sub>H</sub> | 13 <sub>H</sub> |

| CAPCOM Register 4                          | CC4IR           | CC4IE          | CC4INT              | 00'0050 <sub>H</sub> | 14 <sub>H</sub> |

| CAPCOM Register 5                          | CC5IR           | CC5IE          | CC5INT              | 00'0054 <sub>H</sub> | 15 <sub>H</sub> |

| CAPCOM Register 6                          | CC6IR           | CC6IE          | CC6INT              | 00'0058 <sub>H</sub> | 16 <sub>H</sub> |

| CAPCOM Register 7                          | CC7IR           | CC7IE          | CC7INT              | 00'005C <sub>H</sub> | 17 <sub>H</sub> |

| CAPCOM Register 8                          | CC8IR           | CC8IE          | CC8INT              | 00'0060 <sub>H</sub> | 18 <sub>H</sub> |

| CAPCOM Register 9                          | CC9IR           | CC9IE          | CC9INT              | 00'0064 <sub>H</sub> | 19 <sub>H</sub> |

| CAPCOM Register 10                         | CC10IR          | CC10IE         | CC10INT             | 00'0068 <sub>H</sub> | 1A <sub>H</sub> |

| CAPCOM Register 11                         | CC11IR          | CC11IE         | CC11INT             | 00'006C <sub>H</sub> | 1B <sub>H</sub> |

| CAPCOM Register 12                         | CC12IR          | CC12IE         | CC12INT             | 00'0070 <sub>H</sub> | 1C <sub>H</sub> |

| CAPCOM Register 13                         | CC13IR          | CC13IE         | CC13INT             | 00'0074 <sub>H</sub> | 1D <sub>H</sub> |

| CAPCOM Register 14                         | CC14IR          | CC14IE         | CC14INT             | 00'0078 <sub>H</sub> | 1E <sub>H</sub> |

| CAPCOM Register 15                         | CC15IR          | CC15IE         | CC15INT             | 00'007C <sub>H</sub> | 1F <sub>H</sub> |

| CAPCOM Register 16                         | CC16IR          | CC16IE         | CC16INT             | 00'00C0 <sub>H</sub> | 30 <sub>H</sub> |

| CAPCOM Register 17                         | CC17IR          | CC17IE         | CC17INT             | 00'00C4 <sub>H</sub> | 31 <sub>H</sub> |

| CAPCOM Register 18                         | CC18IR          | CC18IE         | CC18INT             | 00'00C8 <sub>H</sub> | 32 <sub>H</sub> |

| CAPCOM Register 19                         | CC19IR          | CC19IE         | CC19INT             | 00'00CC <sub>H</sub> | 33 <sub>H</sub> |

| CAPCOM Register 20                         | CC20IR          | CC20IE         | CC20INT             | 00'00D0 <sub>H</sub> | 34 <sub>H</sub> |

| CAPCOM Register 21                         | CC21IR          | CC21IE         | CC21INT             | 00'00D4 <sub>H</sub> | 35 <sub>H</sub> |

| CAPCOM Register 22                         | CC22IR          | CC22IE         | CC22INT             | 00'00D8 <sub>H</sub> | 36 <sub>H</sub> |

| CAPCOM Register 23                         | CC23IR          | CC23IE         | CC23INT             | 00'00DC <sub>H</sub> | 37 <sub>H</sub> |

| CAPCOM Register 24                         | CC24IR          | CC24IE         | CC24INT             | 00'00E0 <sub>H</sub> | 38 <sub>H</sub> |

| CAPCOM Register 25                         | CC25IR          | CC25IE         | CC25INT             | 00'00E4 <sub>H</sub> | 39 <sub>H</sub> |

| CAPCOM Register 26                         | CC26IR          | CC26IE         | CC26INT             | 00'00E8 <sub>H</sub> | 3A <sub>H</sub> |

| CAPCOM Register 27                         | CC27IR          | CC27IE         | CC27INT             | 00'00EC <sub>H</sub> | 3B <sub>H</sub> |

| CAPCOM Register 28                         | CC28IR          | CC28IE         | CC28INT             | 00'00E0 <sub>H</sub> | 3C <sub>H</sub> |

| CAPCOM Register 29                         | CC29IR          | CC29IE         | CC29INT             | 00'0110 <sub>H</sub> | 44 <sub>H</sub> |

# 3.7 General Purpose Timer (GPT) Unit

The GPT unit represents a very flexible multifunctional timer/counter structure which may be used for many different time related tasks such as event timing and counting, pulse width and duty cycle measurements, pulse generation, or pulse multiplication.

The GPT unit incorporates five 16-bit timers which are organized in two separate modules, GPT1 and GPT2. Each timer in each module may operate independently in a number of different modes, or may be concatenated with another timer of the same module.

Each of the three timers T2, T3, T4 of **module GPT1** can be configured individually for one of four basic modes of operation, which are Timer, Gated Timer, Counter, and Incremental Interface Mode. In Timer Mode, the input clock for a timer is derived from the CPU clock, divided by a programmable prescaler, while Counter Mode allows a timer to be clocked in reference to external events.

Pulse width or duty cycle measurement is supported in Gated Timer Mode, where the operation of a timer is controlled by the 'gate' level on an external input pin. For these purposes, each timer has one associated port pin (TxIN) which serves as gate or clock input. The maximum resolution of the timers in module GPT1 is 16 TCL.

The count direction (up/down) for each timer is programmable by software or may additionally be altered dynamically by an external signal on a port pin (TxEUD) to facilitate e.g. position tracking.

In Incremental Interface Mode the GPT1 timers (T2, T3, T4) can be directly connected to the incremental position sensor signals A and B via their respective inputs TxIN and TxEUD. Direction and count signals are internally derived from these two input signals, so the contents of the respective timer Tx corresponds to the sensor position. The third position sensor signal TOP0 can be connected to an interrupt input.

Timer T3 has an output toggle latch (T3OTL) which changes its state on each timer overflow/underflow. The state of this latch may be output on pin T3OUT e.g. for time out monitoring of external hardware components, or may be used internally to clock timers T2 and T4 for measuring long time periods with high resolution.

In addition to their basic operating modes, timers T2 and T4 may be configured as reload or capture registers for timer T3. When used as capture or reload registers, timers T2 and T4 are stopped. The contents of timer T3 is captured into T2 or T4 in response to a signal at their associated input pins (TxIN). Timer T3 is reloaded with the contents of T2 or T4 triggered either by an external signal or by a selectable state transition of its toggle latch T3OTL. When both T2 and T4 are configured to alternately reload T3 on opposite state transitions of T3OTL with the low and high times of a PWM signal, this signal can be constantly generated without software intervention.

# 3.8 A/D Converter

For analog signal measurement, a 10-bit A/D converter with 16 multiplexed input channels and a sample and hold circuit has been integrated on-chip. It uses the method of successive approximation. The sample time (for loading the capacitors) and the conversion time is programmable and can so be adjusted to the external circuitry.

Overrun error detection/protection is provided for the conversion result register (ADDAT): either an interrupt request will be generated when the result of a previous conversion has not been read from the result register at the time the next conversion is complete, or the next conversion is suspended in such a case until the previous result has been read.

For applications which require less than 16 analog input channels, the remaining channel inputs can be used as digital input port pins.

The A/D converter of the C167CR supports four different conversion modes. In the standard Single Channel conversion mode, the analog level on a specified channel is sampled once and converted to a digital result. In the Single Channel Continuous mode, the analog level on a specified channel is repeatedly sampled and converted without software intervention. In the Auto Scan mode, the analog levels on a prespecified number of channels are sequentially sampled and converted. In the Auto Scan Continuous mode, the number of prespecified channels is repeatedly sampled and converted in a converted. In addition, the conversion of a specific channel can be inserted (injected) into a running sequence without disturbing this sequence. This is called Channel Injection Mode.

The Peripheral Event Controller (PEC) may be used to automatically store the conversion results into a table in memory for later evaluation, without requiring the overhead of entering and exiting interrupt routines for each data transfer.

After each reset and also during normal operation the ADC automatically performs calibration cycles. This automatic self-calibration constantly adjusts the converter to changing operating conditions (e.g. temperature) and compensates process variations.

These calibration cycles are part of the conversion cycle, so they do not affect the normal operation of the A/D converter.

In order to decouple analog inputs from digital noise and to avoid input trigger noise those pins used for analog input can be disconnected from the digital IO or input stages under software control. This can be selected for each pin separately via register P5DIDIS (Port 5 Digital Input Disable).

# 3.15 Special Function Registers Overview

The following table lists all SFRs which are implemented in the C167CR in alphabetical order.

**Bit-addressable** SFRs are marked with the letter "**b**" in column "Name". SFRs within the **Extended SFR-Space** (ESFRs) are marked with the letter "**E**" in column "Physical Address". Registers within on-chip X-peripherals are marked with the letter "**X**" in column "Physical Address".

An SFR can be specified via its individual mnemonic name. Depending on the selected addressing mode, an SFR can be accessed via its physical address (using the Data Page Pointers), or via its short 8-bit address (without using the Data Page Pointers).

Note: Registers within device specific interface modules (CAN) are only present in the corresponding device, of course.

| Name     | _ | Physica<br>Addres |   | 8-Bit<br>Addr.  | Description                                                   | Reset<br>Value    |

|----------|---|-------------------|---|-----------------|---------------------------------------------------------------|-------------------|

| ADCIC    | b | FF98 <sub>H</sub> |   | CC <sub>H</sub> | A/D Converter End of Conversion<br>Interrupt Control Register | 0000 <sub>H</sub> |

| ADCON    | b | FFA0 <sub>H</sub> |   | D0 <sub>H</sub> | A/D Converter Control Register                                | 0000 <sub>H</sub> |

| ADDAT    |   | FEA0 <sub>H</sub> |   | 50 <sub>H</sub> | A/D Converter Result Register                                 | 0000 <sub>H</sub> |

| ADDAT2   |   | F0A0 <sub>H</sub> | Ε | 50 <sub>H</sub> | A/D Converter 2 Result Register                               | 0000 <sub>H</sub> |

| ADDRSEL1 |   | FE18 <sub>H</sub> |   | 0C <sub>H</sub> | Address Select Register 1                                     | 0000 <sub>H</sub> |

| ADDRSEL2 |   | FE1A <sub>H</sub> |   | 0D <sub>H</sub> | Address Select Register 2                                     | 0000 <sub>H</sub> |

| ADDRSEL3 |   | FE1C <sub>H</sub> |   | 0E <sub>H</sub> | Address Select Register 3                                     | 0000 <sub>H</sub> |

| ADDRSEL4 |   | FE1E <sub>H</sub> |   | 0F <sub>H</sub> | Address Select Register 4                                     | 0000 <sub>H</sub> |

| ADEIC    | b | FF9A <sub>H</sub> |   | CD <sub>H</sub> | A/D Converter Overrun Error Interrupt<br>Control Register     | 0000 <sub>H</sub> |

| BUSCON0  | b | FF0C <sub>H</sub> |   | 86 <sub>H</sub> | Bus Configuration Register 0                                  | 0XX0 <sub>H</sub> |

| BUSCON1  | b | FF14 <sub>H</sub> |   | 8A <sub>H</sub> | Bus Configuration Register 1                                  | 0000 <sub>H</sub> |

| BUSCON2  | b | FF16 <sub>H</sub> |   | 8B <sub>H</sub> | Bus Configuration Register 2                                  | 0000 <sub>H</sub> |

| BUSCON3  | b | FF18 <sub>H</sub> |   | 8C <sub>H</sub> | Bus Configuration Register 3                                  | 0000 <sub>H</sub> |

| BUSCON4  | b | FF1A <sub>H</sub> |   | 8D <sub>H</sub> | Bus Configuration Register 4                                  | 0000 <sub>H</sub> |

| C1BTR    |   | EF04 <sub>H</sub> | Χ | _               | CAN1 Bit Timing Register                                      | UUUU <sub>H</sub> |

| C1CSR    |   | EF00 <sub>H</sub> | Χ | _               | CAN1 Control / Status Register                                | XX01 <sub>H</sub> |

| C1GMS    |   | EF06 <sub>H</sub> | Χ | _               | CAN1 Global Mask Short                                        | UFUU <sub>H</sub> |

Table 8

C167CR Registers, Ordered by Name

# Table 8C167CR Registers, Ordered by Name (cont'd)

| Table 8 | C | 167CR F             | keg | isters,         | Ordered by Name (cont'd)            |                   |

|---------|---|---------------------|-----|-----------------|-------------------------------------|-------------------|

| Name    |   | Physical<br>Address |     | 8-Bit<br>Addr.  | Description                         | Reset<br>Value    |

| CC19IC  | b | F166 <sub>H</sub>   | Ε   | B3 <sub>H</sub> | CAPCOM Reg. 19 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC1IC   | b | FF7A <sub>H</sub>   |     | BD <sub>H</sub> | CAPCOM Reg. 1 Interrupt Ctrl. Reg.  | 0000 <sub>H</sub> |

| CC2     |   | FE84 <sub>H</sub>   |     | 42 <sub>H</sub> | CAPCOM Register 2                   | 0000 <sub>H</sub> |

| CC20    |   | FE68 <sub>H</sub>   |     | 34 <sub>H</sub> | CAPCOM Register 20                  | 0000 <sub>H</sub> |

| CC20IC  | b | F168 <sub>H</sub>   | Ε   | B4 <sub>H</sub> | CAPCOM Reg. 20 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC21    |   | FE6A <sub>H</sub>   |     | 35 <sub>H</sub> | CAPCOM Register 21                  | 0000 <sub>H</sub> |

| CC21IC  | b | F16A <sub>H</sub>   | Ε   | B5 <sub>H</sub> | CAPCOM Reg. 21 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC22    |   | FE6C <sub>H</sub>   |     | 36 <sub>H</sub> | CAPCOM Register 22                  | 0000 <sub>H</sub> |

| CC22IC  | b | F16C <sub>H</sub>   | Ε   | B6 <sub>H</sub> | CAPCOM Reg. 22 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC23    |   | FE6E <sub>H</sub>   |     | 37 <sub>H</sub> | CAPCOM Register 23                  | 0000 <sub>H</sub> |

| CC23IC  | b | F16E <sub>H</sub>   | Ε   | B7 <sub>H</sub> | CAPCOM Reg. 23 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC24    |   | FE70 <sub>H</sub>   |     | 38 <sub>H</sub> | CAPCOM Register 24                  | 0000 <sub>H</sub> |

| CC24IC  | b | F170 <sub>H</sub>   | Ε   | B8 <sub>H</sub> | CAPCOM Reg. 24 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC25    |   | FE72 <sub>H</sub>   |     | 39 <sub>H</sub> | CAPCOM Register 25                  | 0000 <sub>H</sub> |

| CC25IC  | b | F172 <sub>H</sub>   | Ε   | B9 <sub>H</sub> | CAPCOM Reg. 25 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC26    |   | FE74 <sub>H</sub>   |     | 3A <sub>H</sub> | CAPCOM Register 26                  | 0000 <sub>H</sub> |

| CC26IC  | b | F174 <sub>H</sub>   | Ε   | BA <sub>H</sub> | CAPCOM Reg. 26 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC27    |   | FE76 <sub>H</sub>   |     | 3B <sub>H</sub> | CAPCOM Register 27                  | 0000 <sub>H</sub> |

| CC27IC  | b | F176 <sub>H</sub>   | Ε   | BB <sub>H</sub> | CAPCOM Reg. 27 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC28    |   | FE78 <sub>H</sub>   |     | 3C <sub>H</sub> | CAPCOM Register 28                  | 0000 <sub>H</sub> |

| CC28IC  | b | F178 <sub>H</sub>   | Ε   | BC <sub>H</sub> | CAPCOM Reg. 28 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC29    |   | FE7A <sub>H</sub>   |     | 3D <sub>H</sub> | CAPCOM Register 29                  | 0000 <sub>H</sub> |

| CC29IC  | b | F184 <sub>H</sub>   | Ε   | C2 <sub>H</sub> | CAPCOM Reg. 29 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC2IC   | b | FF7C <sub>H</sub>   |     | BE <sub>H</sub> | CAPCOM Reg. 2 Interrupt Ctrl. Reg.  | 0000 <sub>H</sub> |

| CC3     |   | FE86 <sub>H</sub>   |     | 43 <sub>H</sub> | CAPCOM Register 3                   | 0000 <sub>H</sub> |

| CC30    |   | FE7C <sub>H</sub>   |     | 3E <sub>H</sub> | CAPCOM Register 30                  | 0000 <sub>H</sub> |

| CC30IC  | b | F18C <sub>H</sub>   | Ε   | C6 <sub>H</sub> | CAPCOM Reg. 30 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC31    |   | FE7E <sub>H</sub>   |     | 3F <sub>н</sub> | CAPCOM Register 31                  | 0000 <sub>H</sub> |

| CC31IC  | b | F194 <sub>H</sub>   | Ε   | CA <sub>H</sub> | CAPCOM Reg. 31 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC3IC   | b | FF7E <sub>H</sub>   |     | BF <sub>H</sub> | CAPCOM Reg. 3 Interrupt Ctrl. Reg.  | 0000 <sub>H</sub> |

## Table 8C167CR Registers, Ordered by Name (cont'd)

| Table 8 | U. | 16/CR Re                   | jisters,        | Ordered by Name (cont'd)                                       | 1                               |

|---------|----|----------------------------|-----------------|----------------------------------------------------------------|---------------------------------|

| Name    |    | Physical<br>Address        | 8-Bit<br>Addr.  | Description                                                    | Reset<br>Value                  |

| S0EIC   | b  | FF70 <sub>H</sub>          | B8 <sub>H</sub> | Serial Chan. 0 Error Interrupt Ctrl. Reg.                      | 0000 <sub>H</sub>               |

| SORBUF  |    | FEB2 <sub>H</sub>          | 59 <sub>H</sub> | Serial Channel 0 Receive Buffer Reg.<br>(read only)            | XX <sub>H</sub>                 |

| SORIC   | b  | FF6E <sub>H</sub>          | B7 <sub>H</sub> | Serial Channel 0 Receive Interrupt<br>Control Register         | 0000 <sub>H</sub>               |

| SOTBIC  | b  | F19C <sub>H</sub> E        | CE <sub>H</sub> | Serial Channel 0 Transmit Buffer<br>Interrupt Control Register | 0000 <sub>H</sub>               |

| SOTBUF  |    | FEB0 <sub>H</sub>          | 58 <sub>H</sub> | Serial Channel 0 Transmit Buffer Reg.<br>(write only)          | 00 <sub>H</sub>                 |

| SOTIC   | b  | FF6C <sub>H</sub>          | B6 <sub>H</sub> | Serial Channel 0 Transmit Interrupt<br>Control Register        | 0000 <sub>H</sub>               |

| SP      |    | FE12 <sub>H</sub>          | 09 <sub>H</sub> | CPU System Stack Pointer Register                              | FC00 <sub>H</sub>               |

| SSCBR   |    | F0B4 <sub>H</sub> E        | 5A <sub>H</sub> | SSC Baudrate Register                                          | 0000 <sub>H</sub>               |

| SSCCON  | b  | FFB2 <sub>H</sub>          | D9 <sub>H</sub> | SSC Control Register                                           | 0000 <sub>H</sub>               |

| SSCEIC  | b  | FF76 <sub>H</sub>          | BB <sub>H</sub> | SSC Error Interrupt Control Register                           | 0000 <sub>H</sub>               |

| SSCRB   |    | F0B2 <sub>H</sub> E        | 59 <sub>H</sub> | SSC Receive Buffer                                             | XXXX <sub>H</sub>               |

| SSCRIC  | b  | FF74 <sub>H</sub>          | $BA_H$          | SSC Receive Interrupt Control Register                         | 0000 <sub>H</sub>               |

| SSCTB   |    | F0B0 <sub>H</sub> <b>E</b> | 58 <sub>H</sub> | SSC Transmit Buffer                                            | 0000 <sub>H</sub>               |

| SSCTIC  | b  | FF72 <sub>H</sub>          | B9 <sub>H</sub> | SSC Transmit Interrupt Control Register                        | 0000 <sub>H</sub>               |

| STKOV   |    | FE14 <sub>H</sub>          | 0A <sub>H</sub> | CPU Stack Overflow Pointer Register                            | FA00 <sub>H</sub>               |

| STKUN   |    | FE16 <sub>H</sub>          | 0B <sub>H</sub> | CPU Stack Underflow Pointer Register                           | FC00 <sub>H</sub>               |

| SYSCON  | b  | FF12 <sub>H</sub>          | 89 <sub>H</sub> | CPU System Configuration Register                              | <sup>1)</sup> 0xx0 <sub>H</sub> |

| Т0      |    | FE50 <sub>H</sub>          | 28 <sub>H</sub> | CAPCOM Timer 0 Register                                        | 0000 <sub>H</sub>               |

| T01CON  | b  | FF50 <sub>H</sub>          | A8 <sub>H</sub> | CAPCOM Timer 0 and Timer 1 Ctrl. Reg.                          | 0000 <sub>H</sub>               |

| TOIC    | b  | FF9C <sub>H</sub>          | CE <sub>H</sub> | CAPCOM Timer 0 Interrupt Ctrl. Reg.                            | 0000 <sub>H</sub>               |

| T0REL   |    | FE54 <sub>H</sub>          | 2A <sub>H</sub> | CAPCOM Timer 0 Reload Register                                 | 0000 <sub>H</sub>               |

| T1      |    | FE52 <sub>H</sub>          | 29 <sub>H</sub> | CAPCOM Timer 1 Register                                        | 0000 <sub>H</sub>               |

| T1IC    | b  | FF9E <sub>H</sub>          | $CF_H$          | CAPCOM Timer 1 Interrupt Ctrl. Reg.                            | 0000 <sub>H</sub>               |

| T1REL   |    | FE56 <sub>H</sub>          | 2B <sub>H</sub> | CAPCOM Timer 1 Reload Register                                 | 0000 <sub>H</sub>               |

| Т2      |    | FE40 <sub>H</sub>          | 20 <sub>H</sub> | GPT1 Timer 2 Register                                          | 0000 <sub>H</sub>               |

| T2CON   | b  | FF40 <sub>H</sub>          | A0 <sub>H</sub> | GPT1 Timer 2 Control Register                                  | 0000 <sub>H</sub>               |

## 4.1 General Parameters

#### Table 9Absolute Maximum Rating Parameters

| Parameter                                                            | Symbol          | Limi | t Values              | Unit | Notes      |

|----------------------------------------------------------------------|-----------------|------|-----------------------|------|------------|

|                                                                      |                 | Min. | Max.                  |      |            |

| Storage temperature                                                  | T <sub>ST</sub> | -65  | 150                   | °C   | -          |

| Junction temperature                                                 | T <sub>J</sub>  | -40  | 150                   | °C   | under bias |

| Voltage on $V_{\rm DD}$ pins with respect to ground ( $V_{\rm SS}$ ) | V <sub>DD</sub> | -0.5 | 6.5                   | V    | -          |

| Voltage on any pin with respect to ground $(V_{SS})$                 | V <sub>IN</sub> | -0.5 | V <sub>DD</sub> + 0.5 | V    | -          |

| Input current on any pin during overload condition                   | _               | -10  | 10                    | mA   | -          |

| Absolute sum of all input<br>currents during overload<br>condition   | -               | -    | 100                   | mA   | -          |

| Power dissipation                                                    | $P_{DISS}$      | -    | 1.5                   | W    | _          |

Note: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. During absolute maximum rating overload conditions ( $V_{IN} > V_{DD}$  or  $V_{IN} < V_{SS}$ ) the voltage on  $V_{DD}$  pins with respect to ground ( $V_{SS}$ ) must not exceed the values defined by the absolute maximum ratings.

## **Operating Conditions**

The following operating conditions must not be exceeded in order to ensure correct operation of the C167CR. All parameters specified in the following sections refer to these operating conditions, unless otherwise noticed.

| Parameter                         | Symbol            | Limit Values      |      | Unit | Notes                                                                           |

|-----------------------------------|-------------------|-------------------|------|------|---------------------------------------------------------------------------------|

|                                   |                   | Min.              | Max. |      |                                                                                 |

| Digital supply voltage            | V <sub>DD</sub>   | 4.5               | 5.5  | V    | Active mode,<br>$f_{CPUmax}$ = 33 MHz                                           |

|                                   |                   | 2.5 <sup>1)</sup> | 5.5  | V    | Power Down mode                                                                 |

| Digital ground voltage            | V <sub>SS</sub>   |                   | 0    | V    | Reference voltage                                                               |

| Overload current                  | I <sub>OV</sub>   | _                 | ±5   | mA   | Per pin <sup>2)3)</sup>                                                         |

| Absolute sum of overload currents | $\Sigma  I_{OV} $ | -                 | 50   | mA   | 3)                                                                              |

| External Load Capacitance         | CL                | -                 | 50   | pF   | Pin drivers in<br><b>fast edge</b> mode<br>(PDCR.BIPEC = '0')                   |

|                                   |                   | -                 | 30   | pF   | Pin drivers in<br><b>reduced edge</b> mode<br>(PDCR.BIPEC = '1') <sup>3)</sup>  |

|                                   |                   | -                 | 100  | рF   | Pin drivers in<br><b>fast edge</b> mode,<br>$f_{CPUmax}$ = 25 MHz <sup>4)</sup> |

| Ambient temperature               | T <sub>A</sub>    | 0                 | 70   | °C   | SAB-C167CR                                                                      |

|                                   |                   | -40               | 85   | °C   | SAF-C167CR                                                                      |

|                                   |                   | -40               | 125  | °C   | SAK-C167CR                                                                      |

## Table 10Operating Condition Parameters

1) Output voltages and output currents will be reduced when  $V_{\rm DD}$  leaves the range defined for active mode.

2) Overload conditions occur if the standard operating conditions are exceeded, i.e. the voltage on any pin exceeds the specified range (i.e.  $V_{OV} > V_{DD} + 0.5 \text{ V}$  or  $V_{OV} < V_{SS} - 0.5 \text{ V}$ ). The absolute sum of input overload currents on all pins may not exceed **50 mA**. The supply voltage must remain within the specified limits. Proper operation is not guaranteed if overload conditions occur on functional pins like XTAL1,  $\overline{\text{RD}}$ ,  $\overline{\text{WR}}$ , etc.

3) Not subject to production test - verified by design/characterization.

4) The increased capacitive load is valid for the 25 MHz-derivatives up to a CPU clock frequency of 25 MHz. Under these circumstances the timing parameters as specified in the "C167CR Data Sheet 1999-06" are valid.

- 9) This specification is valid during Reset and during Adapt-mode.

- 10) Not subject to production test verified by design/characterization.

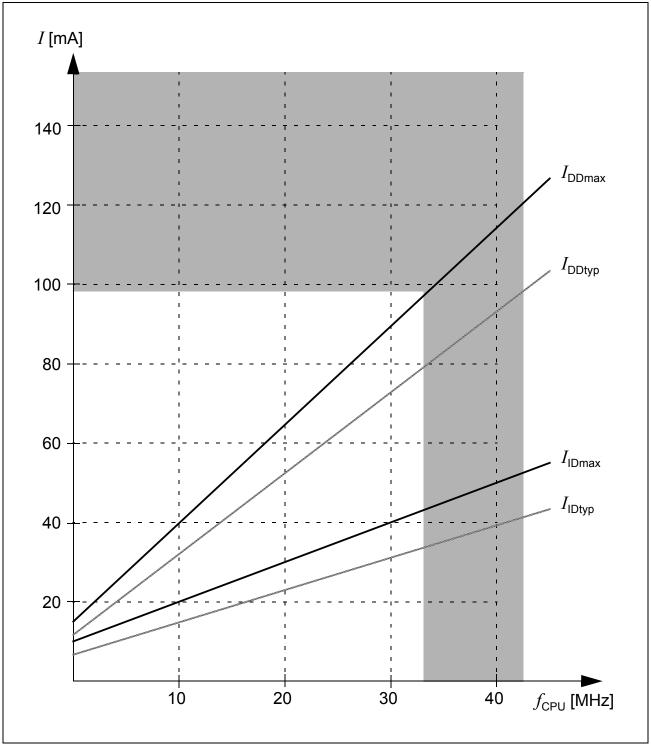

#### Table 12Power Consumption C167CR (Operating Conditions apply)

| Parameter                                                 | Symbol          | Limit V | alues                                 | Unit | <b>Test Condition</b>                                                             |

|-----------------------------------------------------------|-----------------|---------|---------------------------------------|------|-----------------------------------------------------------------------------------|

|                                                           |                 | Min.    | Max.                                  |      |                                                                                   |

| Power supply current (active) with all peripherals active | I <sub>DD</sub> | -       | 15 + 2.5<br>× <i>f</i> <sub>СРU</sub> | mA   | $\frac{\text{RSTIN}}{f_{\text{CPU}} \text{ in } [\text{MHz}]^{1)}}$               |

| Idle mode supply current                                  | I <sub>ID</sub> | -       | 10 + 1.0<br>× <i>f</i> <sub>CPU</sub> | mA   | $\overline{\text{RSTIN}} = V_{\text{IH1}}$ $f_{\text{CPU}} \text{ in [MHz]}^{1)}$ |

| Power-down mode supply current                            | I <sub>PD</sub> | _       | 50                                    | μA   | $V_{\rm DD} = V_{\rm DDmax}^{2}$                                                  |

1) The supply current is a function of the operating frequency. This dependency is illustrated in Figure 9. These parameters are tested at  $V_{\text{DDmax}}$  and maximum CPU clock with all outputs disconnected and all inputs at  $V_{\text{IL}}$  or  $V_{\text{IH}}$ .

2) This parameter is tested including leakage currents. All inputs (including pins configured as inputs) at 0 V to 0.1 V or at  $V_{DD}$  - 0.1 V to  $V_{DD}$ , all outputs (including pins configured as outputs) disconnected.

C167CR C167SR

## **Electrical Parameters**

Figure 9

Supply/Idle Current as a Function of Operating Frequency

# 4.3 Analog/Digital Converter Parameters

| Table 13 | A/D Converter Characteristics (Operating Conditions apply) |

|----------|------------------------------------------------------------|

|----------|------------------------------------------------------------|

| Parameter                                       | Symbol              | Limit                 | Values                                             | Unit | Test                                           |  |

|-------------------------------------------------|---------------------|-----------------------|----------------------------------------------------|------|------------------------------------------------|--|

|                                                 |                     | Min.                  | Max.                                               |      | Condition                                      |  |

| Analog reference supply                         | $V_{AREF}  SR$      | 4.0                   | V <sub>DD</sub> + 0.1                              | V    | 1)                                             |  |

| Analog reference ground                         | $V_{\rm AGND} SR$   | V <sub>SS</sub> - 0.1 | V <sub>SS</sub> + 0.2                              | V    | -                                              |  |

| Analog input voltage range                      | $V_{\rm AIN}$ SR    | V <sub>AGND</sub>     | V <sub>AREF</sub>                                  | V    | 2)                                             |  |

| Basic clock frequency                           | $f_{\rm BC}$        | 0.5                   | 6.25                                               | MHz  | 3)                                             |  |

| Conversion time                                 | t <sub>C</sub> CC   | -                     | 40 $t_{\rm BC}$ + $t_{\rm S}$<br>+ 2 $t_{\rm CPU}$ | -    | $t_{\rm CPU} = 1/f_{\rm CPU}$                  |  |

| Calibration time after reset                    | t <sub>CAL</sub> CC | -                     | 3328 t <sub>BC</sub>                               | _    | 5)                                             |  |

| Total unadjusted error                          | TUE CC              | -                     | ±2                                                 | LSB  | 1)                                             |  |

| Internal resistance of reference voltage source | $R_{AREF}SR$        | -                     | t <sub>BC</sub> / 60<br>- 0.25                     | kΩ   | <i>t</i> <sub>BC</sub> in [ns] <sup>6)7)</sup> |  |

| Internal resistance of analog source            | $R_{\rm ASRC} SR$   | -                     | t <sub>s</sub> / 450<br>- 0.25                     | kΩ   | <i>t</i> <sub>S</sub> in [ns] <sup>7)8)</sup>  |  |

| ADC input capacitance                           | $C_{AIN}$ CC        | -                     | 33                                                 | pF   | 7)                                             |  |

1) TUE is tested at  $V_{AREF}$  = 5.0 V,  $V_{AGND}$  = 0 V,  $V_{DD}$  = 4.9 V. It is guaranteed by design for all other voltages within the defined voltage range.

If the analog reference supply voltage exceeds the power supply voltage by up to 0.2 V  $\,$

(i.e.  $V_{AREF} = V_{DD} + 0.2 \text{ V}$ ) the maximum TUE is increased to ±3 LSB. This range is not 100% tested.

The specified TUE is guaranteed only if the absolute sum of input overload currents on Port 5 pins (see  $I_{OV}$  specification) does not exceed 10 mA.

During the reset calibration sequence the maximum TUE may be  $\pm$ 4 LSB.

- V<sub>AIN</sub> may exceed V<sub>AGND</sub> or V<sub>AREF</sub> up to the absolute maximum ratings. However, the conversion result in these cases will be X000<sub>H</sub> or X3FF<sub>H</sub>, respectively.

- 3) The limit values for  $f_{\rm BC}$  must not be exceeded when selecting the CPU frequency and the ADCTC setting.

- 4) This parameter includes the sample time t<sub>S</sub>, the time for determining the digital result and the time to load the result register with the conversion result.

Values for the basic clock t<sub>BC</sub> depend on programming and can be taken from Table 14.

This parameter depends on the ADC control logic. It is not a real maximum value, but rather a fixum.

- This parameter depends on the ADC control logic. It is not a real maximum value, but rather a fixum.

- 5) During the reset calibration conversions can be executed (with the current accuracy). The time required for these conversions is added to the total reset calibration time.

- 6) During the conversion the ADC's capacitance must be repeatedly charged or discharged. The internal resistance of the reference voltage source must allow the capacitance to reach its respective voltage level within each conversion step. The maximum internal resistance results from the programmed conversion timing.

- 7) Not subject to production test verified by design/characterization.

8) During the sample time the input capacitance  $C_{AIN}$  can be charged/discharged by the external source. The internal resistance of the analog source must allow the capacitance to reach its final voltage level within  $t_{S}$ . After the end of the sample time  $t_{S}$ , changes of the analog input voltage have no effect on the conversion result.

Values for the sample time  $t_{\rm S}$  depend on programming and can be taken from **Table 14**.

Sample time and conversion time of the C167CR's A/D Converter are programmable. **Table 14** should be used to calculate the above timings. The limit values for f must not be exceeded when selecting ADCTC

The limit values for  $f_{\rm BC}$  must not be exceeded when selecting ADCTC.

| ADCON.15 14<br>(ADCTC) | A/D Converter<br>Basic clock $f_{\rm BC}$ | ADCON.13 12<br>(ADSTC) | Sample time<br>t <sub>s</sub> |  |

|------------------------|-------------------------------------------|------------------------|-------------------------------|--|

| 00                     | <i>f</i> <sub>СРU</sub> / 4               | 00                     | $t_{\rm BC} 	imes 8$          |  |

| 01                     | f <sub>сри</sub> / 2                      | 01                     | $t_{\rm BC} 	imes$ 16         |  |

| 10                     | <i>f</i> <sub>СРU</sub> / 16              | 10                     | $t_{\rm BC} 	imes 32$         |  |

| 11                     | f <sub>сри</sub> / 8                      | 11                     | $t_{\rm BC} 	imes 64$         |  |

#### Table 14 A/D Converter Computation Table

### **Converter Timing Example:**

| Assumptions:       | $f_{\rm CPU}$  | = 25 MHz (i.e. <i>t</i> <sub>CPU</sub> = 40 ns), ADCTC = '00', ADSTC = '00'        |

|--------------------|----------------|------------------------------------------------------------------------------------|

| Basic clock        | $f_{\rm BC}$   | = f <sub>CPU</sub> / 4 = 6.25 MHz, i.e. t <sub>BC</sub> = 160 ns                   |

| Sample time        | t <sub>S</sub> | = <i>t</i> <sub>BC</sub> × 8 = 1280 ns                                             |

| Conversion<br>time | t <sub>C</sub> | = $t_{\rm S}$ + 40 $t_{\rm BC}$ + 2 $t_{\rm CPU}$ = (1280 + 6400 + 80) ns = 7.8 µs |

upper half of PORT0 (P0H), i.e. bitfield CLKCFG represents the logic levels on pins P0.15-13 (P0H.7-5).

Table 15 associates the combinations of these three bits with the respective clock generation mode.

| CLKCFG<br>(P0H.7-5) | CPU Frequency $f_{CPU} = f_{OSC} \times F$ | External Clock<br>Input Range <sup>1)</sup> | Notes                      |  |  |

|---------------------|--------------------------------------------|---------------------------------------------|----------------------------|--|--|

| 111                 | $f_{\rm OSC} \times 4$                     | 2.5 to 8.25 MHz                             | Default configuration      |  |  |

| 110                 | $f_{\rm OSC} \times 3$                     | 3.33 to 11 MHz                              | -                          |  |  |

| 101                 | $f_{\rm OSC} \times 2$                     | 5 to 16.5 MHz                               | -                          |  |  |

| 100                 | $f_{\rm OSC} 	imes 5$                      | 2 to 6.6 MHz                                | -                          |  |  |

| 011                 | $f_{\rm OSC} 	imes 1$                      | 1 to 33 MHz                                 | Direct drive <sup>2)</sup> |  |  |

| 010                 | $f_{\rm OSC} 	imes$ 1.5                    | 6.66 to 22 MHz                              | -                          |  |  |

| 001                 | <i>f</i> <sub>OSC</sub> / 2                | 2 to 66 MHz                                 | CPU clock via prescaler    |  |  |

| 000                 | $f_{\rm OSC} \times 2.5$                   | 4 to 13.2 MHz                               | -                          |  |  |

Table 15

C167CR Clock Generation Modes

1) The external clock input range refers to a CPU clock range of 10 ... 33 MHz (PLL operation).

2) The maximum frequency depends on the duty cycle of the external clock signal.

# Prescaler Operation

When prescaler operation is configured (CLKCFG =  $001_B$ ) the CPU clock is derived from the internal oscillator (input clock signal) by a 2:1 prescaler.

The frequency of  $f_{\text{CPU}}$  is half the frequency of  $f_{\text{OSC}}$  and the high and low time of  $f_{\text{CPU}}$  (i.e. the duration of an individual TCL) is defined by the period of the input clock  $f_{\text{OSC}}$ .

The timings listed in the AC Characteristics that refer to TCLs therefore can be calculated using the period of  $f_{\rm OSC}$  for any TCL.

## Phase Locked Loop

When PLL operation is configured (via CLKCFG) the on-chip phase locked loop is enabled and provides the CPU clock (see table above). The PLL multiplies the input frequency by the factor **F** which is selected via the combination of pins P0.15-13 (i.e.  $f_{CPU} = f_{OSC} \times \mathbf{F}$ ). With every **F**'th transition of  $f_{OSC}$  the PLL circuit synchronizes the CPU clock to the input clock. This synchronization is done smoothly, i.e. the CPU clock frequency does not change abruptly.

Due to this adaptation to the input clock the frequency of  $f_{\rm CPU}$  is constantly adjusted so it is locked to  $f_{\rm OSC}$ . The slight variation causes a jitter of  $f_{\rm CPU}$  which also effects the duration of individual TCLs.

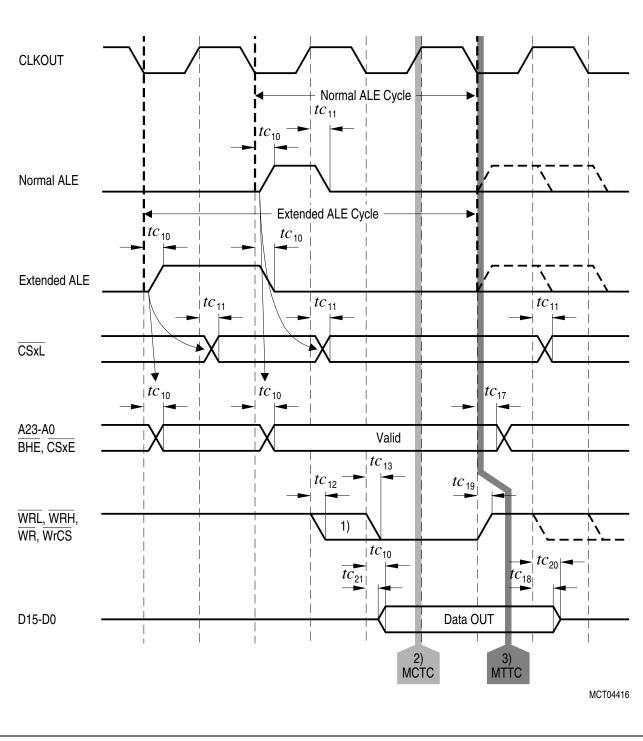

## General Notes for the Following Timing Figures

These standard notes apply to all subsequent timing figures. Additional individual notes are placed at the respective figure.

- 1. The falling edge of signals  $\overline{RD}$  and  $\overline{WR}/\overline{WRH}/\overline{WRL}/\overline{WrCS}$  is controlled by the Read/Write delay feature (bit BUSCON.RWDCx).

- 2. A bus cycle is extended here, if MCTC waitstates are selected or if the READY input is sampled inactive.

- 3. A bus cycle is extended here, if an MTTC waitstate is selected.

Figure 16 Demultiplexed Bus, Write Access

# **External Bus Arbitration**

# Table 21 Bus Arbitration Timing (Operating Conditions apply)

| Parameter                                    | Symbol                  |    | Limits |      | Unit |

|----------------------------------------------|-------------------------|----|--------|------|------|

|                                              |                         |    | Min.   | Max. |      |

| HOLD input setup time to CLKOUT falling edge | <i>tc</i> <sub>28</sub> | SR | 18     | _    | ns   |

| CLKOUT to BREQ delay                         | <i>tc</i> <sub>29</sub> | CC | -4     | 6    | ns   |

| CLKOUT to HLDA delay                         | <i>tc</i> <sub>30</sub> | CC | -4     | 6    | ns   |

| CSx release <sup>1)</sup>                    | <i>tc</i> <sub>31</sub> | CC | 0      | 10   | ns   |

| CSx drive                                    | <i>tc</i> <sub>32</sub> | CC | -2     | 6    | ns   |

| Other signals release <sup>1)</sup>          | <i>tc</i> <sub>33</sub> | CC | 0      | 10   | ns   |

| Other signals drive <sup>1)</sup>            | <i>tc</i> <sub>34</sub> | CC | 0      | 6    | ns   |

|                                              |                         |    | I      | I    |      |

1) Not subject to production test - verified by design/characterization.

C167CR C167SR

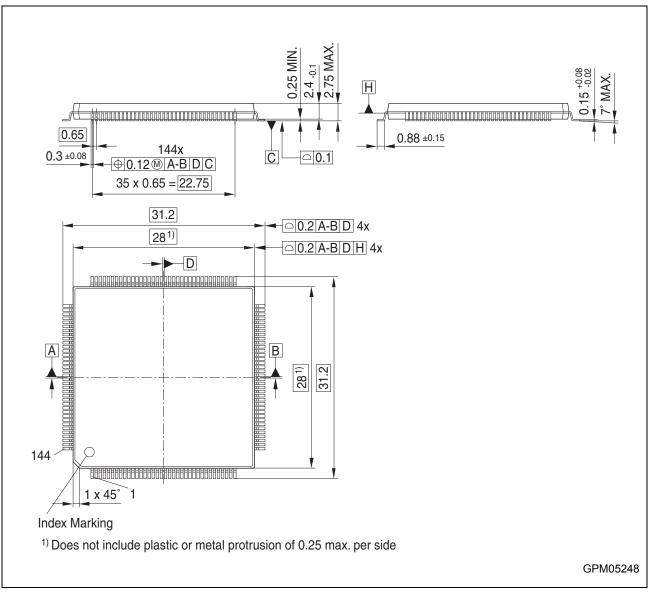

## **Package Outlines**

You can find all of our packages, sorts of packing and others in our Infineon Internet Page "Products": http://www.infineon.com/products. Dimensions in mm