#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | C166                                                                        |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 25MHz                                                                       |

| Connectivity               | CANbus, EBI/EMI, SPI, UART/USART                                            |

| Peripherals                | POR, PWM, WDT                                                               |

| Number of I/O              | 111                                                                         |

| Program Memory Size        | -                                                                           |

| Program Memory Type        | ROMIess                                                                     |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                 |

| Data Converters            | A/D 16x10b                                                                  |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 144-BQFP                                                                    |

| Supplier Device Package    | P-MQFP-144-8                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/c167crlmhabxuma2 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

C167CR C167SR

#### **Table of Contents**

# **Table of Contents**

| Table of Contents                                                                                                                                                                                                                                                                                                                                                    | 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Summary of Features                                                                                                                                                                                                                                                                                                                                                  | 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| General Device Information       Introduction         Introduction       Introduction         Pin Configuration and Definition for P-MQFP-144-8       8         Pin Configuration and Definition for P-BGA-176-2       1                                                                                                                                             | 7<br>8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Functional Description26Memory Organization27External Bus Controller28Central Processing Unit (CPU)30Interrupt System32Capture/Compare (CAPCOM) Units36PWM Module38General Purpose Timer (GPT) Unit39A/D Converter42Serial Channels43CAN-Module44Watchdog Timer44Parallel Ports44Oscillator Watchdog44Instruction Set Summary50Special Function Registers Overview50 | 78026892344567                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Electrical Parameters58General Parameters58DC Parameters60Analog/Digital Converter Parameters64AC Parameters66Definition of Internal Timing66External Clock Drive XTAL170Testing Waveforms72External Bus Timing72Package Outlines88                                                                                                                                  | 8<br>0<br>4<br>6<br>0<br>1<br>2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                      | Summary of Features       General Device Information         Introduction       Pin Configuration and Definition for P-MQFP-144-8         Pin Configuration and Definition for P-BGA-176-2       1         Functional Description       2         Memory Organization       2         External Bus Controller       2         Central Processing Unit (CPU)       3         Interrupt System       3         Capture/Compare (CAPCOM) Units       3         PWM Module       3         General Purpose Timer (GPT) Unit       3         A/D Converter       4         Serial Channels       4         CAN-Module       4         Watchdog Timer       4         Parallel Ports       4         Oscillator Watchdog       44         Instruction Set Summary       4         Special Function Registers Overview       55         General Parameters       56         DC Parameters       56         Definition of Internal Timing       66         Actoral Clock Drive XTAL1       70         Testing Waveforms       7 |

C167CR/C167SR

#### 16-Bit Single-Chip Microcontroller C166 Family

# 1 Summary of Features

- High Performance 16-bit CPU with 4-Stage Pipeline

- 80/60 ns Instruction Cycle Time at 25/33 MHz CPU Clock

- 400/303 ns Multiplication (16  $\times$  16 bits), 800/606 ns Division (32 / 16 bits)

- Enhanced Boolean Bit Manipulation Facilities

- Additional Instructions to Support HLL and Operating Systems

- Register-Based Design with Multiple Variable Register Banks

- Single-Cycle Context Switching Support

- 16 Mbytes Total Linear Address Space for Code and Data

- 1024 Bytes On-Chip Special Function Register Area

- 16-Priority-Level Interrupt System with 56 Sources, Sample-Rate down to 40/30 ns

- 8-Channel Interrupt-Driven Single-Cycle Data Transfer Facilities via Peripheral Event Controller (PEC)

- Clock Generation via on-chip PLL (factors 1:1.5/2/2.5/3/4/5), via prescaler or via direct clock input

- On-Chip Memory Modules

- 2 Kbytes On-Chip Internal RAM (IRAM)

- 2 Kbytes On-Chip Extension RAM (XRAM)

- 128/32 Kbytes On-Chip Mask ROM

- On-Chip Peripheral Modules

- 16-Channel 10-bit A/D Converter with Programmable Conversion Time down to 7.8  $\mu s$

- Two 16-Channel Capture/Compare Units

- 4-Channel PWM Unit

- Two Multi-Functional General Purpose Timer Units with 5 Timers

- Two Serial Channels (Synchronous/Asynchronous and High-Speed-Synchronous)

- On-Chip CAN Interface (Rev. 2.0B active) with 15 Message Objects (Full CAN / Basic CAN)

- Up to 16 Mbytes External Address Space for Code and Data

- Programmable External Bus Characteristics for Different Address Ranges

- Multiplexed or Demultiplexed External Address/Data Buses with 8-Bit or 16-Bit Data Bus Width

- Five Programmable Chip-Select Signals

- Hold- and Hold-Acknowledge Bus Arbitration Support

- Idle and Power Down Modes

- Programmable Watchdog Timer and Oscillator Watchdog

| Table 2    | Pir        | n Defini       | tions and Functions P-MQFP-144-8 (cont'd)                                                                                                                                                                                                                                                               |

|------------|------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol     | Pin<br>No. | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                |

| P4         |            | IO             | Port 4 is an 8-bit bidirectional I/O port. It is bit-wise<br>programmable for input or output via direction bits. For a pin<br>configured as input, the output driver is put into high-<br>impedance state.<br>Port 4 can be used to output the segment address lines and<br>for serial bus interfaces: |

| P4.0       | 85         | 0              | A16 Least Significant Segment Address Line                                                                                                                                                                                                                                                              |

| P4.1       | 86         | 0              | A17 Segment Address Line                                                                                                                                                                                                                                                                                |

| P4.2       | 87         | 0              | A18 Segment Address Line                                                                                                                                                                                                                                                                                |

| P4.3       | 88         | 0              | A19 Segment Address Line                                                                                                                                                                                                                                                                                |

| P4.4       | 89         | 0              | A20 Segment Address Line                                                                                                                                                                                                                                                                                |

| P4.5       | 90         | 0              | A21 Segment Address Line,                                                                                                                                                                                                                                                                               |

|            |            | 1              | CAN1_RxD CAN 1 Receive Data Input                                                                                                                                                                                                                                                                       |

| P4.6       | 91         | 0              | A22 Segment Address Line,                                                                                                                                                                                                                                                                               |

|            |            | 0              | CAN1_TxD CAN 1 Transmit Data Output                                                                                                                                                                                                                                                                     |

| P4.7       | 92         | 0              | A23 Most Significant Segment Address Line                                                                                                                                                                                                                                                               |

| RD         | 95         | 0              | External Memory Read Strobe. $\overline{RD}$ is activated for every external instruction or data read access.                                                                                                                                                                                           |

| WR/<br>WRL | 96         | 0              | External Memory Write Strobe. In WR-mode this pin is<br>activated for every external data write access. In WRL-mode<br>this pin is activated for low byte data write accesses on a<br>16-bit bus, and for every data write access on an 8-bit bus.<br>See WRCFG in register SYSCON for mode selection.  |

| READY      | 97         | I              | Ready Input. When the Ready function is enabled, a high<br>level at this pin during an external memory access will force<br>the insertion of memory cycle time waitstates until the pin<br>returns to a low level.<br>An internal pull-up device will hold this pin high when nothing<br>is driving it. |

| ALE        | 98         | 0              | Address Latch Enable Output. Can be used for latching the address into external memory or an address latch in the multiplexed bus modes.                                                                                                                                                                |

| ĒĀ         | 99         | I              | External Access Enable pin. A low level at this pin during and<br>after Reset forces the C167CR to begin instruction execution<br>out of external memory. A high level forces execution out of<br>the internal program memory.<br>"ROMless" versions must have this pin tied to '0'.                    |

| Table 2    | Pin        | Definit        | tions and Functions P-MQFP-144-8 (cont'd)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|------------|------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol     | Pin<br>No. | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RSTIN      | 140        | I/O            | Reset Input with Schmitt-Trigger characteristics. A low level<br>at this pin while the oscillator is running resets the C167CR.<br>An internal pull-up resistor permits power-on reset using only<br>a capacitor connected to $V_{SS}$ .<br>A spike filter suppresses input pulses < 10 ns. Input pulses<br>> 100 ns safely pass the filter. The minimum duration for a<br>safe recognition should be 100 ns + 2 CPU clock cycles.<br>In bidirectional reset mode (enabled by setting bit BDRSTEN<br>in register SYSCON) the RSTIN line is internally pulled low<br>for the duration of the internal reset sequence upon any reset<br>(HW, SW, WDT). See note below this table. |

|            |            |                | Note: To let the reset configuration of PORT0 settle and to let<br>the PLL lock a reset duration of ca. 1 ms is<br>recommended.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| RST<br>OUT | 141        | 0              | Internal Reset Indication Output. This pin is set to a low level<br>when the part is executing either a hardware-, a software- or<br>a watchdog timer reset. RSTOUT remains low until the EINIT<br>(end of initialization) instruction is executed.                                                                                                                                                                                                                                                                                                                                                                                                                             |

| NMI        | 142        | 1              | Non-Maskable Interrupt Input. A high to low transition at this<br>pin causes the CPU to vector to the NMI trap routine. When<br>the PWRDN (power down) instruction is executed, the NMI<br>pin must be low in order to force the C167CR to go into power<br>down mode. If NMI is high, when PWRDN is executed, the<br>part will continue to run in normal mode.<br>If not used, pin NMI should be pulled high externally.                                                                                                                                                                                                                                                       |

| $V_{AREF}$ | 37         | _              | Reference voltage for the A/D converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $V_{AGND}$ | 38         | _              | Reference ground for the A/D converter.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Table 3      | Pir         | Definit        | tions and Functions P-BGA-176-2                                                                                                                                                                                                                                                                                                                      |

|--------------|-------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol       | Pin<br>Num. | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                                                             |

| P5           |             | 1              | Port 5 is a 16-bit input-only port with Schmitt-Trigger                                                                                                                                                                                                                                                                                              |

|              |             |                | characteristic.                                                                                                                                                                                                                                                                                                                                      |

|              |             |                | The pins of Port 5 also serve as analog input channels for the                                                                                                                                                                                                                                                                                       |

|              | ۸ <i>Б</i>  |                | A/D converter, or they serve as timer inputs:                                                                                                                                                                                                                                                                                                        |

| P5.0         | A5          |                |                                                                                                                                                                                                                                                                                                                                                      |

| P5.1<br>P5.2 | D5<br>A4    |                | AN1<br>AN2                                                                                                                                                                                                                                                                                                                                           |

| P5.2<br>P5.3 | C5          |                | AN3                                                                                                                                                                                                                                                                                                                                                  |

| P5.4         | B4          |                | AN4                                                                                                                                                                                                                                                                                                                                                  |

| P5.5         | A3          |                | AN5                                                                                                                                                                                                                                                                                                                                                  |

| P5.6         | C4          |                | ANG                                                                                                                                                                                                                                                                                                                                                  |

| P5.7         | D4          | li –           | AN7                                                                                                                                                                                                                                                                                                                                                  |

| P5.8         | B3          | I              | AN8                                                                                                                                                                                                                                                                                                                                                  |

| P5.9         | C3          | 1              | AN9                                                                                                                                                                                                                                                                                                                                                  |

| P5.10        | D3          | 1              | AN10, T6EUD GPT2 Timer T6 Ext. Up/Down Ctrl. Inp.                                                                                                                                                                                                                                                                                                    |

| P5.11        | C1          | 1              | AN11, T5EUD GPT2 Timer T5 Ext. Up/Down Ctrl. Inp.                                                                                                                                                                                                                                                                                                    |

| P5.12        | D1          | 1              | AN12, T6IN GPT2 Timer T6 Count Inp.                                                                                                                                                                                                                                                                                                                  |

| P5.13        | D2          | 1              | AN13, T5IN GPT2 Timer T5 Count Inp.                                                                                                                                                                                                                                                                                                                  |

| P5.14        | E3          | 1              | AN14, T4EUD GPT1 Timer T4 Ext. Up/Down Ctrl. Inp.                                                                                                                                                                                                                                                                                                    |

| P5.15        | E2          | 1              | AN15, T2EUD GPT1 Timer T5 Ext. Up/Down Ctrl. Inp.                                                                                                                                                                                                                                                                                                    |

| P7           |             | IO             | Port 7 is an 8-bit bidirectional I/O port. It is bit-wise<br>programmable for input or output via direction bits. For a pin<br>configured as input, the output driver is put into high-<br>impedance state. Port 7 outputs can be configured as<br>push/pull or open drain drivers. The input threshold of Port 7<br>is selectable (TTL or special). |

|              |             |                | The following Port 7 pins also serve for alternate functions:                                                                                                                                                                                                                                                                                        |

| P7.0         | D7          | 0              | POUT0 PWM Channel 0 Output                                                                                                                                                                                                                                                                                                                           |

| P7.1         | C7          | 0              | POUT1 PWM Channel 1 Output                                                                                                                                                                                                                                                                                                                           |

| P7.2         | B7          | 0              | POUT2 PWM Channel 2 Output                                                                                                                                                                                                                                                                                                                           |

| P7.3         | A7          | 0              | POUT3 PWM Channel 3 Output                                                                                                                                                                                                                                                                                                                           |

| P7.4         | D6          | I/O            | CC28IO CAPCOM2: CC28 Capture Inp./Compare Outp.                                                                                                                                                                                                                                                                                                      |

| P7.5         | C6          | I/O            | CC29IO CAPCOM2: CC29 Capture Inp./Compare Outp.                                                                                                                                                                                                                                                                                                      |

| P7.6         | B6          | I/O            | CC30IO CAPCOM2: CC30 Capture Inp./Compare Outp.                                                                                                                                                                                                                                                                                                      |

| P7.7         | A6          | I/O            | CC31IO CAPCOM2: CC31 Capture Inp./Compare Outp.                                                                                                                                                                                                                                                                                                      |

| Table 3                                      | Pin Definitions and Functions P-BGA-176-2 (cont'd) |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

|----------------------------------------------|----------------------------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Symbol                                       | Pin<br>Num.                                        | Input<br>Outp. | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| P8                                           |                                                    | IO             | Port 8 is an 8-bit bidirectional I/O port. It is bit-wise<br>programmable for input or output via direction bits. For a pin<br>configured as input, the output driver is put into high-<br>mpedance state. Port 8 outputs can be configured as<br>bush/pull or open drain drivers. The input threshold of Port 8<br>s selectable (TTL or special).<br>The following Port 8 pins also serve for alternate functions:                                                                                                                                              |  |  |  |

| P8.0                                         | B10                                                | I/O            | CC16IO CAPCOM2: CC16 Capture Inp./Compare Outp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| P8.1                                         | A10                                                | 1/0            | CC17IO CAPCOM2: CC17 Capture Inp./Compare Outp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| P8.2                                         | D9                                                 | 1/0            | CC18IO CAPCOM2: CC18 Capture Inp./Compare Outp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| P8.3<br>P8.4                                 | C9<br>B9                                           | 1/O<br>1/O     | CC19IO CAPCOM2: CC19 Capture Inp./Compare Outp.<br>CC20IO CAPCOM2: CC20 Capture Inp./Compare Outp.                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| P8.5                                         | A9                                                 | 1/0            | CC21IO CAPCOM2: CC21 Capture Inp./Compare Outp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| P8.6                                         | D8                                                 | 1/0            | CC22IO CAPCOM2: CC22 Capture Inp./Compare Outp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| P8.7                                         | C8                                                 | I/O            | CC23IO CAPCOM2: CC23 Capture Inp./Compare Outp.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |

| P6.0<br>P6.1<br>P6.2<br>P6.3<br>P6.4<br>P6.5 | A13<br>B12<br>D10<br>C11<br>A12<br>B11             |                | Port 6 is an 8-bit bidirectional I/O port. It is bit-wise<br>programmable for input or output via direction bits. For a pin<br>configured as input, the output driver is put into high-<br>impedance state. Port 6 outputs can be configured as<br>push/pull or open drain drivers. The input threshold of Port 6<br>is selectable (TTL or special).The Port 6 pins also serve for alternate functions:CS0Chip Select 0 OutputCS1Chip Select 1 OutputCS2Chip Select 2 OutputCS3Chip Select 3 OutputCS4Chip Select 4 OutputHOLDExternal Master Hold Request Input |  |  |  |

| P6.6                                         | C10                                                | I/O            | HLDA Hold Acknowledge Output (master mode) or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

|                                              |                                                    |                | Input (slave mode)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| P6.7                                         | A11                                                | 0              | BREQ Bus Request Output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| <u>NMI</u>                                   | C14                                                | 1              | Non-Maskable Interrupt Input. A high to low transition at this<br>pin causes the CPU to vector to the NMI trap routine. When<br>the PWRDN (power down) instruction is executed, the NMI<br>pin must be low in order to force the C167CR to go into power<br>down mode. If NMI is high, when PWRDN is executed, the<br>part will continue to run in normal mode.<br>If not used, pin NMI should be pulled high externally.                                                                                                                                        |  |  |  |

# 3 Functional Description

The architecture of the C167CR combines advantages of both RISC and CISC processors and of advanced peripheral subsystems in a very well-balanced way. In addition the on-chip memory blocks allow the design of compact systems with maximum performance.

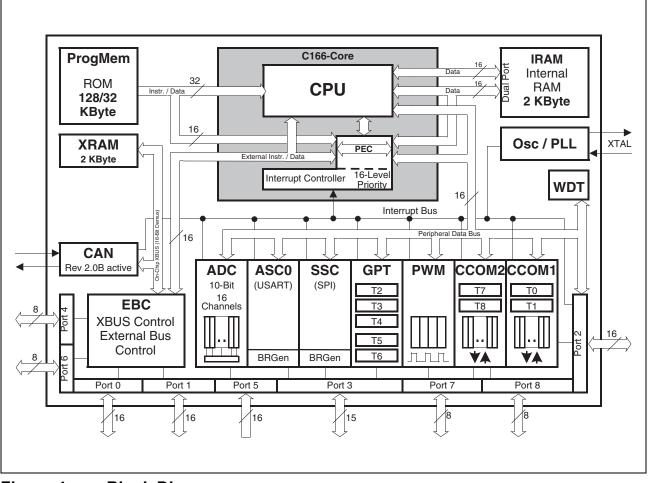

The following block diagram gives an overview of the different on-chip components and of the advanced, high bandwidth internal bus structure of the C167CR.

Note: All time specifications refer to a CPU clock of 33 MHz (see definition in the AC Characteristics section).

#### Figure 4 Block Diagram

The program memory, the internal RAM (IRAM) and the set of generic peripherals are connected to the CPU via separate buses. A fourth bus, the XBUS, connects external resources as well as additional on-chip resources, the X-Peripherals (see Figure 4).

#### 3.1 Memory Organization

The memory space of the C167CR is configured in a Von Neumann architecture which means that code memory, data memory, registers and I/O ports are organized within the same linear address space which includes 16 Mbytes. The entire memory space can be accessed bytewise or wordwise. Particular portions of the on-chip memory have additionally been made directly bitaddressable.

The C167CR incorporates 128/32 Kbytes (depending on the derivative) of on-chip maskprogrammable ROM for code or constant data. The lower 32 Kbytes of the on-chip ROM can be mapped either to segment 0 or segment 1.

2 Kbytes of on-chip Internal RAM (IRAM) are provided as a storage for user defined variables, for the system stack, general purpose register banks and even for code. A register bank can consist of up to 16 wordwide (R0 to R15) and/or bytewide (RL0, RH0, ..., RL7, RH7) so-called General Purpose Registers (GPRs).

1024 bytes ( $2 \times 512$  bytes) of the address space are reserved for the Special Function Register areas (SFR space and ESFR space). SFRs are wordwide registers which are used for controlling and monitoring functions of the different on-chip units. Unused SFR addresses are reserved for future members of the C166 Family.

2 Kbytes of on-chip Extension RAM (XRAM) are provided to store user data, user stacks, or code. The XRAM is accessed like external memory and therefore cannot be used for the system stack or for register banks and is not bitaddressable. The XRAM permits 16-bit accesses with maximum speed.

In order to meet the needs of designs where more memory is required than is provided on chip, up to 16 Mbytes of external RAM and/or ROM can be connected to the microcontroller.

## Table 4 C167CR Interrupt Nodes

| Source of Interrupt or PEC Service Request | Request<br>Flag | Enable<br>Flag | Interrupt<br>Vector | Vector<br>Location   | Trap<br>Number  |

|--------------------------------------------|-----------------|----------------|---------------------|----------------------|-----------------|

| CAPCOM Register 0                          | CC0IR           | CC0IE          | CC0INT              | 00'0040 <sub>H</sub> | 10 <sub>H</sub> |

| CAPCOM Register 1                          | CC1IR           | CC1IE          | CC1INT              | 00'0044 <sub>H</sub> | 11 <sub>H</sub> |

| CAPCOM Register 2                          | CC2IR           | CC2IE          | CC2INT              | 00'0048 <sub>H</sub> | 12 <sub>H</sub> |

| CAPCOM Register 3                          | CC3IR           | CC3IE          | CC3INT              | 00'004C <sub>H</sub> | 13 <sub>H</sub> |

| CAPCOM Register 4                          | CC4IR           | CC4IE          | CC4INT              | 00'0050 <sub>H</sub> | 14 <sub>H</sub> |

| CAPCOM Register 5                          | CC5IR           | CC5IE          | CC5INT              | 00'0054 <sub>H</sub> | 15 <sub>H</sub> |

| CAPCOM Register 6                          | CC6IR           | CC6IE          | CC6INT              | 00'0058 <sub>H</sub> | 16 <sub>H</sub> |

| CAPCOM Register 7                          | CC7IR           | CC7IE          | CC7INT              | 00'005C <sub>H</sub> | 17 <sub>H</sub> |

| CAPCOM Register 8                          | CC8IR           | CC8IE          | CC8INT              | 00'0060 <sub>H</sub> | 18 <sub>H</sub> |

| CAPCOM Register 9                          | CC9IR           | CC9IE          | CC9INT              | 00'0064 <sub>H</sub> | 19 <sub>H</sub> |

| CAPCOM Register 10                         | CC10IR          | CC10IE         | CC10INT             | 00'0068 <sub>H</sub> | 1A <sub>H</sub> |

| CAPCOM Register 11                         | CC11IR          | CC11IE         | CC11INT             | 00'006C <sub>H</sub> | 1B <sub>H</sub> |

| CAPCOM Register 12                         | CC12IR          | CC12IE         | CC12INT             | 00'0070 <sub>H</sub> | 1C <sub>H</sub> |

| CAPCOM Register 13                         | CC13IR          | CC13IE         | CC13INT             | 00'0074 <sub>H</sub> | 1D <sub>H</sub> |

| CAPCOM Register 14                         | CC14IR          | CC14IE         | CC14INT             | 00'0078 <sub>H</sub> | 1E <sub>H</sub> |

| CAPCOM Register 15                         | CC15IR          | CC15IE         | CC15INT             | 00'007C <sub>H</sub> | 1F <sub>H</sub> |

| CAPCOM Register 16                         | CC16IR          | CC16IE         | CC16INT             | 00'00C0 <sub>H</sub> | 30 <sub>H</sub> |

| CAPCOM Register 17                         | CC17IR          | CC17IE         | CC17INT             | 00'00C4 <sub>H</sub> | 31 <sub>H</sub> |

| CAPCOM Register 18                         | CC18IR          | CC18IE         | CC18INT             | 00'00C8 <sub>H</sub> | 32 <sub>H</sub> |

| CAPCOM Register 19                         | CC19IR          | CC19IE         | CC19INT             | 00'00CC <sub>H</sub> | 33 <sub>H</sub> |

| CAPCOM Register 20                         | CC20IR          | CC20IE         | CC20INT             | 00'00D0 <sub>H</sub> | 34 <sub>H</sub> |

| CAPCOM Register 21                         | CC21IR          | CC21IE         | CC21INT             | 00'00D4 <sub>H</sub> | 35 <sub>H</sub> |

| CAPCOM Register 22                         | CC22IR          | CC22IE         | CC22INT             | 00'00D8 <sub>H</sub> | 36 <sub>H</sub> |

| CAPCOM Register 23                         | CC23IR          | CC23IE         | CC23INT             | 00'00DC <sub>H</sub> | 37 <sub>H</sub> |

| CAPCOM Register 24                         | CC24IR          | CC24IE         | CC24INT             | 00'00E0 <sub>H</sub> | 38 <sub>H</sub> |

| CAPCOM Register 25                         | CC25IR          | CC25IE         | CC25INT             | 00'00E4 <sub>H</sub> | 39 <sub>H</sub> |

| CAPCOM Register 26                         | CC26IR          | CC26IE         | CC26INT             | 00'00E8 <sub>H</sub> | 3A <sub>H</sub> |

| CAPCOM Register 27                         | CC27IR          | CC27IE         | CC27INT             | 00'00EC <sub>H</sub> | 3B <sub>H</sub> |

| CAPCOM Register 28                         | CC28IR          | CC28IE         | CC28INT             | 00'00E0 <sub>H</sub> | 3C <sub>H</sub> |

| CAPCOM Register 29                         | CC29IR          | CC29IE         | CC29INT             | 00'0110 <sub>H</sub> | 44 <sub>H</sub> |

| Compare Modes           | Function                                                                                                                         |

|-------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Mode 0                  | Interrupt-only compare mode;<br>several compare interrupts per timer period are possible                                         |

| Mode 1                  | Pin toggles on each compare match;<br>several compare events per timer period are possible                                       |

| Mode 2                  | Interrupt-only compare mode;<br>only one compare interrupt per timer period is generated                                         |

| Mode 3                  | Pin set '1' on match; pin reset '0' on compare time overflow;<br>only one compare event per timer period is generated            |

| Double<br>Register Mode | Two registers operate on one pin;<br>pin toggles on each compare match;<br>several compare events per timer period are possible. |

## Table 6 Compare Modes (CAPCOM)

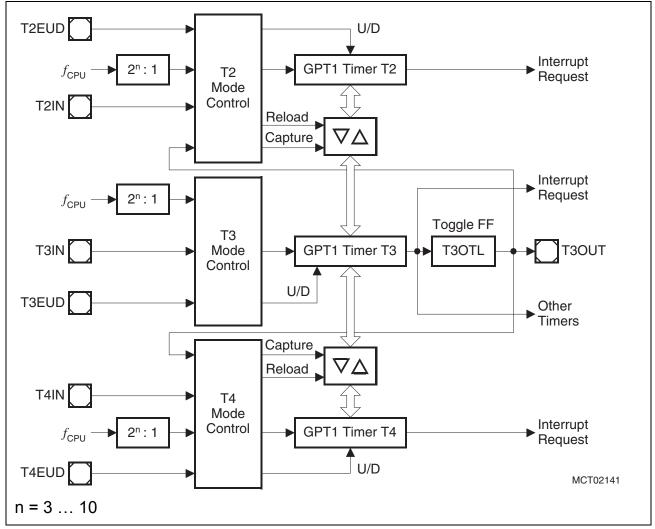

#### 3.7 General Purpose Timer (GPT) Unit

The GPT unit represents a very flexible multifunctional timer/counter structure which may be used for many different time related tasks such as event timing and counting, pulse width and duty cycle measurements, pulse generation, or pulse multiplication.

The GPT unit incorporates five 16-bit timers which are organized in two separate modules, GPT1 and GPT2. Each timer in each module may operate independently in a number of different modes, or may be concatenated with another timer of the same module.

Each of the three timers T2, T3, T4 of **module GPT1** can be configured individually for one of four basic modes of operation, which are Timer, Gated Timer, Counter, and Incremental Interface Mode. In Timer Mode, the input clock for a timer is derived from the CPU clock, divided by a programmable prescaler, while Counter Mode allows a timer to be clocked in reference to external events.

Pulse width or duty cycle measurement is supported in Gated Timer Mode, where the operation of a timer is controlled by the 'gate' level on an external input pin. For these purposes, each timer has one associated port pin (TxIN) which serves as gate or clock input. The maximum resolution of the timers in module GPT1 is 16 TCL.

The count direction (up/down) for each timer is programmable by software or may additionally be altered dynamically by an external signal on a port pin (TxEUD) to facilitate e.g. position tracking.

In Incremental Interface Mode the GPT1 timers (T2, T3, T4) can be directly connected to the incremental position sensor signals A and B via their respective inputs TxIN and TxEUD. Direction and count signals are internally derived from these two input signals, so the contents of the respective timer Tx corresponds to the sensor position. The third position sensor signal TOP0 can be connected to an interrupt input.

Timer T3 has an output toggle latch (T3OTL) which changes its state on each timer overflow/underflow. The state of this latch may be output on pin T3OUT e.g. for time out monitoring of external hardware components, or may be used internally to clock timers T2 and T4 for measuring long time periods with high resolution.

In addition to their basic operating modes, timers T2 and T4 may be configured as reload or capture registers for timer T3. When used as capture or reload registers, timers T2 and T4 are stopped. The contents of timer T3 is captured into T2 or T4 in response to a signal at their associated input pins (TxIN). Timer T3 is reloaded with the contents of T2 or T4 triggered either by an external signal or by a selectable state transition of its toggle latch T3OTL. When both T2 and T4 are configured to alternately reload T3 on opposite state transitions of T3OTL with the low and high times of a PWM signal, this signal can be constantly generated without software intervention.

#### Figure 7 Block Diagram of GPT1

With its maximum resolution of 8 TCL, the **GPT2 module** provides precise event control and time measurement. It includes two timers (T5, T6) and a capture/reload register (CAPREL). Both timers can be clocked with an input clock which is derived from the CPU clock via a programmable prescaler or with external signals. The count direction (up/down) for each timer is programmable by software or may additionally be altered dynamically by an external signal on a port pin (TxEUD). Concatenation of the timers is supported via the output toggle latch (T6OTL) of timer T6, which changes its state on each timer overflow/underflow.

The state of this latch may be used to clock timer T5, and/or it may be output on pin T6OUT. The overflows/underflows of timer T6 can additionally be used to clock the CAPCOM timers T0 or T1, and to cause a reload from the CAPREL register. The CAPREL register may capture the contents of timer T5 based on an external signal transition on the corresponding port pin (CAPIN), and timer T5 may optionally be cleared after the capture procedure. This allows the C167CR to measure absolute time differences or to perform pulse multiplication without software overhead.

#### Table 8C167CR Registers, Ordered by Name (cont'd)

| Table 8 | able 8         C167CR Registers, Ordered by Name (cont'd) |                     |   |                 |                                     |                   |

|---------|-----------------------------------------------------------|---------------------|---|-----------------|-------------------------------------|-------------------|

|         |                                                           | Physical<br>Address |   | 8-Bit<br>Addr.  | Description                         | Reset<br>Value    |

| CC19IC  | b                                                         | F166 <sub>H</sub>   | Ε | B3 <sub>H</sub> | CAPCOM Reg. 19 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC1IC   | b                                                         | FF7A <sub>H</sub>   |   | BD <sub>H</sub> | CAPCOM Reg. 1 Interrupt Ctrl. Reg.  | 0000 <sub>H</sub> |

| CC2     |                                                           | FE84 <sub>H</sub>   |   | 42 <sub>H</sub> | CAPCOM Register 2                   | 0000 <sub>H</sub> |

| CC20    |                                                           | FE68 <sub>H</sub>   |   | 34 <sub>H</sub> | CAPCOM Register 20                  | 0000 <sub>H</sub> |

| CC20IC  | b                                                         | F168 <sub>H</sub>   | Ε | B4 <sub>H</sub> | CAPCOM Reg. 20 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC21    |                                                           | FE6A <sub>H</sub>   |   | 35 <sub>H</sub> | CAPCOM Register 21                  | 0000 <sub>H</sub> |

| CC21IC  | b                                                         | F16A <sub>H</sub>   | Ε | B5 <sub>H</sub> | CAPCOM Reg. 21 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC22    |                                                           | FE6C <sub>H</sub>   |   | 36 <sub>H</sub> | CAPCOM Register 22                  | 0000 <sub>H</sub> |

| CC22IC  | b                                                         | F16C <sub>H</sub>   | Ε | B6 <sub>H</sub> | CAPCOM Reg. 22 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC23    |                                                           | FE6E <sub>H</sub>   |   | 37 <sub>H</sub> | CAPCOM Register 23                  | 0000 <sub>H</sub> |

| CC23IC  | b                                                         | F16E <sub>H</sub>   | Ε | B7 <sub>H</sub> | CAPCOM Reg. 23 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC24    |                                                           | FE70 <sub>H</sub>   |   | 38 <sub>H</sub> | CAPCOM Register 24                  | 0000 <sub>H</sub> |

| CC24IC  | b                                                         | F170 <sub>H</sub>   | Ε | B8 <sub>H</sub> | CAPCOM Reg. 24 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC25    |                                                           | FE72 <sub>H</sub>   |   | 39 <sub>H</sub> | CAPCOM Register 25                  | 0000 <sub>H</sub> |

| CC25IC  | b                                                         | F172 <sub>H</sub>   | Ε | B9 <sub>H</sub> | CAPCOM Reg. 25 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC26    |                                                           | FE74 <sub>H</sub>   |   | 3A <sub>H</sub> | CAPCOM Register 26                  | 0000 <sub>H</sub> |

| CC26IC  | b                                                         | F174 <sub>H</sub>   | Ε | BA <sub>H</sub> | CAPCOM Reg. 26 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC27    |                                                           | FE76 <sub>H</sub>   |   | 3B <sub>H</sub> | CAPCOM Register 27                  | 0000 <sub>H</sub> |

| CC27IC  | b                                                         | F176 <sub>H</sub>   | Ε | BB <sub>H</sub> | CAPCOM Reg. 27 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC28    |                                                           | FE78 <sub>H</sub>   |   | 3C <sub>H</sub> | CAPCOM Register 28                  | 0000 <sub>H</sub> |

| CC28IC  | b                                                         | F178 <sub>H</sub>   | Ε | BC <sub>H</sub> | CAPCOM Reg. 28 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC29    |                                                           | FE7A <sub>H</sub>   |   | 3D <sub>H</sub> | CAPCOM Register 29                  | 0000 <sub>H</sub> |

| CC29IC  | b                                                         | F184 <sub>H</sub>   | Ε | C2 <sub>H</sub> | CAPCOM Reg. 29 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC2IC   | b                                                         | FF7C <sub>H</sub>   |   | BE <sub>H</sub> | CAPCOM Reg. 2 Interrupt Ctrl. Reg.  | 0000 <sub>H</sub> |

| CC3     |                                                           | FE86 <sub>H</sub>   |   | 43 <sub>H</sub> | CAPCOM Register 3                   | 0000 <sub>H</sub> |

| CC30    |                                                           | FE7C <sub>H</sub>   |   | 3E <sub>H</sub> | CAPCOM Register 30                  | 0000 <sub>H</sub> |

| CC30IC  | b                                                         | F18C <sub>H</sub>   | Ε | C6 <sub>H</sub> | CAPCOM Reg. 30 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC31    |                                                           | FE7E <sub>H</sub>   |   | 3F <sub>н</sub> | CAPCOM Register 31                  |                   |

| CC31IC  | b                                                         | F194 <sub>H</sub>   | Ε | CA <sub>H</sub> | CAPCOM Reg. 31 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |

| CC3IC   | b                                                         | FF7E <sub>H</sub>   |   | BF <sub>H</sub> | CAPCOM Reg. 3 Interrupt Ctrl. Reg.  | 0000 <sub>H</sub> |

Reset

Value

0000<sub>н</sub>

0000<sub>н</sub>

0000<sub>н</sub>

0000<sub>H</sub>

0000<sub>H</sub>

0000<sub>H</sub>

0000<sub>H</sub>

0000<sub>н</sub>

0000<sub>н</sub>

0000<sub>н</sub>

0000<sub>н</sub>

0000<sub>H</sub>

0000<sub>н</sub>

0000<sub>H</sub>

0000<sub>H</sub>

0000<sub>н</sub>

0000<sub>H</sub>

0000<sub>H</sub>

0000<sub>H</sub>

0000<sub>H</sub>

0000<sub>H</sub>

0000<sub>H</sub>

0000<sub>H</sub>

0000<sub>н</sub>

0000<sub>H</sub>

0000<sub>H</sub>

0000<sub>H</sub>

#### **Functional Description**

#### C167CR Registers, Ordered by Name (cont'd) Table 8 8-Bit Name Physical Description **Address** Addr. T2IC b FF60<sub>H</sub> B0<sub>H</sub> GPT1 Timer 2 Interrupt Control Register FE42<sub>H</sub> 21<sub>H</sub> **T**3 **GPT1** Timer 3 Register A1<sub>H</sub> T3CON FF42<sub>H</sub> **GPT1** Timer 3 Control Register b T3IC b FF62<sub>H</sub> B1<sub>н</sub> **GPT1** Timer 3 Interrupt Control Register Τ4 FE44<sub>H</sub> 22<sub>н</sub> **GPT1** Timer 4 Register T4CON FF44<sub>H</sub> **GPT1** Timer 4 Control Register b А2<sub>н</sub> FF64<sub>H</sub> T4IC **GPT1** Timer 4 Interrupt Control Register b B2<sub>H</sub> **T5** FE46<sub>H</sub> 23<sub>H</sub> GPT2 Timer 5 Register T5CON FF46<sub>H</sub> A3<sub>H</sub> **GPT2** Timer 5 Control Register b T5IC b FF66<sub>µ</sub> B3<sub>H</sub> GPT2 Timer 5 Interrupt Control Register **T6** FE48<sub>H</sub> 24<sub>H</sub> **GPT2** Timer 6 Register A4<sub>H</sub> **T6CON** FF48<sub>H</sub> **GPT2** Timer 6 Control Register b $B4_{H}$ T6IC **b** | FF68<sub>H</sub> **GPT2** Timer 6 Interrupt Control Register **E** | 28<sub>H</sub> T7 F050<sub>н</sub> CAPCOM Timer 7 Register **T78CON** b FF20<sub>H</sub> 90<sub>H</sub> CAPCOM Timer 7 and 8 Ctrl. Reg. T7IC **b** | F17А<sub>н</sub> E BE<sub>H</sub> CAPCOM Timer 7 Interrupt Ctrl. Reg. F054<sub>H</sub> T7REL CAPCOM Timer 7 Reload Register E 2A<sub>н</sub> F052<sub>H</sub> **T8** Ε **CAPCOM Timer 8 Register** 29<sub>н</sub> F17C<sub>H</sub> T8IC CAPCOM Timer 8 Interrupt Ctrl. Reg. b Ε BF<sub>H</sub> F056<sub>H</sub> $2B_{H}$ T8REL Ε CAPCOM Timer 8 Reload Register FFAC<sub>H</sub> TFR Trap Flag Register b D6<sub>н</sub> WDT FEAE<sub>H</sub> Watchdog Timer Register (read only) 57<sub>H</sub> <sup>2)</sup>00XX<sub>H</sub>

FFAE<sub>H</sub>

F186<sub>H</sub>

F18E<sub>H</sub>

F196<sub>н</sub>

**b** | F19E<sub>н</sub>

**b** | FF1C<sub>H</sub>

b

b

b

D7<sub>H</sub>

C3<sub>H</sub>

С7<sub>н</sub>

CB<sub>H</sub>

8E<sub>н</sub>

E | CF<sub>H</sub>

E

E

E

2) The reset value depends on the indicated reset source.

WDTCON

XP0IC

XP1IC

XP2IC

XP3IC

ZEROS

Watchdog Timer Control Register

CAN1 Module Interrupt Control Register

Unassigned Interrupt Control Register

Unassigned Interrupt Control Register

Constant Value 0's Register (read only)

PLL/OWD Interrupt Control Register

upper half of PORT0 (P0H), i.e. bitfield CLKCFG represents the logic levels on pins P0.15-13 (P0H.7-5).

Table 15 associates the combinations of these three bits with the respective clock generation mode.

| CLKCFG<br>(P0H.7-5) | CPU Frequency $f_{CPU} = f_{OSC} \times F$ | External Clock<br>Input Range <sup>1)</sup> | Notes                      |

|---------------------|--------------------------------------------|---------------------------------------------|----------------------------|

| 111                 | $f_{\rm OSC} \times 4$                     | 2.5 to 8.25 MHz                             | Default configuration      |

| 110                 | $f_{\rm OSC} \times 3$                     | 3.33 to 11 MHz                              | -                          |

| 101                 | $f_{\rm OSC} \times 2$                     | 5 to 16.5 MHz                               | -                          |

| 100                 | $f_{\rm OSC} 	imes 5$                      | 2 to 6.6 MHz                                | -                          |

| 011                 | $f_{\rm OSC} 	imes 1$                      | 1 to 33 MHz                                 | Direct drive <sup>2)</sup> |

| 010                 | $f_{\rm OSC} 	imes$ 1.5                    | 6.66 to 22 MHz                              | -                          |

| 001                 | <i>f</i> <sub>OSC</sub> / 2                | 2 to 66 MHz                                 | CPU clock via prescaler    |

| 000                 | $f_{\rm OSC} \times 2.5$                   | 4 to 13.2 MHz                               | -                          |

Table 15

C167CR Clock Generation Modes

1) The external clock input range refers to a CPU clock range of 10 ... 33 MHz (PLL operation).

2) The maximum frequency depends on the duty cycle of the external clock signal.

#### Prescaler Operation

When prescaler operation is configured (CLKCFG =  $001_B$ ) the CPU clock is derived from the internal oscillator (input clock signal) by a 2:1 prescaler.

The frequency of  $f_{\text{CPU}}$  is half the frequency of  $f_{\text{OSC}}$  and the high and low time of  $f_{\text{CPU}}$  (i.e. the duration of an individual TCL) is defined by the period of the input clock  $f_{\text{OSC}}$ .

The timings listed in the AC Characteristics that refer to TCLs therefore can be calculated using the period of  $f_{\rm OSC}$  for any TCL.

#### Phase Locked Loop

When PLL operation is configured (via CLKCFG) the on-chip phase locked loop is enabled and provides the CPU clock (see table above). The PLL multiplies the input frequency by the factor **F** which is selected via the combination of pins P0.15-13 (i.e.  $f_{CPU} = f_{OSC} \times \mathbf{F}$ ). With every **F**'th transition of  $f_{OSC}$  the PLL circuit synchronizes the CPU clock to the input clock. This synchronization is done smoothly, i.e. the CPU clock frequency does not change abruptly.

Due to this adaptation to the input clock the frequency of  $f_{\rm CPU}$  is constantly adjusted so it is locked to  $f_{\rm OSC}$ . The slight variation causes a jitter of  $f_{\rm CPU}$  which also effects the duration of individual TCLs.

The timings listed in the AC Characteristics that refer to TCLs therefore must be calculated using the minimum TCL that is possible under the respective circumstances.

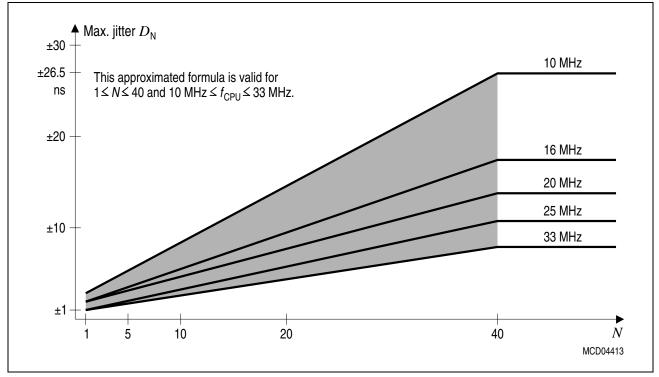

The actual minimum value for TCL depends on the jitter of the PLL. As the PLL is constantly adjusting its output frequency so it corresponds to the applied input frequency (crystal or oscillator) the relative deviation for periods of more than one TCL is lower than for one single TCL (see formula and Figure 11).

For a period of  $\bm{N}\times TCL$  the minimum value is computed using the corresponding deviation  $D_{N}$ :

$$(\mathbf{N} \times \text{TCL})_{\text{min}} = \mathbf{N} \times \text{TCL}_{\text{NOM}} - \mathbf{D}_{\text{N}}, \mathbf{D}_{\text{N}} \text{ [ns]} = \pm (13.3 + \mathbf{N} \times 6.3) / f_{\text{CPU}} \text{ [MHz]}, \tag{1}$$

where **N** = number of consecutive TCLs and  $1 \le N \le 40$ .

So for a period of 3 TCLs @ 25 MHz (i.e.  $\mathbf{N} = 3$ ): D<sub>3</sub> = (13.3 +  $\mathbf{3} \times 6.3$ ) / 25 = 1.288 ns, and (3TCL)<sub>min</sub> = 3TCL<sub>NOM</sub> - 1.288 ns = 58.7 ns (@  $f_{CPU}$  = 25 MHz).

This is especially important for bus cycles using waitstates and e.g. for the operation of timers, serial interfaces, etc. For all slower operations and longer periods (e.g. pulse train generation or measurement, lower baudrates, etc.) the deviation caused by the PLL jitter is negligible.

Note: For all periods longer than 40 TCL the N = 40 value can be used (see Figure 11).

Figure 11 Approximated Maximum Accumulated PLL Jitter

(2)

#### **Electrical Parameters**

#### **Direct Drive**

When direct drive is configured (CLKCFG =  $011_B$ ) the on-chip phase locked loop is disabled and the CPU clock is directly driven from the internal oscillator with the input clock signal.

The frequency of  $f_{\rm CPU}$  directly follows the frequency of  $f_{\rm OSC}$  so the high and low time of  $f_{\rm CPU}$  (i.e. the duration of an individual TCL) is defined by the duty cycle of the input clock  $f_{\rm OSC}$ .

The timings listed below that refer to TCLs therefore must be calculated using the minimum TCL that is possible under the respective circumstances. This minimum value can be calculated via the following formula:

$TCL_{min} = 1/f_{OSC} \times DC_{min}$  (DC = duty cycle)

For two consecutive TCLs the deviation caused by the duty cycle of  $f_{OSC}$  is compensated so the duration of 2TCL is always  $1/f_{OSC}$ . The minimum value TCL<sub>min</sub> therefore has to be used only once for timings that require an odd number of TCLs (1, 3, ...). Timings that require an even number of TCLs (2, 4, ...) may use the formula 2TCL =  $1/f_{OSC}$ .

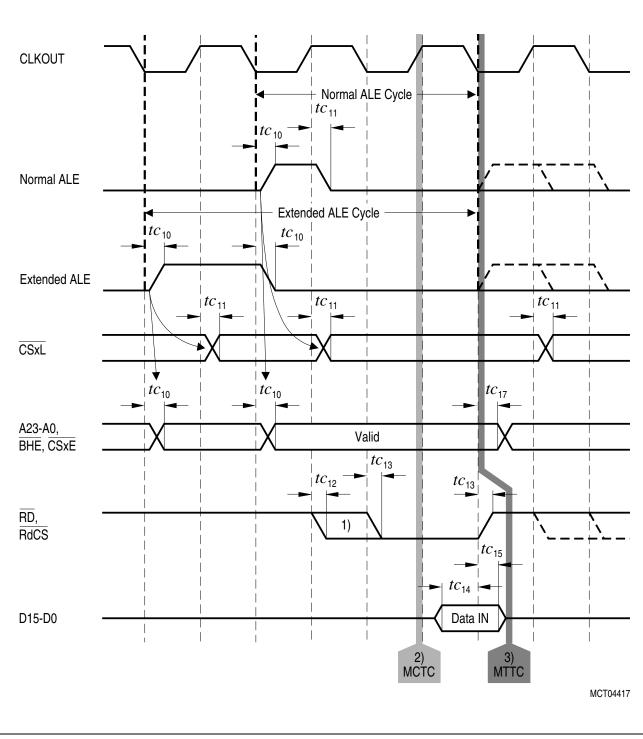

Figure 17 Demultiplexed Bus, Read Access

#### Bus Cycle Control via READY Input

The duration of an external bus cycle can be controlled by the external circuitry via the READY input signal.

**Synchronous** READY permits the shortest possible bus cycle but requires the input signal to be synchronous to the reference signal CLKOUT.

**Asynchronous** READY puts no timing constraints on the input signal but incurs one waitstate minimum due to the additional synchronization stage.

| Table 20 | READT LIMING | (Operating Conditions apply) |