#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                    |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | C166                                                                        |

| Core Size                  | 16-Bit                                                                      |

| Speed                      | 25MHz                                                                       |

| Connectivity               | CANbus, EBI/EMI, SPI, UART/USART                                            |

| Peripherals                | POR, PWM, WDT                                                               |

| Number of I/O              | 111                                                                         |

| Program Memory Size        | -                                                                           |

| Program Memory Type        | ROMIess                                                                     |

| EEPROM Size                | -                                                                           |

| RAM Size                   | 4K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 4.5V ~ 5.5V                                                                 |

| Data Converters            | A/D 16x10b                                                                  |

| Oscillator Type            | External                                                                    |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 144-BQFP                                                                    |

| Supplier Device Package    | P-MQFP-144-8                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/c167srlmhabxuma2 |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2 General Device Information

### 2.1 Introduction

The C167CR derivatives are high performance derivatives of the Infineon C166 Family of full featured single-chip CMOS microcontrollers. They combine high CPU performance (up to 16.5 million instructions per second) with high peripheral functionality and enhanced IO-capabilities. They also provide clock generation via PLL and various on-chip memory modules such as program ROM, internal RAM, and extension RAM.

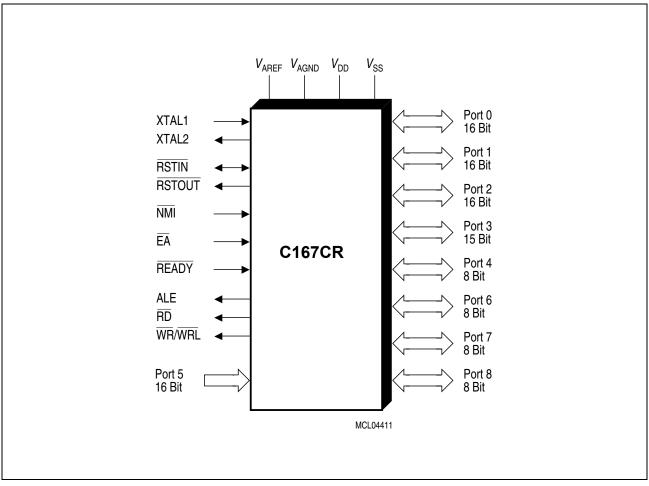

Figure 1 Logic Symbol

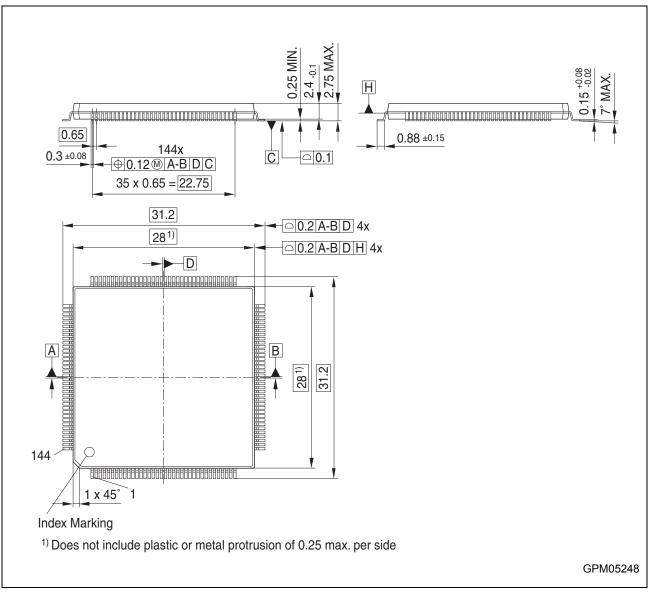

### 2.2 Pin Configuration and Definition for P-MQFP-144-8

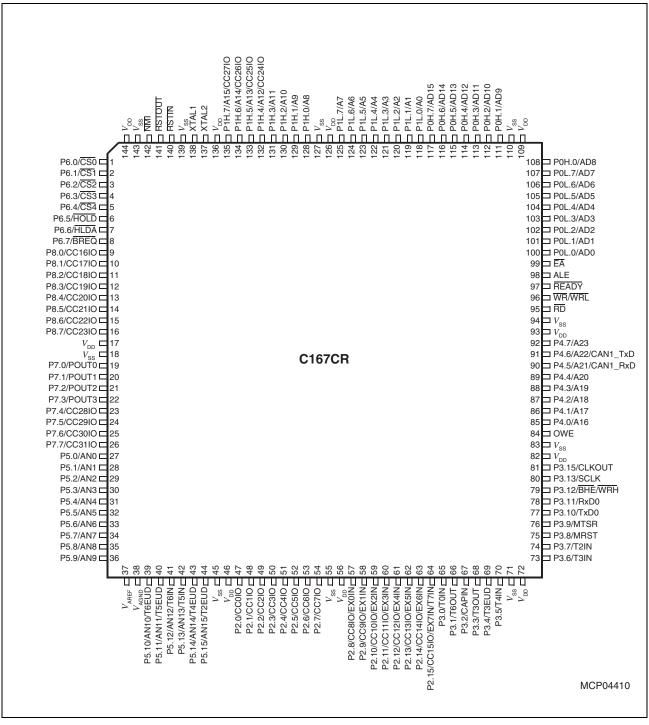

The pins of the C167CR are described in detail in **Table 2**, including all their alternate functions. **Figure 2** summarizes all pins in a condensed way, showing their location on the 4 sides of the package.

Note: The P-BGA-176-2 is described in Table 3 and Figure 3.

#### Figure 2 Pin Configuration P-MQFP-144-8 (top view)

| Table 2      | Pin      | Definit    | tions and Functions P-MQFP-144-8                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|--------------|----------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Symbol       | Pin      | Input      | Function                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|              | No.      | Outp.      |                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| P6           |          | IO         | Port 6 is an 8-bit bidirectional I/O port. It is bit-wise<br>programmable for input or output via direction bits. For a pin<br>configured as input, the output driver is put into high-<br>impedance state. Port 6 outputs can be configured as<br>push/pull or open drain drivers. The input threshold of Port 6<br>is selectable (TTL or special).<br>The Port 6 pins also serve for alternate functions:           |  |  |  |  |  |

| P6.0         | 1        | 0          | CS0 Chip Select 0 Output                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| P6.1         | 2        | 0          | CS1 Chip Select 1 Output                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| P6.2         | 3        | 0          | CS2 Chip Select 2 Output                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| P6.3         | 4        | 0          | CS3 Chip Select 3 Output                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| P6.4         | 5        | 0          | CS4 Chip Select 4 Output                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| P6.5         | 6        | I          | HOLD External Master Hold Request Input                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| P6.6         | 7        | I/O        | HLDA Hold Acknowledge Output (master mode) or                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|              |          |            | Input (slave mode)                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| P6.7         | 8        | 0          | BREQ Bus Request Output                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| P8           |          | IO         | Port 8 is an 8-bit bidirectional I/O port. It is bit-wise<br>programmable for input or output via direction bits. For a pin<br>configured as input, the output driver is put into high-<br>impedance state. Port 8 outputs can be configured as<br>push/pull or open drain drivers. The input threshold of Port 8<br>is selectable (TTL or special).<br>The following Port 8 pins also serve for alternate functions: |  |  |  |  |  |

| P8.0         | 9        | I/O        | CC16IO CAPCOM2: CC16 Capture Inp./Compare Outp.                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| P8.1         | 10       | 1/O        | CC17IO CAPCOM2: CC17 Capture Inp./Compare Outp.                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| P8.2         | 11       | 1/O        | CC18IO CAPCOM2: CC18 Capture Inp./Compare Outp.                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| P8.3         | 12       | 1/0        | CC19IO CAPCOM2: CC19 Capture Inp./Compare Outp.                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| P8.4         | 13       | 1/0        | CC20IO CAPCOM2: CC20 Capture Inp./Compare Outp.                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| P8.5         | 14       | 1/0        | CC21IO CAPCOM2: CC21 Capture Inp./Compare Outp.                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| P8.6<br>P8.7 | 15<br>16 | I/O<br>I/O | CC22IOCAPCOM2: CC22 Capture Inp./Compare Outp.CC23IOCAPCOM2: CC23 Capture Inp./Compare Outp.                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

## Table 3Pin Definitions and Functions P-BGA-176-2 (cont'd)

| D13 |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-----|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C13 | O<br>I | <ul> <li>XTAL2: Output of the oscillator amplifier circuit.</li> <li>XTAL1: Input to the oscillator amplifier and input to the internal clock generator.</li> <li>To clock the device from an external source, drive XTAL1, while leaving XTAL2 unconnected. Minimum and maximum high/low and rise/fall times specified in the AC Characteristics must be observed.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                             |

| D12 | 0      | Internal Reset Indication Output. This pin is set to a low level<br>when the part is executing either a hardware-, a software- or<br>a watchdog timer reset. RSTOUT remains low until the EINIT<br>(end of initialization) instruction is executed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Ξ11 | I/O    | Reset Input with Schmitt-Trigger characteristics. A low level<br>at this pin while the oscillator is running resets the C167CR.<br>An internal pull-up resistor permits power-on reset using only<br>a capacitor connected to $V_{SS}$ .<br>A spike filter suppresses input pulses < 10 ns. Input pulses<br>> 100 ns safely pass the filter. The minimum duration for a<br>safe recognition should be 100 ns + 2 CPU clock cycles.<br>In bidirectional reset mode (enabled by setting bit BDRSTEN<br>in register SYSCON) the RSTIN line is internally pulled low<br>for the duration of the internal reset sequence upon any reset<br>(HW, SW, WDT). See note below this table.<br><i>Note: To let the reset configuration of PORT0 settle and to let<br/>the PLL lock a reset duration of ca. 1 ms is</i> |

|     |        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

### Table 3Pin Definitions and Functions P-BGA-176-2 (cont'd)

| Symbol     | Pin  | Input | Function                                                                                                                                                                                                                                                                                                |

|------------|------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|            | Num. | Outp. |                                                                                                                                                                                                                                                                                                         |

| ĒĀ         | M9   | I     | External Access Enable pin. A low level at this pin during and<br>after Reset forces the C167CR to begin instruction execution<br>out of external memory. A high level forces execution out of<br>the internal program memory.<br>"ROMless" versions must have this pin tied to '0'.                    |

| WR/<br>WRL | N9   | 0     | External Memory Write Strobe. In WR-mode this pin is<br>activated for every external data write access. In WRL-mode<br>this pin is activated for low byte data write accesses on a<br>16-bit bus, and for every data write access on an 8-bit bus.<br>See WRCFG in register SYSCON for mode selection.  |

| READY      | P9   | 1     | Ready Input. When the Ready function is enabled, a high<br>level at this pin during an external memory access will force<br>the insertion of memory cycle time waitstates until the pin<br>returns to a low level.<br>An internal pull-up device will hold this pin high when nothing<br>is driving it. |

| ALE        | P10  | 0     | Address Latch Enable Output. Can be used for latching the address into external memory or an address latch in the multiplexed bus modes.                                                                                                                                                                |

| P4         |      | IO    | Port 4 is an 8-bit bidirectional I/O port. It is bit-wise<br>programmable for input or output via direction bits. For a pin<br>configured as input, the output driver is put into high-<br>impedance state.<br>Port 4 can be used to output the segment address lines and<br>for serial bus interfaces: |

| P4.0       | P6   | 0     | A16 Least Significant Segment Address Line                                                                                                                                                                                                                                                              |

| P4.1       | M6   | 0     | A17 Segment Address Line                                                                                                                                                                                                                                                                                |

| P4.2       | L6   | 0     | A18 Segment Address Line                                                                                                                                                                                                                                                                                |

| P4.3       | N7   | 0     | A19 Segment Address Line                                                                                                                                                                                                                                                                                |

| P4.4       | P7   | 0     | A20 Segment Address Line                                                                                                                                                                                                                                                                                |

| P4.5       | M7   | 0     | A21 Segment Address Line,                                                                                                                                                                                                                                                                               |

|            |      | I     | CAN1_RxD CAN 1 Receive Data Input                                                                                                                                                                                                                                                                       |

| P4.6       | L7   | 0     | A22 Segment Address Line,                                                                                                                                                                                                                                                                               |

|            |      | 0     | CAN1_TxD CAN 1 Transmit Data Output                                                                                                                                                                                                                                                                     |

| P4.7       | N8   | 0     | A23 Most Significant Segment Address Line                                                                                                                                                                                                                                                               |

| Table 3    | Pir         | Pin Definitions and Functions P-BGA-176-2 (cont'd) |                                                 |                                                                            |  |  |  |  |  |

|------------|-------------|----------------------------------------------------|-------------------------------------------------|----------------------------------------------------------------------------|--|--|--|--|--|

| Symbol     | Pin<br>Num. | Input<br>Outp.                                     | Function                                        |                                                                            |  |  |  |  |  |

| P2         |             | IO                                                 | Port 2 is a                                     | 16-bit bidirectional I/O port. It is bit-wise                              |  |  |  |  |  |

|            |             |                                                    | programm                                        | able for input or output via direction bits. For a pin                     |  |  |  |  |  |

|            |             |                                                    | -                                               | as input, the output driver is put into high-                              |  |  |  |  |  |

|            |             |                                                    | -                                               | e state. Port 2 outputs can be configured as                               |  |  |  |  |  |

|            |             |                                                    |                                                 | or open drain drivers. The input threshold of Port 2 ble (TTL or special). |  |  |  |  |  |

|            |             |                                                    | The follow                                      | ring Port 2 pins also serve for alternate functions:                       |  |  |  |  |  |

| P2.0       | F3          | I/O                                                | CC0IO                                           | CAPCOM1: CC0 Capture Inp./Compare Output                                   |  |  |  |  |  |

| P2.1       | F2          | I/O                                                | CC1IO                                           | CAPCOM1: CC1 Capture Inp./Compare Output                                   |  |  |  |  |  |

| P2.2       | F4          | I/O                                                | CC2IO                                           | CAPCOM1: CC2 Capture Inp./Compare Output                                   |  |  |  |  |  |

| P2.3       | G4          | I/O                                                | CC3IO                                           | CAPCOM1: CC3 Capture Inp./Compare Output                                   |  |  |  |  |  |

| P2.4       | G3          | I/O                                                | CC4IO                                           | CAPCOM1: CC4 Capture Inp./Compare Output                                   |  |  |  |  |  |

| P2.5       | G2          | I/O                                                | CC5IO                                           | CAPCOM1: CC5 Capture Inp./Compare Output                                   |  |  |  |  |  |

| P2.6       | G1          | I/O                                                | CC6IO                                           | CAPCOM1: CC6 Capture Inp./Compare Output                                   |  |  |  |  |  |

| P2.7       | H1          | I/O                                                | CC7IO                                           | CAPCOM1: CC7 Capture Inp./Compare Output                                   |  |  |  |  |  |

| P2.8       | H4          | I/O                                                | CC8IO CAPCOM1: CC8 Capture Inp./Compare Output, |                                                                            |  |  |  |  |  |

|            |             | I                                                  | EX0IN                                           | Fast External Interrupt 0 Input                                            |  |  |  |  |  |

| P2.9       | J1          | I/O                                                | CC9IO                                           | CAPCOM1: CC9 Capture Inp./Compare Output,                                  |  |  |  |  |  |

|            |             | I                                                  | EX1IN                                           | Fast External Interrupt 1 Input                                            |  |  |  |  |  |

| P2.10      | J2          | I/O                                                | CC10IO                                          | CAPCOM1: CC10 Capture Inp./Compare Outp.,                                  |  |  |  |  |  |

|            |             | I                                                  | EX2IN                                           | Fast External Interrupt 2 Input                                            |  |  |  |  |  |

| P2.11      | J4          | I/O                                                | CC11IO                                          | CAPCOM1: CC11 Capture Inp./Compare Outp.,                                  |  |  |  |  |  |

|            |             | 1                                                  | EX3IN                                           | Fast External Interrupt 3 Input                                            |  |  |  |  |  |

| P2.12      | J3          | I/O                                                | CC12IO                                          | CAPCOM1: CC12 Capture Inp./Compare Outp.,                                  |  |  |  |  |  |

|            |             | 1                                                  | EX4IN                                           | Fast External Interrupt 4 Input                                            |  |  |  |  |  |

| P2.13      | K1          | I/O                                                | CC13IO                                          | CAPCOM1: CC13 Capture Inp./Compare Outp.,                                  |  |  |  |  |  |

|            |             | 1                                                  | EX5IN                                           | Fast External Interrupt 5 Input                                            |  |  |  |  |  |

| P2.14      | K2          | I/O                                                | CC14IO                                          | CAPCOM1: CC14 Capture Inp./Compare Outp.,                                  |  |  |  |  |  |

|            |             | 1                                                  | EX6IN                                           | Fast External Interrupt 6 Input                                            |  |  |  |  |  |

| P2.15      | L1          | I/O                                                | CC15IO                                          | CAPCOM1: CC15 Capture Inp./Compare Outp.,                                  |  |  |  |  |  |

|            |             | 1                                                  | EX7IN                                           | Fast External Interrupt 7 Input,                                           |  |  |  |  |  |

|            |             | I                                                  | T7IN                                            | CAPCOM2: Timer T7 Count Input                                              |  |  |  |  |  |

| $V_{AREF}$ | B2          | -                                                  | Reference                                       | e voltage for the A/D converter.                                           |  |  |  |  |  |

| $V_{AGND}$ | C2          | -                                                  | Reference                                       | e ground for the A/D converter.                                            |  |  |  |  |  |

### 3.2 External Bus Controller

All of the external memory accesses are performed by a particular on-chip External Bus Controller (EBC). It can be programmed either to Single Chip Mode when no external memory is required, or to one of four different external memory access modes, which are as follows:

- 16-/18-/20-/24-bit Addresses, 16-bit Data, Demultiplexed

- 16-/18-/20-/24-bit Addresses, 16-bit Data, Multiplexed

- 16-/18-/20-/24-bit Addresses, 8-bit Data, Multiplexed

- 16-/18-/20-/24-bit Addresses, 8-bit Data, Demultiplexed

In the demultiplexed bus modes, addresses are output on PORT1 and data is input/output on PORT0 or P0L, respectively. In the multiplexed bus modes both addresses and data use PORT0 for input/output.

Important timing characteristics of the external bus interface (Memory Cycle Time, Memory Tri-State Time, Length of ALE and Read Write Delay) have been made programmable to allow the user the adaption of a wide range of different types of memories and external peripherals.

In addition, up to 4 independent address windows may be defined (via register pairs ADDRSELx / BUSCONx) which control the access to different resources with different bus characteristics. These address windows are arranged hierarchically where BUSCON4 overrides BUSCON3 and BUSCON2 overrides BUSCON1. All accesses to locations not covered by these 4 address windows are controlled by BUSCON0.

Up to 5 external  $\overline{\text{CS}}$  signals (4 windows plus default) can be generated in order to save external glue logic. The C167CR offers the possibility to switch the  $\overline{\text{CS}}$  outputs to an unlatched mode. In this mode the internal filter logic is switched off and the  $\overline{\text{CS}}$  signals are directly generated from the address. The unlatched  $\overline{\text{CS}}$  mode is enabled by setting CSCFG (SYSCON.6).

Access to very slow memories or memories with varying access times is supported via a particular 'Ready' function.

A HOLD/HLDA protocol is available for bus arbitration and allows to share external resources with other bus masters. The bus arbitration is enabled by setting bit HLDEN in register PSW. After setting HLDEN once, pins P6.7 ... P6.5 (BREQ, HLDA, HOLD) are automatically controlled by the EBC. In Master Mode (default after reset) the HLDA pin is an output. By setting bit DP6.7 to '1' the Slave Mode is selected where pin HLDA is switched to input. This allows to directly connect the slave controller to another master controller without glue logic.

For applications which require less than 16 Mbytes of external memory space, this address space can be restricted to 1 Mbyte, 256 Kbyte, or to 64 Kbyte. In this case Port 4 outputs four, two, or no address lines at all. It outputs all 8 address lines, if an address space of 16 Mbytes is used.

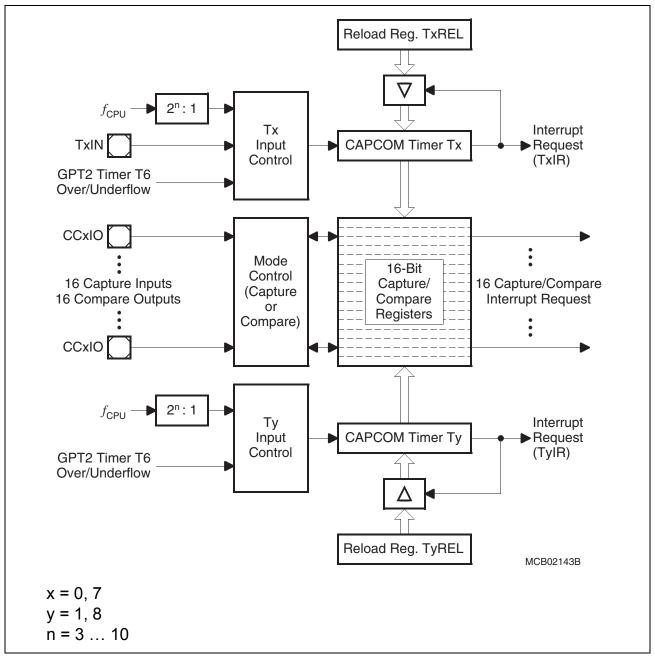

Figure 6 CAPCOM Unit Block Diagram

### 3.6 **PWM Module**

The Pulse Width Modulation Module can generate up to four PWM output signals using edge-aligned or center-aligned PWM. In addition the PWM module can generate PWM burst signals and single shot outputs. The frequency range of the PWM signals covers 4 Hz to 16.5 MHz (referred to a CPU clock of 33 MHz), depending on the resolution of the PWM output signal. The level of the output signals is selectable and the PWM module can generate interrupt requests.

### 3.12 Parallel Ports

The C167CR provides up to 111 I/O lines which are organized into eight input/output ports and one input port. All port lines are bit-addressable, and all input/output lines are individually (bit-wise) programmable as inputs or outputs via direction registers. The I/O ports are true bidirectional ports which are switched to high impedance state when configured as inputs. The output drivers of five I/O ports can be configured (pin by pin) for push/pull operation or open-drain operation via control registers. During the internal reset, all port pins are configured as inputs.

The input threshold of Port 2, Port 3, Port 6, Port 7, and Port 8 is selectable (TTL or CMOS like), where the special CMOS like input threshold reduces noise sensitivity due to the input hysteresis. The input threshold may be selected individually for each byte of the respective ports.

All port lines have programmable alternate input or output functions associated with them. All port lines that are not used for these alternate functions may be used as general purpose IO lines.

PORT0 and PORT1 may be used as address and data lines when accessing external memory, while Port 4 outputs the additional segment address bits A23/19/17 ... A16 in systems where segmentation is enabled to access more than 64 Kbytes of memory.

Port 2, Port 8 and Port 7 (and parts of PORT1) are associated with the capture inputs or compare outputs of the CAPCOM units and/or with the outputs of the PWM module.

Port 6 provides optional bus arbitration signals (BREQ, HLDA, HOLD) and chip select signals.

Port 3 includes alternate functions of timers, serial interfaces, the optional bus control signal BHE/WRH, and the system clock output (CLKOUT).

Port 5 is used for the analog input channels to the A/D converter or timer control signals.

The edge characteristics (transition time) of the C167CR's port drivers can be selected via the Port Driver Control Register (PDCR). Two bits select fast edges ('0') or reduced edges ('1') for bus interface pins and non-bus pins separately.

PDCR.0 = BIPEC controls PORT0, PORT1, Port 4, RD, WR, ALE, CLKOUT, BHE/WRH. PDCR.4 = NBPEC controls Port 3, Port 8, RSTOUT, RSTIN (bidir. reset mode).

| Table 7 Ins            | struction Set Summary (cont'd)                                                                       |       |

|------------------------|------------------------------------------------------------------------------------------------------|-------|

| Mnemonic               | Description                                                                                          | Bytes |

| PRIOR                  | Determine number of shift cycles to normalize direct<br>word GPR and store result in direct word GPR | 2     |

| SHL / SHR              | Shift left/right direct word GPR                                                                     | 2     |

| ROL / ROR              | Rotate left/right direct word GPR                                                                    | 2     |

| ASHR                   | Arithmetic (sign bit) shift right direct word GPR                                                    | 2     |

| MOV(B)                 | Move word (byte) data                                                                                | 2/4   |

| MOVBS                  | Move byte operand to word operand with sign extension                                                | 2/4   |

| MOVBZ                  | Move byte operand to word operand. with zero extension                                               | 2/4   |

| JMPA, JMPI,<br>JMPR    | Jump absolute/indirect/relative if condition is met                                                  | 4     |

| JMPS                   | Jump absolute to a code segment                                                                      | 4     |

| J(N)B                  | Jump relative if direct bit is (not) set                                                             | 4     |

| JBC                    | Jump relative and clear bit if direct bit is set                                                     | 4     |

| JNBS                   | Jump relative and set bit if direct bit is not set                                                   | 4     |

| CALLA, CALLI,<br>CALLR | Call absolute/indirect/relative subroutine if condition is met                                       | 4     |

| CALLS                  | Call absolute subroutine in any code segment                                                         | 4     |

| PCALL                  | Push direct word register onto system stack and call absolute subroutine                             | 4     |

| TRAP                   | Call interrupt service routine via immediate trap number                                             | 2     |

| PUSH, POP              | Push/pop direct word register onto/from system stack                                                 | 2     |

| SCXT                   | Push direct word register onto system stack and update register with word operand                    | 4     |

| RET                    | Return from intra-segment subroutine                                                                 | 2     |

| RETS                   | Return from inter-segment subroutine                                                                 | 2     |

| RETP                   | Return from intra-segment subroutine and pop direct word register from system stack                  | 2     |

| RETI                   | Return from interrupt service subroutine                                                             | 2     |

| SRST                   | Software Reset                                                                                       | 4     |

| IDLE                   | Enter Idle Mode                                                                                      | 4     |

| PWRDN                  | Enter Power Down Mode (supposes NMI-pin being low)                                                   | 4     |

| SRVWDT                 | Service Watchdog Timer                                                                               | 4     |

### 3.15 Special Function Registers Overview

The following table lists all SFRs which are implemented in the C167CR in alphabetical order.

**Bit-addressable** SFRs are marked with the letter "**b**" in column "Name". SFRs within the **Extended SFR-Space** (ESFRs) are marked with the letter "**E**" in column "Physical Address". Registers within on-chip X-peripherals are marked with the letter "**X**" in column "Physical Address".

An SFR can be specified via its individual mnemonic name. Depending on the selected addressing mode, an SFR can be accessed via its physical address (using the Data Page Pointers), or via its short 8-bit address (without using the Data Page Pointers).

Note: Registers within device specific interface modules (CAN) are only present in the corresponding device, of course.

| Name     | _                 | Physica<br>Addres |                 | 8-Bit<br>Addr.                                                | Description                                               | Reset<br>Value    |

|----------|-------------------|-------------------|-----------------|---------------------------------------------------------------|-----------------------------------------------------------|-------------------|

| ADCIC    | FF98 <sub>H</sub> |                   | CC <sub>H</sub> | A/D Converter End of Conversion<br>Interrupt Control Register | 0000 <sub>H</sub>                                         |                   |

| ADCON    | b                 | FFA0 <sub>H</sub> |                 | D0 <sub>H</sub>                                               | A/D Converter Control Register                            | 0000 <sub>H</sub> |

| ADDAT    |                   | FEA0 <sub>H</sub> |                 | 50 <sub>H</sub>                                               | A/D Converter Result Register                             | 0000 <sub>H</sub> |

| ADDAT2   |                   | F0A0 <sub>H</sub> | Ε               | 50 <sub>H</sub>                                               | A/D Converter 2 Result Register                           | 0000 <sub>H</sub> |

| ADDRSEL1 |                   | FE18 <sub>H</sub> |                 | 0C <sub>H</sub>                                               | Address Select Register 1                                 | 0000 <sub>H</sub> |

| ADDRSEL2 |                   | FE1A <sub>H</sub> |                 | 0D <sub>H</sub>                                               | Address Select Register 2                                 | 0000 <sub>H</sub> |

| ADDRSEL3 |                   | FE1C <sub>H</sub> |                 | 0E <sub>H</sub>                                               | Address Select Register 3                                 | 0000 <sub>H</sub> |

| ADDRSEL4 |                   | FE1E <sub>H</sub> |                 | 0F <sub>H</sub>                                               | Address Select Register 4                                 | 0000 <sub>H</sub> |

| ADEIC    | b                 | FF9A <sub>H</sub> |                 | CD <sub>H</sub>                                               | A/D Converter Overrun Error Interrupt<br>Control Register | 0000 <sub>H</sub> |

| BUSCON0  | b                 | FF0C <sub>H</sub> |                 | 86 <sub>H</sub>                                               | Bus Configuration Register 0                              | 0XX0 <sub>H</sub> |

| BUSCON1  | b                 | FF14 <sub>H</sub> |                 | 8A <sub>H</sub>                                               | Bus Configuration Register 1                              | 0000 <sub>H</sub> |

| BUSCON2  | b                 | FF16 <sub>H</sub> |                 | 8B <sub>H</sub>                                               | Bus Configuration Register 2                              | 0000 <sub>H</sub> |

| BUSCON3  | b                 | FF18 <sub>H</sub> |                 | 8C <sub>H</sub>                                               | Bus Configuration Register 3                              | 0000 <sub>H</sub> |

| BUSCON4  | b                 | FF1A <sub>H</sub> |                 | 8D <sub>H</sub>                                               | Bus Configuration Register 4                              | 0000 <sub>H</sub> |

| C1BTR    |                   | EF04 <sub>H</sub> | Χ               | _                                                             | CAN1 Bit Timing Register                                  | UUUU <sub>H</sub> |

| C1CSR    |                   | EF00 <sub>H</sub> | Χ               | _                                                             | CAN1 Control / Status Register                            | XX01 <sub>H</sub> |

| C1GMS    |                   | EF06 <sub>H</sub> | Χ               | _                                                             | CAN1 Global Mask Short                                    | UFUU <sub>H</sub> |

Table 8

C167CR Registers, Ordered by Name

### Table 8C167CR Registers, Ordered by Name (cont'd)

| Name   |                   | Physical<br>Address                                                       |   | 8-Bit<br>Addr.              | Description                            | Reset<br>Value    |  |

|--------|-------------------|---------------------------------------------------------------------------|---|-----------------------------|----------------------------------------|-------------------|--|

| C1IR   | EF02 <sub>H</sub> | Χ                                                                         | _ | CAN1 Interrupt Register     | XX <sub>H</sub>                        |                   |  |

| C1LGML |                   | EF0A <sub>H</sub>                                                         | Χ | _                           | CAN1 Lower Global Mask Long            | UUUU <sub>H</sub> |  |

| C1LMLM |                   | EF0E <sub>H</sub>                                                         | Χ | _                           | CAN1 Lower Mask of Last Message        | UUUU <sub>H</sub> |  |

| C1UAR  |                   | EFn2 <sub>H</sub> X – CAN1 Upper Arbitration Register (message <b>n</b> ) |   |                             |                                        | UUUU <sub>H</sub> |  |

| C1UGML |                   | EF08 <sub>H</sub>                                                         | Χ | CAN1 Upper Global Mask Long |                                        |                   |  |

| C1UMLM |                   | EF0C <sub>H</sub>                                                         | Χ | -                           | CAN1 Upper Mask of Last Message        | UUUU <sub>H</sub> |  |

| CAPREL |                   | FE4A <sub>H</sub>                                                         |   | 25 <sub>H</sub>             | GPT2 Capture/Reload Register           | 0000 <sub>H</sub> |  |

| CC0    |                   | FE80 <sub>H</sub>                                                         |   | 40 <sub>H</sub>             | CAPCOM Register 0                      | 0000 <sub>H</sub> |  |

| CC0IC  | b                 | FF78 <sub>H</sub>                                                         |   | BC <sub>H</sub>             | CAPCOM Register 0 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |  |

| CC1    |                   | FE82 <sub>H</sub>                                                         |   | 41 <sub>H</sub>             | CAPCOM Register 1                      | 0000 <sub>H</sub> |  |

| CC10   |                   | FE94 <sub>H</sub>                                                         |   | 4A <sub>H</sub>             | CAPCOM Register 10                     | 0000 <sub>H</sub> |  |

| CC10IC | b                 | FF8C <sub>H</sub>                                                         |   | C6 <sub>H</sub>             | CAPCOM Reg. 10 Interrupt Ctrl. Reg.    | 0000 <sub>H</sub> |  |

| CC11   |                   | FE96 <sub>H</sub>                                                         |   | 4B <sub>H</sub>             | CAPCOM Register 11                     | 0000 <sub>H</sub> |  |

| CC11IC | b                 | FF8E <sub>H</sub>                                                         |   | C7 <sub>H</sub>             | CAPCOM Reg. 11 Interrupt Ctrl. Reg.    | 0000 <sub>H</sub> |  |

| CC12   |                   | FE98 <sub>H</sub>                                                         |   | 4C <sub>H</sub>             | CAPCOM Register 12                     | 0000 <sub>H</sub> |  |

| CC12IC | b                 | FF90 <sub>H</sub>                                                         |   | C8 <sub>H</sub>             | CAPCOM Reg. 12 Interrupt Ctrl. Reg.    | 0000 <sub>H</sub> |  |

| CC13   |                   | FE9A <sub>H</sub>                                                         |   | 4D <sub>H</sub>             | CAPCOM Register 13                     | 0000 <sub>H</sub> |  |

| CC13IC | b                 | FF92 <sub>H</sub>                                                         |   | C9 <sub>H</sub>             | CAPCOM Reg. 13 Interrupt Ctrl. Reg.    | 0000 <sub>H</sub> |  |

| CC14   |                   | FE9C <sub>H</sub>                                                         |   | 4E <sub>H</sub>             | CAPCOM Register 14                     | 0000 <sub>H</sub> |  |

| CC14IC | b                 | FF94 <sub>H</sub>                                                         |   | CA <sub>H</sub>             | CAPCOM Reg. 14 Interrupt Ctrl. Reg.    | 0000 <sub>H</sub> |  |

| CC15   |                   | FE9E <sub>H</sub>                                                         |   | 4F <sub>H</sub>             | CAPCOM Register 15                     | 0000 <sub>H</sub> |  |

| CC15IC | b                 | FF96 <sub>H</sub>                                                         |   | CB <sub>H</sub>             | CAPCOM Reg. 15 Interrupt Ctrl. Reg.    | 0000 <sub>H</sub> |  |

| CC16   |                   | FE60 <sub>H</sub>                                                         |   | 30 <sub>H</sub>             | CAPCOM Register 16                     | 0000 <sub>H</sub> |  |

| CC16IC | b                 | F160 <sub>H</sub>                                                         | Ε | B0 <sub>Н</sub>             | CAPCOM Reg. 16 Interrupt Ctrl. Reg.    | 0000 <sub>H</sub> |  |

| CC17   |                   | FE62 <sub>H</sub>                                                         |   | 31 <sub>H</sub>             | CAPCOM Register 17                     | 0000 <sub>H</sub> |  |

| CC17IC | b                 | F162 <sub>H</sub>                                                         | Ε | B1 <sub>H</sub>             | CAPCOM Reg. 17 Interrupt Ctrl. Reg.    | 0000 <sub>H</sub> |  |

| CC18   |                   | FE64 <sub>H</sub>                                                         |   | 32 <sub>H</sub>             | CAPCOM Register 18                     | 0000 <sub>H</sub> |  |

| CC18IC | b                 | F164 <sub>H</sub>                                                         | Ε | B2 <sub>H</sub>             | CAPCOM Reg. 18 Interrupt Ctrl. Reg.    | 0000 <sub>H</sub> |  |

| CC19   |                   |                                                                           |   | 33 <sub>H</sub>             | CAPCOM Register 19                     | 0000 <sub>H</sub> |  |

### Table 8C167CR Registers, Ordered by Name (cont'd)

| Table 8 | e 8 C167CR Registers, Ordered by Name (cont'd) |                     |   |                 |                                     |                   |  |  |

|---------|------------------------------------------------|---------------------|---|-----------------|-------------------------------------|-------------------|--|--|

| Name    |                                                | Physical<br>Address |   | 8-Bit<br>Addr.  | Description                         | Reset<br>Value    |  |  |

| CC19IC  | b                                              | F166 <sub>H</sub>   | Ε | B3 <sub>H</sub> | CAPCOM Reg. 19 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |  |  |

| CC1IC   | b                                              | FF7A <sub>H</sub>   |   | BD <sub>H</sub> | CAPCOM Reg. 1 Interrupt Ctrl. Reg.  | 0000 <sub>H</sub> |  |  |

| CC2     |                                                | FE84 <sub>H</sub>   |   | 42 <sub>H</sub> | CAPCOM Register 2                   | 0000 <sub>H</sub> |  |  |

| CC20    |                                                | FE68 <sub>H</sub>   |   | 34 <sub>H</sub> | CAPCOM Register 20                  | 0000 <sub>H</sub> |  |  |

| CC20IC  | b                                              | F168 <sub>H</sub>   | Ε | B4 <sub>H</sub> | CAPCOM Reg. 20 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |  |  |

| CC21    |                                                | FE6A <sub>H</sub>   |   | 35 <sub>H</sub> | CAPCOM Register 21                  | 0000 <sub>H</sub> |  |  |

| CC21IC  | b                                              | F16A <sub>H</sub>   | Ε | B5 <sub>H</sub> | CAPCOM Reg. 21 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |  |  |

| CC22    |                                                | FE6C <sub>H</sub>   |   | 36 <sub>H</sub> | CAPCOM Register 22                  | 0000 <sub>H</sub> |  |  |

| CC22IC  | b                                              | F16C <sub>H</sub>   | Ε | B6 <sub>H</sub> | CAPCOM Reg. 22 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |  |  |

| CC23    |                                                | FE6E <sub>H</sub>   |   | 37 <sub>H</sub> | CAPCOM Register 23                  | 0000 <sub>H</sub> |  |  |

| CC23IC  | b                                              | F16E <sub>H</sub>   | Ε | B7 <sub>H</sub> | CAPCOM Reg. 23 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |  |  |

| CC24    |                                                | FE70 <sub>H</sub>   |   | 38 <sub>H</sub> | CAPCOM Register 24                  | 0000 <sub>H</sub> |  |  |

| CC24IC  | b                                              | F170 <sub>H</sub>   | Ε | B8 <sub>H</sub> | CAPCOM Reg. 24 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |  |  |

| CC25    |                                                | FE72 <sub>H</sub>   |   | 39 <sub>H</sub> | CAPCOM Register 25                  | 0000 <sub>H</sub> |  |  |

| CC25IC  | b                                              | F172 <sub>H</sub>   | Ε | B9 <sub>H</sub> | CAPCOM Reg. 25 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |  |  |

| CC26    |                                                | FE74 <sub>H</sub>   |   | 3A <sub>H</sub> | CAPCOM Register 26                  | 0000 <sub>H</sub> |  |  |

| CC26IC  | b                                              | F174 <sub>H</sub>   | Ε | BA <sub>H</sub> | CAPCOM Reg. 26 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |  |  |

| CC27    |                                                | FE76 <sub>H</sub>   |   | 3B <sub>H</sub> | CAPCOM Register 27                  | 0000 <sub>H</sub> |  |  |

| CC27IC  | b                                              | F176 <sub>H</sub>   | Ε | BB <sub>H</sub> | CAPCOM Reg. 27 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |  |  |

| CC28    |                                                | FE78 <sub>H</sub>   |   | 3C <sub>H</sub> | CAPCOM Register 28                  | 0000 <sub>H</sub> |  |  |

| CC28IC  | b                                              | F178 <sub>H</sub>   | Ε | BC <sub>H</sub> | CAPCOM Reg. 28 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |  |  |

| CC29    |                                                | FE7A <sub>H</sub>   |   | 3D <sub>H</sub> | CAPCOM Register 29                  | 0000 <sub>H</sub> |  |  |

| CC29IC  | b                                              | F184 <sub>H</sub>   | Ε | C2 <sub>H</sub> | CAPCOM Reg. 29 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |  |  |

| CC2IC   | b                                              | FF7C <sub>H</sub>   |   | BE <sub>H</sub> | CAPCOM Reg. 2 Interrupt Ctrl. Reg.  | 0000 <sub>H</sub> |  |  |

| CC3     |                                                | FE86 <sub>H</sub>   |   | 43 <sub>H</sub> | CAPCOM Register 3                   | 0000 <sub>H</sub> |  |  |

| CC30    |                                                | FE7C <sub>H</sub>   |   | 3E <sub>H</sub> | CAPCOM Register 30                  | 0000 <sub>H</sub> |  |  |

| CC30IC  | b                                              | F18C <sub>H</sub>   | Ε | C6 <sub>H</sub> | CAPCOM Reg. 30 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |  |  |

| CC31    |                                                | FE7E <sub>H</sub>   |   | 3F <sub>н</sub> | CAPCOM Register 31                  | 0000 <sub>H</sub> |  |  |

| CC31IC  | b                                              | F194 <sub>H</sub>   | Ε | CA <sub>H</sub> | CAPCOM Reg. 31 Interrupt Ctrl. Reg. | 0000 <sub>H</sub> |  |  |

| CC3IC   | b                                              | FF7E <sub>H</sub>   |   | BF <sub>H</sub> | CAPCOM Reg. 3 Interrupt Ctrl. Reg.  | 0000 <sub>H</sub> |  |  |

### **Operating Conditions**

The following operating conditions must not be exceeded in order to ensure correct operation of the C167CR. All parameters specified in the following sections refer to these operating conditions, unless otherwise noticed.

| Parameter                         | Symbol            | Limit             | Values | Unit | Notes                                                                           |  |

|-----------------------------------|-------------------|-------------------|--------|------|---------------------------------------------------------------------------------|--|

|                                   |                   | Min.              | Max.   |      |                                                                                 |  |

| Digital supply voltage            | V <sub>DD</sub>   | 4.5               | 5.5    | V    | Active mode,<br>$f_{CPUmax}$ = 33 MHz                                           |  |

|                                   |                   | 2.5 <sup>1)</sup> | 5.5    | V    | Power Down mode                                                                 |  |

| Digital ground voltage            | V <sub>SS</sub>   |                   | 0      | V    | Reference voltage                                                               |  |

| Overload current                  | I <sub>OV</sub>   | _                 | ±5     | mA   | Per pin <sup>2)3)</sup>                                                         |  |

| Absolute sum of overload currents | $\Sigma  I_{OV} $ | -                 | 50     | mA   | 3)                                                                              |  |

| External Load Capacitance         | CL                | -                 | 50     | pF   | Pin drivers in<br><b>fast edge</b> mode<br>(PDCR.BIPEC = '0')                   |  |

|                                   |                   | -                 | 30     | pF   | Pin drivers in<br><b>reduced edge</b> mode<br>(PDCR.BIPEC = '1') <sup>3)</sup>  |  |

|                                   |                   | -                 | 100    | рF   | Pin drivers in<br><b>fast edge</b> mode,<br>$f_{CPUmax}$ = 25 MHz <sup>4)</sup> |  |

| Ambient temperature               | T <sub>A</sub>    | 0                 | 70     | °C   | SAB-C167CR                                                                      |  |

|                                   |                   | -40               | 85     | °C   | SAF-C167CR                                                                      |  |

|                                   |                   | -40               | 125    | °C   | SAK-C167CR                                                                      |  |

### Table 10Operating Condition Parameters

1) Output voltages and output currents will be reduced when  $V_{\rm DD}$  leaves the range defined for active mode.

2) Overload conditions occur if the standard operating conditions are exceeded, i.e. the voltage on any pin exceeds the specified range (i.e.  $V_{OV} > V_{DD} + 0.5 \text{ V}$  or  $V_{OV} < V_{SS} - 0.5 \text{ V}$ ). The absolute sum of input overload currents on all pins may not exceed **50 mA**. The supply voltage must remain within the specified limits. Proper operation is not guaranteed if overload conditions occur on functional pins like XTAL1,  $\overline{\text{RD}}$ ,  $\overline{\text{WR}}$ , etc.

3) Not subject to production test - verified by design/characterization.

4) The increased capacitive load is valid for the 25 MHz-derivatives up to a CPU clock frequency of 25 MHz. Under these circumstances the timing parameters as specified in the "C167CR Data Sheet 1999-06" are valid.

| Table 11 | <b>DC Characteristics</b> (Operating Conditions apply) <sup>1)</sup> (cont'd) |

|----------|-------------------------------------------------------------------------------|

|----------|-------------------------------------------------------------------------------|

| Parameter                                                      | Sym                                   | ool | Limit               | Values | Unit | <b>Test Condition</b>                         |

|----------------------------------------------------------------|---------------------------------------|-----|---------------------|--------|------|-----------------------------------------------|

|                                                                |                                       |     | Min.                | Max.   |      |                                               |

| Output high voltage <sup>3)</sup>                              | V <sub>OH</sub>                       | CC  | 2.4                 | _      | V    | I <sub>OH</sub> = -2.4 mA                     |

| (PORT0, PORT1, Port 4, ALE,<br>RD, WR, BHE, CLKOUT,<br>RSTOUT) |                                       |     | 0.9 V <sub>DD</sub> | _      | V    | I <sub>OH</sub> = -0.5 mA                     |

| Output high voltage <sup>3)</sup>                              | V <sub>OH1</sub>                      | CC  | 2.4                 | _      | V    | I <sub>он</sub> = -1.6 mА                     |

| (all other outputs)                                            |                                       |     | 0.9 V <sub>DD</sub> | _      | V    | I <sub>OH</sub> = -0.5 mA                     |

| Input leakage current (Port 5)                                 | I <sub>OZ1</sub>                      | CC  | _                   | ±200   | nA   | $0 \lor < V_{\rm IN} < V_{\rm DD}$            |

| Input leakage current<br>(all other) <sup>4)</sup>             | I <sub>OZ2</sub>                      | СС  | _                   | ±500   | nA   | 0.45 V < V <sub>IN</sub> <<br>V <sub>DD</sub> |

| RSTIN inactive current <sup>5)</sup>                           | I <sub>RSTH</sub>                     | 6)  | _                   | -10    | μA   | $V_{\rm IN} = V_{\rm IH1}$                    |

| RSTIN active current <sup>5)</sup>                             | I <sub>RSTL</sub> <sup>7</sup>        | 7)  | -100                | _      | μA   | $V_{\rm IN} = V_{\rm IL}$                     |

| READY/RD/WR inact. current <sup>8)</sup>                       | I <sub>RWH</sub> <sup>6</sup>         | i)  | _                   | -40    | μA   | $V_{\rm OUT}$ = 2.4 V                         |

| READY/RD/WR active current <sup>8)</sup>                       | $I_{\rm RWL}^{7}$                     |     | -500                | _      | μA   | $V_{\rm OUT}$ = $V_{\rm OLmax}$               |

| ALE inactive current <sup>8)</sup>                             | I <sub>ALEL</sub> <sup>6</sup>        |     | _                   | 40     | μA   | $V_{\rm OUT}$ = $V_{\rm OLmax}$               |

| ALE active current <sup>8)</sup>                               | I <sub>ALEH</sub> 7                   |     | 500                 | _      | μA   | V <sub>OUT</sub> = 2.4 V                      |

| Port 6 inactive current <sup>8)</sup>                          | I <sub>P6H</sub> <sup>6)</sup>        |     | _                   | -40    | μA   | V <sub>OUT</sub> = 2.4 V                      |

| Port 6 active current <sup>8)</sup>                            | <i>I</i> <sub>P6L</sub> <sup>7)</sup> |     | -500                | _      | μA   | $V_{\rm OUT}$ = $V_{\rm OL1max}$              |

| PORT0 configuration current <sup>9)</sup>                      | I <sub>P0H</sub> <sup>6)</sup>        |     | _                   | -10    | μA   | $V_{\rm IN} = V_{\rm IHmin}$                  |

|                                                                | $I_{\rm P0L}^{(7)}$                   |     | -100                | _      | μA   | $V_{\rm IN} = V_{\rm ILmax}$                  |

| XTAL1 input current                                            | $I_{\rm IL}$                          | CC  | _                   | ±20    | μA   | $0 V < V_{IN} < V_{DD}$                       |

| Pin capacitance <sup>10)</sup><br>(digital inputs/outputs)     | $C_{\rm IO}$                          | СС  | _                   | 10     | pF   | f = 1 MHz;<br>T <sub>A</sub> = 25 °C          |

1) Keeping signal levels within the levels specified in this table, ensures operation without overload conditions. For signal levels outside these specifications also refer to the specification of the overload current  $I_{OV}$ .

2) Valid in bidirectional reset mode only.

3) This specification is not valid for outputs which are switched to open drain mode. In this case the respective output will float and the voltage results from the external circuitry.

- 4) This parameter is not valid for pins READY, ALE, RD, and WR while the respective pull device is on.

- 5) These parameters describe the  $\overline{\text{RSTIN}}$  pull-up, which equals a resistance of ca. 50 to 250 k $\Omega$ .

- 6) The maximum current may be drawn while the respective signal line remains inactive.

- 7) The minimum current must be drawn in order to drive the respective signal line active.

- 8) This specification is valid during Reset and during Hold-mode or Adapt-mode. During Hold-mode Port 6 pins are only affected, if they are used (configured) for CS output and the open drain function is not enabled. The READY-pull-up is always active, except for Power-down mode.

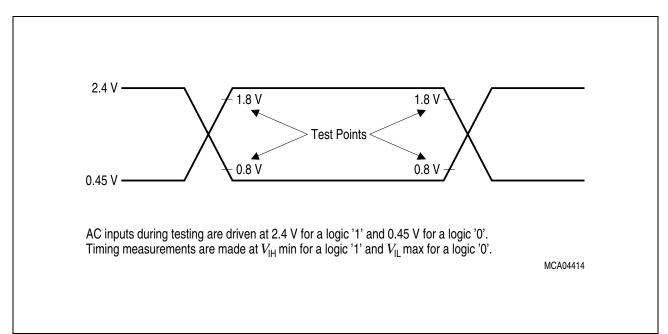

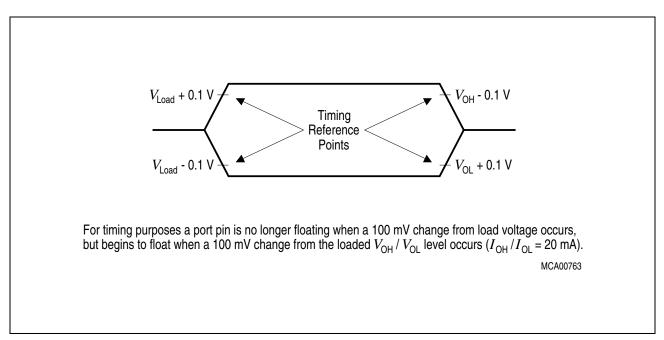

Figure 13 Input Output Waveforms

Figure 14 Float Waveforms

### 4.4.4 External Bus Timing

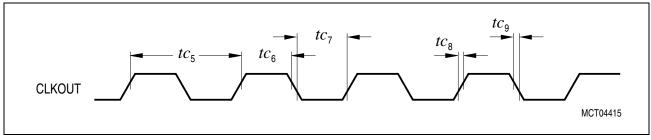

### Table 17CLKOUT Reference Signal

| Parameter         |                 | Symbol |      | Limits           |    |

|-------------------|-----------------|--------|------|------------------|----|

|                   |                 |        | Min. | Max.             |    |

| CLKOUT cycle time | $tc_5$          | CC     | 3    | 30 <sup>1)</sup> | ns |

| CLKOUT high time  | tc <sub>6</sub> | CC     | 8    | _                | ns |

| CLKOUT low time   | tc <sub>7</sub> | CC     | 6    | _                | ns |

| CLKOUT rise time  | tc <sub>8</sub> | CC     | _    | 4                | ns |

| CLKOUT fall time  | tc <sub>9</sub> | CC     | -    | 4                | ns |

1) The CLKOUT cycle time is influenced by the PLL jitter.

For a single CLKOUT cycle (2 TCL) the deviation caused by the PLL jitter is below 1 ns (for  $f_{CPU}$  > 25 MHz). For longer periods the relative deviation decreases (see PLL deviation formula).

Figure 15 CLKOUT Signal Timing

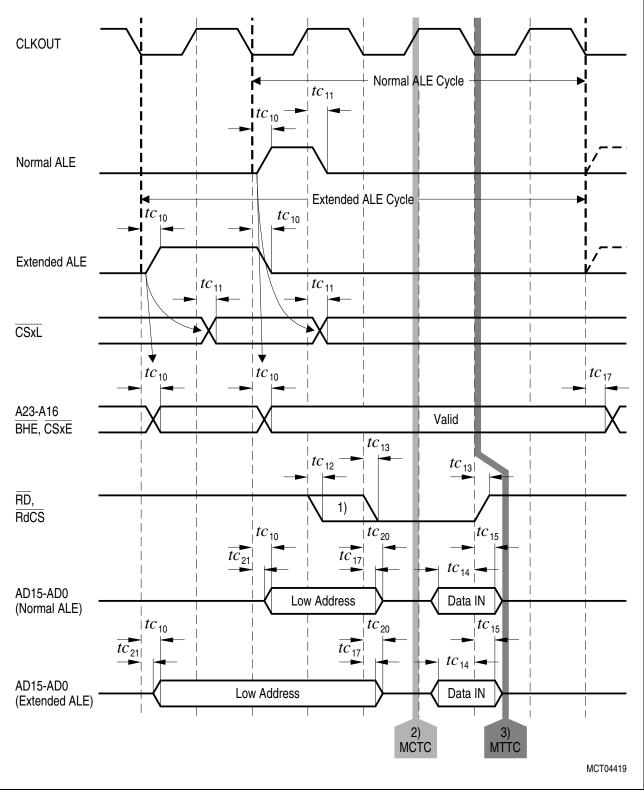

#### Variable Memory Cycles

The bus timing shown below is programmable via the BUSCONx registers. The duration of ALE and two types of waitstates can be selected. This table summarizes the possible bus cycle durations.

| Table 18 | Variable M | Memory | Cycles         |

|----------|------------|--------|----------------|

|          |            |        | <b>Uy</b> CIC3 |

| Bus Cycle Type                            | Bus Cycle Duration                                         | Unit | 25/33 MHz, 0 Waitstates |

|-------------------------------------------|------------------------------------------------------------|------|-------------------------|

| Demultiplexed bus cycle with normal ALE   | 4 + 2 × (15 - <mctc>)<br/>+ 2 × (1 - <mttc>)</mttc></mctc> | TCL  | 80 ns/60.6 ns           |

| Demultiplexed bus cycle with extended ALE | 6 + 2 × (15 - <mctc>)<br/>+ 2 × (1 - <mttc>)</mttc></mctc> | TCL  | 120 ns/90.9 ns          |

| Multiplexed bus cycle with normal ALE     | 6 + 2 × (15 - <mctc>)<br/>+ 2 × (1 - <mttc>)</mttc></mctc> | TCL  | 120 ns/90.9 ns          |

| Multiplexed bus cycle with extended ALE   | 8 + 2 × (15 - <mctc>)<br/>+ 2 × (1 - <mttc>)</mttc></mctc> | TCL  | 160 ns/121.2 ns         |

### General Notes for the Following Timing Figures

These standard notes apply to all subsequent timing figures. Additional individual notes are placed at the respective figure.

- 1. The falling edge of signals  $\overline{RD}$  and  $\overline{WR}/\overline{WRH}/\overline{WRL}/\overline{WrCS}$  is controlled by the Read/Write delay feature (bit BUSCON.RWDCx).

- 2. A bus cycle is extended here, if MCTC waitstates are selected or if the READY input is sampled inactive.

- 3. A bus cycle is extended here, if an MTTC waitstate is selected.

Figure 19 Multiplexed Bus, Read Access

C167CR C167SR

### **Package Outlines**

You can find all of our packages, sorts of packing and others in our Infineon Internet Page "Products": http://www.infineon.com/products. Dimensions in mm