Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 50MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, Microwire, SPI, SSI, SSP, UART/USART                    |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 28                                                                        |

| Program Memory Size        | 24KB (24K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 2K x 8                                                                    |

| RAM Size                   | 6K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.6V ~ 3.6V                                                               |

| Data Converters            | A/D 8x10b; D/A 1x10b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 32-VFQFN Exposed Pad                                                      |

| Supplier Device Package    | 32-HVQFN (5x5)                                                            |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc11a13fhi33-201 |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- ◆ Up to 16 pins are configurable with a digital input glitch filter for removing glitches with widths of 10 ns or less and two pins are configurable for 50 ns glitch filters.

- ♦ GPIO pins can be used as edge and level sensitive interrupt sources.

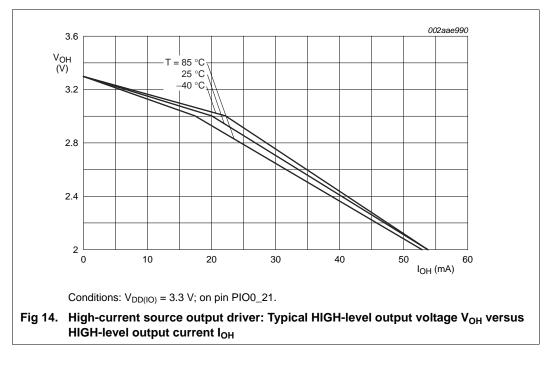

- ♦ High-current source output driver (20 mA) on one pin (PIO0\_21).

- ♦ High-current sink driver (20 mA) on true open-drain pins (PIO0\_2 and PIO0\_3).

- Four general purpose counter/timers with a total of up to 16 capture inputs and 14 match outputs.

- Programmable Windowed WatchDog Timer (WWDT) with a dedicated, internal low-power WatchDog Oscillator (WDOsc).

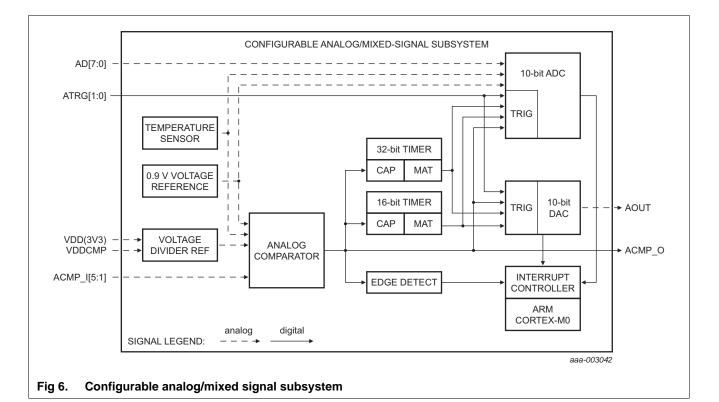

- Analog peripherals:

- ◆ 10-bit ADC with input multiplexing among 8 pins.

- ◆ 10-bit DAC with flexible conversion triggering.

- ◆ Highly flexible analog comparator with a programmable voltage reference.

- Integrated temperature sensor.

- ◆ Internal voltage reference.

- ◆ UnderVoltage Lockout (UVLO) protection against power-supply droop below 2.4 V.

- Serial interfaces:

- USART with fractional baud rate generation, internal FIFO, support for RS-485/9-bit mode and synchronous mode.

- Two SSP controllers with FIFO and multi-protocol capabilities. Support data rates of up to 25 Mbit/s.

- ♦ I<sup>2</sup>C-bus interface supporting the full I<sup>2</sup>C-bus specification and Fast-mode Plus with a data rate of 1 Mbit/s with multiple address recognition and monitor mode.

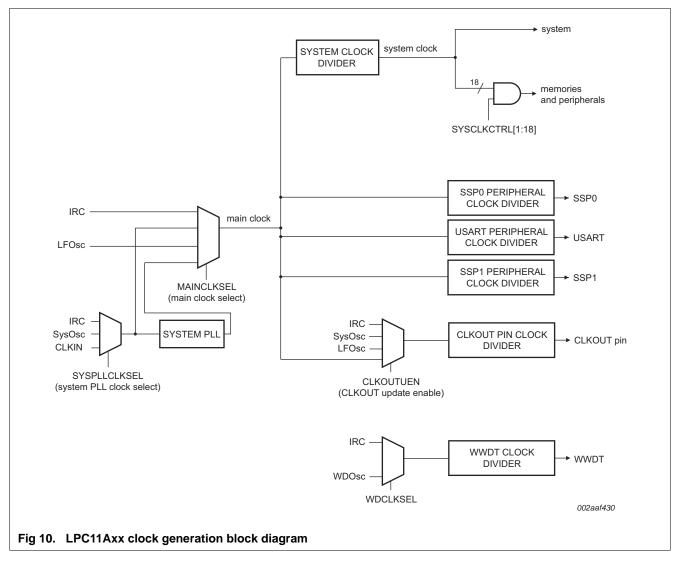

- Clock generation:

- Crystal Oscillator (SysOsc) with an operating range of 1 MHz to 25 MHz.

- 12 MHz internal RC Oscillator (IRC) trimmed to 1% accuracy that can optionally be used as a system clock.

- Internal low-power, Low-Frequency Oscillator (LFOsc) with programmable frequency output.

- Clock input for external system clock (25 MHz typical).

- PLL allows CPU operation up to the maximum CPU rate with the IRC, the external clock, or the SysOsc as clock sources.

- Clock output function with divider that can reflect the SysOsc, the IRC, the main clock, or the LFOsc.

- Power control:

- Supports one reduced power mode: The ARM Sleep mode.

- Power profiles residing in boot ROM allowing to optimize performance and minimize power consumption for any given application through one simple function call.

- Processor wake-up from reduced power mode using any interrupt.

- Power-On Reset (POR).

- Brown-Out Detect (BOD) with two programmable thresholds for interrupt and one hardware controlled reset trip point.

- POR and BOD are always enabled for rapid UVLO protection against power supply voltage droop below 2.4 V.

- Unique device serial number for identification.

# 32-bit ARM Cortex-M0 microcontroller

- Single 3.3 V power supply (2.6 V to 3.6 V).

- Temperature range –40 °C to +85 °C.

- Available as LQFP48 package, HVQFN33 (7 × 7) and HVQFN33 (5 × 5) packages, and in a very small WLCSP20 package.

# 3. Applications

- Power management

- Industrial control

- Remote monitoring

- Point-of-sale

- Test and measurement equipment

- Network appliances and services

- Factory automation

- Gaming equipment

- Motion control

- Medical instrumentation

- Fire and security

- Sensors

- Precision instrumentation

- HVAC and building control

# 4. Ordering information

# Table 1. Ordering information

| Type number       | Package |                                                                                                                         |          |

|-------------------|---------|-------------------------------------------------------------------------------------------------------------------------|----------|

|                   | Name    | Description                                                                                                             | Version  |

| LPC11A02UK        | WLCSP20 | wafer level chip-size package; 20 bumps; $2.5 \times 2.5 \times 0.6$ mm                                                 | -        |

| LPC11A04UK        | WLCSP20 | wafer level chip-size package; 20 bumps; $2.5 \times 2.5 \times 0.6$ mm                                                 | -        |

| LPC11A11FHN33/001 | HVQFN33 | HVQFN: plastic thermal enhanced very thin quad flat package; no leads; 33 terminals; body 7 $\times$ 7 $\times$ 0.85 mm | n/a      |

| LPC11A12FHN33/101 | HVQFN33 | HVQFN: plastic thermal enhanced very thin quad flat package; no leads; 33 terminals; body 7 $\times$ 7 $\times$ 0.85 mm | n/a      |

| LPC11A13FHI33/201 | HVQFN33 | HVQFN: plastic thermal enhanced very thin quad flat package; no leads; 33 terminals; body 5 $\times$ 5 $\times$ 0.85 mm | n/a      |

| LPC11A14FHN33/301 | HVQFN33 | HVQFN: plastic thermal enhanced very thin quad flat package; no leads; 33 terminals; body 7 $\times$ 7 $\times$ 0.85 mm | n/a      |

| LPC11A12FBD48/101 | LQFP48  | LQFP48: plastic low profile quad flat package; 48 leads; body 7 $\times$ 7 $\times$ 1.4 mm                              | SOT313-2 |

| LPC11A14FBD48/301 | LQFP48  | LQFP48: plastic low profile quad flat package; 48 leads; body 7 $\times$ 7 $\times$ 1.4 mm                              | SOT313-2 |

### 32-bit ARM Cortex-M0 microcontroller

| Function | Туре    |         |                      | LQFP48 | HVQFN33 | WCSP20 |

|----------|---------|---------|----------------------|--------|---------|--------|

|          |         | Port    | Glitch filter        | Pin    | Pin     | Ball   |

| SSP1 con | troller |         |                      |        |         |        |

| MISO1    | I/O     | PIO0_14 | 10 ns <sup>[2]</sup> | 30     | 20      | -      |

|          |         | PIO0_26 | no                   | 1      | 1       | -      |

|          |         | PIO1_8  | no                   | 26     | -       | -      |

| MOSI1    | I/O     | PIO0_27 | 10 ns <sup>[2]</sup> | 43     | 28      | -      |

|          |         | PIO0_31 | no                   | 24     | -       | -      |

|          |         | PIO0_30 | no                   | 40     | -       | -      |

|          |         | PIO1_6  | no                   | 11     | -       | -      |

| SCK1     | I/O     | PIO0_8  | 10 ns <sup>[2]</sup> | 34     | 23      | -      |

|          |         | PIO1_5  | no                   | 20     | -       | -      |

|          |         | PIO0_29 | no                   | 13     | -       | -      |

| SSEL1    | I/O     | PIO0_25 | no                   | 17     | 12      | -      |

|          |         | PIO1_4  | no                   | 19     | -       | -      |

|          |         | PIO0_28 | no                   | 2      | -       | -      |

| USART    |         |         |                      |        |         |        |

| RXD      | l       | PIO0_1  | no                   | 4      | 3       | B2     |

|          |         | PIO0_12 | no                   | 46     | 31      | E1     |

|          |         | PIO1_4  | no                   | 19     | -       | -      |

|          |         | PIO1_8  | no                   | 26     | -       | -      |

| TXD      | 0       | PIO0_13 | no                   | 47     | 32      | D1     |

|          |         | PIO0_15 | no                   | 41     | 27      | E4     |

|          |         | PIO0_26 | no                   | 1      | 1       | -      |

|          |         | PIO1_5  | no                   | 20     | -       | -      |

| SCLK     | I/O     | PIO0_11 | 10 ns <sup>[2]</sup> | 39     | 26      | D2     |

|          |         | PIO0_21 | no                   | 23     | 16      | -      |

|          |         | PIO0_23 | no                   | 45     | 30      | -      |

| CTS      | I       | PIO0_9  | 10 ns <sup>[2]</sup> | 35     | 24      | D4     |

|          |         | PIO0_21 | no                   | 23     | 16      | -      |

|          |         | PIO1_7  | no                   | 25     | -       | -      |

| RTS      | 0       | PIO0_10 | no                   | 38     | 25      | D3     |

|          |         | PIO0_23 | no                   | 45     | 30      | -      |

|          |         | PIO1_6  | no                   | 11     | -       | -      |

| DCD      | I       | PIO1_9  | no                   | 12     | -       | -      |

|          |         | PIO1_0  | no                   | 31     | -       | -      |

| DSR      | I       | PIO0_29 | no                   | 13     | -       | -      |

|          |         | PIO1_2  | no                   | 37     | -       | -      |

| DTR      | 0       | PIO0_28 | no                   | 2      | -       | -      |

|          |         | PIO1_1  | no                   | 36     | -       | -      |

#### Table 3. Pin multiplexing

### 32-bit ARM Cortex-M0 microcontroller

| Function      | Туре                    |         |                      | LQFP48 | HVQFN33 | WCSP20 |

|---------------|-------------------------|---------|----------------------|--------|---------|--------|

|               |                         | Port    | Glitch filter        | Pin    | Pin     | Ball   |

| RI            | I                       | PIO0_30 | no                   | 40     | -       | -      |

|               |                         | PIO0_31 | no                   | 24     | -       | -      |

|               |                         | PIO1_3  | no                   | 48     | -       | -      |

| 16-bit counte | r/timer CT <sup>·</sup> | 16B0    |                      |        |         |        |

| CT16B0_CAP    | 0                       | PIO0_2  | 50 ns <sup>[2]</sup> | 15     | 10      | A1     |

|               |                         | PIO0_18 | no                   | 10     | 8       | -      |

|               |                         | PIO0_30 | no                   | 40     | -       | -      |

| CT16B0_CAP    | 1                       | PIO0_16 | 10 ns <sup>[2]</sup> | 18     | 13      | A2     |

|               |                         | PIO1_4  | no                   | 19     | -       | -      |

| CT16B0_CAP    | 2                       | PIO0_17 | 10 ns <sup>[2]</sup> | 21     | 14      | A3     |

|               |                         | PIO1_5  | no                   | 20     | -       | -      |

| CT16B0_MAT    | 0 0                     | PIO0_7  | no                   | 33     | 22      | C4     |

|               |                         | PIO0_17 | no                   | 21     | 14      | A3     |

|               |                         | PIO1_6  | no                   | 11     | -       | -      |

| CT16B0_MAT    | 1 0                     | PIO0_4  | no                   | 28     | 18      | A4     |

|               |                         | PIO0_9  | no                   | 35     | 24      | D4     |

|               |                         | PIO1_0  | no                   | 31     | -       | -      |

| CT16B0_MAT    | 2 0                     | PIO0_5  | no                   | 29     | 19      | B3     |

|               |                         | PIO0_10 | no                   | 38     | 25      | D3     |

|               |                         | PIO1_7  | no                   | 25     | -       | -      |

| 16-bit counte | r/timer CT <sup>.</sup> | 16B1    | I                    |        |         |        |

| CT16B1_CAP    | 0                       | PIO0_3  | 50 ns <sup>[2]</sup> | 16     | 11      | B1     |

|               |                         | PIO0_24 | no                   | 9      | 7       | -      |

|               |                         | PIO1_3  | no                   | 48     | -       | -      |

| CT16B1_CAP    | 1                       | PIO0_18 | no                   | 10     | 8       | -      |

|               |                         | PIO0_26 | no                   | 1      | 1       | -      |

|               |                         | PIO0_31 | no                   | 24     | -       | -      |

| CT16B1_CAP    | 2                       | PIO0_27 | 10 ns <sup>[2]</sup> | 43     | 28      | -      |

|               |                         | PIO1_7  | no                   | 25     | -       | -      |

| CT16B1_MAT    | 0 O                     | PIO0_19 | no                   | 14     | 9       | -      |

|               |                         | PIO0_25 | no                   | 17     | 12      | -      |

|               |                         | PIO1_1  | no                   | 36     | -       | -      |

| CT16B1_MAT    | 1 0                     | PIO0_14 | no                   | 30     | 20      | B4     |

|               |                         | PIO1_2  | no                   | 37     | -       | -      |

|               |                         | PIO1_8  | no                   | 26     | -       | -      |

| CT16B1_MAT    | 2 0                     | PIO0_20 | no                   | 22     | 15      | -      |

|               |                         | PIO1_2  | no                   | 37     | -       | -      |

|               |                         | PIO1_9  | no                   | 12     | -       | -      |

#### Table 3. Pin multiplexing

### 32-bit ARM Cortex-M0 microcontroller

### Table 4. LPC11Axx pin description table

| Symbol                               | /Ball  |         |         | Туре | Reset<br>state<br>[1] | Description |                                                                                                |

|--------------------------------------|--------|---------|---------|------|-----------------------|-------------|------------------------------------------------------------------------------------------------|

|                                      | LQFP48 | HVQFN33 | WLCSP20 |      |                       |             |                                                                                                |

| TDI/PIO0_6/AD0/<br>CT32B0_MAT3/MISO0 | 32     | 21      | C3      | [9]  | 1                     | I; PU       | <b>TDI</b> — Test Data In for JTAG interface. Input glitch filter (10 ns) capable.             |

|                                      |        |         |         |      | I/O                   | -           | <b>PIO0_6</b> — General purpose digital input/output pin. Input glitch filter (10 ns) capable. |

|                                      |        |         |         |      | I                     | -           | AD0 — A/D converter input 0.                                                                   |

|                                      |        |         |         |      | 0                     | -           | CT32B0_MAT3 — Match output 3 for 32-bit timer 0.                                               |

|                                      |        |         |         |      | I/O                   | -           | <b>MISO0</b> — Master In Slave Out for SSP0. Input glitch filter (10 ns) capable.              |

| TMS/PIO0_7/AD1/<br>CT32B1_CAP0/      | 33     | 22      | C4      | [9]  | I                     | I; PU       | <b>TMS</b> — Test Mode Select for JTAG interface. Input glitch filter (10 ns) capable.         |

| CT16B0_MAT0                          |        |         |         |      | I/O                   | -           | <b>PIO0_7</b> — General purpose digital input/output pin. Input glitch filter (10 ns) capable. |

|                                      |        |         |         |      | I                     | -           | AD1 — A/D converter input 1.                                                                   |

|                                      |        |         |         |      | I                     | -           | <b>CT32B1_CAP0</b> — Capture input 0 for 32-bit timer 1. Input glitch filter (10 ns) capable.  |

|                                      |        |         |         |      | 0                     | -           | CT16B0_MAT0 — Match output 2 for 16-bit timer 0.                                               |

| TDO/PIO0_8/AD2/                      | 34     | 23      | C2      | [9]  | 0                     | I; PU       | <b>TDO</b> — Test Data Out for JTAG interface.                                                 |

| CT32B1_MAT0/SCK1                     |        |         |         |      | I/O                   | -           | <b>PIO0_8</b> — General purpose digital input/output pin. Input glitch filter (10 ns) capable. |

|                                      |        |         |         |      | I                     | -           | AD2 — A/D converter input 2.                                                                   |

|                                      |        |         |         |      | 0                     | -           | CT32B1_MAT0 — Match output 0 for 32-bit timer 1.                                               |

|                                      |        |         |         |      | I/O                   | -           | <b>SCK1</b> — Serial clock for SSP1. Input glitch filter (10 ns) capable.                      |

| TRST/PIO0_9/AD3/<br>CT32B1_MAT1/     | 35     | 24      | D4      | [9]  | I                     | I; PU       | <b>TRST</b> — Test Reset for JTAG interface. Input glitch filter (10 ns) capable.              |

| CT16B0_MAT1/CTS                      |        |         |         |      | I/O                   | -           | <b>PIO0_9</b> — General purpose digital input/output pin. Input glitch filter (10 ns) capable. |

|                                      |        |         |         |      | I                     | -           | AD3 — A/D converter, input 3.                                                                  |

|                                      |        |         |         |      | 0                     | -           | CT32B1_MAT1 — Match output 1 for 32-bit timer 1.                                               |

|                                      |        |         |         |      | 0                     | -           | CT16B0_MAT1 — Match output 1 for 16-bit timer 0.                                               |

|                                      |        |         |         |      | Ι                     | -           | <b>CTS</b> — Clear To Send input for USART. Input glitch filter (10 ns) capable.               |

### 32-bit ARM Cortex-M0 microcontroller

#### Table 4. LPC11Axx pin description table

| Symbol                      | Pin    | /Ball   | I       |            | Туре | Reset<br>state<br>[1] | Description                                                                                                                |                                                 |

|-----------------------------|--------|---------|---------|------------|------|-----------------------|----------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

|                             | LQFP48 | HVQFN33 | WLCSP20 |            |      |                       |                                                                                                                            |                                                 |

| PIO0_23/RTS/                | 45     | 30      | -       | [3]        | I/O  | I; PU                 | PIO0_23 — General purpose digital input/output pin.                                                                        |                                                 |

| ACMP_O/<br>CT32B0_CAP0/SCLK |        |         |         |            | 0    | -                     | RTS — Request To Send output for USART.                                                                                    |                                                 |

| 013200_0AI 0/30ER           |        |         |         |            | 0    | -                     | ACMP_O — Analog comparator output.                                                                                         |                                                 |

|                             |        |         |         |            | Ι    | -                     | CT32B0_CAP0 — Capture input 0 for 32-bit timer 0.                                                                          |                                                 |

|                             |        |         |         |            | I/O  | -                     | SCLK — Serial clock for USART.                                                                                             |                                                 |

| PIO0_24/SCL/CLKIN/          | 9      | 7       | -       | [3]        | I/O  | I; PU                 | PIO0_24 — General purpose digital input/output pin.                                                                        |                                                 |

| CT16B1_CAP0                 |        |         |         |            | I/O  | -                     | <b>SCL</b> — I <sup>2</sup> C-bus clock input/output. This is not an I <sup>2</sup> C-bus open-drain pin <sup>[10]</sup> . |                                                 |

|                             |        |         |         |            | Ι    | -                     | CLKIN — External clock input.                                                                                              |                                                 |

|                             |        |         |         |            | Ι    | -                     | CT16B1_CAP0 — Capture input 0 for 16-bit timer 1.                                                                          |                                                 |

| PIO0_25/SDA/SSEL1/          | 17     | 12      | -       | [3]        | I/O  | I; PU                 | PIO0_25 — General purpose digital input/output pin.                                                                        |                                                 |

| CT16B1_MAT0                 |        |         |         |            | I/O  | -                     | <b>SDA</b> — $I^2$ C-bus data input/output. This is not an $I^2$ C-bus open-drain pin <sup>[10]</sup> .                    |                                                 |

|                             |        |         |         |            | I/O  | -                     | SSEL1 — Slave Select for SSP1.                                                                                             |                                                 |

|                             |        |         |         |            | 0    | -                     | CT16B1_MAT0 — Match output 0 for 16-bit timer 1.                                                                           |                                                 |

| PIO0_26/TXD/MISO1/          | 1      | 1       | -       | [3]        | I/O  | I; PU                 | PIO0_26 — General purpose digital input/output pin.                                                                        |                                                 |

| CT16B1_CAP1/<br>CT32B0_CAP2 |        |         |         |            |      | 0                     | -                                                                                                                          | <b>TXD</b> — Transmitter data output for USART. |

| 010200_0/112                |        |         |         |            | I/O  | -                     | MISO1 — Master In Slave Out for SSP1.                                                                                      |                                                 |

|                             |        |         |         |            | 1    | -                     | <b>CT16B1_CAP1</b> — Capture input 1 for 16-bit timer 1.                                                                   |                                                 |

|                             |        |         |         |            | Ι    | -                     | CT32B0_CAP2 — Capture input 2 for 32-bit timer 0.                                                                          |                                                 |

| PIO0_27/MOSI1/<br>ACMP_I1/  | 43     | 28      | -       | <u>[9]</u> | I/O  | I; PU                 | <b>PIO0_27</b> — General purpose digital input/output pin. Input glitch filter (10 ns) capable.                            |                                                 |

| CT32B1_MAT1/<br>CT16B1_CAP2 |        |         |         |            | I/O  | -                     | <b>MOSI1</b> — Master Out Slave In for SSP1. Input glitch filter (10 ns) capable.                                          |                                                 |

|                             |        |         |         |            | I    | -                     | ACMP_I1 — Analog comparator input 1.                                                                                       |                                                 |

|                             |        |         |         |            | 0    | -                     | CT32B1_MAT1 — Match output 1 for 32-bit timer 1.                                                                           |                                                 |

|                             |        |         |         |            | I    | -                     | <b>CT16B1_CAP2</b> — Capture input 2 for 16-bit timer 1. Input glitch filter (10 ns) capable.                              |                                                 |

| PIO0_28/DTR/SSEL1/          | 2      | -       | -       | [3]        | I/O  | I; PU                 | PIO0_28 — General purpose digital input/output pin.                                                                        |                                                 |

| CT32B0_CAP0                 |        |         |         |            | 0    | -                     | <b>DTR</b> — Data Terminal Ready output for USART.                                                                         |                                                 |

|                             |        |         |         |            | I/O  | -                     | SSEL1 — Slave Select for SSP1.                                                                                             |                                                 |

|                             |        |         |         |            | Ι    | -                     | CT32B0_CAP0 — Capture input 0 for 32-bit timer 0.                                                                          |                                                 |

| PIO0_29/DSR/SCK1/           | 13     | -       | -       | [3]        | I/O  | I; PU                 | PIO0_29 — General purpose digital input/output pin.                                                                        |                                                 |

| CT32B0_CAP1                 |        |         |         |            | Ι    | -                     | <b>DSR</b> — Data Set Ready input for USART.                                                                               |                                                 |

|                             |        |         |         |            | I/O  | -                     | SCK1 — Serial clock for SSP1.                                                                                              |                                                 |

|                             |        |         |         |            | I    | -                     | CT32B0_CAP1 — Capture input 1 for 32-bit timer 0.                                                                          |                                                 |

#### 32-bit ARM Cortex-M0 microcontroller

| таріс ч.             |         | 40301   | 1010    |              |      |                       |                                                                                                                                                     |

|----------------------|---------|---------|---------|--------------|------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol               | Р       | in/Ball |         |              | Туре | Reset<br>state<br>[1] | Description                                                                                                                                         |

|                      | L OFP48 | HVQFN33 | WLCSP20 |              |      |                       |                                                                                                                                                     |

| $V_{SS(IO)}$         | 5       | 33      | E3      | <u>[14]</u>  | -    | -                     | Ground.                                                                                                                                             |

| V <sub>DD(3V3)</sub> | 44      | 4 29    | E2      | [12]<br>[13] | -    | -                     | 3.3 V supply voltage to the analog blocks, internal regulator,<br>and internal clock generator circuits. Also used as the ADC<br>reference voltage. |

| $V_{SS}$             | 4:      | 2 33    | E3      | [14]         | -    | -                     | Ground.                                                                                                                                             |

#### Table 4. LPC11Axx pin description table

[1] Pin state at reset for default function: I = Input; O = Output; PU = internal pull-up resistor (weak PMOS device) enabled; IA = inactive, no pull-up/down enabled.

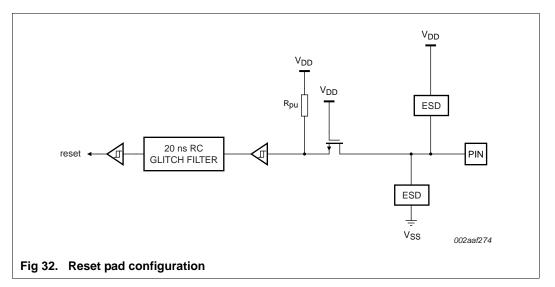

[2] See Figure 32 for the reset configuration.

[3] 5 V tolerant pin providing standard digital I/O functions with configurable modes and configurable hysteresis (Figure 31).

- [4] I<sup>2</sup>C-bus pins compliant with the I<sup>2</sup>C-bus specification for I<sup>2</sup>C standard mode, I<sup>2</sup>C Fast-mode, and I<sup>2</sup>C Fast-mode Plus.

- [5] For the SWD function, a pull-up resistor is recommended for the SWCLK pin (WLCSP20 parts only).

- [6] For the SWD function, a pull-up resistor is recommended for the SWDIO pin (WLCSP20 parts only).

- [7] Not a 5 V tolerant pin due to special analog functionality. Pin provides standard digital I/O functions with configurable modes, configurable hysteresis, and analog I/O. When configured as an analog I/O, the digital section of the pin is disabled (Figure 31).

- [8] If this pin is configured for its VDDCMP function, it cannot be used for SWCLK when the part is on the board. The bypass filter of the power supply filters out the SWCLK clock input signal.

- [9] 5 V tolerant pin providing standard digital I/O functions with configurable modes, configurable hysteresis, and analog I/O. When configured as an analog I/O, digital section of the pin is disabled, and the pin is not 5 V tolerant (Figure 31).

- [10] I<sup>2</sup>C-bus pins are standard digital I/O pins and have limited performance and electrical characteristics compared to the full I<sup>2</sup>C-bus specification. Pins can be configured with an on-chip pull-up resistor (pMOS device) and with open-drain mode. In this mode, typical bit rates of up to 100 kbit/s with 20 pF load are supported if the internal pull-ups are enabled. Higher bit rates can be achieved with an external resistor.

- [11] When the system oscillator is not used, connect XTALIN and XTALOUT as follows: XTALIN can be left floating or can be grounded (grounding is preferred to reduce susceptibility to noise). XTALOUT should be left floating. See <u>Section 12.3</u> if an external clock is connected to the XTALIN pin.

- [12] If separate supplies are used for V<sub>DD(3V3)</sub> and V<sub>DD(IO)</sub>, ensure that the power supply pins are filtered for noise with respect to their corresponding grounds V<sub>SS</sub> and V<sub>SS(IO)</sub> (LQFP48 package). Using separate filtered supplies reduces the noise to the analog blocks (see also Section 12.1).

- [13] If separate supplies are used for V<sub>DD(3V3)</sub> and V<sub>DD(IO)</sub>, ensure that the voltage difference between both supplies is smaller than or equal to 0.5 V.

- [14] Thermal pad (HVQFN33 pin package). Connect to ground.

### **NXP Semiconductors**

# LPC11Axx

### 32-bit ARM Cortex-M0 microcontroller

# 7.14 10-bit ADC

The LPC11Axx contains one ADC. It is a single 10-bit successive approximation ADC with eight channels.

#### 32-bit ARM Cortex-M0 microcontroller

#### 7.18.1 Features

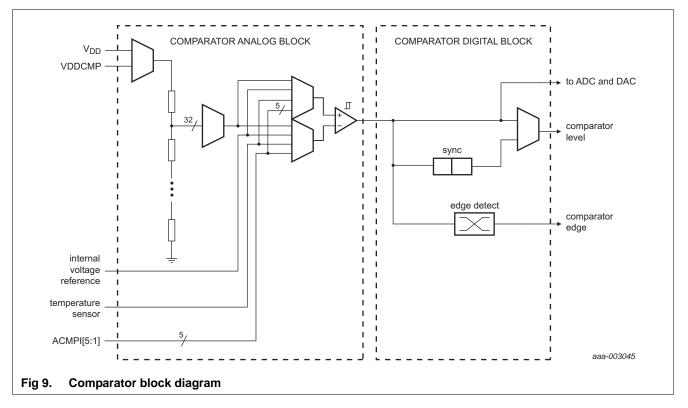

- Selectable 0 mV, 10 mV ( $\pm$  5 mV), and 20 mV ( $\pm$  10 mV), 40 mV ( $\pm$  20 mV) input hysteresis.

- Five selectable external voltages; fully configurable on either positive or negative input channel.

- Internal voltage reference from band gap and temperature sensor selectable on either positive or negative input channel.

- 32-stage voltage ladder with the internal reference voltage selectable on either the positive or the negative input channel. See <u>Table 24</u> to <u>Table 26</u>.

- Voltage ladder source voltage is selectable from an external pin or the main 3.3 V supply voltage rail.

- Voltage ladder can be separately powered down for applications only requiring the comparator function.

- Interrupt output is connected to NVIC.

- Comparator level output is connected to output pin ACMP\_O.

- Comparator output is internally connected to the ADC and DAC and can be used to trigger a conversion.

- The comparator output is also connected internally to capture channel 3 on each of the 32-bit and 16-bit counter/timers.

### 7.19 General purpose external event counter/timers

The LPC11Axx includes two 32-bit counter/timers and two 16-bit counter/timers. The counter/timer is designed to count cycles of the system derived clock. It can optionally generate interrupts or perform other actions at specified timer values, based on four match registers. Each counter/timer also includes four capture inputs to trap the timer value when an input signal transitions, optionally generating an interrupt.

### 7.19.1 Features

- A 32-bit/16-bit timer/counter with a programmable 32-bit/16-bit prescaler.

- Counter or timer operation.

- Four capture channels per timer, that can take a snapshot of the timer value when an input signal transitions. A capture event may also generate an interrupt. Up to three capture channels are pinned out. One channel is internally connected to the comparator output ACMP\_O.

- Four match registers per timer that allow:

- Continuous operation with optional interrupt generation on match.

- Stop timer on match with optional interrupt generation.

- Reset timer on match with optional interrupt generation.

- Up to four external outputs corresponding to match registers, with the following capabilities:

- Set LOW on match.

- Set HIGH on match.

- Toggle on match.

- Do nothing on match.

### 7.20 System tick timer

The ARM Cortex-M0 includes a system tick timer (SYSTICK) that is intended to generate a dedicated SYSTICK exception at a fixed time interval (typically 10 ms).

# 7.21 Windowed WatchDog Timer (WWDT)

The purpose of the watchdog is to reset the controller if software fails to periodically service it within a programmable time window.

### 7.21.1 Features

- Internally resets chip if not periodically reloaded during the programmable time-out period.

- Optional windowed operation requires reload to occur between a minimum and maximum time period, both programmable.

- Optional warning interrupt can be generated at a programmable time prior to watchdog time-out.

- Enabled by software but requires a hardware reset or a watchdog reset/interrupt to be disabled.

- Incorrect feed sequence causes reset or interrupt if enabled.

#### 32-bit ARM Cortex-M0 microcontroller

#### 7.22.1.1 Internal RC Oscillator (IRC)

The IRC may be used as the clock source for the WWDT, and/or as the clock that drives the PLL and subsequently the CPU. The nominal IRC frequency is 12 MHz. The IRC is trimmed to 1 % accuracy over the entire voltage and temperature range.

The IRC can be used as a clock source for the CPU with or without using the PLL. The IRC frequency can be boosted to a higher frequency, up to the maximum CPU operating frequency, by the system PLL.

Upon power-up or any chip reset, the LPC11Axx use the IRC as the clock source. Software may later switch to one of the other available clock sources.

#### 7.22.1.2 Crystal Oscillator (SysOsc)

The crystal oscillator can be used as the clock source for the CPU, with or without using the PLL.

The SysOsc operates at frequencies of 1 MHz to 25 MHz. This frequency can be boosted to a higher frequency, up to the maximum CPU operating frequency, by the system PLL.

#### 32-bit ARM Cortex-M0 microcontroller

# 8. Limiting values

#### Table 5. Limiting values

In accordance with the Absolute Maximum Rating System (IEC 60134).[1]

| Symbol                 | Parameter                             | Conditions                                                                                             | Min                  | Max  | Unit |

|------------------------|---------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------|------|------|

| V <sub>DD(3V3)</sub>   | supply voltage (3.3 V)                |                                                                                                        | [2] -0.5             | 4.6  | V    |

| V <sub>DD(IO)</sub>    | input/output supply voltage           |                                                                                                        | <u>[2]</u> –0.5      | 4.6  | V    |

| Vı                     | input voltage                         | 5 V tolerant I/O<br>pins; only valid<br>when the V <sub>DD(IO)</sub><br>supply voltage is<br>present   | <u>[3][4]</u> –0.5   | +5.5 | V    |

|                        |                                       | on pins PIO0_2<br>and PIO0_3                                                                           | <u>[5]</u> –0.5      | +5.5 | V    |

|                        |                                       | 3 V tolerant I/O<br>pins without<br>over-voltage<br>protection                                         | <u>[6]</u> –0.5      | +3.6 | V    |

| V <sub>IA</sub>        | analog input voltage                  |                                                                                                        | [7][8]<br>[9] –0.5 V | 4.6  | V    |

| V <sub>i(xtal)</sub>   | crystal input voltage                 |                                                                                                        | <u>[2]</u> –0.5      | +2.5 | V    |

| I <sub>DD</sub>        | supply current                        | per supply pin                                                                                         | -                    | 100  | mA   |

| I <sub>SS</sub>        | ground current                        | per ground pin                                                                                         | -                    | 100  | mA   |

| I <sub>latch</sub>     | I/O latch-up current                  | −(0.5V <sub>DD(IO)</sub> ) < V <sub>I</sub> <<br>(1.5V <sub>DD(IO)</sub> );<br>T <sub>i</sub> < 125 °C | -                    | 100  | mA   |

| T <sub>stg</sub>       | storage temperature                   |                                                                                                        | <u>[10]</u> –65      | +150 | °C   |

| T <sub>j(max)</sub>    | maximum junction temperature          |                                                                                                        | -                    | 150  | °C   |

| P <sub>tot(pack)</sub> | total power dissipation (per package) | based on package<br>heat transfer, not<br>device power<br>consumption                                  | -                    | 1.5  | W    |

| V <sub>esd</sub>       | electrostatic discharge voltage       | human body<br>model; all pins                                                                          | <u>[11]</u> –6.5     | +6.5 | kV   |

| V <sub>trig</sub>      | trigger voltage                       | for LVTSCR based<br>ESD pin protection;                                                                | <u>[12]</u> 8.2      | -    | V    |

|                        |                                       | 1 ns to 10 ns rise<br>time                                                                             |                      |      |      |

|                        |                                       | > 10 ns rise time                                                                                      | > 8.5                | -    | V    |

[1] The following applies to the limiting values:

a) This product includes circuitry specifically designed for the protection of its internal devices from the damaging effects of excessive static charge. Nonetheless, it is suggested that conventional precautions be taken to avoid applying greater than the rated maximum.

b) Parameters are valid over operating temperature range unless otherwise specified. All voltages are with respect to V<sub>SS</sub> unless otherwise noted.

[2] Maximum/minimum voltage above the maximum operating voltage (see <u>Table 6</u>) and below ground that can be applied for a short time (< 10 ms) to a device without leading to irrecoverable failure. Failure includes the loss of reliability and shorter lifetime of the device.

[3] Applies to all 5 V tolerant I/O pins except true open-drain pins PIO0\_2 and PIO0\_3 and except the 3 V tolerant pins PIO0\_4 and PIO0\_14 (LQFP and HVQFN packages) or PIO0\_5 (WLCSP package).

#### 32-bit ARM Cortex-M0 microcontroller

- [4] Including the voltage on outputs in 3-state mode.

- [5] V<sub>DD(IO)</sub> present or not present. Compliant with the I<sup>2</sup>C-bus standard. 5.5 V can be applied to this pin when V<sub>DD(IO)</sub> is powered down.

- [6] Applies to 3 V tolerant pins PIO0\_4 and PIO0\_14 (LQFP and HVQFN packages) or PIO0\_5 (WLCSP package).

- [7] An ADC input voltage above 3.6 V can be applied for a short time without leading to immediate, unrecoverable failure. Accumulated exposure to elevated voltages at 4.6 V must be less than 10<sup>6</sup> s total over the lifetime of the device. Applying an elevated voltage to the ADC inputs for a long time affects the reliability of the device and reduces its lifetime.

- [8] If the comparator is configured with the common mode input  $V_{IC} = V_{DD}$ , the other comparator input can be up to 0.2 V above or below  $V_{DD}$  without affecting the hysteresis range of the comparator function.

- [9] It is recommended to connect an overvoltage protection diode between the analog input pin and the voltage supply pin.

- [10] Dependent on package type.

- [11] Human body model: equivalent to discharging a 100 pF capacitor through a 1.5 kΩ series resistor.

- [12] Not characterized.

Product data sheet

#### 32-bit ARM Cortex-M0 microcontroller

-15

10

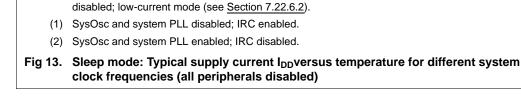

Conditions:  $V_{DD(3V3)} = 3.3 V$ ; sleep mode entered from flash; all peripherals disabled in the SYSAHBCLKCTRL register and PDRUNCFG register; all peripheral clocks disabled; BOD

35

0

-40

LPC11AXX

85

60 temperature (°C)

# 9.2 Peripheral power consumption

The supply current per peripheral is measured as the difference in supply current between the peripheral block enabled and the peripheral block disabled in the SYSAHBCLKCFG and PDRUNCFG (for analog blocks) registers. All other blocks are disabled in both registers and no code is executed. Measured on a typical sample at  $T_{amb} = 25$  °C.

| Peripheral                                    | Typical supply<br>current in mA |                     |

|-----------------------------------------------|---------------------------------|---------------------|

|                                               | 12 MHz <sup>[1]</sup>           | Average $\mu$ A/MHz |

| Analog peripherals                            |                                 |                     |

| BOD                                           | 0.05                            | -                   |

| BOD, comparator                               | 0.14                            | -                   |

| BOD, comparator, ADC, DAC, temperature sensor | 0.40                            | -                   |

| DAC                                           | 0.26                            | -                   |

| ADC                                           | 0.01                            | -                   |

| Temperature sensor, ADC                       | 0.01                            | -                   |

| Digital peripherals                           |                                 |                     |

| USART                                         | 0.15                            | 12                  |

| 12C                                           | 0.02                            | 2                   |

| 16-bit counter/timer 0/1                      | 0.02                            | 2                   |

| 32-bit counter/timer 0/1                      | 0.02                            | 2                   |

| WWDT                                          | 0.02                            | 2                   |

Table 7.

Power consumption for individual analog and digital blocks

[1] IRC on; PLL off.

# 9.3 Electrical pin characteristics

All information provided in this document is subject to legal disclaimers

### 32-bit ARM Cortex-M0 microcontroller

Product data sheet

# **10.** Dynamic characteristics

### 10.1 Power supply fluctuations

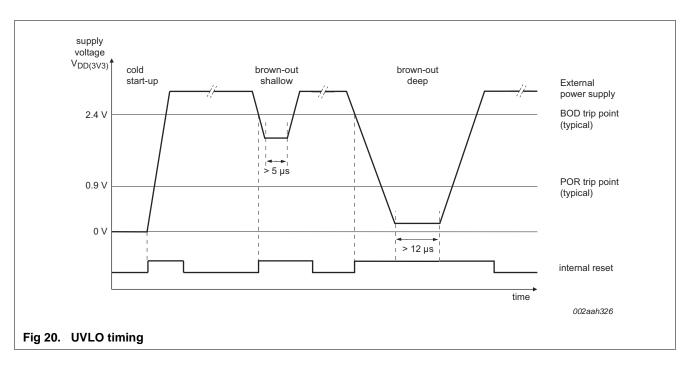

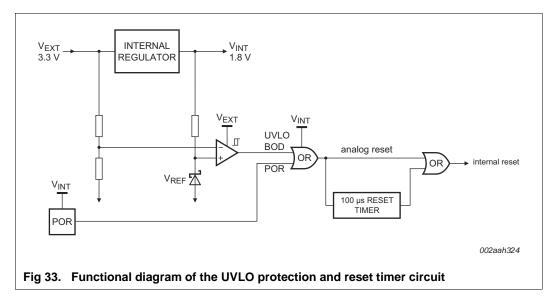

If the input voltage  $(V_{DD(3V3)})$  to the internal regulator fluctuates, the LPC11Axx is held in reset during a brown-out condition as long as the UVLO circuit is operating. The settling times of the BOD and POR circuits, which constitute the UVLO, determine the minimum time the supply level must remain in the shallow or deep brown-out condition to ensure that the internal reset is asserted properly.

See also Section 7.23.1, Section 12.7, and Section 12.8.

| Table 8. | UVLO | circuits | settling | characteristics |

|----------|------|----------|----------|-----------------|

|          |      | onounco  | ooung    |                 |

| Symbol         | Parameter     | Conditions                                                                                                                                  | Min | Тур | Max | Unit |

|----------------|---------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| t <sub>s</sub> | settling time | power droop:<br>from active level to shallow<br>brown-out level<br>$(0.9 \text{ V} \le \text{V}_{\text{DD}(3\text{V3})} \le 2.4 \text{ V})$ | 5   | -   | -   | μS   |

|                |               | from active level to deep brown-out level (0 < $V_{DD(3V3)}$ < 0.9 V)                                                                       | 12  | -   | -   | μs   |

### 10.2 Flash/EEPROM memory

#### Table 9. Flash characteristics

$T_{amb} = -40 \ ^{\circ}C$  to +85  $^{\circ}C$ . Based on JEDEC NVM qualification. Failure rate < 10 ppm for parts as specified below.

| Symbol            | Parameter | Conditions |               | Min   | Тур    | Max | Unit   |

|-------------------|-----------|------------|---------------|-------|--------|-----|--------|

| N <sub>endu</sub> | endurance |            | <u>[2][1]</u> | 10000 | 100000 | -   | cycles |

LPC11AXX

#### 32-bit ARM Cortex-M0 microcontroller

#### Table 9. Flash characteristics

$T_{amb} = -40 \ ^{\circ}C$  to +85  $^{\circ}C$ . Based on JEDEC NVM qualification. Failure rate < 10 ppm for parts as specified below.

| Symbol            | Parameter           | Conditions                                   | ſ               | Min  | Тур | Max  | Unit  |

|-------------------|---------------------|----------------------------------------------|-----------------|------|-----|------|-------|

| t <sub>ret</sub>  | retention time      | powered                                      | <u>[2]</u> 1    | 10   | 20  | -    | years |

|                   |                     | unpowered                                    | [2] 2           | 20   | 40  | -    | years |

| t <sub>er</sub>   | erase time          | sector or multiple<br>consecutive<br>sectors | <u>[2]</u> ç    | 95   | 100 | 105  | ms    |

| t <sub>prog</sub> | programming<br>time |                                              | <u>[2][3]</u> ( | 0.95 | 1   | 1.05 | ms    |

[1] Number of program/erase cycles.

[2] Min and max values are valid for  $T_{amb}$  = -40 °C to +85 °C only.

[3] Programming times are given for writing 256 bytes to the flash. T<sub>amb</sub> < +85 °C. Data must be written to the flash in blocks of 256 bytes. Flash programming is accomplished via IAP calls (see LPC11Axx user manual). Execution time of IAP calls depends on the system clock and is typically between 1.5 and 2 ms per 256 bytes.</p>

#### Table 10. EEPROM characteristics

$T_{amb} = -55 \text{ }^{\circ}\text{C}$  to +125  $\text{}^{\circ}\text{C}$ ;  $V_{DD(3V3)} = 2.7 \text{ V}$  to 3.6 V. Based on JEDEC NVM qualification. Failure rate < 10 ppm for parts as specified below.

| Symbol            | Parameter           | Conditions | Min                | Тур     | Max | Unit   |

|-------------------|---------------------|------------|--------------------|---------|-----|--------|

| N <sub>endu</sub> | endurance           |            | [ <u>1]</u> 100000 | 1000000 | -   | cycles |

| t <sub>ret</sub>  | retention time      | powered    | <u>[1]</u> 100     | 200     | -   | years  |

|                   |                     | unpowered  | <u>[1]</u> 150     | 300     | -   | years  |

| t <sub>prog</sub> | programming<br>time | 64 bytes   | [2] _              | 1.1     | -   | ms     |

[1] Min and max values are valid for  $T_{amb} = -40 \text{ °C to } +85 \text{ °C only}$ .

[2] T<sub>amb</sub> < +85 °C.

### 10.3 External clock for oscillator in slave mode

**Remark:** The input voltage on the XTALIN pin must be  $\leq$  1.95 V (see <u>Table 6</u>). For connecting the oscillator to the XTALIN/XTALOUT pins also see Section 12.3.

| Table 11. | Dynamic characteristic: exter | nal clock (XTALIN or CLKIN pin) |

|-----------|-------------------------------|---------------------------------|

|           |                               |                                 |

$T_{amb} = -40 \ ^{\circ}C$  to +85  $^{\circ}C$ ;  $V_{DD(3V3)}$  over specified ranges.[1]

| anno                 | 22(010)              |            | •                               |                |      |      |

|----------------------|----------------------|------------|---------------------------------|----------------|------|------|

| Symbol               | Parameter            | Conditions | Min                             | Typ <u>[2]</u> | Max  | Unit |

| f <sub>osc</sub>     | oscillator frequency |            | 1                               | -              | 25   | MHz  |

| T <sub>cy(clk)</sub> | clock cycle time     |            | 40                              | -              | 1000 | ns   |

| t <sub>CHCX</sub>    | clock HIGH time      |            | $T_{\text{cy(clk)}} \times 0.4$ | -              | -    | ns   |

| t <sub>CLCX</sub>    | clock LOW time       |            | $T_{\text{cy(clk)}} \times 0.4$ | -              | -    | ns   |

| t <sub>CLCH</sub>    | clock rise time      |            | -                               | -              | 5    | ns   |

| t <sub>CHCL</sub>    | clock fall time      |            | -                               | -              | 5    | ns   |

[1] Parameters are valid over operating temperature range unless otherwise specified.

[2] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

32-bit ARM Cortex-M0 microcontroller

# 12.6 Reset pad configuration

# 12.7 UVLO protection and reset timer circuit

# 12.8 Guidelines for selecting a power supply filter for UVLO protection

For the UVLO circuits to hold the part in reset during shallow and deep brown-out conditions, you must filter the power supply line to allow for the BOD and POR circuits to settle when short voltage drops occur (see <u>Section 10.1 "Power supply fluctuations</u>").

Select the capacitance of the decoupling/bypass capacitor according to the following guidelines:

$C >> I_{DD} \times t_{s} / \Delta V_{DD(3V3)}$  with

- $\Delta V_{DD(3V3)} \approx 100 \text{ mV}$  for the voltage drop below the BOD or POR trip points.

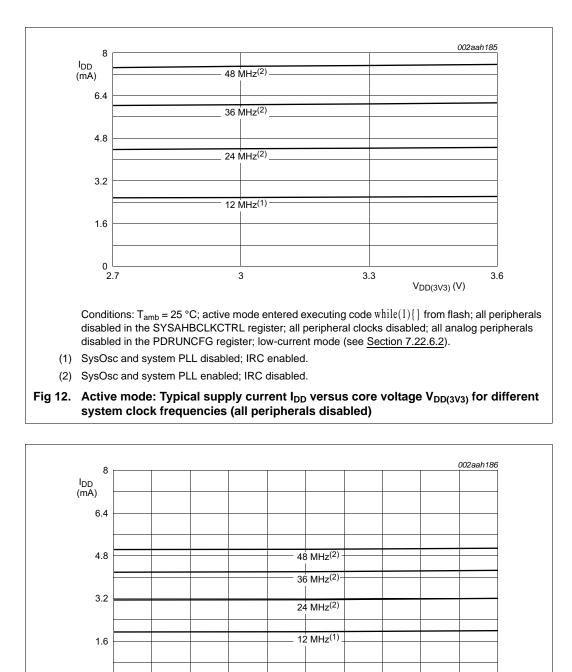

- $I_{DD} \approx 3$  mA with the IRC running and PLL/SysOsc off (see Figure 12).

# 17. Legal information

# 17.1 Data sheet status

| Document status[1][2]          | Product status[3] | Definition                                                                            |

|--------------------------------|-------------------|---------------------------------------------------------------------------------------|

| Objective [short] data sheet   | Development       | This document contains data from the objective specification for product development. |

| Preliminary [short] data sheet | Qualification     | This document contains data from the preliminary specification.                       |

| Product [short] data sheet     | Production        | This document contains the product specification.                                     |

[1] Please consult the most recently issued document before initiating or completing a design.

[2] The term 'short data sheet' is explained in section "Definitions".

[3] The product status of device(s) described in this document may have changed since this document was published and may differ in case of multiple devices. The latest product status information is available on the Internet at URL <a href="http://www.nxp.com">http://www.nxp.com</a>.

# 17.2 Definitions

**Draft** — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

Short data sheet — A short data sheet is an extract from a full data sheet with the same product type number(s) and title. A short data sheet is intended for quick reference only and should not be relied upon to contain detailed and full information. For detailed and full information see the relevant full data sheet, which is available on request via the local NXP Semiconductors sales office. In case of any inconsistency or conflict with the short data sheet, the full data sheet shall prevail.

**Product specification** — The information and data provided in a Product data sheet shall define the specification of the product as agreed between NXP Semiconductors and its customer, unless NXP Semiconductors and customer have explicitly agreed otherwise in writing. In no event however, shall an agreement be valid in which the NXP Semiconductors product is deemed to offer functions and qualities beyond those described in the Product data sheet.

# 17.3 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. NXP Semiconductors takes no responsibility for the content in this document if provided by an information source outside of NXP Semiconductors.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the *Terms and conditions of commercial sale* of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors and its suppliers accept no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

Limiting values — Stress above one or more limiting values (as defined in the Absolute Maximum Ratings System of IEC 60134) will cause permanent damage to the device. Limiting values are stress ratings only and (proper) operation of the device at these or any other conditions above those given in the Recommended operating conditions section (if present) or the Characteristics sections of this document is not warranted. Constant or repeated exposure to limiting values will permanently and irreversibly affect the quality and reliability of the device.

Terms and conditions of commercial sale — NXP Semiconductors products are sold subject to the general terms and conditions of commercial sale, as published at <a href="http://www.nxp.com/profile/terms">http://www.nxp.com/profile/terms</a>, unless otherwise agreed in a valid written individual agreement. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. NXP Semiconductors hereby expressly objects to applying the customer's general terms and conditions with regard to the purchase of NXP Semiconductors products by customer.

**No offer to sell or license** — Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights.

© NXP B.V. 2012. All rights reserved.