Welcome to **E-XFL.COM**

# **Understanding Embedded - FPGAs (Field Programmable Gate Array)**

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                             |

|--------------------------------|-------------------------------------------------------------|

| Product Status                 | Obsolete                                                    |

| Number of LABs/CLBs            | 6144                                                        |

| Number of Logic Elements/Cells | 27648                                                       |

| Total RAM Bits                 | 131072                                                      |

| Number of I/O                  | 404                                                         |

| Number of Gates                | 1124022                                                     |

| Voltage - Supply               | 2.375V ~ 2.625V                                             |

| Mounting Type                  | Through Hole                                                |

| Operating Temperature          | -55°C ~ 125°C (TJ)                                          |

| Package / Case                 | 28-CDIP (0.300", 7.62mm)                                    |

| Supplier Device Package        | 28-CDIP                                                     |

| Purchase URL                   | https://www.e-xfl.com/product-detail/xilinx/5962-9957401qxa |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 1: QPro Virtex Field-Programmable Gate Array Family Members

| Device  | System Gates | CLB Array | Logic Cells | Maximum<br>Available I/O | Block RAM Bits | Max Select<br>RAM Bits |

|---------|--------------|-----------|-------------|--------------------------|----------------|------------------------|

| XQV100  | 108,904      | 20 x 30   | 2,700       | 180                      | 40,960         | 38,400                 |

| XQV300  | 322,970      | 32 x 48   | 6,912       | 316                      | 65,536         | 98,304                 |

| XQV600  | 661,111      | 48 x 72   | 15,552      | 316                      | 98,304         | 221,184                |

| XQV1000 | 1,124,022    | 64 x 96   | 27,648      | 404                      | 131,072        | 393,216                |

### **Virtex Electrical Characteristics**

Based on preliminary characterization. Further changes are not expected.

All specifications are representative of worst-case supply voltage and junction temperature conditions. The parameters included are common to popular designs and typical applications. Contact the factory for design considerations requiring more detailed information.

#### Virtex DC Characteristics

## **Absolute Maximum Ratings**

| Symbol              | Description                                        |                           | Min/Max     | Units |

|---------------------|----------------------------------------------------|---------------------------|-------------|-------|

| V <sub>CCINT</sub>  | Supply voltage relative to GND                     |                           | -0.5 to 3.0 | V     |

| V <sub>CCO</sub>    | Supply voltage relative to GND                     | y voltage relative to GND |             | V     |

| V <sub>REF</sub>    | Input reference Voltage                            | Voltage                   |             | V     |

| Λ <sup>IN</sup> (3) | Input voltage relative to GND                      | Using V <sub>REF</sub>    | -0.5 to 3.6 | V     |

|                     |                                                    | Internal threshold        | -0.5 to 5.5 | V     |

| V <sub>TS</sub>     | Voltage applied to 3-state output                  | ,                         | -0.5 to 5.5 | V     |

| V <sub>CC</sub>     | Longest supply voltage rise time from 1V to 2.375V |                           | 50          | ms    |

| T <sub>STG</sub>    | Storage temperature (ambient)                      |                           | -65 to +150 | °C    |

| T <sub>J</sub>      | Junction temperature                               | Ceramic packages          | +150        | °C    |

|                     |                                                    | Plastic packages          | +125        | °C    |

- Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress

ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions

is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time may affect device reliability.

- 2. Power supplies may turn on in any order.

- 3. For protracted periods (e.g., longer than a day), V<sub>IN</sub> should not exceed V<sub>CCO</sub> by more that 3.6V.

## **Recommended Operating Conditions**

| Symbol             | Description                                                    |                  | Min             | Max      | Units |

|--------------------|----------------------------------------------------------------|------------------|-----------------|----------|-------|

| V <sub>CCINT</sub> | Supply voltage relative to GND, $T_C = -55^{\circ}C$ to +125°C | Ceramic packages | 2.5 – 5%        | 2.5 + 5% | V     |

|                    | Supply voltage relative to GND, $T_J = -55^{\circ}C$ to +125°C | Plastic packages | 2.5 – 5%        | 2.5 + 5% | V     |

| V <sub>CCO</sub>   | Supply voltage relative to GND, $T_C = -55^{\circ}C$ to +125°C | Ceramic packages | 1.2             | 3.6      | V     |

|                    | Supply voltage relative to GND, $T_J = -55^{\circ}C$ to +125°C | Plastic packages | 1.2             | 3.6      | V     |

| T <sub>IN</sub>    | Input signal transition time                                   |                  | -               | 250      | ns    |

| T <sub>IC</sub>    | Initialization Temperature Range <sup>(4)</sup>                | XQVR300          | <del>-</del> 55 | +125     | °C    |

|                    |                                                                | XQVR600          | <del>-</del> 55 | +125     | °C    |

|                    |                                                                | XQVR1000         | -40             | +125     | °C    |

| T <sub>OC</sub>    | Operational Temperature Range <sup>(5)</sup>                   | XQVR300          | <del>-</del> 55 | +125     | °C    |

|                    |                                                                | XQVR600          | <b>-</b> 55     | +125     | °C    |

|                    |                                                                | XQVR1000         | <b>-</b> 55     | +125     | ç     |

#### Notes:

- 1. Correct operation is guaranteed with a minimum  $V_{CCINT}$  of 2.25V (Nominal  $V_{CCINT}$  10%). Below the minimum value stated above, all delay parameters increase by 3% for each 50 mV reduction in  $V_{CCINT}$  below the specified range.

- 2. At junction temperatures above those listed as Operating Conditions, all delay parameters increase by 0.35% per °C.

- 3. Input and output measurement threshold is  $\sim$ 50% of  $V_{CC}$ .

- 4. Initialization occurs from the moment of V<sub>CC</sub> ramp-up to the rising transition of the INIT pin.

- 5. The device is operational after the INIT pin has transitioned high.

### **DC Characteristics Over Recommended Operating Conditions**

| Symbol              | Description                                                                            | Device  | Min | Max  | Units |

|---------------------|----------------------------------------------------------------------------------------|---------|-----|------|-------|

| V <sub>DRINT</sub>  | Data retention V <sub>CCINT</sub> voltage (below which configuration data may be lost) | All     | 2.0 | -    | V     |

| V <sub>DRIO</sub>   | Data retention V <sub>CCO</sub> voltage (below which configuration data may be lost)   | All     | 1.2 | -    | V     |

| I <sub>CCINTQ</sub> | Quiescent V <sub>CCINT</sub> supply current <sup>(1)</sup>                             | XQV100  | ı   | 50   | mA    |

|                     |                                                                                        | XQV300  | -   | 75   | mA    |

|                     |                                                                                        | XQV600  | -   | 100  | mA    |

|                     |                                                                                        | XQV1000 | -   | 100  | mA    |

| I <sub>CCOQ</sub>   | Quiescent V <sub>CCINT</sub> supply current <sup>(1)</sup>                             | XQV100  | -   | 2    | mA    |

|                     |                                                                                        | XQV300  | -   | 2    | mA    |

|                     |                                                                                        | XQV600  | -   | 2    | mA    |

|                     |                                                                                        | XQV1000 | -   | 2    | mA    |

| I <sub>REF</sub>    | V <sub>REF</sub> current per V <sub>REF</sub> pin                                      | -       | -   | 20   | μΑ    |

| IL                  | Input or output leakage current                                                        | -       | -10 | +10  | μΑ    |

| C <sub>IN</sub>     | Input capacitance (sample tested)                                                      | -       | -   | 8    | pF    |

| I <sub>RPU</sub>    | Pad pull-up (when selected) at $V_{IN} = 0V$ , $V_{CCO} = 3.3V$ (sample tested)        | -       | (2) | 0.25 | mA    |

| I <sub>RPD</sub>    | Pad pull-down (when selected) at V <sub>IN</sub> = 3.6V (sample tested)                | -       | (2) | 0.15 | mA    |

- 1. With no output current loads, no active input pull-up resistors, all I/O pins in a High-Z state and floating.

- 2. Internal pull-up and pull-down resistors guarantee valid logic levels at unconnected input pins. These pull-up and pull-down resistors do not guarantee valid logic levels when input pins are connected to other circuits.

## **Virtex Switching Characteristics**

Testing of switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100% functionally tested. Internal timing parameters are derived from measuring internal test patterns. Listed below are representative values. For more specific, more precise, and worst-case guaranteed data, use the values reported

by the static timing analyzer (TRCE in the Xilinx Development System) and back-annotated to the simulation netlist. All timing parameters assume worst-case operating conditions (supply voltage and junction temperature). Values apply to all Virtex devices unless otherwise noted.

## **IOB Input Switching Characteristics**

Input delays associated with the pad are specified for LVTTL levels. For other standards, adjust the delays with

the values shown in "IOB Input Switching Characteristics Standard Adjustments" on page 6.

|                                             |                                                  |         | Speed     | Grade    |       |

|---------------------------------------------|--------------------------------------------------|---------|-----------|----------|-------|

|                                             |                                                  |         | -4        |          |       |

| Symbol                                      | Description                                      | Device  | Min       | Max      | Units |

| Propagation Delays                          |                                                  |         | '         | <u>'</u> |       |

| T <sub>IOPI</sub>                           | Pad to I output, no delay                        | All     | -         | 1.0      | ns    |

| T <sub>IOPID</sub>                          | Pad to I output, with delay                      | XQV100  | -         | 1.9      | ns    |

|                                             |                                                  | XQV300  | -         | 1.9      | ns    |

|                                             |                                                  | XQV600  | -         | 2.3      | ns    |

|                                             |                                                  | XQV1000 | -         | 2.7      | ns    |

| T <sub>IOPLI</sub>                          | Pad to output IQ via transparent latch, no delay | All     | -         | 2.0      | ns    |

| T <sub>IOPLID</sub>                         | Pad to output IQ via transparent latch, with     | XQV100  | -         | 4.8      | ns    |

|                                             | delay                                            | XQV300  | -         | 5.1      | ns    |

|                                             |                                                  | XQV600  | -         | 5.5      | ns    |

|                                             |                                                  | XQV1000 | -         | 5.9      | ns    |

| Sequential Delays                           |                                                  |         |           | <u> </u> |       |

| T <sub>IOCKIQ</sub>                         | Clock CLK to output IQ                           | All     | -         | 0.8      | ns    |

| Setup and Hold Times                        | with Respect to Clock CLK                        | Setu    | up Time / | Hold Tim | е     |

| T <sub>IOPICK</sub> / T <sub>IOICKP</sub>   | Pad, no delay                                    | All     | 2.0/0     | -        | ns    |

| T <sub>IOPICKD</sub> / T <sub>IOICKPD</sub> | Pad, with delay                                  | All     | 5.0/0     | -        | ns    |

| T <sub>IOICECK</sub> / T <sub>IOCKICE</sub> | ICE input                                        | All     | 1.0/0     | -        | ns    |

| T <sub>IOSRCKI</sub> / T <sub>IOCKISR</sub> | SR input (IFF, synchronous)                      | All     | 1.3/0     | -        | ns    |

| Set/Reset Delays                            | 1                                                |         | 1         |          |       |

| T <sub>IOSRIQ</sub>                         | SR input to IQ (asynchronous)                    | All     | -         | 1.8      | ns    |

| T <sub>GSRQ</sub>                           | GSR to output IQ                                 | All     | -         | 12.5     | ns    |

<sup>1.</sup> A Zero "0" Hold Time listing indicates no hold time or a negative hold time. Negative values can not be guaranteed "best-case", but if a "0" is listed, there is no positive hold time.

# **IOB Input Switching Characteristics Standard Adjustments**

|                       |                                                |                   | Speed Grade | T     |

|-----------------------|------------------------------------------------|-------------------|-------------|-------|

| Symbol                | Description                                    | Standard          | -4          | Units |

| Data Input D          | elay Adjustments                               |                   |             |       |

| T <sub>ILVTTL</sub>   | Standard-specific data input delay adjustments | LVTTL             | 0.0         | ns    |

| T <sub>ILVCMOS2</sub> |                                                | LVCMOS2           | -0.05       | ns    |

| T <sub>IPCI33_3</sub> |                                                | PCI, 33 MHz, 3.3V | -0.14       | ns    |

| T <sub>IPCI33_5</sub> |                                                | PCI, 33 MHz, 5.0V | 0.33        | ns    |

| T <sub>IGTL</sub>     |                                                | GTL               | 0.26        | ns    |

| T <sub>IGTLP</sub>    |                                                | GTL+              | 0.14        | ns    |

| T <sub>IHSTL</sub>    |                                                | HSTL              | 0.04        | ns    |

| T <sub>ISSTL2</sub>   |                                                | SSTL2             | -0.10       | ns    |

| T <sub>ISSTL3</sub>   |                                                | SSTL3             | -0.06       | ns    |

| T <sub>ICTT</sub>     |                                                | CTT               | 0.02        | ns    |

| T <sub>IAGP</sub>     |                                                | AGP               | -0.08       | ns    |

## **IOB Output Switching Characteristics**

Output delays terminating at a pad are specified for LVTTL with 12 mA drive and fast slew rate. For other standards, adjust the delays with the values shown in "IOB Output Switching Characteristics Standard Adjustments" on page 8.

|                                            |                                                                    | Speed   | Grade     |                       |  |

|--------------------------------------------|--------------------------------------------------------------------|---------|-----------|-----------------------|--|

|                                            | Description                                                        | -4      | 1         |                       |  |

| Symbol                                     |                                                                    | Min     | Max       | Units                 |  |

| Propagation Delays                         |                                                                    |         |           |                       |  |

| T <sub>IOOP</sub>                          | O input to pad                                                     | -       | 3.5       | ns                    |  |

| T <sub>IOOLP</sub>                         | O input to pad via transparent latch                               | -       | 4.0       | ns                    |  |

| 3-State Delays                             |                                                                    |         |           | II.                   |  |

| T <sub>IOTHZ</sub>                         | T input to pad high-impedance <sup>(1)</sup>                       | -       | 2.4       | ns                    |  |

| T <sub>IOTON</sub>                         | T input to valid data on pad                                       | -       | 3.7       | ns                    |  |

| T <sub>IOTLPHZ</sub>                       | T input to pad high-impedance via transparent latch <sup>(1)</sup> | -       | 3.0       | ns                    |  |

| T <sub>IOTLPON</sub>                       | T input to valid data on pad via transparent latch                 | -       | 4.2       | ns                    |  |

| T <sub>GTS</sub>                           | GTS to pad high-impedance <sup>(1)</sup>                           | -       | 6.3       | ns                    |  |

| Sequential Delays                          | 1                                                                  |         |           |                       |  |

| T <sub>IOCKP</sub>                         | Clock CLK to pad                                                   | -       | 3.5       | ns                    |  |

| T <sub>IOCKHZ</sub>                        | Clock CLK to pad high-impedance (synchronous)(1)                   | -       | 2.9       | ns                    |  |

| T <sub>IOCKON</sub>                        | Clock CLK to valid data on pad (synchronous)                       | -       | 4.1       | ns                    |  |

| Setup and Hold Times                       | before/after Clock CLK                                             | Setup T | ime / Hol | d Time <sup>(2)</sup> |  |

| T <sub>IOOCK</sub> /T <sub>IOCKO</sub>     | O input                                                            | 1.3 / 0 | -         | ns                    |  |

| T <sub>IOOCECK</sub> /T <sub>IOCKOCE</sub> | OCE input                                                          | 1.0 / 0 | -         | ns                    |  |

| T <sub>IOSRCKO</sub> /T <sub>IOCKOSR</sub> | SR input (OFF)                                                     | 1.4 / 0 | -         | ns                    |  |

| T <sub>IOTCK</sub> /T <sub>IOCKT</sub>     | 3-state setup times, T input                                       | 0.9 / 0 | -         | ns                    |  |

| T <sub>IOTCECK</sub> /T <sub>IOCKTCE</sub> | 3-state setup times, TCE input                                     | 1.1 / 0 | -         | ns                    |  |

| T <sub>IOSRCKT</sub> /T <sub>IOCKTSR</sub> | 3-state setup times, SR input (TFF)                                | 1.3 / 0 | -         | ns                    |  |

| Set/Reset Delays                           | 1                                                                  |         |           | 1                     |  |

| T <sub>IOSRP</sub>                         | SR input to pad (asynchronous)                                     | 4.6     | -         | ns                    |  |

| T <sub>IOSRHZ</sub>                        | SR input to pad high-impedance (asynchronous) <sup>(1)</sup>       | 3.9     | -         | ns                    |  |

| T <sub>IOSRON</sub>                        | SR input to valid data on pad (asynchronous)                       | 5.1     | -         | ns                    |  |

<sup>1.</sup> High-impedance turn-off delays should not be adjusted.

<sup>2.</sup> A Zero "0" Hold Time listing indicates no hold time or a negative hold time. Negative values can not be guaranteed "best-case", but if a "0" is listed, there is no positive hold time.

# Calculation of $T_{ioop}$ as a Function of Capacitance

The values for  $T_{ioop}$  were based on the standard capacitive load (CsI) for each I/O standard as listed in Table 2.

For other capacitive loads, use the formulas below to calculate the corresponding  $T_{\text{ioop}}$ :

$$T_{ioop} = T_{ioopl} + T_{opadjust} + (C_{load} - C_{sl}) * fl$$

Where:

$T_{opadjust}$  is reported above in the Output Delay Adjustment section.

C<sub>load</sub> is the capacitive load for the design.

Table 2: Constants for Use in Calculation of Top

| Star       | ndard       | C <sub>sl</sub> (pF) | fl (ns/pF) |

|------------|-------------|----------------------|------------|

| LVTTL slow | 2 mA drive  | 35                   | 0.41       |

| slew rate  | 4 mA drive  | 35                   | 0.20       |

|            | 6 mA drive  | 35                   | 0.100      |

|            | 8 mA drive  | 35                   | 0.086      |

|            | 12 mA drive | 35                   | 0.058      |

|            | 16 mA drive | 35                   | 0.050      |

|            | 24 mA drive | 35                   | 0.048      |

| LVTTL fast | 2 mA drive  | 35                   | 0.41       |

| slew rate  | 4 mA drive  | 35                   | 0.20       |

|            | 6 mA drive  | 35                   | 0.13       |

|            | 8 mA drive  | 35                   | 0.079      |

|            | 12 mA drive | 35                   | 0.044      |

|            | 16 mA drive | 35                   | 0.043      |

|            | 24 mA drive | 35                   | 0.033      |

Table 2: Constants for Use in Calculation of Top

| Standard        | C <sub>sl</sub> (pF) | fl (ns/pF) |

|-----------------|----------------------|------------|

| LVCMOS2         | 35                   | 0.041      |

| PCI 33 MHz 5V   | 50                   | 0.050      |

| PCI 33 MHZ 3.3V | 10                   | 0.050      |

| GTL             | 0                    | 0.014      |

| GTL+            | 0                    | 0.017      |

| HSTL Class I    | 20                   | 0.022      |

| HSTL Class III  | 20                   | 0.016      |

| HSTL Class IV   | 20                   | 0.014      |

| SSTL2 Class I   | 30                   | 0.028      |

| SSTL2 Class II  | 30                   | 0.016      |

| SSTL3 Class 1   | 30                   | 0.029      |

| SSTL3 Class II  | 30                   | 0.016      |

| CTT             | 20                   | 0.035      |

| AGP             | 10                   | 0.037      |

### **Clock Distribution Guidelines and Switching Characteristics**

|                       |                                          |          | Speed Grade -4 Min Max |      |       |

|-----------------------|------------------------------------------|----------|------------------------|------|-------|

|                       |                                          |          |                        |      |       |

| Symbol                | Description                              | Device   |                        |      | Units |

| Global Clock S        | kew                                      | <u> </u> |                        | 1    |       |

| T <sub>GSKEWIOB</sub> | Global clock skew between IOB flip-flops | XQV100   | -                      | 0.15 | ns    |

|                       |                                          | XQV300   | -                      | 0.18 | ns    |

|                       |                                          | XQV600   | -                      | 0.17 | ns    |

|                       |                                          | XQV1000  | -                      | 0.25 | ns    |

| $T_{GPIO}$            | Global clock PAD to output               | All      | -                      | 0.9  | ns    |

| $T_{GIO}$             | Global clock buffer I input to O output  | All      | -                      | 0.9  | ns    |

<sup>1.</sup> These clock-distribution delays are provided for guidance only. They reflect the delays encountered in a typical design under worst-case conditions. Precise values for a particular design are provided by the timing analyzer.

## **CLB Switching Characteristics**

Delays originating at F/G inputs vary slightly according to the input used. The values listed below are worst-case. Precise values are provided by the timing analyzer.

|                                          |                                                                      | Speed   | Grade    |          |

|------------------------------------------|----------------------------------------------------------------------|---------|----------|----------|

|                                          | Description                                                          |         | 4        |          |

| Symbol                                   |                                                                      | Min     | Max      | Units    |

| Combinatorial Dela                       | ys                                                                   |         | •        |          |

| T <sub>ILO</sub>                         | 4-input function: F/G inputs to X/Y outputs                          | -       | 0.8      | ns       |

| T <sub>IF5</sub>                         | 5-input function: F/G inputs to F5 output                            | -       | 0.9      | ns       |

| T <sub>IF5X</sub>                        | 5-input function: F/G inputs to X output                             | -       | 1.0      | ns       |

| T <sub>IF6Y</sub>                        | 6-input function: F/G inputs to Y output via F6 MUX                  | -       | 1.2      | ns       |

| T <sub>F5INY</sub>                       | 6-input function: F5IN input to Y output                             | -       | 0.5      | ns       |

| T <sub>IFNCTL</sub>                      | Incremental delay routing through transparent latch to XQ/YQ outputs | -       | 0.8      | ns       |

| T <sub>BYYB</sub>                        | BY input to YB output                                                | -       | 0.7      | ns       |

| Sequential Delays                        |                                                                      | 1       | <u>I</u> |          |

| T <sub>CKO</sub>                         | FF clock CLK to XQ/YQ outputs                                        | -       | 1.4      | ns       |

| T <sub>CKLO</sub>                        | Latch clock CLK to XQ/YQ outputs                                     | -       | 1.6      | ns       |

| Setup and Hold Tim                       | nes before/after Clock CLK                                           | Setup   | Time / H | old Time |

| T <sub>ICK</sub> /T <sub>CKI</sub>       | 4-input function: F/G Inputs                                         | 1.5 / 0 | -        | ns       |

| T <sub>IF5CK</sub> /T <sub>CKIF5</sub>   | 5-input function: F/G inputs                                         | 1.7 / 0 | -        | ns       |

| T <sub>F5INCK</sub> /T <sub>CKF5IN</sub> | 6-input function: F5IN input                                         | 1.2 / 0 | -        | ns       |

| T <sub>IF6CK</sub> /T <sub>CKIF6</sub>   | 6-input function: F/G inputs via F6 MUX                              | 1.9 / 0 | -        | ns       |

| T <sub>DICK</sub> /T <sub>CKDI</sub>     | BX/BY inputs                                                         | 0.8/0   | -        | ns       |

| T <sub>CECK</sub> /T <sub>CKCE</sub>     | CE input                                                             | 1.0 / 0 | -        | ns       |

| $T_{RCK}T_{CKR}$                         | SR/BY inputs (synchronous)                                           | 0.9 / 0 | -        | ns       |

| Clock CLK                                |                                                                      |         |          |          |

| T <sub>CH</sub>                          | Minimum pulse width, High                                            | 2.0     | -        | ns       |

| T <sub>CL</sub>                          | Minimum pulse width, Low                                             | 2.0     | -        | ns       |

| Set/Reset                                | 1                                                                    | 1       | I        |          |

| T <sub>RPW</sub>                         | Minimum pulse width, SR/BY inputs                                    | 3.3     | -        | ns       |

| T <sub>RQ</sub>                          | Delay from SR/BY inputs to XQ/YQ outputs (asynchronous)              | -       | 1.4      | ns       |

| T <sub>IOGSRQ</sub>                      | Delay from GSR to XQ/YQ outputs                                      | -       | 12.5     | ns       |

<sup>1.</sup> A Zero "0" Hold Time listing indicates no hold time or a negative hold time. Negative values can not be guaranteed "best-case", but if a "0" is listed, there is no positive hold time.

### **TBUF Switching Characteristics**

|                   |                                        | Speed Grade -4 Description Min Max |     |       |

|-------------------|----------------------------------------|------------------------------------|-----|-------|

|                   |                                        |                                    |     |       |

| Symbol            | Description                            |                                    |     | Units |

| Combinatorial Del | ays                                    |                                    |     |       |

| T <sub>IO</sub>   | IN input to OUT output                 | -                                  | 0.0 | ns    |

| T <sub>OFF</sub>  | TRI input to OUT output high-impedance | -                                  | 0.2 | ns    |

| T <sub>ON</sub>   | Tri input to valid data on OUT output  | -                                  | 0.2 | ns    |

## **JTAG Test Access Port Switching Characteristics**

|                     |                                           | Speed Grade |      |       |

|---------------------|-------------------------------------------|-------------|------|-------|

|                     |                                           | -           | 4    |       |

| Symbol              | Description                               | Min         | Max  | Units |

| T <sub>TAPTCK</sub> | TMS and TDI setup times before TCK        | 4.0         | -    | ns    |

| T <sub>TCKTAP</sub> | TMS and TDI hold times after TCK          | 2.0         | -    | ns    |

| T <sub>TCKTDO</sub> | Output delay from clock TCK to output TDO | -           | 11.0 | ns    |

| F <sub>TCK</sub>    | Maximum TCK clock frequency               | -           | 33   | MHz   |

## **Virtex Pin-to-Pin Output Parameter Guidelines**

Testing of switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100% functionally tested. Listed below are representative

values for typical pin locations and normal clock loading. Values are expressed in nanoseconds unless otherwise noted.

## Global Clock Input to Output Delay for LVTTL, 12 mA, Fast Slew Rate, with DLL

|                 |                                                                                                                              |         | Speed Grade<br>-4 |     |       |

|-----------------|------------------------------------------------------------------------------------------------------------------------------|---------|-------------------|-----|-------|

|                 |                                                                                                                              |         |                   |     |       |

| Symbol          | Description                                                                                                                  | Device  | Min               | Max | Units |

|                 | LVTTL Global Clock Input to Output Delay using Output Flip-flop,                                                             | XQV100  | -                 | 3.6 | ns    |

|                 | 12 mA, Fast Slew Rate, <i>with</i> DLL. For data <i>output</i> with different                                                | XQV300  | -                 | 3.6 | ns    |

|                 | standards, adjust the delays with the values shown in "IOB Output Switching Characteristics Standard Adjustments" on page 8. | XQV600  | -                 | 3.6 | ns    |

| - Cwitoming one | omening of a action on our page of                                                                                           | XQV1000 | -                 | 3.6 | ns    |

#### Notes:

- Listed above are representative values where one global clock input drives one vertical clock line in each accessible column, and where all accessible IOB and CLB flip-flops are clocked by the global clock net.

- 2. Output timing is measured at 50%  $V_{CC}$  threshold with 35 pF external capacitive load. For different loads, see Table 2.

- 3. DLL output jitter is already included in the timing calculation.

### Global Clock Input to Output Delay for LVTTL, 12 mA, Fast Slew Rate, without DLL

|        |                                                                                                                              |         | Speed Grade<br>-4 |     |       |

|--------|------------------------------------------------------------------------------------------------------------------------------|---------|-------------------|-----|-------|

|        |                                                                                                                              |         |                   |     |       |

| Symbol | Description                                                                                                                  | Device  | Min               | Max | Units |

|        | LVTTL Global Clock Input to Output Delay using Output Flip-flop,                                                             | XQV100  | -                 | 5.7 | ns    |

|        | 12 mA, Fast Slew Rate, <i>without</i> DLL. For data <i>output</i> with different                                             | XQV300  | -                 | 5.9 | ns    |

|        | standards, adjust the delays with the values shown in "IOB Output Switching Characteristics Standard Adjustments" on page 8. | XQV600  | -                 | 6.0 | ns    |

| Í      | Switching Characteristics Standard Adjustments on page 6.                                                                    | XQV1000 | -                 | 6.3 | ns    |

- Listed above are representative values where one global clock input drives one vertical clock line in each accessible column, and where all accessible IOB and CLB flip-flops are clocked by the global clock net.

- 2. Output timing is measured at 50%  $V_{CC}$  threshold with 35 pF external capacitive load. For different loads, see Table 2.

### **Minimum Clock to Out for Virtex Devices**

|                          | With DLL    |      |      | Without DLI | _     |       |

|--------------------------|-------------|------|------|-------------|-------|-------|

| I/O Standard             | All Devices | V100 | V300 | V600        | V1000 | Units |

| LVTTL_S2 <sup>(1)</sup>  | 5.2         | 6.0  | 6.1  | 6.1         | 6.1   | ns    |

| LVTTL_S4 <sup>(1)</sup>  | 3.5         | 4.3  | 4.4  | 4.4         | 4.4   | ns    |

| LVTTL_S6 <sup>(1)</sup>  | 2.8         | 3.6  | 3.7  | 3.7         | 3.7   | ns    |

| LVTTL_S8 <sup>(1)</sup>  | 2.2         | 3.1  | 3.1  | 3.2         | 3.2   | ns    |

| LVTTL_S12 <sup>(1)</sup> | 2.0         | 2.9  | 2.9  | 3.0         | 3.0   | ns    |

| LVTTL_S16 <sup>(1)</sup> | 1.9         | 2.8  | 2.8  | 2.9         | 2.9   | ns    |

| LVTTL_S24 <sup>(1)</sup> | 1.8         | 2.6  | 2.7  | 2.7         | 2.8   | ns    |

| LVTTL_F2 <sup>(1)</sup>  | 2.9         | 3.8  | 3.8  | 3.9         | 3.9   | ns    |

| LVTTL_F4 <sup>(1)</sup>  | 1.7         | 2.6  | 2.6  | 2.7         | 2.7   | ns    |

| LVTTL_F6 <sup>(1)</sup>  | 1.2         | 2.0  | 2.1  | 2.1         | 2.2   | ns    |

| LVTTL_F8 <sup>(1)</sup>  | 1.1         | 1.9  | 2.0  | 2.0         | 2.0   | ns    |

| LVTTL_F12 <sup>(1)</sup> | 1.0         | 1.8  | 1.9  | 1.9         | 1.9   | ns    |

| LVTTL_F16 <sup>(1)</sup> | 0.9         | 1.8  | 1.8  | 1.8         | 1.9   | ns    |

| LVTTL_F24 <sup>(1)</sup> | 0.9         | 1.7  | 1.8  | 1.8         | 1.9   | ns    |

| LVCMOS2                  | 1.1         | 1.9  | 2.0  | 2.0         | 2.1   | ns    |

| PCI33_3                  | 1.5         | 2.4  | 2.4  | 2.5         | 2.5   | ns    |

| PCl33_5                  | 1.4         | 2.2  | 2.3  | 2.3         | 2.4   | ns    |

| GTL                      | 1.6         | 2.5  | 2.5  | 2.6         | 2.6   | ns    |

| GTL+                     | 1.7         | 2.5  | 2.6  | 2.6         | 2.7   | ns    |

| HSTL I                   | 1.1         | 1.9  | 2.0  | 2.0         | 2.0   | ns    |

| HSTL III                 | 0.9         | 1.7  | 1.8  | 1.8         | 1.9   | ns    |

| HSTL IV                  | 0.8         | 1.6  | 1.7  | 1.7         | 1.8   | ns    |

| SSTL2 I                  | 0.9         | 1.7  | 1.8  | 1.8         | 1.8   | ns    |

| SSTL2 II                 | 0.8         | 1.6  | 1.7  | 1.7         | 1.7   | ns    |

| SSTL3 I                  | 0.8         | 1.7  | 1.7  | 1.7         | 1.8   | ns    |

| SSTL3 II                 | 0.7         | 1.5  | 1.6  | 1.6         | 1.7   | ns    |

| CTT                      | 1.0         | 1.8  | 1.9  | 1.9         | 2.0   | ns    |

| AGP                      | 1.0         | 1.8  | 1.9  | 1.9         | 2.0   | ns    |

- S = Slow Slew Rate, F = Fast Slew Rate

- Listed above are representative values where one global clock input drives one vertical clock line in each accessible column. and where all accessible IOB and CLB flip-flops are clocked by the global clock net.

Output timing is measured at 50% V<sub>CC</sub> threshold with 8 pF external capacitive load.

## **Virtex Pin-to-Pin Input Parameter Guidelines**

Testing of switching parameters is modeled after testing methods specified by MIL-M-38510/605. All devices are 100% functionally tested. Listed below are representative

values for typical pin locations and normal clock loading. Values are expressed in nanoseconds unless otherwise noted

### Global Clock Setup and Hold for LVTTL Standard, with DLL

|                       |                                                                                                         |                   | Speed G       | rade         |       |

|-----------------------|---------------------------------------------------------------------------------------------------------|-------------------|---------------|--------------|-------|

|                       |                                                                                                         |                   | -4<br>Min Max |              |       |

| Symbol                | Description                                                                                             | Device            |               |              | Units |

| standards, adjust th  | Id Time Relative to Global Clock Input Signal for L\ e setup time delay by the values shown in Input De | elay Adjustments. | 2.1 / –0.4    | rith differe |       |

| $T_{PSDLL}/T_{PHDLL}$ | No Delay                                                                                                | XQV100            | 2.17-0.4      | -            | ns    |

|                       | Global clock and IFF, with DLL                                                                          | XQV300            | 2.1 / -0.4    | -            | ns    |

|                       |                                                                                                         | XQV600            | 2.1 / -0.4    | -            | ns    |

|                       |                                                                                                         | XQV1000           | 2.1 / -0.4    | -            | ns    |

#### Notes:

- 1. IFF = Input Flip-Flop or Latch

- 2. Setup time is measured relative to the Global Clock input signal with the fastest route and the lightest load. Hold time is measured relative to the Global Clock input signal with the slowest route and heaviest load.

- 3. DLL output jitter is already included in the timing calculation.

## Global Clock Setup and Hold for LVTTL Standard, without DLL

|                                      |                                                                                                               |              |               |              | Speed G | irade |  |

|--------------------------------------|---------------------------------------------------------------------------------------------------------------|--------------|---------------|--------------|---------|-------|--|

|                                      |                                                                                                               |              | -4<br>Min Max |              |         |       |  |

| Symbol                               | Description                                                                                                   | Device       |               |              | Units   |       |  |

| standards, adjust th                 | Id Time Relative to Global Clock Input Signal for LVTTI e setup time delay by the values shown in Input Delay | Adjustments. |               | vith differe |         |       |  |

| T <sub>PSFD</sub> /T <sub>PHFD</sub> | Full Delay                                                                                                    | XQV100       | 3.0 / 0.0     | -            | ns      |       |  |

|                                      | Global clock and IFF, without DLL                                                                             | XQV300       | 3.1 / 0.0     | -            | ns      |       |  |

|                                      |                                                                                                               | XQV600       | 3.3 / 0.0     | -            | ns      |       |  |

|                                      |                                                                                                               | XQV1000      | 3.6 / 0.0     | -            | ns      |       |  |

- 1. IFF = Input Flip-Flop or Latch

- 2. Setup time is measured relative to the Global Clock input signal with the fastest route and the lightest load. Hold time is measured relative to the Global Clock input signal with the slowest route and heaviest load.

- 3. A Zero "0" Hold Time listing indicates no hold time or a negative hold time. Negative values can not be guaranteed "best-case", but if a "0" is listed, there is no positive hold time.

### **DLL Timing Parameters**

Switching parameters testing is modeled after testing methods specified by MIL-M-38510/605; all devices are 100 percent functionally tested. Because of the difficulty in directly measuring many internal timing parameters, those parame-

ters are derived from benchmark timing patterns. The following guidelines reflect worst-case values across the recommended operating conditions.

|                      |                                    | Speed Grade -4 |     |       |

|----------------------|------------------------------------|----------------|-----|-------|

| Symbol               | Description                        | Min            | Max | Units |

| F <sub>CLKINHF</sub> | Input clock frequency (CLKDLLHF)   | 60             | 180 | MHz   |

| F <sub>CLKINLF</sub> | Inputclock frequency (CLKDLL)      | 25             | 90  | MHz   |

| T <sub>DLLPWHF</sub> | Input clock pulse width (CLKDLLHF) | 2.4            | -   | ns    |

| T <sub>DLLPWLF</sub> | Input clock pulse width (CLKDLL)   | 3.0            | -   | ns    |

#### Notes:

1. All specifications correspond to Commercial Operating Temperatures (0°C to +100°C).

|                     |                                          |           | CLKE | LLHF | CLKDLL |      |       |

|---------------------|------------------------------------------|-----------|------|------|--------|------|-------|

| Symbol              | Description                              |           | Min  | Max  | Min    | Max  | Units |

| T <sub>IPTOL</sub>  | Input clock period tolerance             |           | -    | 1.0  | -      | 1.0  | ns    |

| T <sub>IJITCC</sub> | Input clock jitter cycle to cycle        |           | -    | ±150 | -      | ±300 | ps    |

| T <sub>LOCK</sub>   | Time required for DLL to acquire Lock    |           |      |      |        |      |       |

|                     | F <sub>CLKIN</sub>                       | > 60 MHz  | -    | 20   | -      | 20   | μs    |

|                     |                                          | 50-60 MHz | -    | -    | -      | 25   | μs    |

|                     |                                          | 40-50 MHz | -    | -    | -      | 50   | μs    |

|                     |                                          | 30-40 MHz | -    | -    | -      | 90   | μs    |

|                     |                                          | 25-30 MHz | -    | -    | -      | 120  | μs    |

| T <sub>SKEW</sub>   | DLL output skew (between any DLL output) |           | -    | ±150 | -      | ±150 | ps    |

| T <sub>OPHASE</sub> | DLL output long term phase differential  |           | -    | ±100 | -      | ±100 | ps    |

| T <sub>OJITCC</sub> | DLL output ditter cycle to cycle         |           | -    | ±60  | 1      | ±60  | ps    |

#### Notes:

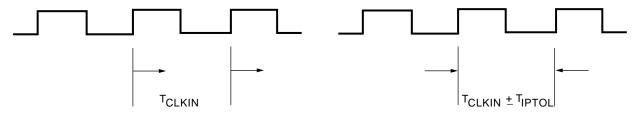

Period Tolerance: the allowed input clock period change in nanoseconds.

Clock Jitter: the difference between an ideal reference clock edgfe and the actual design.

Figure 1: Frequency Tolerance and Clock Jitter

All specifications correspond to Commercial Operating Temperatures (0°C to +100°C).

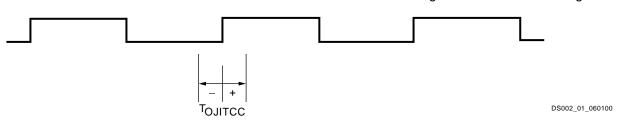

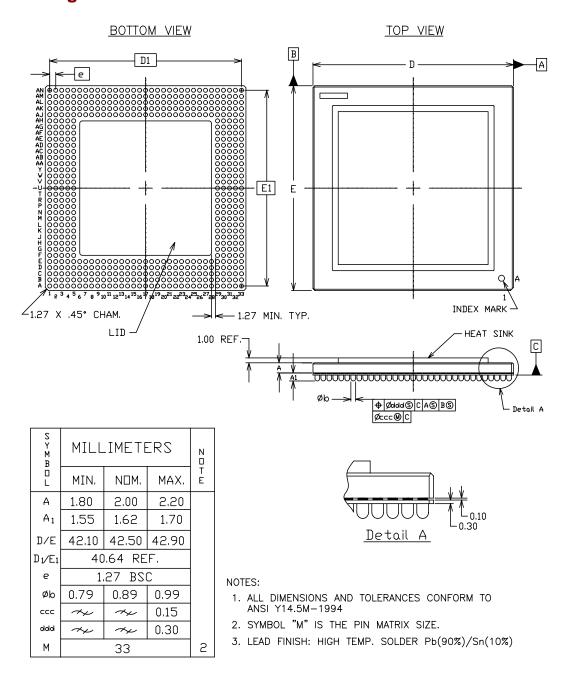

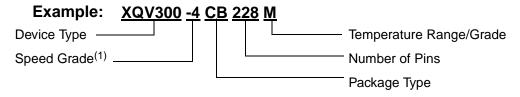

## **QPro Virtex Pinouts**

### **Pinout Tables**

See the Xilinx WebLINX web site (<a href="http://www.xilinx.com/partinfo/databook.htm">http://www.xilinx.com/partinfo/databook.htm</a>) for updates or additional pinout information. For convenience, Table 3, Table 4 and

Table 5 list the locations of special-purpose and power-supply pins. Pins not listed are user I/Os.

Table 3: Virtex QFP Package Pinout Information

| Pin Name                                                                                                                                                                                              | Device | PQ/HQ240                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|--------------------------------------------------------------------------------|

| GCK0                                                                                                                                                                                                  | All    | 92                                                                             |

| GCK1                                                                                                                                                                                                  | All    | 89                                                                             |

| GCK2                                                                                                                                                                                                  | All    | 210                                                                            |

| GCK3                                                                                                                                                                                                  | All    | 213                                                                            |

| M0                                                                                                                                                                                                    | All    | 60                                                                             |

| M1                                                                                                                                                                                                    | All    | 58                                                                             |

| M2                                                                                                                                                                                                    | All    | 62                                                                             |

| CCLK                                                                                                                                                                                                  | All    | 179                                                                            |

| PROGRAM                                                                                                                                                                                               | All    | 122                                                                            |

| DONE                                                                                                                                                                                                  | All    | 120                                                                            |

| INIT                                                                                                                                                                                                  | All    | 123                                                                            |

| BUSY/DOUT                                                                                                                                                                                             | All    | 178                                                                            |

| D0/DIN                                                                                                                                                                                                | All    | 177                                                                            |

| D1                                                                                                                                                                                                    | All    | 167                                                                            |

| D2                                                                                                                                                                                                    | All    | 163                                                                            |

| D3                                                                                                                                                                                                    | All    | 156                                                                            |

| D4                                                                                                                                                                                                    | All    | 145                                                                            |

| D5                                                                                                                                                                                                    | All    | 138                                                                            |

| D6                                                                                                                                                                                                    | All    | 134                                                                            |

| D7                                                                                                                                                                                                    | All    | 124                                                                            |

| WRITE                                                                                                                                                                                                 | All    | 185                                                                            |

| CS                                                                                                                                                                                                    | All    | 184                                                                            |

| TDI                                                                                                                                                                                                   | All    | 183                                                                            |

| TDO                                                                                                                                                                                                   | All    | 181                                                                            |

| TMS                                                                                                                                                                                                   | All    | 2                                                                              |

| TCK                                                                                                                                                                                                   | All    | 239                                                                            |

| V <sub>CCINT</sub>                                                                                                                                                                                    | All    | 16, 32, 43, 77, 88, 104,<br>137, 148, 164, 198, 214,<br>225                    |

| $V_{\rm CCO}$ (The $V_{\rm CCO}$ for the PQ/HQ240 package is common to all eight I/O banks. Different output standards per I/O bank that require different $V_{\rm CCO}$ values cannot be supported.) | All    | 15, 30, 44, 61, 76, 90,<br>105, 121, 136, 150, 165,<br>180, 197, 212, 226, 240 |

## Table 3: Virtex QFP Package Pinout Information (Continued)

| Pin Name                                                                                                 | Device | PQ/HQ240 |

|----------------------------------------------------------------------------------------------------------|--------|----------|

| V <sub>REF</sub> Bank 0                                                                                  | XQV100 | + 229    |

| (V <sub>REF</sub> pins are listed incrementally. Connect all pins listed for both                        | XQV300 | + 236    |

| the required device and all smaller devices listed in the same package.)                                 | XQV600 | + 230    |

| Within each bank, if input reference voltage is not required, all $V_{\text{REF}}$ pins are general I/O. |        |          |

| V <sub>REF</sub> Bank 1                                                                                  | XQV100 | + 194    |

| (V <sub>REF</sub> pins are listed incrementally. Connect all pins listed for both                        | XQV300 | + 187    |

| the required device and all smaller devices listed in the same package.)                                 | XQV600 | + 193    |

| Within each bank, if input reference voltage is not required, all $V_{\text{REF}}$ pins are general I/O. |        |          |

| V <sub>REF</sub> Bank 2                                                                                  | XQV100 | + 168    |

| (V <sub>REF</sub> pins are listed incrementally. Connect all pins listed for both                        | XQV300 | + 175    |

| the required device and all smaller devices listed in the same package.)                                 | XQV600 | + 169    |

| Within each bank, if input reference voltage is not required, all $V_{\text{REF}}$ pins are general I/O. |        |          |

| V <sub>REF</sub> Bank 3                                                                                  | XQV100 | + 133    |

| (V <sub>REF</sub> pins are listed incrementally. Connect all pins listed for both                        | XQV300 | + 126    |

| the required device and all smaller devices listed in the same package.)                                 | XQV600 | + 132    |

| Within each bank, if input reference voltage is not required, all $V_{\text{REF}}$ pins are general I/O. |        |          |

| V <sub>REF</sub> Bank 4                                                                                  | XQV100 | + 108    |

| (V <sub>REF</sub> pins are listed incrementally. Connect all pins listed for both                        | XQV300 | + 115    |

| the required device and all smaller devices listed in the same package.)                                 | XQV600 | + 109    |

| Within each bank, if input reference voltage is not required, all $V_{\text{REF}}$ pins are general I/O. |        |          |

| V <sub>REF</sub> Bank 5                                                                                  | XQV100 | + 73     |

| (V <sub>REF</sub> pins are listed incrementally. Connect all pins listed for both                        | XQV300 | + 66     |

| the required device and all smaller devices listed in the same package.)                                 | XQV600 | + 72     |

| Within each bank, if input reference voltage is not required, all $V_{\text{REF}}$ pins are general I/O. |        |          |

| V <sub>REF</sub> Bank 6                                                                                  | XQV100 | + 47     |

| (V <sub>REF</sub> pins are listed incrementally. Connect all pins listed for both                        | XQV300 | + 54     |

| the required device and all smaller devices listed in the same package.)                                 | XQV600 | + 48     |

| Within each bank, if input reference voltage is not required, all $V_{REF}$ pins are general I/O.        |        |          |

Table 4: Virtex Plastic Ball Grid and Ceramic Column Grid Pinout Information (Continued)

| Pin Name                                                                                                 | Device  | BG256         | BG352                 | BG432                 | BG560/CG560                                   |

|----------------------------------------------------------------------------------------------------------|---------|---------------|-----------------------|-----------------------|-----------------------------------------------|

| V <sub>REF</sub> Bank 0                                                                                  | XQV100  | A4, A8, B4    | -                     | -                     | -                                             |

| (VREF pins are listed incrementally. Connect all pins listed for both the                                | XQV300  | -             | A16, C19,<br>C21, D21 | B19, D22, D24,<br>D26 | -                                             |

| required device and all smaller devices listed in the same package.)                                     | XQV600  | -             | -                     | + C18, C24            | -                                             |

| Within each bank, if input reference voltage is not required, all V <sub>REF</sub> pins are general I/O. | XQV1000 | -             | -                     | -                     | A19, D20, D26,<br>D29, E21, E23,<br>E24, E27, |

| V <sub>REF</sub> Bank 1                                                                                  | XQV100  | A17, B12,     | -                     | -                     | -                                             |

| (VREF pins are listed incrementally.                                                                     |         | B15           |                       |                       |                                               |

| Connect all pins listed for both the required device and all smaller                                     | XQV300  | -             | B6, C9, C12,<br>D6    | A13, B7, C6,<br>C10   | -                                             |

| devices listed in the same package.)                                                                     | XQV600  | -             | -                     | + B15, D10            | -                                             |

| Within each bank, if input reference voltage is not required, all V <sub>REF</sub> pins are general I/O. | XQV1000 | -             | -                     | -                     | A6, D7, D10,<br>D11, D13, D16,<br>E7, E15     |

| V <sub>REF</sub> Bank 2                                                                                  | XQV100  | C20, F19, J18 | -                     | -                     | -                                             |

| (V <sub>REF</sub> pins are listed incrementally.<br>Connect all pins listed for both the                 | XQV300  | -             | D2, E2, H2,<br>M4     | E2, G3, J2, N1        | -                                             |

| required device and all smaller devices listed in the same package.)                                     | XQV600  | -             | -                     | + H1, R3              | -                                             |

| Within each bank, if input reference voltage is not required, all V <sub>REF</sub> pins are general I/O. | XQV1000 | -             | -                     | -                     | B3, G5, H4, K5,<br>L5, N5, P4, R1             |

| V <sub>REF</sub> Bank 3                                                                                  | XQV100  | M18, R19,     | -                     | -                     | -                                             |

| (V <sub>REF</sub> pins are listed incrementally.                                                         |         | V20           |                       |                       |                                               |

| Connect all pins listed for both the required device and all smaller                                     | XQV300  | -             | R4, V4, Y3,<br>AC2    | V2, AB4, AD4,<br>AF3  | -                                             |

| devices listed in the same package.)                                                                     | XQV600  | -             | -                     | + U2, AC3             | -                                             |

| Within each bank, if input reference voltage is not required, all V <sub>REF</sub> pins are general I/O. | XQV1000 | -             | -                     | -                     | V4, W5, AA4,<br>AD3, AE5, AF1,<br>AH4, AK2    |

Table 4: Virtex Plastic Ball Grid and Ceramic Column Grid Pinout Information (Continued)

| Pin Name                                                                                                 | Device  | BG256            | BG352                     | BG432                     | BG560/CG560                                             |

|----------------------------------------------------------------------------------------------------------|---------|------------------|---------------------------|---------------------------|---------------------------------------------------------|

| V <sub>REF</sub> Bank 4 (V <sub>RFF</sub> pins are listed incrementally.                                 | XQV100  | V12, W15,<br>Y18 | -                         | -                         | -                                                       |

| Connect all pins listed for both the required device and all smaller                                     | XQV300  | -                | AC12, AE4,<br>AE5, AE8    | AJ7, AL4, AL8,<br>AL13    | -                                                       |

| devices listed in the same package.)                                                                     | XQV600  | -                | -                         | + AK8, AK15               | -                                                       |

| Within each bank, if input reference voltage is not required, all V <sub>REF</sub> pins are general I/O. | XQV1000 | -                | -                         | -                         | AK13, AL7, AL9,<br>AL10, AL16,<br>AM4, AM14,AN3         |

| V <sub>REF</sub> Bank 5                                                                                  | XQV100  | V9, W6, Y3       | -                         | -                         | -                                                       |

| (V <sub>REF</sub> pins are listed incrementally.<br>Connect all pins listed for both the                 | XQV300  | -                | AC15, AC18,<br>AD20, AE23 | AJ18, AJ25,<br>AK23, AK27 | -                                                       |

| required device and all smaller devices listed in the same package.)                                     | XQV600  | -                | -                         | + AJ17,<br>AL24           | -                                                       |

| Within each bank, if input reference voltage is not required, all V <sub>REF</sub> pins are general I/O. | XQV1000 | -                | -                         | -                         | AJ18, AJ25,<br>AK28, AL20,<br>AL24, AL29,<br>AM26, AN23 |

| V <sub>REF</sub> Bank 6                                                                                  | XQV100  | M2, R3, T1       | -                         | -                         | -                                                       |

| (V <sub>REF</sub> pins are listed incrementally.<br>Connect all pins listed for both the                 | XQV300  | -                | R24, Y26,<br>AA25, AD26   | V28, AB28,<br>AE30, AF28  | -                                                       |

| required device and all smaller devices listed in the same package.)                                     | XQV600  | -                | -                         | + U28, AC28               | -                                                       |

| Within each bank, if input reference voltage is not required, all V <sub>REF</sub> pins are general I/O. | XQV1000 | -                | -                         | -                         | V29, Y32,<br>AA30,AD31,<br>AE29, AK32,<br>AE31, AH30    |

| V <sub>REF</sub> Bank 7                                                                                  | XQV100  | D1, G3, H1       | -                         | -                         | -                                                       |

| (V <sub>REF</sub> pins are listed incrementally.<br>Connect all pins listed for both the                 | XQV300  | -                | D26, E24,<br>G26, L26     | F28, F31, J30,<br>N30     | -                                                       |

| required device and all smaller devices listed in the same package.)                                     | XQV600  | -                | -                         | + J28, R31                | -                                                       |

| Within each bank, if input reference voltage is not required, all V <sub>REF</sub> pins are general I/O. | XQV1000 | -                | -                         | -                         | D31, E31, G31,<br>H32, K31, P31,<br>T31, L33            |

Table 4: Virtex Plastic Ball Grid and Ceramic Column Grid Pinout Information (Continued)

| Pin Name           | Device | BG256                                                                                                                                                     | BG352                                                                                                                                                                                               | BG432                                                                                                                                                                                                                                          | BG560/CG560                                                                                                                                                                                                                                                                                                                                                                  |

|--------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GND                | All    | C3, C18, D4, D5, D9, D10, D11, D12, D16, D17, E4, E17, J4, J17, K4, K17, L4, L17, M4, M9, M10, M17, T4, T17, U4, U5, U9, U10, U11, U12, U16, U17, V3, V18 | A1, A2, A5,<br>A8, A14, A19,<br>A22, A25,<br>A26, B1, B26,<br>E1, E26, H1,<br>H26, N1, P26,<br>W1, W26,<br>AB1, AB26,<br>AE1, AE26,<br>AF1, AF2,<br>AF5, AF8,<br>AF13, AF19,<br>AF22, AF25,<br>AF26 | A2, A3, A7, A9, A14, A18, A23, A25, A29, A30, B1, B2, B30, B31, C1, C31, D16, G1, G31, J1, J31, P1, P31, T4, T28, V1, V31, AC1, AC31, AE1, AE31, AH16, AJ1, AJ31, AK1, AK2, AK30, AK31, AL2, AL3, AL7, AL9, AL14, AL18, AL23, AL25, AL29, AL30 | A1, A7, A12, A14,<br>A18, A20, A24,<br>A29, A32, A33,<br>B1, B6, B9, B15,<br>B23, B27, B31,<br>C2, E1, F32, G2,<br>G33, J32, K1, L2,<br>M33, P1, P33,<br>R32, T1, V33,<br>W2, Y1, Y33,<br>AB1, AC32,<br>AD33, AE2, AG1,<br>AG32, AH2,<br>AJ33, AL32,<br>AM3, AM7,<br>AM11, AM19,<br>AM25, AM28,<br>AM33, AN1, AN2,<br>AN5, AN10,<br>AN14, AN16,<br>AN20, AN22,<br>AN27, AN33 |

| GND <sup>(1)</sup> | All    | J9, J10, J11,<br>J12, K9, K10,<br>K11, K12, L9,<br>L10, L11,<br>L12, M9,<br>M10,<br>M11,M12                                                               | -                                                                                                                                                                                                   | -                                                                                                                                                                                                                                              | -                                                                                                                                                                                                                                                                                                                                                                            |

| No Connect         | -      | -                                                                                                                                                         | -                                                                                                                                                                                                   | -                                                                                                                                                                                                                                              | C31, AC2, AK4,<br>AL3                                                                                                                                                                                                                                                                                                                                                        |

#### Notes:

1. 16 extra balls (grounded) at package center.

Table 5: CQFP Package (CB228) (Continued)

| Fame 1's as  | 1       |

|--------------|---------|

| Function     | Pin No. |

| IO_VREF_2    | 159     |

| IO           | 160     |

| IO           | 161     |

| IO_VREF_2    | 162     |

| GND          | 163     |

| IO           | 164     |

| IO           | 165     |

| IO_VREF_2    | 166     |

| IO           | 167     |

| IO_DIN_D0    | 168     |

| IO_DOUT_BUSY | 169     |

| CCLK         | 170     |

| VCCO         | 171     |

| TDO          | 172     |

| GND          | 173     |

| TDI          | 174     |

| IO_CS        | 175     |

| IO_WRITE     | 176     |

| IO           | 177     |