Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Product Status          | Obsolete                                                                       |

|-------------------------|--------------------------------------------------------------------------------|

| Туре                    | SC3850 Quad Core                                                               |

| Interface               | Ethernet, I <sup>2</sup> C, PCI, RGMII, Serial RapidIO, SGMII, SPI, UART/USART |

| Clock Rate              | 1GHz                                                                           |

| Non-Volatile Memory     | ROM (96kB)                                                                     |

| On-Chip RAM             | 576kB                                                                          |

| Voltage - I/O           | 2.50V                                                                          |

| Voltage - Core          | 1.00V                                                                          |

| Operating Temperature   | -40°C ~ 105°C (TJ)                                                             |

| Mounting Type           | Surface Mount                                                                  |

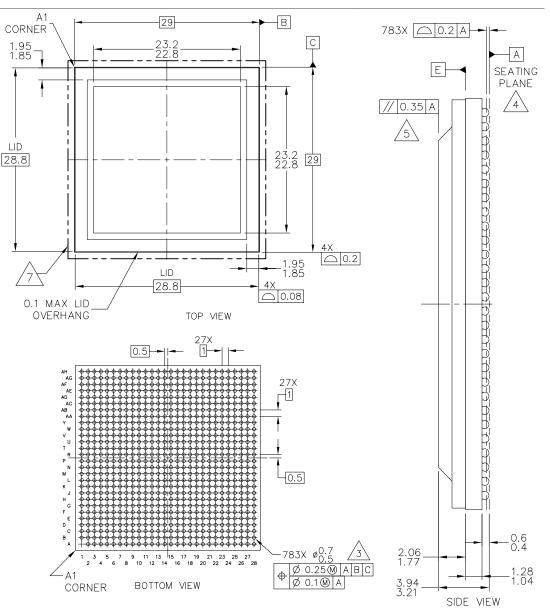

| Package / Case          | 783-BBGA, FCBGA                                                                |

| Supplier Device Package | 783-FCPBGA (29x29)                                                             |

| Purchase URL            | https://www.e-xfl.com/product-detail/nxp-semiconductors/msc8154tag1000b        |

|                         |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Ball Number | Signal Name <sup>1,2</sup>   | Pin Type <sup>10</sup> | Power Rail<br>Name |  |

|-------------|------------------------------|------------------------|--------------------|--|

| E17         | M2DQ56                       | I/O                    | GVDD2              |  |

| E18         | M2DQ57                       | I/O                    | GVDD2              |  |

| E19         | M2DQS7                       | I/O                    | GVDD2              |  |

| E20         | Reserved                     | NC                     | _                  |  |

| E21         | Reserved                     | NC                     | _                  |  |

| E22         | Reserved                     | NC                     |                    |  |

| E23         | SXPVDD1                      | Power                  | N/A                |  |

| E24         | SXPVSS1                      | Ground                 | N/A                |  |

| E25         | SR1_PLL_AGND <sup>9</sup>    | Ground                 | SXCVSS1            |  |

| E26         | SR1_PLL_AVDD <sup>9</sup>    | Power                  | SXCVDD1            |  |

| E27         | SXCVSS1                      | Ground                 | N/A                |  |

| E28         | SXCVDD1                      | Power                  | N/A                |  |

| F1          | VSS                          | Ground                 | N/A                |  |

| F2          | GVDD2                        | Power                  | N/A                |  |

| F3          | M2DQ16                       | I/O                    | GVDD2              |  |

| F4          | VSS                          | Ground                 | N/A                |  |

| F5          | GVDD2                        | Power                  | N/A                |  |

| F6          | M2DQ17                       | I/O                    | GVDD2              |  |

| F7          | VSS                          | Ground                 | N/A                |  |

| F8          | GVDD2                        | Power                  | N/A                |  |

| F9          | M2BA2                        | 0                      | GVDD2              |  |

| F10         | VSS                          | Ground                 | N/A                |  |

| F11         | GVDD2                        | Power                  | N/A                |  |

| F12         | M2A4                         | 0                      | GVDD2              |  |

| F13         | VSS                          | Ground                 | N/A                |  |

| F14         | GVDD2                        | Power                  | N/A                |  |

| F15         | M2DQ42                       | I/O                    | GVDD2              |  |

| F16         | VSS                          | Ground                 | N/A                |  |

| F17         | GVDD2                        | Power                  | N/A                |  |

| F18         | M2DQ58                       | I/O                    | GVDD2              |  |

| F19         | M2DQS7                       | I/O                    | GVDD2              |  |

| F20         | GVDD2                        | Power                  | N/A                |  |

| F21         | SXPVDD1                      | Power                  | N/A                |  |

| F22         | SXPVSS1                      | Ground                 | N/A                |  |

| F23         | SR1_TXD2/SG1_TX <sup>4</sup> | 0                      | SXPVDD1            |  |

| F24         | SR1_TXD2/SG1_TX <sup>4</sup> | 0                      | SXPVDD1            |  |

| F25         | SXCVDD1                      | Power                  | N/A                |  |

| F26         | SXCVSS1                      | Ground                 | N/A                |  |

| F27         | SR1_RXD2/SG1_RX <sup>4</sup> |                        | SXCVDD1            |  |

| F28         | SR1_RXD2/SG1_RX <sup>4</sup> |                        | SXCVDD1            |  |

| G1          | M2DQS2                       | I/O                    | GVDD2              |  |

| G2          | M2DQS2                       | I/O                    | GVDD2<br>GVDD2     |  |

| G3          | M2DQ32<br>M2DQ19             | I/O                    | GVDD2<br>GVDD2     |  |

| G3<br>G4    | M2DQ19<br>M2DM2              | 0                      | GVDD2<br>GVDD2     |  |

| G5          | M2DQ21                       | U                      | GVDD2<br>GVDD2     |  |

| 00          | M2DQ21<br>M2DQ22             | I/O                    | GVDD2<br>GVDD2     |  |

| Ball Number | Signal Name <sup>1,2</sup> | Pin Type <sup>10</sup> | Power Rail<br>Name |  |

|-------------|----------------------------|------------------------|--------------------|--|

| M5          | M2DQ1                      | I/O                    | GVDD2              |  |

| M6          | VSS                        | Ground                 | N/.A               |  |

| M7          | GVDD2                      | Power                  | N/A                |  |

| M8          | M2DQ7                      | I/O                    | GVDD2              |  |

| M9          | M2DQ6                      | I/O                    | GVDD2              |  |

| M10         | VSS                        | Ground                 | N/A                |  |

| M11         | VDD                        | Power                  | N/A                |  |

| M12         | VSS                        | Ground                 | N/A                |  |

| M13         | VDD                        | Power                  | N/A                |  |

| M14         | VSS                        | Ground                 | N/A                |  |

| M15         | VSS                        | Ground                 | N/A                |  |

| M16         | VSS                        | Ground                 | N/A                |  |

| M17         | VSS                        | Ground                 | N/A                |  |

| M18         | VSS                        | Ground                 | N/A                |  |

| M19         | VDD                        | Power                  | N/A                |  |

| M20         | Reserved                   | NC                     | _                  |  |

| M21         | Reserved                   | NC                     | _                  |  |

| M22         | Reserved                   | NC                     | _                  |  |

| M23         | SXPVSS2                    | Ground                 | N/A                |  |

| M24         | SXPVDD2                    | Power                  | N/A                |  |

| M25         | SR2_IMP_CAL_TX             |                        | SXCVDD2            |  |

| M26         | SXCVSS2                    | Ground                 | N/A                |  |

| M27         | Reserved                   | NC                     | _                  |  |

| M28         | Reserved                   | NC                     | _                  |  |

| N1          | VSS                        | Ground                 | N/A                |  |

| N2          | TRST <sup>7</sup>          |                        | QVDD               |  |

| N3          | PORESET <sup>7</sup>       | I                      | QVDD               |  |

| N4          | VSS                        | Ground                 | N/A                |  |

| N5          | TMS <sup>7</sup>           |                        | QVDD               |  |

| N6          | CLKOUT                     | 0                      | QVDD               |  |

| N7          | VSS                        | Ground                 | N/A                |  |

| N8          | VSS                        | Ground                 | N/A                |  |

| N9          | VSS                        | Ground                 | N/A                |  |

| N10         | VDD                        | Power                  | N/A                |  |

| N11         | VSS                        | Ground                 | N/A                |  |

| N12         | M3VDD                      | Power                  | N/A                |  |

| N13         | VSS                        | Ground                 | N/A                |  |

| N14         | VSS                        | Ground                 | N/A                |  |

| N15         | VSS                        | Ground                 | N/A                |  |

| N16         | VDD                        | Power                  | N/A                |  |

| N17         | VSS                        | Ground                 | N/A                |  |

| N18         | VDD                        | Power                  | N/A                |  |

| N19         | VSS                        | Ground                 | N/A                |  |

| N20         | Reserved                   | NC                     |                    |  |

| N21         | SXPVDD2                    | Power                  | N/A                |  |

| N22         | SXPVSS2                    | Ground                 | N/A                |  |

| Ball Number | Signal Name <sup>1,2</sup>    | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|-------------------------------|------------------------|--------------------|

| R13         | VSS                           | Ground                 | N/A                |

| R14         | VDD                           | Power                  | N/A                |

| R15         | VSS                           | Ground                 | N/A                |

| R16         | MVDD                          | Power                  | N/A                |

| R17         | VSS                           | Ground                 | N/A                |

| R18         | VDD                           | Power                  | N/A                |

| R19         | VSS                           | Ground                 | N/A                |

| R20         | VSS                           | Non-user               | N/A                |

| R21         | SXPVSS2                       | Ground                 | N/A                |

| R22         | SXPVDD2                       | Power                  | N/A                |

| R23         | SR2_TXD1/PE_TXD1 <sup>4</sup> | 0                      | SXPVDD2            |

| R24         | SR2_TXD1/PE_TXD1 <sup>4</sup> | 0                      | SXPVDD2            |

| R25         | SXCVSS2                       | Ground                 | N/A                |

| R26         | SXCVDD2                       | Power                  | N/A                |

| R27         | SR2_RXD1/PE_RXD1 <sup>4</sup> |                        | SXCVDD2            |

| R28         | SR2_RXD1/PE_RXD1 <sup>4</sup> |                        | SXCVDD2            |

| T1          | VSS                           | Ground                 | N/A                |

| T2          | тск                           |                        | QVDD               |

| T3          | SRESET <sup>6,7</sup>         | I/O                    | QVDD               |

| T4          | TDI                           |                        | QVDD               |

| T5          | VSS                           | Ground                 | N/A                |

| T6          | TDO                           | 0                      | QVDD               |

| T7          | VSS                           | Ground                 | N/A                |

| T8          | VSS                           | Ground                 | N/A                |

| T9          | QVDD                          | Power                  | N/A                |

| T10         | VSS                           | Ground                 | N/A                |

| T10         | VDD                           | Power                  | N/A                |

| T12         | VSS                           | Ground                 | N/A<br>N/A         |

|             |                               |                        |                    |

| T13         | M3VDD                         | Power                  | N/A                |

| T14         | VSS                           | Ground                 | N/A                |

| T15         | VDD                           | Power                  | N/A                |

| T16         | VSS                           | Ground                 | N/A                |

| T17         | MVDD                          | Power                  | N/A                |

| T18         | VSS                           | Ground                 | N/A                |

| T19         | VDD                           | Power                  | N/A                |

| T20         | VSS                           | Ground                 | N/A                |

| T21         | VSS                           | Non-user               | N/A                |

| T22         | SR2_IMP_CAL_RX                |                        | SXCVDD2            |

| T23         | SXPVSS2                       | Ground                 | N/A                |

| T24         | SXPVDD2                       | Power                  | N/A                |

| T25         | SR2_REF_CLK                   |                        | SXCVDD2            |

| T26         | SR2_REF_CLK                   |                        | SXCVDD2            |

| T27         | Reserved                      | NC                     | —                  |

| T28         | Reserved                      | NC                     |                    |

| U1          | M1DQ8                         | I/O                    | GVDD1              |

| U2          | VSS                           | Ground                 | N/A                |

| Ball Number  | Signal Name <sup>1,2</sup>            | Pin Type <sup>10</sup> | Power Rail<br>Name |  |

|--------------|---------------------------------------|------------------------|--------------------|--|

| Y11          | GVDD1                                 | Power                  | N/A                |  |

| Y12          | VSS                                   | Ground                 | N/A                |  |

| Y13          | GVDD1                                 | Power                  | N/A                |  |

| Y14          | VSS                                   | Ground                 | N/A                |  |

| Y15          | GVDD1                                 | Power                  | N/A                |  |

| Y16          | VSS                                   | Ground                 | N/A                |  |

| Y17          | GVDD1                                 | Power                  | N/A                |  |

| Y18          | VSS                                   | Ground                 | N/A                |  |

| Y19          | GVDD1                                 | Power                  | N/A                |  |

| Y20          | VSS                                   | Ground                 | N/A                |  |

| Y21          | NVDD                                  | Power                  | N/A                |  |

| Y22          | GPIO20/SPI_SL <sup>5,8</sup>          | I/O                    | NVDD               |  |

| Y23          | GPIO17/SPI_SCK <sup>5,8</sup>         | I/O                    | NVDD               |  |

| Y24          | GPIO14/DRQ0/IRQ14/RC14 <sup>5,8</sup> | I/O                    | NVDD               |  |

| Y25          | GPI012/IRQ12/RC12 <sup>5,8</sup>      | I/O                    | NVDD               |  |

| Y26          | GPIO8/IRQ8/RC8 <sup>5,8</sup>         | I/O                    | NVDD               |  |

| Y27          | NVDD                                  | Power                  | N/A                |  |

| Y28          | VSS                                   | Ground                 | N/A                |  |

| AA1          | GVDD1                                 | Power                  | N/A                |  |

| AA2          | VSS                                   | Ground                 | N/A                |  |

| AA3          | M1DQ18                                | I/O                    | GVDD1              |  |

| AA4          | GVDD1                                 | Power                  | N/A                |  |

| AA5          | VSS                                   | Ground                 | N/A                |  |

| AA6          | M1DQ20                                | I/O                    | GVDD1              |  |

| AA7          | GVDD1                                 | Power                  | N/A                |  |

| AA8          | VSS                                   | Ground                 | N/A                |  |

| AA9          | M1A15                                 | 0                      | GVDD1              |  |

| AA10         | M1CK2                                 | 0                      | GVDD1              |  |

| AA11         | M1MDIC0                               | I/O                    | GVDD1              |  |

| AA12         | M1VREF                                |                        | GVDD1              |  |

| AA13         | M1MDIC1                               | I/O                    | GVDD1              |  |

| AA14         | M1DQ46                                | I/O                    | GVDD1              |  |

| AA15         | M1DQ47                                | I/O                    | GVDD1              |  |

| AA16         | M1DQ45                                | I/O                    | GVDD1              |  |

| AA17         | M1DQ41                                | I/O                    | GVDD1              |  |

| AA18         | M1DQ62                                | I/O                    | GVDD1              |  |

| AA19         | M1DQ63                                | I/O                    | GVDD1              |  |

| AA20         | M1DQ61                                | I/O                    | GVDD1              |  |

| AA21         | VSS                                   | Ground                 | N/A                |  |

| AA22         | GPI021 <sup>5,8</sup>                 | I/O                    | NVDD               |  |

| AA23         | GPI018/SPI_MOSI <sup>5,8</sup>        | I/O                    | NVDD               |  |

| AA23<br>AA24 | GPIO16/RC16 <sup>5,8</sup>            | I/O                    | NVDD               |  |

| AA24<br>AA25 | GPIO4/DDN1/IRQ4/RC4 <sup>5,8</sup>    | I/O                    | NVDD               |  |

| AA26         | GPIO9/IRQ9/RC9 <sup>5,8</sup>         | I/O                    | NVDD               |  |

| AA20<br>AA27 | GPIO6/IRQ6/RC6 <sup>5,8</sup>         | I/O                    | NVDD               |  |

| AA27<br>AA28 | GPI01/IRQ1/RC1 <sup>5,8</sup>         | I/O                    | NVDD               |  |

| Ball Number | Signal Name <sup>1,2</sup>          | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|-------------------------------------|------------------------|--------------------|

| AB1         | M1DQS2                              | I/O                    | GVDD1              |

| AB2         | M1DQS2                              | I/O                    | GVDD1              |

| AB3         | M1DQ19                              | I/O                    | GVDD1              |

| AB4         | M1DM2                               | 0                      | GVDD1              |

| AB5         | M1DQ21                              | I/O                    | GVDD1              |

| AB6         | M1DQ22                              | I/O                    | GVDD1              |

| AB7         | M1CKE0                              | 0                      | GVDD1              |

| AB8         | M1A11                               | 0                      | GVDD1              |

| AB9         | M1A7                                | 0                      | GVDD1              |

| AB10        | M1CK2                               | 0                      | GVDD1              |

| AB11        | M1APAR_OUT                          | 0                      | GVDD1              |

| AB12        | M1ODT1                              | 0                      | GVDD1              |

| AB13        | M1APAR_IN                           | I                      | GVDD1              |

| AB14        | M1DQ43                              | I/O                    | GVDD1              |

| AB15        | M1DM5                               | 0                      | GVDD1              |

| AB16        | M1DQ44                              | I/O                    | GVDD1              |

| AB17        | M1DQ40                              | I/O                    | GVDD1              |

| AB18        | M1DQ59                              | I/O                    | GVDD1              |

| AB19        | M1DM7                               | 0                      | GVDD1              |

| AB20        | M1DQ60                              | I/O                    | GVDD1              |

| AB21        | VSS                                 | Ground                 | N/A                |

| AB22        | GPIO31/I2C_SDA <sup>5,8</sup>       | I/O                    | NVDD               |

| AB23        | GPIO27/TMR4/RCW_SRC0 <sup>5,8</sup> | I/O                    | NVDD               |

| AB24        | GPIO25/TMR2/RCW_SRC1 <sup>5,8</sup> | I/O                    | NVDD               |

| AB25        | GPIO24/TMR1/RCW_SRC2 <sup>5,8</sup> | I/O                    | NVDD               |

| AB26        | GPIO10/IRQ10/RC10 <sup>5,8</sup>    | I/O                    | NVDD               |

| AB27        | GPIO5/IRQ5/RC5 <sup>5,8</sup>       | I/O                    | NVDD               |

| AB28        | GPIO0/IRQ0/RC0 <sup>5,8</sup>       | I/O                    | NVDD               |

| AC1         | VSS                                 | Ground                 | N/A                |

| AC2         | GVDD1                               | Power                  | N/A                |

| AC3         | M1DQ16                              | I/O                    | GVDD1              |

| AC4         | VSS                                 | Ground                 | N/A                |

| AC5         | GVDD1                               | Power                  | N/A                |

| AC6         | M1DQ17                              | I/O                    | GVDD1              |

| AC7         | VSS                                 | Ground                 | N/A                |

| AC8         | GVDD1                               | Power                  | N/A                |

| AC9         | M1BA2                               | 0                      | GVDD1              |

| AC10        | VSS                                 | Ground                 | N/A                |

| AC11        | GVDD1                               | Power                  | N/A                |

| AC12        | M1A4                                | 0                      | GVDD1              |

| AC13        | VSS                                 | Ground                 | N/A                |

| AC14        | GVDD1                               | Power                  | N/A                |

| AC15        | M1DQ42                              | I/O                    | GVDD1              |

| AC16        | VSS                                 | Ground                 | N/A                |

| AC17        | GVDD1                               | Power                  | N/A                |

| AC18        | M1DQ58                              | I/O                    | GVDD1              |

| Ball Number | Signal Name <sup>1,2</sup>       | Pin Type <sup>10</sup> | Power Rail<br>Name |

|-------------|----------------------------------|------------------------|--------------------|

| AE9         | M1A8                             | 0                      | GVDD1              |

| AE10        | GVDD1                            | Power                  | N/A                |

| AE11        | VSS                              | Ground                 | N/A                |

| AE12        | M1A0                             | 0                      | GVDD1              |

| AE13        | GVDD1                            | Power                  | N/A                |

| AE14        | VSS                              | Ground                 | N/A                |

| AE15        | M1DQ39                           | I/O                    | GVDD1              |

| AE16        | GVDD1                            | Power                  | N/A                |

| AE17        | VSS                              | Ground                 | N/A                |

| AE18        | M1DQ54                           | I/O                    | GVDD1              |

| AE19        | GVDD1                            | Power                  | N/A                |

| AE20        | VSS                              | Ground                 | N/A                |

| AE21        | GPIO29/UART_TXD <sup>5,8</sup>   | I/O                    | NVDD               |

| AE22        | TDM1TCK/GE2_RX_CLK <sup>3</sup>  |                        | NVDD               |

| AE23        | TDM1RSN/GE2_RX_CTL <sup>3</sup>  | I/O                    | NVDD               |

| AE24        | VSS                              | Ground                 | N/A                |

| AE25        | TDM3RCK/GE1_GTX_CLK <sup>3</sup> | I/O                    | NVDD               |

| AE26        | TDM3TSN/GE1_RX_CLK <sup>3</sup>  | I/O                    | NVDD               |

| AE27        | TDM2RSN/GE1_T02 <sup>3</sup>     | I/O                    | NVDD               |

| AE28        | TDM2RDT/GE1_TD1 <sup>3</sup>     | I/O                    | NVDD               |

| AF1         | M1DQ28                           | I/O                    | GVDD1              |

| AF2         | M1DM3                            | 0                      | GVDD1<br>GVDD1     |

| AF3         | M1DQ26                           | I/O                    | GVDD1<br>GVDD1     |

| AF3<br>AF4  | MIECC4                           | I/O                    | GVDD1<br>GVDD1     |

| AF4<br>AF5  | M1ECC4<br>M1DM8                  | 0                      | GVDD1<br>GVDD1     |

|             |                                  | U                      |                    |

| AF6         | M1ECC2                           |                        | GVDD1              |

| AF7         | M1CKE1                           | 0                      | GVDD1<br>GVDD1     |

| AF8         | M1CK0                            |                        |                    |

| AF9         | M1CK0                            | 0                      | GVDD1              |

| AF10        | M1BA1                            | 0                      | GVDD1              |

| AF11        | M1A1                             | 0                      | GVDD1              |

| AF12        | M1WE                             | 0                      | GVDD1              |

| AF13        | M1DQ37                           | I/O                    | GVDD1              |

| AF14        | M1DM4                            | 0                      | GVDD1              |

| AF15        | M1DQ36                           | I/O                    | GVDD1              |

| AF16        | M1DQ32                           | I/O                    | GVDD1              |

| AF17        | M1DQ55                           | I/O                    | GVDD1              |

| AF18        | M1DM6                            | 0                      | GVDD1              |

| AF19        | M1DQ53                           | I/O                    | GVDD1              |

| AF20        | M1DQ52                           | I/O                    | GVDD1              |

| AF21        | GPIO28/UART_RXD <sup>5,8</sup>   | I/O                    | NVDD               |

| AF22        | TDM0RSN/GE2_TD2 <sup>3</sup>     | I/O                    | NVDD               |

| AF23        | TDM0TDT/GE2_TD3 <sup>3</sup>     | I/O                    | NVDD               |

| AF24        | NVDD                             | Power                  | N/A                |

| AF25        | TDM2TSN/GE1_TX_CTL <sup>3</sup>  | I/O                    | NVDD               |

| AF26        | GE1_RX_CTL                       | I                      | NVDD               |

rical Characteristics

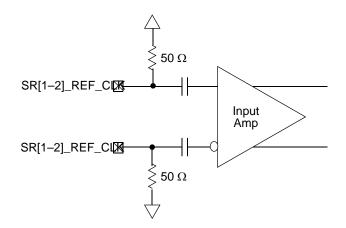

### 2.5.2.2 SerDes Reference Clock Receiver Characteristics

The SerDes reference clock inputs are applied to an internal PLL whose output creates the clock used by the corresponding SerDes lanes. The SerDes reference clock inputs are SR1\_REF\_CLK/SR1\_REF\_CLK or SR2\_REF\_CLK/SR2\_REF\_CLK. Figure 5 shows a receiver reference diagram of the SerDes reference clocks.

Figure 5. Receiver of SerDes Reference Clocks

The characteristics of the clock signals are as follows:

- The supply voltage requirements for V<sub>DDSXC</sub> are as specified in **Table 3**.

- The SerDes reference clock receiver reference circuit structure is as follows:

- The SR[1–2]\_REF\_CLK and SR[1–2]\_REF\_CLK are internally AC-coupled differential inputs as shown in Figure 5. Each differential clock input (SR[1–2]\_REF\_CLK or SR[1–2]\_REF\_CLK) has on-chip 50-Ω termination to GND<sub>SXC</sub> followed by on-chip AC-coupling.

- The external reference clock driver must be able to drive this termination.

- The SerDes reference clock input can be either differential or single-ended. Refer to the differential mode and single-ended mode descriptions below for detailed requirements.

- The maximum average current requirement also determines the common mode voltage range.

- When the SerDes reference clock differential inputs are DC coupled externally with the clock driver chip, the maximum average current allowed for each input pin is 8 mA. In this case, the exact common mode input voltage is not critical as long as it is within the range allowed by the maximum average current of 8 mA because the input is AC-coupled on-chip.

- This current limitation sets the maximum common mode input voltage to be less than 0.4 V (0.4 V / 50 = 8 mA) while the minimum common mode input level is 0.1 V above GND<sub>SXC</sub>. For example, a clock with a 50/50 duty cycle can be produced by a clock driver with output driven by its current source from 0 mA to 16 mA (0–0.8 V), such that each phase of the differential input has a single-ended swing from 0 V to 800 mV with the common mode voltage at 400 mV.

- If the device driving the SR[1–2]\_REF\_CLK and  $\overline{SR[1-2]}_REF_CLK$  inputs cannot drive 50  $\Omega$  to GND<sub>SXC</sub> DC or the drive strength of the clock driver chip exceeds the maximum input current limitations, it must be AC-coupled externally.

- The input amplitude requirement is described in detail in the following sections.

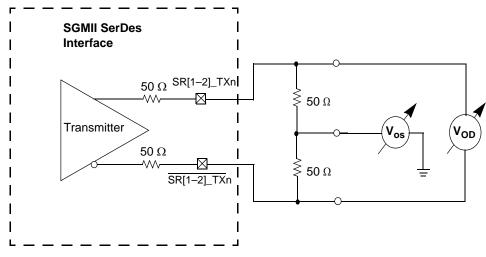

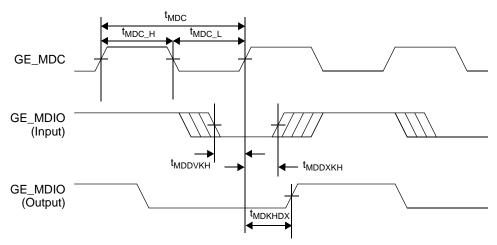

#### Figure 10. SGMII Transmitter DC Measurement Circuit

Table 16 describes the SGMII SerDes receiver AC-coupled DC electrical characteristics.

| Table 16. SGMII DC Receiver Electrical Characteristics <sup>5</sup> |

|---------------------------------------------------------------------|

|---------------------------------------------------------------------|

| Parameter                             |                                                                                    | Symbol                  | Min        | Тур | Max  | Unit | Notes |

|---------------------------------------|------------------------------------------------------------------------------------|-------------------------|------------|-----|------|------|-------|

| DC Input voltage range                |                                                                                    | _                       |            | N/A | I    | _    | 1     |

| Input<br>differential<br>voltage      | SRDSnCR4[EICE{12:10}] = 0b001 for SGMII1<br>SRDSnCR4[EICF{4:2}] = 0b001 for SGMII2 | V <sub>RX_DIFFp-p</sub> | IFFp-p 100 | —   | 1200 | mV   | 2, 4  |

|                                       | SRDSnCR4[EICE{12:10}] = 0b100 for SGMII1<br>SRDSnCR4[EICF{4:2}] = 0b100 for SGMII2 |                         | 175        | —   |      |      |       |

| Loss of<br>signal<br>threshold        | SRDSnCR4[EICE{12:10}] = 0b001 for SGMII1<br>SRDSnCR4[EICF{4:2}] = 0b001 for SGMII2 | VLOS                    | 30         | —   | 100  | mV   | 3, 4  |

|                                       | SRDSnCR4[EICE{12:10}] = 0b100 for SGMII1<br>SRDSnCR4[EICF{4:2}] = 0b100 for SGMII2 |                         | 65         | _   | 175  |      |       |

| Receiver differential input impedance |                                                                                    | Z <sub>RX_DIFF</sub>    | 80         | _   | 120  | W    | —     |

**tes:** 1. Input must be externally AC-coupled.

2.  $V_{RX\_DIFFp-p}$  is also referred to as peak-to-peak input differential voltage.

3. The concept of this parameter is equivalent to the Electrical Idle Detect Threshold parameter in the PCI Express interface. Refer to the PCI Express Differential Receiver (RX) Input Specifications section of the PCI Express Specification document. for details.

4. The values for SGMII1 and SGMII2 are selected in the SRDS control registers.

5. The supply voltage is 1.0 V.

rical Characteristics

# 2.5.4 RGMII and Other Interface DC Electrical Characteristics

Table 17 describes the DC electrical characteristics for the following interfaces:

- RGMII Ethernet

- SPI

- TDM

- GPIO

- UART

- TIMER

- EE

- I<sup>2</sup>C

- Interrupts (IRQn, NMI\_OUT, INT\_OUT)

- Clock and resets (CLKIN, PORESET, HRESET, SRESET)

- DMA External Request

- JTAG signals

### Table 17. 2.5 V I/O DC Electrical Characteristics

| Characteristic                                                                                                                                                                                                                                                                     | Symbol          | Min       | Мах         | Unit | Notes |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-----------|-------------|------|-------|--|--|

| Input high voltage                                                                                                                                                                                                                                                                 | V <sub>IH</sub> | 1.7       | _           | V    | 1     |  |  |

| Input low voltage                                                                                                                                                                                                                                                                  | V <sub>IL</sub> | _         | 0.7         | V    | 1     |  |  |

| Input high current (V <sub>IN</sub> = V <sub>DDIO</sub> )                                                                                                                                                                                                                          | I <sub>IN</sub> | —         | 30          | μA   | 2     |  |  |

| Output high voltage ( $V_{DDIO} = min, I_{OH} = -1.0 mA$ )                                                                                                                                                                                                                         | V <sub>OH</sub> | 2.0       | VDDIO + 0.3 | V    | 1     |  |  |

| Output low voltage (V <sub>DDIO</sub> = min, I <sub>OL</sub> = 1.0 mA)                                                                                                                                                                                                             | V <sub>OL</sub> | GND – 0.3 | 0.40        | V    | 1     |  |  |

| <ol> <li>Notes: 1. The min V<sub>IL</sub> and max V<sub>IH</sub> values are based on the respective min and max V<sub>IN</sub> values listed in Table 3.</li> <li>2. The symbol V<sub>IN</sub> represents the input voltage of the supply. It is referenced in Table 3.</li> </ol> |                 |           |             |      |       |  |  |

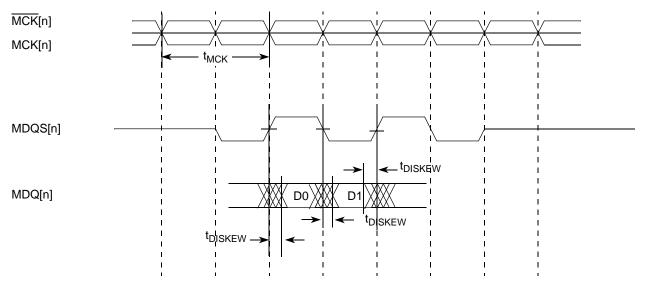

Figure 11 shows the DDR2 and DDR3 SDRAM interface input timing diagram.

Figure 11. DDR2 and DDR3 SDRAM Interface Input Timing Diagram

## 2.6.1.2 DDR SDRAM Output AC Timing Specifications

Table 21 provides the output AC timing specifications for the DDR SDRAM interface.

| Parameter                                                                               | Symbol <sup>1</sup>                         | Min                   | Max                          | Unit     | Notes |

|-----------------------------------------------------------------------------------------|---------------------------------------------|-----------------------|------------------------------|----------|-------|

| MCK[n] cycle time                                                                       | t <sub>MCK</sub>                            | 2.5                   | 5                            | ns       | 2     |

| ADDR/CMD output setup with respect to MCK<br>• 800 MHz data rate<br>• 667 MHz data rate | <sup>t</sup> DDKHAS                         | 0.917<br>1.10         |                              | ns<br>ns | 3     |

| ADDR/CMD output hold with respect to MCK<br>• 800 MHz data rate<br>• 667 MHz data rate  | <sup>t</sup> ddkhax                         | 0.767<br>1.02         |                              | ns<br>ns | 3     |

| MCSn output setup with respect to MCK<br>• 800 MHz data rate<br>• 667 MHz data rate     | <sup>t</sup> DDKHCS                         | 0.917<br>1.10         |                              | ns<br>ns | 3     |

| MCSn output hold with respect to MCK<br>• 800 MHz data rate<br>• 667 MHz data rate      | <sup>t</sup> DDKHCX                         | 0.767<br>1.02         |                              | ns<br>ns | 3     |

| MCK to MDQS Skew<br>• 800 MHz data rate<br>• 667 MHz data rate                          | t <sub>DDKHMH</sub>                         | -0.4<br>-0.6          | 0.375<br>0.6                 | ns       | 4     |

| MDQ/MECC/MDM output setup with respect to MDQS<br>• 800 MHz<br>• 667 MHz                | <sup>t</sup> DDKHDS,<br><sup>t</sup> DDKLDS | 300<br>375            |                              | ps<br>ps | 5     |

| MDQ/MECC/MDM output hold with respect to MDQS<br>• 800 MHz<br>• 667 MHz                 | <sup>t</sup> DDKHDX,<br><sup>t</sup> DDKLDX | 300<br>375            |                              | ps<br>ps | 5     |

| MDQS preamble                                                                           | t <sub>DDKHMP</sub>                         | $-0.9 \times t_{MCK}$ | —                            | ns       |       |

| MDQS postamble                                                                          | t <sub>DDKHME</sub>                         | $-0.4 \times t_{MCK}$ | $-0.6 \times t_{\text{MCK}}$ | ns       | _     |

### Table 21. DDR SDRAM Output AC Timing Specifications

### 2.6.2.2 PCI Express AC Physical Layer Specifications

The AC requirements for PCI Express implementations have separate requirements for the Tx and Rx lines. The MSC8154 supports a 2.5 Gbps PCI Express interface defined by the *PCI Express Base Specification, Revision 1.0a*. The transmitter specifications are defined in Table 25 and the receiver specifications are defined in Table 26. The parameters are specified at the component pins. the AC timing specifications do not include REF\_CLK jitter.

Note: Specifications are valid at the recommended operating conditions listed in Table 3.

### Table 25. PCI Express (2.5 Gbps) Differential Transmitter (Tx) Output AC Specifications

| Parameter                                                                     | Symbol                                       | Min    | Typical | Max    | Units | Notes |

|-------------------------------------------------------------------------------|----------------------------------------------|--------|---------|--------|-------|-------|

| Unit interval                                                                 | UI                                           | 399.88 | 400.00  | 400.12 | ps    | 1     |

| Minimum Tx eye width                                                          | T <sub>TX-EYE</sub>                          | 0.70   | -       | -      | UI    | 2, 3  |

| Maximum time between the jitter median and maximum deviation from the median. | T <sub>TX-EYE-MEDIAN-</sub><br>to-MAX-JITTER | _      | _       | 0.15   | UI    | 3, 4  |

| AC coupling capacitor                                                         | C <sub>TX</sub>                              | 75     | —       | 200    | nF    | 5     |

Notes: 1. Each UI is 400 ps ± 300 ppm. UI does not account for spread spectrum clock dictated variations. No test load is necessarily associated with this value.

2. The maximum transmitter jitter can be derived as  $T_{TX-MAX-JITTER} = 1 - T_{TX-EYE} = 0.3$  UI.

3. Specified at the measurement point into a timing and voltage compliance test load as shown in Figure 8 and measured over any 250 consecutive Tx UIs. A T<sub>TX-EYE</sub> = 0.70 UI provides for a total sum of deterministic and random jitter budget of T<sub>TX-JITTER-MAX</sub> = 0.30 UI for the transmitter collected over any 250 consecutive Tx UIs. The T<sub>TX-EYE-MEDIAN-to-MAX-JITTER</sub> median is less than half of the total Tx jitter budget collected over any 250 consecutive Tx UIs. It should be noted that the median is not the same as the mean. The jitter median describes the point in time where the number of jitter points on either side is approximately equal as opposed to the averaged time value. Jitter is defined as the measurement variation of the crossing points (V<sub>TX-DIFFp-p</sub> = 0 V) in relation to a recovered Tx UI. A recovered Tx UI is calculated over 3500 consecutive unit intervals of sample data.

4. Jitter is measured using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the Tx UI.

5. All transmitters shall be AC-coupled. The AC coupling is required either within the media or within the transmitting component itself. The SerDes transmitter does not have built-in Tx capacitance. An external AC coupling capacitor is required.

### Table 26. PCI Express (2.5 Gbps) Differential Receiver (Rx) Input AC Specifications

| Parameter                                                                     | Symbol                                       | Min    | Typical | Мах    | Units | Notes   |

|-------------------------------------------------------------------------------|----------------------------------------------|--------|---------|--------|-------|---------|

| Unit Interval                                                                 | UI                                           | 399.88 | 400.00  | 400.12 | ps    | 1       |

| Minimum receiver eye width                                                    | T <sub>RX-EYE</sub>                          | 0.4    | —       | _      | UI    | 2, 3, 4 |

| Maximum time between the jitter median and maximum deviation from the median. | T <sub>RX-EYE-MEDIAN-to-MAX</sub><br>-JITTER | _      | —       | 0.3    | UI    | 3, 4, 5 |

Notes: 1. Each UI is 400 ps ± 300 ppm. UI does not account for spread spectrum clock dictated variations. No test load is necessarily associated with this value.

2. The maximum interconnect media and transmitter jitter that can be tolerated by the receiver can be derived as  $T_{RX-MAX-JITTER} = 1 - T_{RX-EYE} = 0.6$  UI.

3. Specified at the measurement point and measured over any 250 consecutive UIs. The test load in Figure 8 should be used as the Rx device when taking measurements. If the clocks to the Rx and Tx are not derived from the same reference clock, the Tx UI recovered from 3500 consecutive UI must be used as a reference for the eye diagram.

4. A T<sub>RX-EYE</sub> = 0.40 UI provides for a total sum of 0.60 UI deterministic and random jitter budget for the transmitter and interconnect collected any 250 consecutive UIs. The T<sub>RX-EYE-MEDIAN-to-MAX-JITTER</sub> specification ensures a jitter distribution in which the median and the maximum deviation from the median is less than half of the total. UI jitter budget collected over any 250 consecutive Tx UIs. It should be noted that the median is not the same as the mean. The jitter median describes the point in time where the number of jitter points on either side is approximately equal as opposed to the averaged time value. If the clocks to the Rx and Tx are not derived from the same reference clock, the Tx UI recovered from 3500 consecutive UI must be used as the reference for the eye diagram.

5. Jitter is defined as the measurement variation of the crossing points (V<sub>RX-DIFFp-p</sub> = 0 V) in relation to a recovered Tx UI. A recovered Tx UI is calculated over 3500 consecutive unit intervals of sample data. Jitter is measured using all edges of the 250 consecutive UI in the center of the 3500 UI used for calculating the Tx UI. It is recommended that the recovered Tx UI is calculated using all edges in the 3500 consecutive UI interval with a fit algorithm using a minimization merit function. Least squares and median deviation fits have worked well with experimental and simulated data.

rical Characteristics

#### Serial RapidIO AC Timing Specifications 2.6.2.3

Note: Specifications are valid at the recommended operating conditions listed in Table 3.

Table 27 defines the transmitter AC specifications for the Serial RapidIO interface. The AC timing specifications do not include REF\_CLK jitter.

| Table 27. Serial RapidIO | Transmitter AC | Timing Specifications |

|--------------------------|----------------|-----------------------|

|--------------------------|----------------|-----------------------|

| Characteristic             | Symbol         | Min          | Typical | Мах          | Unit   |

|----------------------------|----------------|--------------|---------|--------------|--------|

| Deterministic Jitter       | J <sub>D</sub> | —            | _       | 0.17         | UI p-p |

| Total Jitter               | J <sub>T</sub> | —            | —       | 0.35         | UI p-p |

| Unit Interval: 1.25 GBaud  | UI             | 800 – 100ppm | 800     | 800 + 100ppm | ps     |

| Unit Interval: 2.5 GBaud   | UI             | 400 – 100ppm | 400     | 400 + 100ppm | ps     |

| Unit Interval: 3.125 GBaud | UI             | 320 – 100ppm | 320     | 320 + 100ppm | ps     |

Table 28 defines the Receiver AC specifications for the Serial RapidIO interface. The AC timing specifications do not include REF\_CLK jitter.

### Table 28. Serial RapidIO Receiver AC Timing Specifications

| Symbol          | Min                                                                    | Typical                                                                                                                                                                      | Max                                                                                                                                                                                                                                          | Unit                                                                                                                                                                                                                                                                          | Notes                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------|------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| J <sub>D</sub>  | 0.37                                                                   | _                                                                                                                                                                            | —                                                                                                                                                                                                                                            | UI p-p                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                   |

| J <sub>DR</sub> | 0.55                                                                   | _                                                                                                                                                                            | _                                                                                                                                                                                                                                            | UI p-p                                                                                                                                                                                                                                                                        | 1                                                                                                                                                                                                                                                                                                                                                                                                                   |

| J <sub>T</sub>  | 0.65                                                                   | _                                                                                                                                                                            | —                                                                                                                                                                                                                                            | UI p-p                                                                                                                                                                                                                                                                        | 1, 2                                                                                                                                                                                                                                                                                                                                                                                                                |

| BER             | —                                                                      | _                                                                                                                                                                            | 10 <sup>-12</sup>                                                                                                                                                                                                                            | _                                                                                                                                                                                                                                                                             | —                                                                                                                                                                                                                                                                                                                                                                                                                   |

| UI              | 800 – 100ppm                                                           | 800                                                                                                                                                                          | 800 + 100ppm                                                                                                                                                                                                                                 | ps                                                                                                                                                                                                                                                                            | _                                                                                                                                                                                                                                                                                                                                                                                                                   |

| UI              | 400 – 100ppm                                                           | 400                                                                                                                                                                          | 400 + 100ppm                                                                                                                                                                                                                                 | ps                                                                                                                                                                                                                                                                            | —                                                                                                                                                                                                                                                                                                                                                                                                                   |

| UI              | 320 – 100ppm                                                           | 320                                                                                                                                                                          | 320 + 100ppm                                                                                                                                                                                                                                 | ps                                                                                                                                                                                                                                                                            | _                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                 | J <sub>D</sub><br>J <sub>DR</sub><br>J <sub>T</sub><br>BER<br>UI<br>UI | J <sub>D</sub> 0.37           J <sub>DR</sub> 0.55           J <sub>T</sub> 0.65           BER         —           UI         800 – 100ppm           UI         400 – 100ppm | J <sub>D</sub> 0.37         —           J <sub>DR</sub> 0.55         —           J <sub>T</sub> 0.65         —           BER         —         —           UI         800 – 100ppm         800           UI         400 – 100ppm         400 | J <sub>D</sub> 0.37             J <sub>DR</sub> 0.55             J <sub>T</sub> 0.65             BER          10 <sup>-12</sup> 10 <sup>-12</sup> UI         800 - 100ppm         800         800 + 100ppm           UI         400 - 100ppm         400         400 + 100ppm | J <sub>D</sub> 0.37         —         —         UI p-p           J <sub>DR</sub> 0.55         —         —         UI p-p           J <sub>T</sub> 0.65         —         —         UI p-p           BER         —         —         10 <sup>-12</sup> —           UI         800 – 100ppm         800         800 + 100ppm         ps           UI         400 – 100ppm         400         400 + 100ppm         ps |

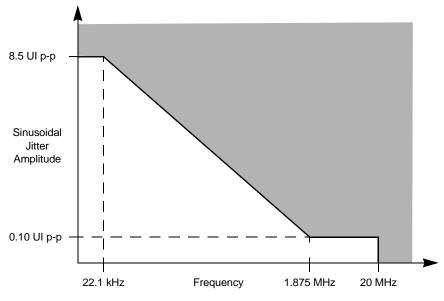

Total jitter is composed of three components, deterministic jitter, random jitter, and single frequency sinusoidal jitter. The 2. sinusoidal jitter may have any amplitude and frequency in the unshaded region of Figure 18. The sinusoidal jitter component is included to ensure margin for low frequency jitter, wander, noise, crosstalk, and other variable system effects.

Figure 18. Single Frequency Sinusoidal Jitter Limits

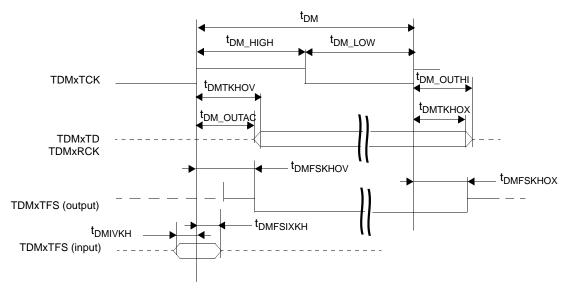

Figure 21 shows the TDM transmit signal timing.

Figure 21. TDM Transmit Signals

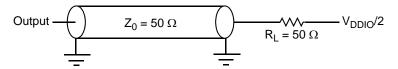

Figure 22 provides the AC test load for the TDM/SI.

Figure 22. TDM AC Test Load

# 2.6.4 Timers AC Timing Specifications

Table 32 lists the timer input AC timing specifications.

#### **Table 32. Timers Input AC Timing Specifications**

|                                                                                                                                                                                                                                                                            |                                                                                                                 | Characteristics      | Symbol             | Minimum | Unit | Notes |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|----------------------|--------------------|---------|------|-------|

| Timers i                                                                                                                                                                                                                                                                   | nputs-                                                                                                          | -minimum pulse width | T <sub>TIWID</sub> | 8       | ns   | 1, 2  |

| Notes:                                                                                                                                                                                                                                                                     | Notes: 1. The maximum allowed frequency of timer outputs is 125 MHz. Configure the timer modules appropriately. |                      |                    |         |      |       |

| <ol> <li>Timer inputs and outputs are asynchronous to any visible clock. Timer outputs should be synchronized before use by any external synchronous logic. Timer inputs are required to be valid for at least t<sub>TIWID</sub> ns to ensure proper operation.</li> </ol> |                                                                                                                 | y any                |                    |         |      |       |

Note: For recommended operating conditions, see Table 3.

Figure 23 shows the AC test load for the timers.

Figure 23. Timer AC Test Load

rical Characteristics

## 2.6.5 Ethernet Timing

This section describes the AC electrical characteristics for the Ethernet interface.

There are programmable delay units (PDU) that should be programmed differently for each interface to meet timing. There is a general configuration register 4 (GCR4) used to configure the timing. For additional information, see the *MSC8154 Reference Manual*.

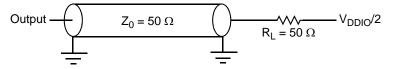

# 2.6.5.1 Management Interface Timing

Table 33 lists the timer input Ethernet controller management interface timing specifications shown in Figure 24.

Table 33. Ethernet Controller Management Interface Timing

| Characteristics                          | Symbol              | Min | Max | Unit |

|------------------------------------------|---------------------|-----|-----|------|

| GE_MDC frequency                         | f <sub>MDC</sub>    | -   | 2.5 | MHz  |

| GE_MDC period                            | t <sub>MDC</sub>    | 400 | —   | ns   |

| GE_MDC clock pulse width high            | t <sub>MDC_H</sub>  | 160 | _   | ns   |

| GE_MDC clock pulse width low             | t <sub>MDC_L</sub>  | 160 | _   | ns   |

| GE_MDC to GE_MDIO delay <sup>2</sup>     | t <sub>MDKHDX</sub> | 10  | 70  | ns   |

| GE_MDIO to GE_MDC rising edge setup time | t <sub>MDDVKH</sub> | 20  | —   | ns   |

| GE_MDC rising edge to GE_MDIO hold time  | t <sub>MDDXKH</sub> | 0   | _   | ns   |

Notes: 1. Program the GE\_MDC frequency (f<sub>MDC</sub>) to a maximum value of 2.5 MHz (400 ns period for t<sub>MDC</sub>). The value depends on the source clock and configuration of MIIMCFG[MCS] and UPSMR[MDCP]. For example, for a source clock of 400 MHz to achieve f<sub>MDC</sub> = 2.5 MHz, program MIIMCFG[MCS] = 0x4 and UPSMR[MDCP] = 0. See the *MSC8154 Reference Manual* for configuration details.

2. The value depends on the source clock. For example, for a source clock of 267 MHz, the delay is 70 ns. For a source clock of 333 MHz, the delay is 58 ns.

Figure 24. MII Management Interface Timing

ware Design Considerations

# 3.3 Clock and Timing Signal Board Layout Considerations

When laying out the system board, use the following guidelines:

- Keep clock and timing signal paths as short as possible and route with 50  $\Omega$  impedance.

- Use a serial termination resistor placed close to the clock buffer to minimize signal reflection. Use the following equation to compute the resistor value:

Rterm = Rim - Rbuf

where Rim = trace characteristic impedance

Rbuf = clock buffer internal impedance.

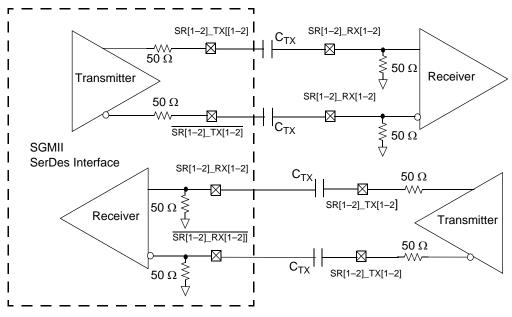

# 3.4 SGMII AC-Coupled Serial Link Connection Example

Figure 39 shows an example of a 4-wire AC-coupled serial link connection. For additional layout suggestions, see *AN3556 MSC815x High Speed Serial Interface Hardware Design Considerations*, available on the Freescale website or from your local sales office or representative.

Figure 39. 4-Wire AC-Coupled SGMII Serial Link Connection Example

# 3.5 Connectivity Guidelines

**Note:** Although the package actually uses a ball grid array, the more conventional term pin is used to denote signal connections in this discussion.

First, select the pin multiplexing mode to allocate the required I/O signals. Then use the guidelines presented in the following subsections for board design and connections. The following conventions are used in describing the connectivity requirements:

- GND indicates using a 10 kΩ pull-down resistor (recommended) or a direct connection to the ground plane. Direct connections to the ground plane may yield DC current up to 50 mA through the I/O supply that adds to overall power consumption.

- 2.  $V_{DD}$  indicates using a 10 k $\Omega$  pull-up resistor (recommended) or a direct connection to the appropriate power supply. Direct connections to the supply may yield DC current up to 50 mA through the I/O supply that adds to overall power consumption.

- 3. Mandatory use of a pull-up or pull-down resistor is clearly indicated as "pull-up/pull-down." For buses, each pin on the bus should have its own resistor.

- 4. NC indicates "not connected" and means do not connect anything to the pin.

- 5. The phrase "in use" indicates a typical pin connection for the required function.

- **Note:** Please see recommendations #1 and #2 as mandatory pull-down or pull-up connection for unused pins in case of subset interface connection.

| Signal Name                                                                  | Pin Connection |  |

|------------------------------------------------------------------------------|----------------|--|

| SR[1–2]_RXD <b>n</b>                                                         | SXCVSS         |  |

| SR[1-2]_RXD <b>n</b>                                                         | SXCVSS         |  |

| SR[1-2]_TXDn                                                                 | NC             |  |

| SR[1–2]_TXD <b>n</b>                                                         | NC             |  |

| SR[1-2]_PLL_AVDD                                                             | in use         |  |

| SR[1–2]_PLL_AGND                                                             | in use         |  |

| SXPVSS                                                                       | in use         |  |

| SXCVSS                                                                       | in use         |  |

| SXPVDD                                                                       | in use         |  |

| SXCVDD                                                                       | in use         |  |

| Note: The <i>n</i> indicates the lane number {0,1,2,3} for all unused lanes. |                |  |

### Table 45. Connectivity of HSSI Related Pins When Specific Lane Is Not Used (continued)

# 3.5.3 RGMII Ethernet Related Pins

**Note:** Table 46 and Table 47 assume that the alternate function of the specified pin is not used. If the alternate function is used, connect the pin as required to support that function.

### Table 46. Connectivity of RGMII Related Pins When the RGMII Interface Is Not Used

| Signal Name                                                              | Pin Connection |  |

|--------------------------------------------------------------------------|----------------|--|

| GE1_RX_CTL                                                               | GND            |  |

| GE2_TX_CTL                                                               | NC             |  |

| Note: Assuming GE1 and GE2 are disabled in the reset configuration word. |                |  |

GE\_MDC and GE\_MDIO pins should be connected as required by the specified protocol. If neither GE1 nor GE2 is used, Table 47 lists the recommended management pin connections.

### Table 47. Connectivity of GE Management Pins When GE1 and GE2 Are Not Used

| Signal Name | Pin Connection |

|-------------|----------------|

| GE_MDC      | NC             |

| GE_MDIO     | NC             |

## 3.5.4 TDM Interface Related Pins

Table 48 lists the board connections of the TDM pins when an entire specific TDM is not used. For multiplexing options that select a subset of a TDM interface, use the connections described in Table 48 for those signals that are not selected. Table 48 assumes that the alternate function of the specified pin is not used. If the alternate function is used, connect that pin as required to support the selected function.

#### Table 48. Connectivity of TDM Related Pins When TDM Interface Is Not Used

| Signal Name       | Pin Connection |

|-------------------|----------------|

| TDM <b>n</b> RCLK | GND            |

| TDM <b>n</b> RDAT | GND            |

| TDM <b>n</b> RSYN | GND            |

ware Design Considerations

#### Table 48. Connectivity of TDM Related Pins When TDM Interface Is Not Used

| Signal Name           |                                                                                                                                | Pin Connection                                                                                                                       |  |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|

| TDMnTCLK              |                                                                                                                                | GND                                                                                                                                  |  |

| TDMT <i>n</i> DAT GND |                                                                                                                                | GND                                                                                                                                  |  |

| TDM <b>n</b> TSYN     |                                                                                                                                | GND                                                                                                                                  |  |

| V <sub>DDIO</sub>     | 2.5 V                                                                                                                          |                                                                                                                                      |  |

|                       | <i>n</i> = {0, 1, 2,3}<br>In case of subset of TDM interface usage please make<br><i>MSC8154 Reference Manual</i> for details. | set of TDM interface usage please make sure to disable unused TDM modules. See <i>TDM</i> chapter in the ference Manual for details. |  |

# 3.5.5 Miscellaneous Pins

Table 49 lists the board connections for the pins not required by the system design. Table 49 assumes that the alternate function of the specified pin is not used. If the alternate function is used, connect that pin as required to support the selected function.

Table 49. Connectivity of Individual Pins When They Are Not Required

| Signal Name       | Pin Connection                                      |

|-------------------|-----------------------------------------------------|

| CLKOUT            | NC                                                  |

| EEO               | GND                                                 |

| EE1               | NC                                                  |

| GPIO[31-0]        | NC                                                  |

| SCL               | See the GPIO connectivity guidelines in this table. |

| SDA               | See the GPIO connectivity guidelines in this table. |

| INT_OUT           | NC                                                  |

| IRQ[15–0]         | See the GPIO connectivity guidelines in this table. |

| NMI               | V <sub>DDIO</sub>                                   |

| NMI_OUT           | NC                                                  |

| RC[21–0]          | GND                                                 |

| STOP_BS           | GND                                                 |

| ТСК               | GND                                                 |

| ТDI               | GND                                                 |

| TDO               | NC                                                  |

| TMR[4-0]          | See the GPIO connectivity guidelines in this table. |

| TMS               | GND                                                 |

| TRST              | See Section 3.1 for guidelines.                     |

| URXD              | See the GPIO connectivity guidelines in this table. |

| UTXD              | See the GPIO connectivity guidelines in this table. |

| DDN[1-0]          | See the GPIO connectivity guidelines in this table. |

| DRQ[1-0]          | See the GPIO connectivity guidelines in this table. |

| RCW_LSEL_0        | GND                                                 |

| RCW_LSEL_1        | GND                                                 |