Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2014112                    |                                                                        |

|----------------------------|------------------------------------------------------------------------|

| Product Status             | Active                                                                 |

| Core Processor             | e200z0h                                                                |

| Core Size                  | 32-Bit Single-Core                                                     |

| Speed                      | 64MHz                                                                  |

| Connectivity               | CANbus, I <sup>2</sup> C, LINbus, SCI, SPI                             |

| Peripherals                | DMA, POR, PWM, WDT                                                     |

| Number of I/O              | 121                                                                    |

| Program Memory Size        | 1MB (1M x 8)                                                           |

| Program Memory Type        | FLASH                                                                  |

| EEPROM Size                | 64K x 8                                                                |

| RAM Size                   | 80K x 8                                                                |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                              |

| Data Converters            | A/D 15x10b, 5x12b                                                      |

| Oscillator Type            | Internal                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                     |

| Mounting Type              | Surface Mount                                                          |

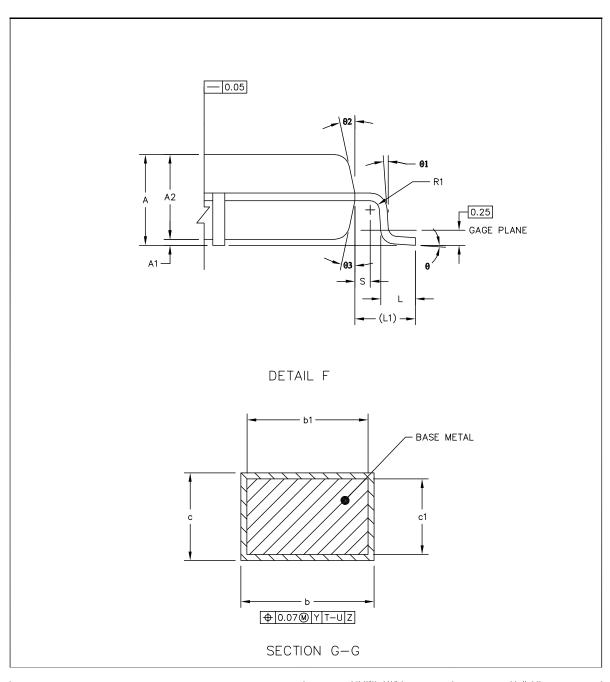

| Package / Case             | 144-LQFP                                                               |

| Supplier Device Package    | 144-LQFP (20x20)                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/spc5606bk0vlq6 |

|                            |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

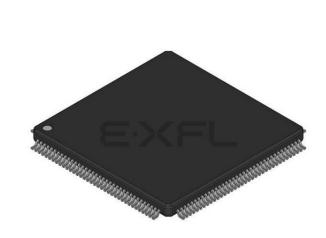

## 1.4 Block diagram

Figure 1 shows a top-level block diagram of the MPC5606BK.

Figure 1. MPC5606BK block diagram

| Port   | PCR      | Alternate                          | ou al oterret                                   | uo                                     | pe <sup>2</sup>  | ⊢°÷                   | Pin number                    |             |             |             |

|--------|----------|------------------------------------|-------------------------------------------------|----------------------------------------|------------------|-----------------------|-------------------------------|-------------|-------------|-------------|

| pin    | register | function <sup>1</sup>              | Function                                        | Peripheral                             | I/O<br>direction | Pad type <sup>2</sup> | RESET<br>config. <sup>3</sup> | 100<br>LQFP | 144<br>LQFP | 176<br>LQFP |

| PD[5]  | PCR[53]  | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[53]<br>—<br>—<br>ADC0_P[9]<br>ADC1_P[9]    | SIUL<br>—<br>—<br>ADC_0<br>ADC_1       | <br> <br> <br>   | I                     | Tristate                      | 46          | 68          | 82          |

| PD[6]  | PCR[54]  | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[54]<br>—<br>—<br>ADC0_P[10]<br>ADC1_P[10]  | SIUL<br>—<br>—<br>ADC_0<br>ADC_1       | -                | I                     | Tristate                      | 47          | 69          | 83          |

| PD[7]  | PCR[55]  | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[55]<br>—<br>—<br>ADC0_P[11]<br>ADC1_P[11]  | SIUL<br>—<br>—<br>ADC_0<br>ADC_1       | <br> -<br> <br>  | I                     | Tristate                      | 48          | 70          | 84          |

| PD[8]  | PCR[56]  | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[56]<br>—<br>—<br>ADC0_P[12]<br>ADC1_P[12]  | SIUL<br>—<br>—<br>ADC_0<br>ADC_1       |                  | I                     | Tristate                      | 49          | 71          | 87          |

| PD[9]  | PCR[57]  | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[57]<br>—<br>—<br>ADC0_P[13]<br>ADC1_P[13]  | SIUL<br>—<br>—<br>ADC_0<br>ADC_1       | <br> -<br> <br>  | I                     | Tristate                      | 56          | 78          | 94          |

| PD[10] | PCR[58]  | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[58]<br>—<br>—<br>ADC0_P[14]<br>ADC1_P[14]  | SIUL<br>—<br>—<br>ADC_0<br>ADC_1       | -<br>   <br>     | I                     | Tristate                      | 57          | 79          | 95          |

| PD[11] | PCR[59]  | AF0<br>AF1<br>AF2<br>AF3<br>—<br>— | GPIO[59]<br>—<br>—<br>ADC0_P[15]<br>ADC1_P[15]  | SIUL<br>—<br>—<br>ADC_0<br>ADC_1       | <br> -<br> <br>  | Ι                     | Tristate                      | 58          | 80          | 96          |

| PD[12] | PCR[60]  | AF0<br>AF1<br>AF2<br>AF3<br>—      | GPIO[60]<br>CS5_0<br>E0UC[24]<br>—<br>ADC0_S[4] | SIUL<br>DSPI_0<br>eMIOS_0<br><br>ADC_0 | I/O O/O   -      | J                     | Tristate                      |             |             | 100         |

Table 2. Functional port pins (continued)

| Port   | PCR      | Alternate                     |                                                        | eral                                | no                     | pe <sup>2</sup>       | н <sup>°</sup> я              | Ρ           | in numb     | er          |

|--------|----------|-------------------------------|--------------------------------------------------------|-------------------------------------|------------------------|-----------------------|-------------------------------|-------------|-------------|-------------|

| pin    |          | function <sup>1</sup>         | Function                                               | Peripheral                          | I/O<br>direction       | Pad type <sup>2</sup> | RESET<br>config. <sup>3</sup> | 100<br>LQFP | 144<br>LQFP | 176<br>LQFP |

| PH[11] | PCR[123] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[123]<br>SOUT_3<br>CS0_4<br>E1UC[5]                | SIUL<br>DSPI_3<br>DSPI_4<br>eMIOS_1 | I/O<br>O<br>I/O<br>I/O | М                     | Tristate                      | _           | _           | 140         |

| PH[12] | PCR[124] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[124]<br>SCK_3<br>CS1_4<br>E1UC[25]                | SIUL<br>DSPI_3<br>DSPI_4<br>eMIOS_1 | I/O<br>I/O<br>I/O      | М                     | Tristate                      | _           | _           | 141         |

| PH[13] | PCR[125] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[125]<br>SOUT_4<br>CS0_3<br>E1UC[26]               | SIUL<br>DSPI_4<br>DSPI_3<br>eMIOS_1 | I/O<br>O<br>I/O<br>—   | М                     | Tristate                      | _           | _           | 9           |

| PH[14] | PCR[126] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[126]<br>SCK_4<br>CS1_3<br>E1UC[27]                | SIUL<br>DSPI_4<br>DSPI_3<br>eMIOS_1 | I/O<br>I/O<br>I/O<br>— | М                     | Tristate                      | _           | _           | 10          |

| PH[15] | PCR[127] | AF1<br>AF2                    | GPIO[127]<br>SOUT_5<br>                                | SIUL<br>DSPI_5<br>—                 | I/O<br>O<br>—          | М                     | Tristate                      |             | _           | 8           |

|        |          | AF3                           | E1UC[17]                                               | eMIOS_1<br>Port I                   |                        |                       |                               |             |             |             |

| PI[0]  | PCR[128] | AF0                           | GPIO[128]                                              | SIUL                                | I/O                    | s                     | Tristate                      |             |             | 172         |

| 1 1[0] |          | AF1<br>AF2<br>AF3             | E0UC[28]<br>—<br>—                                     | eMIOS_0<br>—                        | I/O<br>—<br>—          | 0                     | motato                        |             |             | 172         |

| PI[1]  | PCR[129] | AF0<br>AF1<br>AF2<br>AF3<br>— | GPIO[129]<br>E0UC[29]<br><br>WKUP[24] <sup>4</sup><br> | SIUL<br>eMIOS_0<br><br>WKUP<br>     | I/O<br>I/O<br><br>I    | S                     | Tristate                      |             |             | 171         |

| PI[2]  | PCR[130] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[130]<br>E0UC[30]<br>—<br>—                        | SIUL<br>eMIOS_0<br>—                | I/O<br>I/O<br>—        | S                     | Tristate                      | _           | _           | 170         |

| PI[3]  | PCR[131] | AF0<br>AF1<br>AF2<br>AF3<br>— | GPIO[131]<br>E0UC[31]<br><br>WKUP[23] <sup>4</sup><br> | SIUL<br>eMIOS_0<br><br>WKUP<br>     | I/O<br>I/O<br><br>I    | S                     | Tristate                      |             |             | 169         |

| PI[4]  | PCR[132] | AF0<br>AF1<br>AF2<br>AF3      | GPIO[132]<br>E1UC[28]<br>SOUT_4<br>—                   | SIUL<br>eMIOS_1<br>DSPI_4<br>—      | I/O<br>I/O<br>O        | S                     | Tristate                      |             |             | 143         |

Table 2. Functional port pins (continued)

#### Table 4. Parameter classifications

| Classification tag | Tag description                                                                                                                                                                                                        |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Р                  | Those parameters are guaranteed during production testing on each individual device.                                                                                                                                   |

| С                  | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations.                                                                              |

| Т                  | Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the typical column are within this category. |

| D                  | Those parameters are derived mainly from simulations.                                                                                                                                                                  |

### NOTE

The classification is shown in the column labeled "C" in the parameter tables where appropriate.

# 3.2 NVUSRO register

Portions of the device configuration, such as high voltage supply, oscillator margin, and watchdog enable/disable after reset are controlled via bit values in the Non-Volatile User Options Register (NVUSRO) register.

For a detailed description of the NVUSRO register, please refer to the MPC5606BK Microcontroller Reference Manual.

## 3.2.1 NVUSRO[PAD3V5V] field description

Table 5 shows how NVUSRO[PAD3V5V] controls the device configuration.

| Table 5. I | PAD3V5V | field | description <sup>1</sup> |

|------------|---------|-------|--------------------------|

|------------|---------|-------|--------------------------|

| Value <sup>2</sup> | Description                  |

|--------------------|------------------------------|

| 0                  | High voltage supply is 5.0 V |

| 1                  | High voltage supply is 3.3 V |

|                    |                              |

<sup>1</sup> See the *MPC5606BK Microcontroller Reference Manual* for more information on the NVUSRO register.

<sup>2</sup> The default manufacturing value is '1'. This value can be programmed by the customer in Shadow Flash.

The DC electrical characteristics are dependent on the PAD3V5V bit value.

# 3.2.2 NVUSRO[OSCILLATOR\_MARGIN] field description

Table 6 shows how NVUSRO[OSCILLATOR\_MARGIN] controls the device configuration.

### Table 6. OSCILLATOR\_MARGIN field description<sup>1</sup>

| Value <sup>2</sup> | Description                                 |  |

|--------------------|---------------------------------------------|--|

| 0                  | Low consumption configuration (4 MHz/8 MHz) |  |

| 1                  | High margin configuration (4 MHz/16 MHz)    |  |

<sup>1</sup> See the *MPC5606BK Microcontroller Reference Manual* for more information on the NVUSRO register.

<sup>2</sup> The default manufacturing value is '1'. This value can be programmed by the customer in Shadow Flash.

The fast external crystal oscillator consumption is dependent on the OSCILLATOR\_MARGIN bit value.

# 3.2.3 NVUSRO[WATCHDOG\_EN] field description

The watchdog enable/disable configuration after reset is dependent on the WATCHDOG\_EN bit value. Table 7 shows how NVUSRO[WATCHDOG\_EN] controls the device configuration.

| Value <sup>2</sup> | Description         |

|--------------------|---------------------|

| 0                  | Disable after reset |

| 1                  | Enable after reset  |

### Table 7. WATCHDOG\_EN field description<sup>1</sup>

<sup>1</sup> See the MPC5606BK Microcontroller Reference Manual for more information on the NVUSRO register.

<sup>2</sup> The default manufacturing value is '1'. This value can be programmed by the customer in Shadow Flash.

# 3.3 Absolute maximum ratings

#### Table 8. Absolute maximum ratings

| Cumha                |                                             | Devenueter                                                                                              | Conditions                                    |                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                               | 11   |

|----------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| Symbo                | 1                                           | Parameter                                                                                               | Conditions                                    | Min                                                                                                                                                                                                  | Max                                                                                                                                                                                                                                                                                                                                                                                           | Unit |

| V <sub>SS</sub>      | SR                                          | Digital ground on VSS_HV pins                                                                           | _                                             | 0                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                             | V    |

| V <sub>DD</sub>      | SR                                          | Voltage on VDD_HV pins with respect to ground (V <sub>SS</sub> )                                        | —                                             | -0.3                                                                                                                                                                                                 | 6.0                                                                                                                                                                                                                                                                                                                                                                                           | V    |

| V <sub>SS_LV</sub>   | SR                                          | Voltage on VSS_LV (low voltage digital supply) pins with respect to ground (V <sub>SS</sub> )           | —                                             | V <sub>SS</sub> -0.1                                                                                                                                                                                 | V <sub>SS</sub> + 0.1                                                                                                                                                                                                                                                                                                                                                                         | V    |

| $V_{DD_BV}$          | SR                                          | Voltage on VDD_BV pin (regulator supply) with                                                           | —                                             | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                               | V    |

|                      |                                             | respect to ground (V <sub>SS</sub> )                                                                    | Relative to V <sub>DD</sub>                   | Min         Max           0         0 $-0.3$ $6.0$ $V_{SS} - 0.1$ $V_{SS} + 0.1$ $-0.3$ $6.0$ $-0.3$ $6.0$ $V_{SS} - 0.1$ $V_{SS} + 0.1$ $V_{SS} - 0.1$ $V_{DD} + 0.3$ $V_{SS} - 0.1$ $V_{SS} + 0.1$ |                                                                                                                                                                                                                                                                                                                                                                                               |      |

| V <sub>SS_ADC</sub>  | SR                                          | Voltage on VSS_HV_ADC0, VSS_HV_ADC1<br>(ADC reference) pin with respect to ground<br>(V <sub>SS</sub> ) | _                                             | V <sub>SS</sub> – 0.1                                                                                                                                                                                | V <sub>SS</sub> + 0.1                                                                                                                                                                                                                                                                                                                                                                         | V    |

| $V_{DD\_ADC}$        | DC SR Voltage on VDD_HV_ADC0, VDD_HV_ADC1 — | -0.3                                                                                                    | 6.0                                           | V                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                               |      |

|                      |                                             | (ADC reference) with respect to ground (V <sub>SS</sub> )                                               | Relative to V <sub>DD</sub>                   | V <sub>DD</sub> - 0.3                                                                                                                                                                                | Min         Max           0         0 $-0.3$ $6.0$ $V_{SS} - 0.1$ $V_{SS} + 0.1$ $-0.3$ $6.0$ $-0.3$ $6.0$ $-0.3$ $6.0$ $-0.3$ $V_{DD} + 0.3$ $V_{SS} - 0.1$ $V_{SS} + 0.1$ $-0.3$ $6.0$ $V_{DD} - 0.3$ $V_{DD} + 0.3$ $-0.3$ $6.0$ $-0.3$ $6.0$ $-0.3$ $6.0$ $-0.3$ $6.0$ $-0.3$ $6.0$ $-0.3$ $6.0$ $-0.3$ $6.0$ $-0.3$ $6.0$ $-0.3$ $6.0$ $-0.3$ $5.0$ $-10$ $10$ $-50$ $50$ $-0.64$ $-0.4$ |      |

| V <sub>IN</sub>      | SR                                          | Voltage on any GPIO pin with respect to                                                                 | —                                             | -0.3                                                                                                                                                                                                 | 6.0                                                                                                                                                                                                                                                                                                                                                                                           | V    |

|                      |                                             | ground (V <sub>SS</sub> )                                                                               | Relative to V <sub>DD</sub>                   | _                                                                                                                                                                                                    | V <sub>DD</sub> + 0.3                                                                                                                                                                                                                                                                                                                                                                         |      |

| I <sub>INJPAD</sub>  | SR                                          | Injected input current on any pin during<br>overload condition                                          | _                                             | -10                                                                                                                                                                                                  | 10                                                                                                                                                                                                                                                                                                                                                                                            | mA   |

| I <sub>INJSUM</sub>  | SR                                          | Absolute sum of all injected input currents during overload condition                                   |                                               | -50                                                                                                                                                                                                  | 50                                                                                                                                                                                                                                                                                                                                                                                            |      |

| I <sub>AVGSEG</sub>  | SR                                          | Sum of all the static I/O current within a supply segment                                               | $V_{DD} = 5.0 V \pm 10\%,$<br>PAD3V5V = 0     | —                                                                                                                                                                                                    | 70                                                                                                                                                                                                                                                                                                                                                                                            | mA   |

|                      |                                             |                                                                                                         | V <sub>DD</sub> = 3.3 V ± 10%,<br>PAD3V5V = 1 | -                                                                                                                                                                                                    | 64                                                                                                                                                                                                                                                                                                                                                                                            |      |

| T <sub>STORAGE</sub> | SR                                          | Storage temperature                                                                                     | —                                             | -55                                                                                                                                                                                                  | 150                                                                                                                                                                                                                                                                                                                                                                                           | °C   |

| Symbo                           | 1  | Parameter                       | Conditions                             | Va  | Value |      |  |

|---------------------------------|----|---------------------------------|----------------------------------------|-----|-------|------|--|

| Symbo                           | •  | Falameter                       | Conditions                             | Min | Мах   | Unit |  |

| T <sub>A C-Grade</sub><br>Part  | SR | Ambient temperature under bias  | f <sub>CPU</sub> < 64 MHz <sup>8</sup> | -40 | 85    | °C   |  |

| T <sub>J C</sub> -Grade<br>Part | SR | Junction temperature under bias | _                                      | -40 | 110   |      |  |

| T <sub>A V-Grade</sub><br>Part  | SR | Ambient temperature under bias  | f <sub>CPU</sub> < 64 MHz <sup>8</sup> | -40 | 105   |      |  |

| T <sub>J V-Grade</sub><br>Part  | SR | Junction temperature under bias | _                                      | -40 | 130   |      |  |

| T <sub>A M-Grade</sub><br>Part  | SR | Ambient temperature under bias  | f <sub>CPU</sub> < 64 MHz <sup>8</sup> | -40 | 125   |      |  |

| T <sub>J M</sub> -Grade<br>Part | SR | Junction temperature under bias | _                                      | -40 | 150   |      |  |

Table 9. Recommended operating conditions (3.3 V) (continued)

$^1\,$  100 nF capacitance needs to be provided between each  $V_{DD}/V_{SS}$  pair.

$^2~$  330 nF capacitance needs to be provided between each  $V_{DD\_LV}/V_{SS\_LV}$  supply pair.

<sup>3</sup> 470 nF capacitance needs to be provided between V<sub>DD\_BV</sub> and the nearest V<sub>SS\_LV</sub> (higher value may be needed depending on external regulator characteristics). Supply ramp slope on VDD\_BV should always be faster or equal to slope of VDD\_HV. Otherwise, device may enter regulator bypass mode if slope on VDD\_BV is slower.

$^4\,$  100 nF capacitance needs to be provided between V\_DD\_ADC/V\_SS\_ADC pair.

<sup>5</sup> Full electrical specification cannot be guaranteed when voltage drops below 3.0 V. In particular, ADC electrical characteristics and I/O DC electrical specification may not be guaranteed. When voltage drops below V<sub>LVDHVL</sub>, the device is reset.

<sup>6</sup> Guaranteed by device validation

$^7\,$  Minimum value of TV\_{DD} must be guaranteed until V\_{DD} reaches 2.6 V (maximum value of V\_{PORH}).

<sup>8</sup> This frequency includes the 4% frequency modulation guard band.

| Table 10 | . Recommended | operating | conditions | (5.0 V) |

|----------|---------------|-----------|------------|---------|

|----------|---------------|-----------|------------|---------|

| Symbol                          | 1  | Parameter                                                                                   | Conditions                  | Va                    | Unit                                                                                                            |      |  |

|---------------------------------|----|---------------------------------------------------------------------------------------------|-----------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------|------|--|

| Cymbol                          | •  | i didileter                                                                                 | Conditions                  | Min                   | Max<br>0<br>5.5<br>5.5<br>V <sub>SS</sub> + 0.1<br>5.5<br>5.5<br>V <sub>DD</sub> + 0.1<br>V <sub>SS</sub> + 0.1 | Unit |  |

| V <sub>SS</sub>                 | SR | Digital ground on VSS_HV pins                                                               |                             | 0                     | 0                                                                                                               | V    |  |

| V <sub>DD</sub> <sup>1</sup>    | SR |                                                                                             | —                           | 4.5                   | 5.5                                                                                                             | V    |  |

|                                 |    | (V <sub>SS</sub> )                                                                          | Voltage drop <sup>2</sup>   | 3.0                   | 5.5                                                                                                             |      |  |

| V <sub>SS_LV</sub> <sup>3</sup> | SR | Voltage on VSS_LV (low voltage digital supply) pins with respect to ground (V $_{\rm SS}$ ) | —                           | V <sub>SS</sub> – 0.1 | V <sub>SS</sub> + 0.1                                                                                           | V    |  |

| V <sub>DD_BV</sub> <sup>4</sup> | SR | Voltage on VDD_BV pin (regulator supply) with                                               | —                           | 4.5                   | 5.5                                                                                                             | V    |  |

|                                 |    | respect to ground (V <sub>SS</sub> )                                                        | Voltage drop <sup>2</sup>   | 3.0                   | 5.5                                                                                                             |      |  |

|                                 |    |                                                                                             | Relative to V <sub>DD</sub> | 3.0                   | V <sub>DD</sub> + 0.1                                                                                           |      |  |

| V <sub>SS_ADC</sub>             | SR | Voltage on VSS_HV_ADC0, VSS_HV_ADC1 (ADC reference) pin with respect to ground ( $V_{SS}$ ) | —                           | V <sub>SS</sub> – 0.1 | V <sub>SS</sub> + 0.1                                                                                           | V    |  |

| Symbo                            | 1  | Parameter                                                             | Conditions                             | Va                    | Max<br>5.5<br>5.5<br>V <sub>DD</sub> + 0.1<br><br>V <sub>DD</sub> + 0.1<br>5<br>50<br>0.25 V/μs | Unit |

|----------------------------------|----|-----------------------------------------------------------------------|----------------------------------------|-----------------------|-------------------------------------------------------------------------------------------------|------|

| Symbol                           |    | Farameter                                                             | Conditions                             | Min                   | Max                                                                                             | Unit |

| V <sub>DD_ADC</sub> <sup>5</sup> | SR | Voltage on VDD_HV_ADC0, VDD_HV_ADC1                                   | —                                      | 4.5                   | 5.5                                                                                             | V    |

|                                  |    | (ADC reference) with respect to ground ( $V_{SS}$ )                   | Voltage drop <sup>2</sup>              | 3.0                   | 5.5                                                                                             |      |

|                                  |    |                                                                       | Relative to V <sub>DD</sub>            | V <sub>DD</sub> - 0.1 | V <sub>DD</sub> + 0.1                                                                           |      |

| V <sub>IN</sub>                  | SR | Voltage on any GPIO pin with respect to ground                        | —                                      | $V_{SS} - 0.1$        | —                                                                                               | V    |

|                                  |    | (V <sub>SS</sub> )                                                    | Relative to V <sub>DD</sub>            | —                     | V <sub>DD</sub> + 0.1                                                                           |      |

| I <sub>INJPAD</sub>              | SR | Injected input current on any pin during overload condition           | -                                      | -5                    | 5                                                                                               | mA   |

| I <sub>INJSUM</sub>              | SR | Absolute sum of all injected input currents during overload condition | -                                      | -50                   | 50                                                                                              |      |

| TV <sub>DD</sub>                 | SR | V <sub>DD</sub> slope to ensure correct power up <sup>6</sup>         | —                                      | 3.0 <sup>7</sup>      | 0.25 V/µs                                                                                       | V/s  |

| T <sub>A C-Grade</sub><br>Part   | SR | Ambient temperature under bias                                        | f <sub>CPU</sub> < 64 MHz <sup>8</sup> | -40                   | 85                                                                                              | °C   |

| T <sub>J C-Grade</sub><br>Part   | SR | Junction temperature under bias                                       | -                                      | -40                   | 110                                                                                             |      |

| T <sub>A V-Grade</sub><br>Part   | SR | Ambient temperature under bias                                        | f <sub>CPU</sub> < 64 MHz <sup>8</sup> | -40                   | 105                                                                                             |      |

| T <sub>J V-Grade</sub><br>Part   | SR | Junction temperature under bias                                       | -                                      | -40                   | 130                                                                                             |      |

| T <sub>A M-Grade</sub><br>Part   | SR | Ambient temperature under bias                                        | f <sub>CPU</sub> < 64 MHz <sup>8</sup> | -40                   | 125                                                                                             |      |

| T <sub>J M</sub> -Grade<br>Part  | SR | Junction temperature under bias                                       | —                                      | -40                   | 150                                                                                             |      |

Table 10. Recommended operating conditions (5.0 V) (continued)

<sup>1</sup> 100 nF capacitance needs to be provided between each  $V_{DD}/V_{SS}$  pair.

<sup>2</sup> Full device operation is guaranteed by design when the voltage drops below 4.5 V down to 3.0 V. However, certain analog electrical characteristics will not be guaranteed to stay within the stated limits.

$^3\,$  330 nF capacitance needs to be provided between each V\_{DD\_LV}/V\_{SS\_LV} supply pair.

<sup>4</sup> 470 nF capacitance needs to be provided between V<sub>DD\_BV</sub> and the nearest V<sub>SS\_LV</sub> (higher value may be needed depending on external regulator characteristics). While the supply voltage ramps up, the slope on V<sub>DD\_BV</sub> should be less than 0.9V<sub>DD\_HV</sub> in order to ensure the device does not enter regulator bypass mode.

$^5\,$  100 nF capacitance needs to be provided between V\_DD\_ADC/V\_{SS\_ADC} pair.

<sup>6</sup> Guaranteed by device validation. Please refer to Section 3.5.1, External ballast resistor recommendations for minimum V<sub>DD</sub> slope to be guaranteed to ensure correct power up in case of external resistor usage.

<sup>7</sup> Minimum value of TV<sub>DD</sub> must be guaranteed until V<sub>DD</sub> reaches 2.6 V (maximum value of V<sub>PORH</sub>).

<sup>8</sup> This frequency includes the 4% frequency modulation guard band.

### NOTE

RAM data retention is guaranteed with  $V_{DD LV}$  not below 1.08 V.

# 3.5 Thermal characteristics

### 3.5.1 External ballast resistor recommendations

External ballast resistor on  $V_{DD_BV}$  pin helps in reducing the overall power dissipation inside the device. This resistor is required only when maximum power consumption exceeds the limit imposed by package thermal characteristics.

As stated in Table 11 LQFP thermal characteristics, considering a thermal resistance of 144 LQFP as 48.3 °C/W, at ambient temperature  $T_A = 125$  °C, the junction temperature  $T_j$  will cross 150 °C if the total power dissipation is greater than (150 - 125)/48.3 = 517 mW. Therefore, the total device current  $I_{DDMAX}$  at 125 °C/5.5 V must not exceed 94.1 mA (i.e., PD/VDD). Assuming an average  $I_{DD}(V_{DD_{-HV}})$  of 15–20 mA consumption typically during device RUN mode, the LV domain consumption  $I_{DD}(V_{DD_{-BV}})$  is thus limited to  $I_{DDMAX} - I_{DD}(V_{DD_{-HV}})$ , i.e., 80 mA.

Therefore, respecting the maximum power allowed as explained in Section 3.5.2, Package thermal characteristics, it is recommended to use this resistor only in the 125 °C/5.5 V operating corner as per the following guidelines:

- If  $I_{DD}(V_{DD BV}) < 80$  mA, then no resistor is required.

- If 80 mA < I\_{DD}(V\_{DD BV}) < 90 mA, then 4  $\Omega$  resistor can be used.

- If  $I_{DD}(V_{DD BV}) > 90$  mA, then 8  $\Omega$  resistor can be used.

Using resistance in the range of 4–8  $\Omega$ , the gain will be around 10–20% of total consumption on V<sub>DD\_BV</sub>. For example, if 8  $\Omega$  resistor is used, then power consumption when I<sub>DD</sub>(V<sub>DD\_BV</sub>) is 110 mA is equivalent to power consumption when I<sub>DD</sub>(V<sub>DD\_BV</sub>) is 90 mA (approximately) when resistor not used.

In order to ensure correct power up, the minimum  $V_{DD_BV}$  to be guaranteed is 30 ms/V. If the supply ramp is slower than this value, then LVDHV3B monitoring ballast supply  $V_{DD_BV}$  pin gets triggered leading to device reset. Until the supply reaches certain threshold, this low voltage monitor generates destructive reset event in the system. This threshold depends on the maximum  $I_{DD}(V_{DD_BV})$  possible across the external resistor.

## **3.5.2 Package thermal characteristics**

### Table 11. LQFP thermal characteristics<sup>1</sup>

| Symb            |    | с | Parameter                                           | Conditions <sup>2</sup> | Pin count |     | Value | )    | Unit |

|-----------------|----|---|-----------------------------------------------------|-------------------------|-----------|-----|-------|------|------|

| Synn            |    | Ŭ | i arameter                                          | Conditions              |           | Min | Тур   | Max  | Onic |

| $R_{\thetaJA}$  | CC | D | Thermal resistance,                                 | Single-layer board — 1s | 100       | —   | _     | 64   | °C/W |

|                 |    |   | junction-to-ambient natural convection <sup>3</sup> |                         | 144       | —   | _     | 64   |      |

|                 |    |   |                                                     |                         | 176       |     |       | 64   |      |

|                 |    |   |                                                     | Four-layer board — 2s2p | 100       |     |       | 49.7 |      |

|                 |    |   |                                                     |                         | 144       | _   |       | 48.3 |      |

|                 |    |   |                                                     | 176                     | _         |     | 47.3  |      |      |

| $R_{\theta JB}$ | СС |   | Thermal resistance,                                 | Single-layer board — 1s | 100       | _   |       | 36   | °C/W |

|                 |    |   | junction-to-board <sup>4</sup>                      | 144                     | 144       | _   |       | 38   |      |

|                 |    |   |                                                     |                         | 176       | _   |       | 38   |      |

|                 |    |   |                                                     | Four-layer board — 2s2p | 100       | _   |       | 33.6 |      |

|                 |    |   |                                                     |                         | 144       | _   | _     | 33.4 |      |

|                 |    |   |                                                     |                         | 176       | _   |       | 33.4 |      |

K is a constant for the particular part, which may be determined from Equation 3 by measuring  $P_D$  (at equilibrium) for a known  $T_A$ . Using this value of K, the values of  $P_D$  and  $T_J$  may be obtained by solving equations 1 and 2 iteratively for any value of  $T_A$ .

## 3.6 I/O pad electrical characteristics

## 3.6.1 I/O pad types

The device provides four main I/O pad types depending on the associated alternate functions:

- Slow pads are the most common pads, providing a good compromise between transition time and low electromagnetic emission.

- Medium pads provide transition fast enough for the serial communication channels with controlled current to reduce electromagnetic emission.

- Fast pads provide maximum speed. These are used for improved debugging capability.

- Input only pads are associated with ADC channels and 32 kHz low power external crystal oscillator providing low input leakage.

Medium and Fast pads can use slow configuration to reduce electromagnetic emission, at the cost of reducing AC performance.

### 3.6.2 I/O input DC characteristics

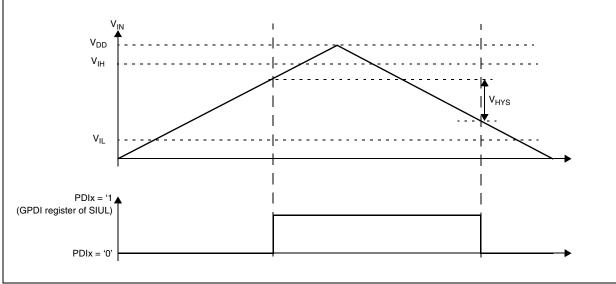

Table 12 provides input DC electrical characteristics as described in Figure 5.

Figure 5. I/O input DC electrical characteristics definition

|          |            |          |        |                      | 176 L   | QFP     |         |         | 144/10  | 0 LQFP  |         |

|----------|------------|----------|--------|----------------------|---------|---------|---------|---------|---------|---------|---------|

| Su       | pply segme | ent      | Pad    | Weigh                | nt 5 V  | Weigh   | t 3.3 V | Weig    | ht 5 V  | Weigh   | t 3.3 V |

| 176 LQFP | 144 LQFP   | 100 LQFP |        | SRC <sup>2</sup> = 0 | SRC = 1 | SRC = 0 | SRC = 1 | SRC = 0 | SRC = 1 | SRC = 0 | SRC = 1 |

| 1        | —          | -        | PH[15] | 2%                   | 3%      | 3%      | 3%      | —       | —       | —       | _       |

|          |            |          | PH[13] | 3%                   | 4%      | 3%      | 4%      | —       | —       | —       |         |

|          | —          |          | PH[14] | 3%                   | 4%      | 4%      | 4%      | —       | —       | —       | _       |

|          | —          | _        | PI[6]  | 4%                   | _       | 4%      | _       | _       | —       | —       | _       |

|          | —          |          | PI[7]  | 4%                   |         | 4%      | —       | _       | —       | —       | _       |

|          | 4          | _        | PG[5]  | 4%                   | _       | 5%      | _       | 10%     | —       | 12%     | _       |

|          |            | _        | PG[4]  | 4%                   | 6%      | 5%      | 5%      | 9%      | 13%     | 11%     | 12%     |

|          |            |          | PG[3]  | 4%                   |         | 5%      | —       | 9%      | —       | 11%     | _       |

|          |            | _        | PG[2]  | 4%                   | 6%      | 5%      | 5%      | 9%      | 12%     | 10%     | 11%     |

|          |            | 4        | PA[2]  | 4%                   | _       | 5%      | _       | 8%      | —       | 10%     | _       |

|          |            |          | PE[0]  | 4%                   |         | 5%      | —       | 8%      | —       | 9%      | _       |

|          |            |          | PA[1]  | 4%                   | _       | 5%      | _       | 8%      | —       | 9%      | _       |

|          |            |          | PE[1]  | 4%                   | 6%      | 5%      | 6%      | 7%      | 10%     | 9%      | 9%      |

|          |            |          | PE[8]  | 4%                   | 6%      | 5%      | 6%      | 7%      | 10%     | 8%      | 9%      |

|          |            |          | PE[9]  | 4%                   | _       | 5%      | _       | 6%      | _       | 8%      | —       |

|          |            |          | PE[10] | 4%                   |         | 5%      |         | 6%      |         | 7%      | —       |

|          |            |          | PA[0]  | 4%                   | 6%      | 5%      | 5%      | 6%      | 8%      | 7%      | 7%      |

|          |            |          | PE[11] | 4%                   |         | 5%      | —       | 5%      | —       | 6%      | —       |

## Table 20. I/O weight<sup>1</sup> (continued)

| <b>C</b> 11 | pply segme |          |        |                      | 176 L   | QFP     |         |         | 144/10  | 0 LQFP  |         |     |     |     |     |

|-------------|------------|----------|--------|----------------------|---------|---------|---------|---------|---------|---------|---------|-----|-----|-----|-----|

| Su          | pply segme | ent      | Pad    | Weigh                | nt 5 V  | Weigh   | t 3.3 V | Weig    | ht 5 V  | Weigh   | t 3.3 V |     |     |     |     |

| 176 LQFP    | 144 LQFP   | 100 LQFP |        | SRC <sup>2</sup> = 0 | SRC = 1 | SRC = 0 | SRC = 1 | SRC = 0 | SRC = 1 | SRC = 0 | SRC = 1 |     |     |     |     |

| 2           | 1          |          | PG[9]  | 9%                   |         | 10%     | —       | 9%      | —       | 10%     | —       |     |     |     |     |

|             |            | _        | PG[8]  | 9%                   |         | 11%     | _       | 9%      | —       | 11%     | —       |     |     |     |     |

|             |            | 1        | PC[11] | 9%                   | _       | 11%     | _       | 9%      | —       | 11%     | —       |     |     |     |     |

|             |            |          | PC[10] | 9%                   | 13%     | 11%     | 12%     | 9%      | 13%     | 11%     | 12%     |     |     |     |     |

|             |            | _        | PG[7]  | 9%                   | _       | 11%     | —       | 9%      | —       | 11%     | —       |     |     |     |     |

|             |            | _        | PG[6]  | 10%                  | 14%     | 11%     | 12%     | 10%     | 14%     | 11%     | 12%     |     |     |     |     |

|             |            | 1        | PB[0]  | 10%                  | 14%     | 12%     | 12%     | 10%     | 14%     | 12%     | 12%     |     |     |     |     |

|             |            |          | PB[1]  | 10%                  | _       | 12%     | —       | 10%     | —       | 12%     | —       |     |     |     |     |

|             |            | _        | PF[9]  | 10%                  |         | 12%     | —       | 10%     | —       | 12%     | —       |     |     |     |     |

|             |            | _        | PF[8]  | 10%                  | 14%     | 12%     | 13%     | 10%     | 14%     | 12%     | 13%     |     |     |     |     |

|             |            |          |        |                      |         | _       | PF[12]  | 10%     | 15%     | 12%     | 13%     | 10% | 15% | 12% | 13% |

|             |            |          |        |                      |         | 1       | PC[6]   | 10%     | _       | 12%     | _       | 10% | —   | 12% | —   |

|             |            |          | PC[7]  | 10%                  | _       | 12%     | —       | 10%     | —       | 12%     | —       |     |     |     |     |

|             |            | _        | PF[10] | 10%                  | 14%     | 11%     | 12%     | 10%     | 14%     | 11%     | 12%     |     |     |     |     |

|             |            | _        | PF[11] | 9%                   | _       | 11%     | _       | 9%      | —       | 11%     | —       |     |     |     |     |

|             |            | 1        | PA[15] | 8%                   | 12%     | 10%     | 10%     | 8%      | 12%     | 10%     | 10%     |     |     |     |     |

|             |            | _        | PF[13] | 8%                   |         | 10%     |         | 8%      |         | 10%     | —       |     |     |     |     |

|             |            | 1        | PA[14] | 8%                   | 11%     | 9%      | 10%     | 8%      | 11%     | 9%      | 10%     |     |     |     |     |

|             |            |          | PA[4]  | 7%                   |         | 9%      |         | 7%      | —       | 9%      | —       |     |     |     |     |

|             |            |          | PA[13] | 7%                   | 10%     | 8%      | 9%      | 7%      | 10%     | 8%      | 9%      |     |     |     |     |

|             |            |          | PA[12] | 7%                   |         | 8%      | —       | 7%      | —       | 8%      |         |     |     |     |     |

# Table 20. I/O weight<sup>1</sup> (continued)

| <b>C</b> |            |          |        |                      | 176 L   | QFP     |         |         | 144/10  | ) LQFP  |         |

|----------|------------|----------|--------|----------------------|---------|---------|---------|---------|---------|---------|---------|

| Su       | pply segme | ent      | Pad    | Weigh                | nt 5 V  | Weigh   | t 3.3 V | Weig    | ht 5 V  | Weigh   | t 3.3 V |

| 176 LQFP | 144 LQFP   | 100 LQFP |        | SRC <sup>2</sup> = 0 | SRC = 1 | SRC = 0 | SRC = 1 | SRC = 0 | SRC = 1 | SRC = 0 | SRC = 1 |

| 3        | 2          | 2        | PB[9]  | 1%                   | —       | 1%      | —       | 1%      | _       | 1%      | _       |

|          |            |          | PB[8]  | 1%                   | —       | 1%      |         | 1%      |         | 1%      |         |

|          |            |          | PB[10] | 5%                   | _       | 6%      | _       | 6%      | _       | 7%      | _       |

|          |            | —        | PF[0]  | 5%                   | _       | 6%      | _       | 6%      | _       | 8%      | _       |

|          |            | _        | PF[1]  | 5%                   | _       | 6%      | _       | 7%      | _       | 8%      |         |

|          |            | —        | PF[2]  | 6%                   | _       | 7%      | _       | 7%      | _       | 9%      | _       |

|          |            | _        | PF[3]  | 6%                   | —       | 7%      | —       | 8%      | _       | 9%      | _       |

|          |            | _        | PF[4]  | 6%                   | _       | 7%      | _       | 8%      | _       | 10%     |         |

|          |            | _        | PF[5]  | 6%                   | —       | 7%      | —       | 9%      | _       | 10%     | _       |

|          |            | _        | PF[6]  | 6%                   | —       | 7%      | —       | 9%      | _       | 11%     | _       |

|          |            |          | PF[7]  | 6%                   | —       | 7%      | —       | 9%      | _       | 11%     | _       |

|          | _          | —        | PJ[3]  | 6%                   | —       | 7%      | —       | —       | _       | —       | _       |

|          | _          | —        | PJ[2]  | 6%                   | —       | 7%      | —       | —       | _       | —       | _       |

|          | _          | —        | PJ[1]  | 6%                   | —       | 7%      | —       | —       | _       | —       | _       |

|          | _          | —        | PJ[0]  | 6%                   | —       | 7%      | —       | —       | _       | —       | _       |

|          | _          | —        | PI[15] | 6%                   | —       | 7%      | —       | —       | _       | —       | _       |

|          | _          | —        | PI[14] | 6%                   | —       | 7%      | —       | —       | _       | —       | _       |

|          | 2          | 2        | PD[0]  | 1%                   | —       | 1%      | —       | 1%      | _       | 1%      | _       |

|          |            |          | PD[1]  | 1%                   | —       | 1%      | —       | 1%      | _       | 1%      | _       |

|          |            |          | PD[2]  | 1%                   | —       | 1%      | —       | 1%      | _       | 1%      | _       |

|          |            |          | PD[3]  | 1%                   | —       | 1%      | _       | 1%      | _       | 1%      | _       |

|          |            |          | PD[4]  | 1%                   |         | 1%      | —       | 1%      |         | 1%      | _       |

|          |            |          | PD[5]  | 1%                   |         | 1%      |         | 1%      |         | 1%      | _       |

|          |            |          | PD[6]  | 1%                   |         | 1%      | —       | 1%      |         | 2%      |         |

|          |            |          | PD[7]  | 1%                   | _       | 1%      | _       | 1%      | _       | 2%      | _       |

## Table 20. I/O weight<sup>1</sup> (continued)

| <b>C</b> 11 |            |          |        |                      | 176 L   | QFP     |         |         | 144/10  | 0 LQFP  |         |

|-------------|------------|----------|--------|----------------------|---------|---------|---------|---------|---------|---------|---------|

| Su          | pply segme | ent      | Pad    | Weigh                | nt 5 V  | Weigh   | t 3.3 V | Weig    | ht 5 V  | Weigh   | t 3.3 V |

| 176 LQFP    | 144 LQFP   | 100 LQFP |        | SRC <sup>2</sup> = 0 | SRC = 1 | SRC = 0 | SRC = 1 | SRC = 0 | SRC = 1 | SRC = 0 | SRC = 1 |

| 5           | 3          |          | PF[15] | 4%                   | _       | 4%      | —       | 4%      | _       | 4%      | _       |

|             |            |          | PF[14] | 4%                   | 6%      | 5%      | 5%      | 4%      | 6%      | 5%      | 5%      |

|             |            | _        | PE[13] | 4%                   | _       | 5%      | —       | 4%      | _       | 5%      | _       |

|             |            | 3        | PA[7]  | 5%                   | _       | 6%      | _       | 5%      | _       | 6%      | _       |

|             |            |          | PA[8]  | 5%                   | _       | 6%      |         | 5%      |         | 6%      |         |

|             |            |          | PA[9]  | 6%                   | _       | 7%      | _       | 6%      | _       | 7%      | _       |

|             |            |          | PA[10] | 6%                   | _       | 8%      | _       | 6%      | _       | 8%      | _       |

|             |            |          | PA[11] | 8%                   | _       | 9%      |         | 8%      |         | 9%      |         |

|             |            |          | PE[12] | 8%                   | _       | 9%      | _       | 8%      | _       | 9%      | _       |

|             |            |          | PG[14] | 8%                   | _       | 9%      | _       | 8%      | _       | 9%      | _       |

|             |            | _        | PG[15] | 8%                   | 11%     | 9%      | 10%     | 8%      | 11%     | 9%      | 10%     |

|             |            | _        | PE[14] | 8%                   | _       | 9%      | _       | 8%      | _       | 9%      | _       |

|             |            |          | PE[15] | 8%                   | 11%     | 9%      | 10%     | 8%      | 11%     | 9%      | 10%     |

|             |            | _        | PG[10] | 8%                   | _       | 9%      |         | 8%      | _       | 9%      | _       |

|             |            |          | PG[11] | 7%                   | 11%     | 9%      | 9%      | 7%      | 11%     | 9%      | 9%      |

|             |            |          | PH[11] | 7%                   | 10%     | 9%      | 9%      | —       | _       | —       | _       |

|             | _          | _        | PH[12] | 7%                   | 10%     | 8%      | 9%      |         |         |         |         |

|             | _          |          | PI[5]  | 7%                   | _       | 8%      | _       | —       | _       | —       | _       |

|             | _          |          | PI[4]  | 7%                   | _       | 8%      | _       | —       | _       | —       | _       |

|             | 3          | 3        | PC[3]  | 6%                   | _       | 8%      | _       | 6%      | _       | 8%      | _       |

|             |            |          | PC[2]  | 6%                   | 8%      | 7%      | 7%      | 6%      | 8%      | 7%      | 7%      |

|             |            |          | PA[5]  | 6%                   | 8%      | 7%      | 7%      | 6%      | 8%      | 7%      | 7%      |

|             |            |          | PA[6]  | 5%                   | _       | 6%      | —       | 5%      |         | 6%      |         |

|             |            |          | PH[10] | 5%                   | 7%      | 6%      | 6%      | 5%      | 7%      | 6%      | 6%      |

|             |            |          | PC[1]  | 5%                   | 19%     | 5%      | 13%     | 5%      | 19%     | 5%      | 13%     |

Table 20. I/O weight<sup>1</sup> (continued)

| 0        |            |          |        |                      | 176 L   | QFP     |         |         | 144/10  | 0 LQFP  |         |

|----------|------------|----------|--------|----------------------|---------|---------|---------|---------|---------|---------|---------|

| Su       | pply segme | ent      | Pad    | Weigh                | nt 5 V  | Weigh   | t 3.3 V | Weig    | ht 5 V  | Weigh   | t 3.3 V |

| 176 LQFP | 144 LQFP   | 100 LQFP |        | SRC <sup>2</sup> = 0 | SRC = 1 | SRC = 0 | SRC = 1 | SRC = 0 | SRC = 1 | SRC = 0 | SRC = 1 |

| 6        | 4          | 4        | PC[0]  | 6%                   | 9%      | 7%      | 8%      | 7%      | 10%     | 8%      | 8%      |

|          |            |          | PH[9]  | 7%                   | —       | 8%      | —       | 7%      | —       | 9%      | _       |

|          |            |          | PE[2]  | 7%                   | 10%     | 8%      | 9%      | 8%      | 11%     | 9%      | 10%     |

|          |            |          | PE[3]  | 7%                   | 10%     | 9%      | 9%      | 8%      | 12%     | 10%     | 10%     |

|          |            |          | PC[5]  | 7%                   | 11%     | 9%      | 9%      | 8%      | 12%     | 10%     | 11%     |

|          |            |          | PC[4]  | 8%                   | 11%     | 9%      | 10%     | 9%      | 13%     | 10%     | 11%     |

|          |            |          | PE[4]  | 8%                   | 11%     | 9%      | 10%     | 9%      | 13%     | 11%     | 12%     |

|          |            |          | PE[5]  | 8%                   | 11%     | 10%     | 10%     | 9%      | 14%     | 11%     | 12%     |

|          |            |          | PH[4]  | 8%                   | 12%     | 10%     | 10%     | 10%     | 14%     | 12%     | 12%     |

|          |            |          | PH[5]  | 8%                   | —       | 10%     | —       | 10%     | —       | 12%     | _       |

|          |            | —        | PH[6]  | 8%                   | 12%     | 10%     | 11%     | 10%     | 15%     | 12%     | 13%     |

|          |            | —        | PH[7]  | 9%                   | 12%     | 10%     | 11%     | 11%     | 15%     | 13%     | 13%     |

|          |            | —        | PH[8]  | 9%                   | 12%     | 10%     | 11%     | 11%     | 16%     | 13%     | 14%     |

|          |            | 4        | PE[6]  | 9%                   | 12%     | 10%     | 11%     | 11%     | 16%     | 13%     | 14%     |

|          |            |          | PE[7]  | 9%                   | 12%     | 10%     | 11%     | 11%     | 16%     | 14%     | 14%     |

|          | _          |          | PI[3]  | 9%                   | —       | 10%     | —       | —       | —       | —       | _       |

|          | _          | _        | PI[2]  | 9%                   | —       | 10%     | —       | —       | —       | —       | _       |

|          | _          |          | PI[1]  | 9%                   | —       | 10%     | —       | —       | —       | —       | _       |

|          | —          | —        | PI[0]  | 9%                   | —       | 10%     | —       | —       | —       | —       | —       |

|          | 4          | 4        | PC[12] | 8%                   | 12%     | 10%     | 11%     | 12%     | 18%     | 15%     | 16%     |

|          |            |          | PC[13] | 8%                   | —       | 10%     | —       | 13%     | —       | 15%     | —       |

|          |            |          | PC[8]  | 8%                   | —       | 10%     | —       | 13%     | —       | 15%     | —       |

|          |            |          | PB[2]  | 8%                   | 11%     | 9%      | 10%     | 13%     | 18%     | 15%     | 16%     |

Table 20. I/O weight<sup>1</sup> (continued)

<sup>1</sup>  $V_{DD} = 3.3 \text{ V} \pm 10\% / 5.0 \text{ V} \pm 10\%$ ,  $T_A = -40$  to 125 °C, unless otherwise specified <sup>2</sup> SRC is the Slew Rate Control bit in SIU\_PCR*x*

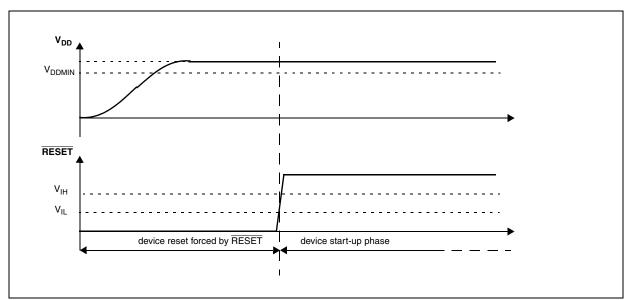

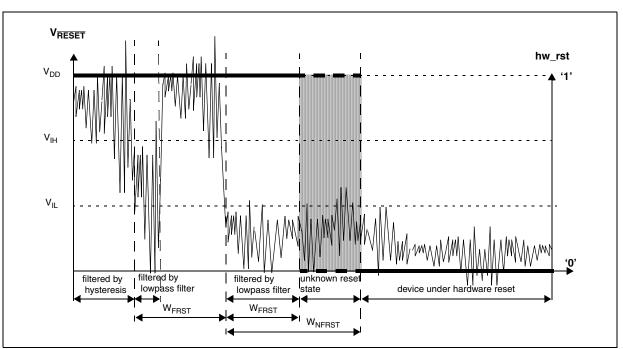

#### **RESET** electrical characteristics 3.7

The device implements a dedicated bidirectional  $\overline{\text{RESET}}$  pin.

Figure 6. Start-up reset requirements

Figure 7. Noise filtering on reset signal

Table 21. Reset electrical characteristics

| Symbol          | с  | Parameter | Conditions <sup>1</sup>                    | onditions <sup>1</sup> |                     |  |                       |   |  |

|-----------------|----|-----------|--------------------------------------------|------------------------|---------------------|--|-----------------------|---|--|

| C y III.        |    | Ū         |                                            | Conditione             | Min Typ Max         |  | Unit                  |   |  |

| V <sub>IH</sub> | SR |           | Input High Level CMOS<br>(Schmitt Trigger) | _                      | 0.65V <sub>DD</sub> |  | V <sub>DD</sub> + 0.4 | V |  |

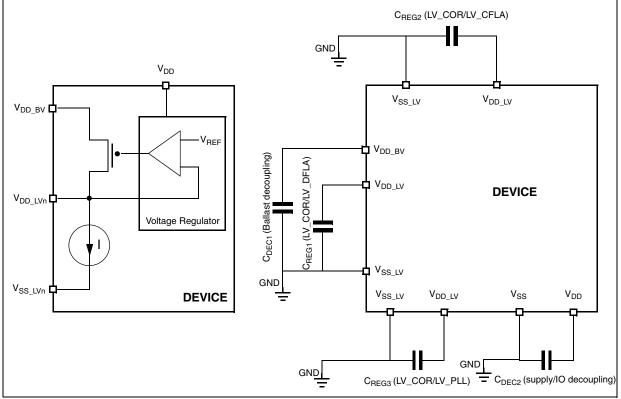

## 3.8 Power management electrical characteristics

### 3.8.1 Voltage regulator electrical characteristics

The device implements an internal voltage regulator to generate the low voltage core supply  $V_{DD_LV}$  from the high voltage ballast supply  $V_{DD_BV}$ . The regulator itself is supplied by the common I/O supply  $V_{DD}$ . The following supplies are involved:

- HV: High voltage external power supply for voltage regulator module. This must be provided externally through V<sub>DD</sub> power pin.

- BV: High voltage external power supply for internal ballast module. This must be provided externally through  $V_{DD_BV}$  power pin. Voltage values should be aligned with  $V_{DD}$ .

- LV: Low voltage internal power supply for core, FMPLL and Flash digital logic. This is generated by the internal voltage regulator but provided outside to connect stability capacitor. It is further split into four main domains to ensure noise isolation between critical LV modules within the device:

- LV\_COR: Low voltage supply for the core. It is also used to provide supply for FMPLL through double bonding.

- LV\_CFLA: Low voltage supply for code Flash module. It is supplied with dedicated ballast and shorted to LV\_COR through double bonding.

- LV\_DFLA: Low voltage supply for data Flash module. It is supplied with dedicated ballast and shorted to LV\_COR through double bonding.

- LV\_PLL: Low voltage supply for FMPLL. It is shorted to LV\_COR through double bonding.

Figure 8. Voltage regulator capacitance connection

The internal voltage regulator requires external capacitance ( $C_{REGn}$ ) to be connected to the device in order to provide a stable low voltage digital supply to the device. Capacitances should be placed on the board as near as possible to the associated pins. Care should also be taken to limit the serial inductance of the board to less than 5 nH.

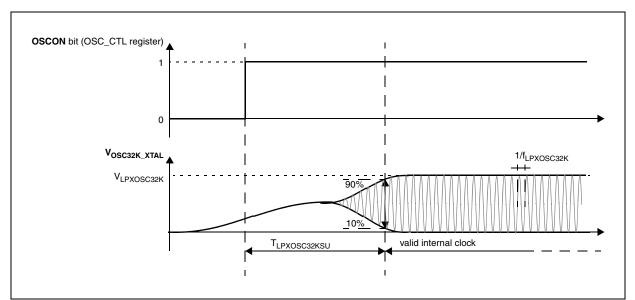

Figure 16. Slow external crystal oscillator (32 kHz) electrical characteristics

| Symbol                 |    | ~ | Deveneter                                      | Conditions <sup>1</sup> |     | Value  |                | Unit |

|------------------------|----|---|------------------------------------------------|-------------------------|-----|--------|----------------|------|

| Symbol                 |    | С | Parameter                                      | Conditions              | Min | Тур    | Max            | Unit |

| f <sub>SXOSC</sub>     | SR |   | Slow external crystal oscillator<br>frequency  |                         | 32  | 32.768 | 40             | kHz  |

| V <sub>SXOSC</sub>     | СС | Т | Oscillation amplitude                          | _                       | —   | 2.1    | —              | V    |

| I <sub>SXOSCBIAS</sub> | СС | Т | Oscillation bias current                       | _                       |     | 2.5    |                | μA   |

| I <sub>SXOSC</sub>     | СС | Т | Slow external crystal oscillator consumption   |                         | _   | —      | 8              | μA   |

| T <sub>SXOSCSU</sub>   | СС | Т | Slow external crystal oscillator start-up time |                         | —   | —      | 2 <sup>2</sup> | S    |

V<sub>DD</sub> = 3.3 V ± 10% / 5.0 V ± 10%, T<sub>A</sub> = -40 to 125 °C, unless otherwise specified

Start-up time has been measured with EPSON TOYOCOM MC306 crystal. Variation may be seen with other crystal.

#### **FMPLL** electrical characteristics 3.14

The device provides a frequency modulated phase locked loop (FMPLL) module to generate a fast system clock from the FXOSC or FIRC sources.

| Symbo              | al | с | Parameter                                     | Conditions <sup>1</sup> |     | Value |     | Unit  |

|--------------------|----|---|-----------------------------------------------|-------------------------|-----|-------|-----|-------|

| Symbo              | 01 | Ŭ | i arameter                                    | Conditions              | Min | Тур   | Max | 01111 |

| f <sub>PLLIN</sub> | SR | _ | FMPLL reference clock <sup>2</sup>            | _                       | 4   |       | 64  | MHz   |

| $\Delta_{PLLIN}$   | SR |   | FMPLL reference clock duty cycle <sup>2</sup> | _                       | 40  | —     | 60  | %     |

| Symbol                     |    | с | Parameter                                                     | Conditions              |                                                          | Value                     | Unit |

|----------------------------|----|---|---------------------------------------------------------------|-------------------------|----------------------------------------------------------|---------------------------|------|

|                            |    | Ŭ | rarameter                                                     |                         |                                                          | Тур                       |      |

| I <sub>DD_HV_ADC1</sub>    | СС | Т | ADC_1 supply current on                                       | V <sub>DD</sub> = 5.5 V | Analog static consumption (no conversion)                | 300 * f <sub>periph</sub> | μA   |

|                            |    |   | V <sub>DD_HV_ADC1</sub>                                       | V <sub>DD</sub> = 5.5 V | Analog dynamic<br>consumption (continuous<br>conversion) | 4                         | mA   |

| I <sub>DD_HV</sub> (FLASH) | CC |   | CFlash +<br>DFlash supply<br>current on<br>V <sub>DD_HV</sub> | V <sub>DD</sub> = 5.5 V | _                                                        | 12                        | mA   |

| I <sub>DD_BV(PLL)</sub>    | СС | Т | PLL supply<br>current on<br>V <sub>DD_BV</sub>                | V <sub>DD</sub> = 5.5 V | _                                                        | 2.5                       | mA   |

Table 43. On-chip peripherals current consumption<sup>1</sup> (continued)

<sup>1</sup> Operating conditions:  $T_A = 25$  °C,  $f_{periph} = 8$  MHz to 64 MHz

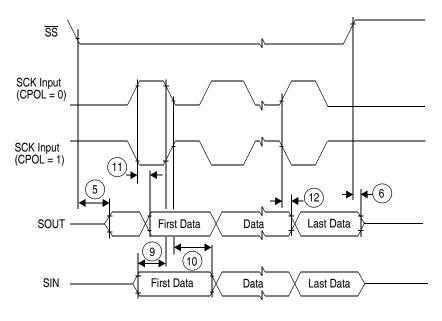

Note: Numbers shown reference Table 44.

Note: Numbers shown reference Table 44.

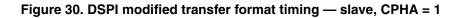

Figure 31. DSPI PCS strobe (PCSS) timing

### 3.18.3 JTAG characteristics

#### Table 45. JTAG characteristics

| No. | Symbol            |    | с | Parameter      | Value |     |     | Unit |

|-----|-------------------|----|---|----------------|-------|-----|-----|------|

| NO. |                   |    |   | i arameter     | Min   | Тур | Max | Onit |

| 1   | t <sub>JCYC</sub> | CC | D | TCK cycle time | 64    | _   | _   | ns   |

| 2   | t <sub>TDIS</sub> | СС | D | TDI setup time | 15    | _   | _   | ns   |

| 3   | t <sub>TDIH</sub> | CC | D | TDI hold time  | 5     | _   | _   | ns   |