#### Intel - EP4CE55F23A7N Datasheet

Welcome to <u>E-XFL.COM</u>

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

#### Details

| Product Status                 | Active                                                   |

|--------------------------------|----------------------------------------------------------|

| Number of LABs/CLBs            | 3491                                                     |

| Number of Logic Elements/Cells | 55856                                                    |

| Total RAM Bits                 | 2396160                                                  |

| Number of I/O                  | 324                                                      |

| Number of Gates                | -                                                        |

| Voltage - Supply               | 1.15V ~ 1.25V                                            |

| Mounting Type                  | Surface Mount                                            |

| Operating Temperature          | -40°C ~ 125°C (TJ)                                       |

| Package / Case                 | 484-BGA                                                  |

| Supplier Device Package        | 484-FBGA (23x23)                                         |

| Purchase URL                   | https://www.e-xfl.com/product-detail/intel/ep4ce55f23a7n |

|                                |                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 1. Cyclone IV FPGA Device Family Overview

Altera's new Cyclone<sup>®</sup> IV FPGA device family extends the Cyclone FPGA series leadership in providing the market's lowest-cost, lowest-power FPGAs, now with a transceiver variant. Cyclone IV devices are targeted to high-volume, cost-sensitive applications, enabling system designers to meet increasing bandwidth requirements while lowering costs.

Built on an optimized low-power process, the Cyclone IV device family offers the following two variants:

- Cyclone IV E—lowest power, high functionality with the lowest cost

- Cyclone IV GX—lowest power and lowest cost FPGAs with 3.125 Gbps transceivers

Cyclone IV E devices are offered in core voltage of 1.0 V and 1.2 V.

**To** For more information, refer to the *Power Requirements for Cyclone IV Devices* chapter.

Providing power and cost savings without sacrificing performance, along with a low-cost integrated transceiver option, Cyclone IV devices are ideal for low-cost, small-form-factor applications in the wireless, wireline, broadcast, industrial, consumer, and communications industries.

## **Cyclone IV Device Family Features**

The Cyclone IV device family offers the following features:

- Low-cost, low-power FPGA fabric:

- 6K to 150K logic elements

- Up to 6.3 Mb of embedded memory

- Up to 360 18 × 18 multipliers for DSP processing intensive applications

- Protocol bridging applications for under 1.5 W total power

<sup>© 2016</sup> Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

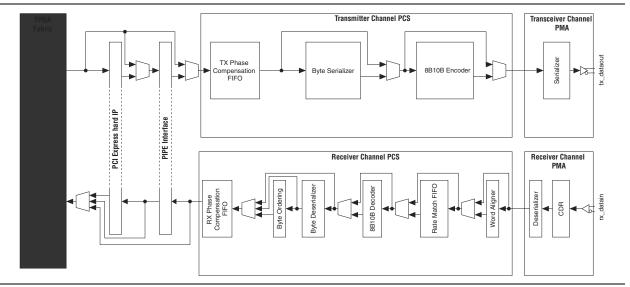

- Cyclone IV GX devices offer up to eight high-speed transceivers that provide:

- Data rates up to 3.125 Gbps

- 8B/10B encoder/decoder

- 8-bit or 10-bit physical media attachment (PMA) to physical coding sublayer (PCS) interface

- Byte serializer / deserializer (SERDES)

- Word aligner

- Rate matching FIFO

- TX bit slipper for Common Public Radio Interface (CPRI)

- Electrical idle

- Dynamic channel reconfiguration allowing you to change data rates and protocols on-the-fly

- Static equalization and pre-emphasis for superior signal integrity

- 150 mW per channel power consumption

- Flexible clocking structure to support multiple protocols in a single transceiver block

- Cyclone IV GX devices offer dedicated hard IP for PCI Express (PIPE) (PCIe) Gen 1:

- ×1, ×2, and ×4 lane configurations

- End-point and root-port configurations

- Up to 256-byte payload

- One virtual channel

- 2 KB retry buffer

- 4 KB receiver (Rx) buffer

- Cyclone IV GX devices offer a wide range of protocol support:

- PCIe (PIPE) Gen 1 ×1, ×2, and ×4 (2.5 Gbps)

- Gigabit Ethernet (1.25 Gbps)

- CPRI (up to 3.072 Gbps)

- XAUI (3.125 Gbps)

- Triple rate serial digital interface (SDI) (up to 2.97 Gbps)

- Serial RapidIO (3.125 Gbps)

- Basic mode (up to 3.125 Gbps)

- V-by-One (up to 3.0 Gbps)

- DisplayPort (2.7 Gbps)

- Serial Advanced Technology Attachment (SATA) (up to 3.0 Gbps)

- OBSAI (up to 3.072 Gbps)

- Up to 532 user I/Os

- LVDS interfaces up to 840 Mbps transmitter (Tx), 875 Mbps Rx

- Support for DDR2 SDRAM interfaces up to 200 MHz

- Support for QDRII SRAM and DDR SDRAM up to 167 MHz

- Up to eight phase-locked loops (PLLs) per device

- Offered in commercial and industrial temperature grades

## **Device Resources**

Table 1–1 lists Cyclone IV E device resources.

Table 1–1. Resources for the Cyclone IV E Device Family

| Resources                       | EP4CE6 | EP4CE10 | EP4CE15 | EP4CE22 | EP4CE30 | EP4CE40 | EP4CE55 | EP4CE75 | EP4CE115 |

|---------------------------------|--------|---------|---------|---------|---------|---------|---------|---------|----------|

| Logic elements (LEs)            | 6,272  | 10,320  | 15,408  | 22,320  | 28,848  | 39,600  | 55,856  | 75,408  | 114,480  |

| Embedded memory<br>(Kbits)      | 270    | 414     | 504     | 594     | 594     | 1,134   | 2,340   | 2,745   | 3,888    |

| Embedded 18 × 18<br>multipliers | 15     | 23      | 56      | 66      | 66      | 116     | 154     | 200     | 266      |

| General-purpose PLLs            | 2      | 2       | 4       | 4       | 4       | 4       | 4       | 4       | 4        |

| Global Clock Networks           | 10     | 10      | 20      | 20      | 20      | 20      | 20      | 20      | 20       |

| User I/O Banks                  | 8      | 8       | 8       | 8       | 8       | 8       | 8       | 8       | 8        |

| Maximum user I/O (1)            | 179    | 179     | 343     | 153     | 532     | 532     | 374     | 426     | 528      |

Note to Table 1-1:

(1) The user I/Os count from pin-out files includes all general purpose I/O, dedicated clock pins, and dual purpose configuration pins. Transceiver pins and dedicated configuration pins are not included in the pin count.

Table 1–2 lists Cyclone IV GX device resources.

| Resources                            | EP4CGX15 | EP4CGX22 | EP4CGX30 | EP4CGX30<br>(2)   | EP4CGX50          | EP4CGX75          | EP4CGX110         | EP4CGX150     |

|--------------------------------------|----------|----------|----------|-------------------|-------------------|-------------------|-------------------|---------------|

| Logic elements (LEs)                 | 14,400   | 21,280   | 29,440   | 29,440            | 49,888            | 73,920            | 109,424           | 149,760       |

| Embedded memory (Kbits)              | 540      | 756      | 1,080    | 1,080             | 2,502             | 4,158             | 5,490             | 6,480         |

| Embedded 18 × 18 multipliers         | 0        | 40       | 80       | 80                | 140               | 198               | 280               | 360           |

| General purpose PLLs                 | 1        | 2        | 2        | 4 <i>(4)</i>      | 4 (4)             | 4 (4)             | 4 (4)             | 4 <i>(4)</i>  |

| Multipurpose PLLs                    | 2 (5)    | 2 (5)    | 2 (5)    | 2 (5)             | 4 (5)             | 4 (5)             | 4 (5)             | 4 (5)         |

| Global clock networks                | 20       | 20       | 20       | 30                | 30                | 30                | 30                | 30            |

| High-speed transceivers (6)          | 2        | 4        | 4        | 4                 | 8                 | 8                 | 8                 | 8             |

| Transceiver maximum data rate (Gbps) | 2.5      | 2.5      | 2.5      | 3.125             | 3.125             | 3.125             | 3.125             | 3.125         |

| PCIe (PIPE) hard IP blocks           | 1        | 1        | 1        | 1                 | 1                 | 1                 | 1                 | 1             |

| User I/O banks                       | g (7)    | g (7)    | g (7)    | 11 <sup>(8)</sup> | 11 <sup>(8)</sup> | 11 <sup>(8)</sup> | 11 <sup>(8)</sup> | 11 <i>(8)</i> |

| Maximum user I/O <sup>(9)</sup>      | 72       | 150      | 150      | 290               | 310               | 310               | 475               | 475           |

Table 1–2. Resources for the Cyclone IV GX Device Family

Notes to Table 1-2:

(1) Applicable for the F169 and F324 packages.

(2) Applicable for the F484 package.

(3) Only two multipurpose PLLs for F484 package.

(4) Two of the general purpose PLLs are able to support transceiver clocking. For more information, refer to the *Clock Networks and PLLs in Cyclone IV Devices* chapter.

(5) You can use the multipurpose PLLs for general purpose clocking when they are not used to clock the transceivers. For more information, refer to the *Clock Networks and PLLs in Cyclone IV Devices* chapter.

(6) If PCIe ×1, you can use the remaining transceivers in a quad for other protocols at the same or different data rates.

(7) Including one configuration I/O bank and two dedicated clock input I/O banks for HSSI reference clock input.

(8) Including one configuration I/O bank and four dedicated clock input I/O banks for HSSI reference clock input.

(9) The user I/Os count from pin-out files includes all general purpose I/O, dedicated clock pins, and dual purpose configuration pins. Transceiver pins and dedicated configuration pins are not included in the pin count.

# **Package Matrix**

Table 1–3 lists Cyclone IV E device package offerings.

| Table 1–3. I | Package Offering | s for the Cyclon | e IV E Device Family <sup>(1),</sup> <sup>(2)</sup> |

|--------------|------------------|------------------|-----------------------------------------------------|

|--------------|------------------|------------------|-----------------------------------------------------|

| Package    |   | E14         | 44                  | M1       | 64      | M2       | 256     | U2           | 56      | F2           | 56      | F3           | 24      | U4           | 84      | F4           | 84      | F7           | '80                 |

|------------|---|-------------|---------------------|----------|---------|----------|---------|--------------|---------|--------------|---------|--------------|---------|--------------|---------|--------------|---------|--------------|---------------------|

| Size (mm)  |   | <b>22</b> × | : 22                | 8 >      | < 8     | 9 3      | k 9     | 14 >         | « 14    | 17 :         | × 17    | 19 3         | x 19    | 19 :         | × 19    | <b>23</b> :  | × 23    | <b>29</b> :  | × 29                |

| Pitch (mm) |   | 0.          | 5                   | 0.       | .5      | 0.       | .5      | 0.           | .8      | 1            | .0      | 1.           | .0      | 0,           | .8      | 1            | .0      | 1            | .0                  |

| Device     |   | User I/O    | LVDS <sup>(3)</sup> | User I/O | (s) San | User I/O | (E) Sav | User I/O     | (s) San | User I/O     | (s) San | User I/O     | (8) San | User I/O     | (S) SOA | User I/O     | (s) San | User I/O     | LVDS <sup>(3)</sup> |

| EP4CE6     | 4 | 91          | 21                  | —        | _       | —        | _       | <b>▲</b> 179 | 66      | <b>▲</b> 179 | 66      | _            | _       |              | _       | _            | —       | —            | —                   |

| EP4CE10    |   | 91          | 21                  | _        | _       | —        | _       | 179          | 66      | 179          | 66      | _            | _       | _            | _       | _            | —       | —            | —                   |

| EP4CE15    |   | 81          | 18                  | 89       | 21      | 165      | 53      | 165          | 53      | 165          | 53      | —            | _       | _            | — .     | <b>▲</b> 343 | 137     | —            | —                   |

| EP4CE22    |   | 79          | 17                  | _        | _       | —        | _       | <b>▼</b> 153 | 52      | <b>▼</b> 153 | 52      | _            | _       | _            | _       | —            | —       | —            | —                   |

| EP4CE30    |   | —           |                     |          | _       | —        | _       | _            | _       | _            | —       | <b>▲</b> 193 | 68      |              | _       | 328          | 124     | <b>◆</b> 532 | 224                 |

| EP4CE40    |   | —           | _                   | _        | _       | —        | _       | —            | _       | _            | _       | <b>1</b> 93  | 68      | <b>▲</b> 328 | 124     | 328          | 124     | 532          | 224                 |

| EP4CE55    |   | —           |                     | _        | —       | —        | —       | —            | —       | _            | —       |              |         | 324          | 132     | 324          | 132     | 374          | 160                 |

| EP4CE75    |   | —           |                     | _        | —       | —        | —       | —            | —       | _            | —       |              |         | 292          | 110     | 292          | 110     | 426          | 178                 |

| EP4CE115   |   |             |                     |          |         |          |         | —            |         | —            |         | —            |         |              |         | 280          | 103     | ▼528         | 230                 |

#### Notes to Table 1-3:

(1) The E144 package has an exposed pad at the bottom of the package. This exposed pad is a ground pad that must be connected to the ground plane of your PCB. Use this exposed pad for electrical connectivity and not for thermal purposes.

(2) Use the Pin Migration View window in Pin Planner of the Quartus II software to verify the pin migration compatibility when you perform device migration. For more information, refer to the *I/O Management* chapter in volume 2 of the *Quartus II Handbook*.

(3) This includes both dedicated and emulated LVDS pairs. For more information, refer to the *I/O Features in Cyclone IV Devices* chapter.

| Package    |          | F169     |       |              | F324     |       |              | F484     |       | F672     |          |       | F896         |          |       |

|------------|----------|----------|-------|--------------|----------|-------|--------------|----------|-------|----------|----------|-------|--------------|----------|-------|

| Size (mm)  |          | 14 × 14  |       |              | 19 × 19  |       | :            | 23 × 23  |       | 27 × 27  |          |       | 31 × 31      |          |       |

| Pitch (mm) |          | 1.0      |       |              | 1.0      |       |              | 1.0      |       |          | 1.0      |       |              | 1.0      |       |

| Device     | User I/O | LVDS (2) | XCVRs | User I/O     | LVDS (2) | XCVRs | User I/O     | LVDS (2) | XCVRs | User I/O | LVDS (2) | XCVRs | User I/O     | LVDS (2) | XCVRs |

| EP4CGX15   | ▲72      | 25       | 2     | —            | —        |       | —            | —        | _     | —        | —        |       | —            | <b>—</b> | —     |

| EP4CGX22   | 72       | 25       | 2     | <b>1</b> 50  | 64       | 4     | —            | —        |       | —        | —        |       | —            | —        |       |

| EP4CGX30   | ▼72      | 25       | 2     | <b>▼</b> 150 | 64       | 4     | <b>▲</b> 290 | 130      | 4     | —        | —        |       | —            | —        |       |

| EP4CGX50   | —        | —        | _     | —            | —        | _     | 290          | 130      | 4     | ▲310     | 140      | 8     | —            | —        | —     |

| EP4CGX75   |          | —        | _     |              |          | _     | 290          | 130      | 4     | 310      | 140      | 8     | —            | —        | _     |

| EP4CGX110  | —        | —        | _     | —            | —        |       | 270          | 120      | 4     | 393      | 181      | 8     | <b>▲</b> 475 | 220      | 8     |

| EP4CGX150  | _        | _        | _     | —            |          | _     | ★270         | 120      | 4     | ▼393     | 181      | 8     | <b>▼</b> 475 | 220      | 8     |

#### Table 1–4. Package Offerings for the Cyclone IV GX Device Family <sup>(1)</sup>

Note to Table 1-4:

(1) Use the Pin Migration View window in Pin Planner of the Quartus II software to verify the pin migration compatibility when you perform device migration. For more information, refer to the *I/O Management* chapter in volume 2 of the *Quartus II Handbook*.

(2) This includes both dedicated and emulated LVDS pairs. For more information, refer to the *I/O Features in Cyclone IV Devices* chapter.

# **Cyclone IV Device Family Speed Grades**

Table 1–5 lists the Cyclone IV GX devices speed grades.

| Device    | F169           | F324             | F484           | F672           | F896       |  |

|-----------|----------------|------------------|----------------|----------------|------------|--|

| EP4CGX15  | C6, C7, C8, I7 | —                | —              | —              | —          |  |

| EP4CGX22  | C6, C7, C8, I7 | C6, C7, C8, I7 — |                | —              | —          |  |

| EP4CGX30  | C6, C7, C8, I7 | C6, C7, C8, I7   | C6, C7, C8, I7 | —              |            |  |

| EP4CGX50  | —              | —                | C6, C7, C8, I7 | C6, C7, C8, I7 | —          |  |

| EP4CGX75  | —              | —                | C6, C7, C8, I7 | C6, C7, C8, I7 | —          |  |

| EP4CGX110 | —              | —                | C7, C8, I7     | C7, C8, I7     | C7, C8, I7 |  |

| EP4CGX150 | _              |                  | C7, C8, I7     | C7, C8, I7     | C7, C8, I7 |  |

Table 1–5. Speed Grades for the Cyclone IV GX Device Family

Table 1–6 lists the Cyclone IV E devices speed grades.

| Table 1–6. Spe | eed Grades for th | e Cyclone IV | E Device Fa | mily <sup>(1), (2)</sup> |

|----------------|-------------------|--------------|-------------|--------------------------|

|----------------|-------------------|--------------|-------------|--------------------------|

| Device   | E144                                   | M164 | M256     | U256 | F256                                   | F324 | U484 | F484                                   | F780                            |

|----------|----------------------------------------|------|----------|------|----------------------------------------|------|------|----------------------------------------|---------------------------------|

| EP4CE6   | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _    | _        | 17N  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _    | _    |                                        |                                 |

| EP4CE10  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _    | _        | I7N  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 |      | _    | _                                      | _                               |

| EP4CE15  | C8L, C9L, I8L<br>C6, C7, C8, I7        | I7N  | C7N, 17N | I7N  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _    | _    | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _                               |

| EP4CE22  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _    | _        | I7N  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | _    | _    | _                                      | _                               |

| EP4CE30  | _                                      | _    | _        | _    | _                                      | A7N  | _    | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | C8L, C9L, I8L<br>C6, C7, C8, I7 |

| EP4CE40  |                                        | _    | _        | _    | _                                      | A7N  | I7N  | C8L, C9L, I8L<br>C6, C7, C8, I7,<br>A7 | C8L, C9L, I8L<br>C6, C7, C8, I7 |

| EP4CE55  | —                                      | _    | _        | _    | _                                      | _    | 17N  | C8L, C9L, I8L<br>C6, C7, C8, I7        | C8L, C9L, I8L<br>C6, C7, C8, I7 |

| EP4CE75  | —                                      | _    | _        | _    | —                                      | _    | 17N  | C8L, C9L, I8L<br>C6, C7, C8, I7        | C8L, C9L, I8L<br>C6, C7, C8, I7 |

| EP4CE115 | _                                      |      | _        |      | _                                      |      |      | C8L, C9L, I8L<br>C7, C8, I7            | C8L, C9L, I8L<br>C7, C8, I7     |

Notes to Table 1-6:

(1) C8L, C9L, and I8L speed grades are applicable for the 1.0-V core voltage.

(2) C6, C7, C8, I7, and A7 speed grades are applicable for the 1.2-V core voltage.

## **Cyclone IV Device Family Architecture**

This section describes Cyclone IV device architecture and contains the following topics:

- "FPGA Core Fabric"

- "I/O Features"

- "Clock Management"

- "External Memory Interfaces"

- "Configuration"

- "High-Speed Transceivers (Cyclone IV GX Devices Only)"

- "Hard IP for PCI Express (Cyclone IV GX Devices Only)"

### **FPGA Core Fabric**

Cyclone IV devices leverage the same core fabric as the very successful Cyclone series devices. The fabric consists of LEs, made of 4-input look up tables (LUTs), memory blocks, and multipliers.

Each Cyclone IV device M9K memory block provides 9 Kbits of embedded SRAM memory. You can configure the M9K blocks as single port, simple dual port, or true dual port RAM, as well as FIFO buffers or ROM. They can also be configured to implement any of the data widths in Table 1–7.

#### Table 1–7. M9K Block Data Widths for Cyclone IV Device Family

| Mode                            | Data Width Configurations            |

|---------------------------------|--------------------------------------|

| Single port or simple dual port | ×1, ×2, ×4, ×8/9, ×16/18, and ×32/36 |

| True dual port                  | ×1, ×2, ×4, ×8/9, and ×16/18         |

The multiplier architecture in Cyclone IV devices is the same as in the existing Cyclone series devices. The embedded multiplier blocks can implement an 18 × 18 or two 9 × 9 multipliers in a single block. Altera offers a complete suite of DSP IP including finite impulse response (FIR), fast Fourier transform (FFT), and numerically controlled oscillator (NCO) functions for use with the multiplier blocks. The Quartus<sup>®</sup> II design software's DSP Builder tool integrates MathWorks Simulink and MATLAB design environments for a streamlined DSP design flow.

## I/O Features

Cyclone IV device I/O supports programmable bus hold, programmable pull-up resistors, programmable delay, programmable drive strength, programmable slew-rate control to optimize signal integrity, and hot socketing. Cyclone IV devices support calibrated on-chip series termination (Rs OCT) or driver impedance matching (Rs) for single-ended I/O standards. In Cyclone IV GX devices, the high-speed transceiver I/Os are located on the left side of the device. The top, bottom, and right sides can implement general-purpose user I/Os.

Table 1–8 lists the I/O standards that Cyclone IV devices support.

| Туре             | I/O Standard                                               |

|------------------|------------------------------------------------------------|

| Single-Ended I/O | LVTTL, LVCMOS, SSTL, HSTL, PCI, and PCI-X                  |

| Differential I/O | SSTL, HSTL, LVPECL, BLVDS, LVDS, mini-LVDS, RSDS, and PPDS |

Table 1–8. I/O Standards Support for the Cyclone IV Device Family

The LVDS SERDES is implemented in the core of the device using logic elements.

• For more information, refer to the I/O Features in Cyclone IV Devices chapter.

### **Clock Management**

Cyclone IV devices include up to 30 global clock (GCLK) networks and up to eight PLLs with five outputs per PLL to provide robust clock management and synthesis. You can dynamically reconfigure Cyclone IV device PLLs in user mode to change the clock frequency or phase.

Cyclone IV GX devices support two types of PLLs: multipurpose PLLs and generalpurpose PLLs:

- Use multipurpose PLLs for clocking the transceiver blocks. You can also use them for general-purpose clocking when they are not used for transceiver clocking.

- Use general purpose PLLs for general-purpose applications in the fabric and periphery, such as external memory interfaces. Some of the general purpose PLLs can support transceiver clocking.

**\*** For more information, refer to the *Clock Networks and PLLs in Cyclone IV Devices* chapter.

### **External Memory Interfaces**

Cyclone IV devices support SDR, DDR, DDR2 SDRAM, and QDRII SRAM interfaces on the top, bottom, and right sides of the device. Cyclone IV E devices also support these interfaces on the left side of the device. Interfaces may span two or more sides of the device to allow more flexible board design. The Altera<sup>®</sup> DDR SDRAM memory interface solution consists of a PHY interface and a memory controller. Altera supplies the PHY IP and you can use it in conjunction with your own custom memory controller or an Altera-provided memory controller. Cyclone IV devices support the use of error correction coding (ECC) bits on DDR and DDR2 SDRAM interfaces. **To** For more information, refer to the *External Memory Interfaces in Cyclone IV Devices* chapter.

## Configuration

Cyclone IV devices use SRAM cells to store configuration data. Configuration data is downloaded to the Cyclone IV device each time the device powers up. Low-cost configuration options include the Altera EPCS family serial flash devices and commodity parallel flash configuration options. These options provide the flexibility for general-purpose applications and the ability to meet specific configuration and wake-up time requirements of the applications.

Table 1–9 lists which configuration schemes are supported by Cyclone IV devices.

Table 1–9. Configuration Schemes for Cyclone IV Device Family

| Devices       | Supported Configuration Scheme       |

|---------------|--------------------------------------|

| Cyclone IV GX | AS, PS, JTAG, and FPP <sup>(1)</sup> |

| Cyclone IV E  | AS, AP, PS, FPP, and JTAG            |

Note to Table 1-9:

(1) The FPP configuration scheme is only supported by the EP4CGX30F484 and EP4CGX50/75/110/150 devices.

IEEE 1149.6 (AC JTAG) is supported on all transceiver I/O pins. All other pins support IEEE 1149.1 (JTAG) for boundary scan testing.

For more information, refer to the *JTAG Boundary-Scan Testing for Cyclone IV Devices* chapter.

For Cyclone IV GX devices to meet the PCIe 100 ms wake-up time requirement, you must use passive serial (PS) configuration mode for the EP4CGX15/22/30 devices and use fast passive parallel (FPP) configuration mode for the EP4CGX30F484 and EP4CGX50/75/110/150 devices.

For more information, refer to the *Configuration and Remote System Upgrades in* -*Cyclone IV Devices* chapter.

The cyclical redundancy check (CRC) error detection feature during user mode is supported in all Cyclone IV GX devices. For Cyclone IV E devices, this feature is only supported for the devices with the core voltage of 1.2 V.

For more information about CRC error detection, refer to the *SEU Mitigation in Cyclone IV Devices* chapter.

### High-Speed Transceivers (Cyclone IV GX Devices Only)

Cyclone IV GX devices contain up to eight full duplex high-speed transceivers that can operate independently. These blocks support multiple industry-standard communication protocols, as well as Basic mode, which you can use to implement your own proprietary protocols. Each transceiver channel has its own pre-emphasis and equalization circuitry, which you can set at compile time to optimize signal integrity and reduce bit error rates. Transceiver blocks also support dynamic reconfiguration, allowing you to change data rates and protocols on-the-fly. Figure 1–1 shows the structure of the Cyclone IV GX transceiver.

For more information, refer to the *Cyclone IV Transceivers Architecture* chapter.

## Hard IP for PCI Express (Cyclone IV GX Devices Only)

Cyclone IV GX devices incorporate a single hard IP block for ×1, ×2, or ×4 PCIe (PIPE) in each device. This hard IP block is a complete PCIe (PIPE) protocol solution that implements the PHY-MAC layer, Data Link Layer, and Transaction Layer functionality. The hard IP for the PCIe (PIPE) block supports root-port and end-point configurations. This pre-verified hard IP block reduces risk, design time, timing closure, and verification. You can configure the block with the Quartus II software's PCI Express Compiler, which guides you through the process step by step.

For more information, refer to the PCI Express Compiler User Guide.

## **Reference and Ordering Information**

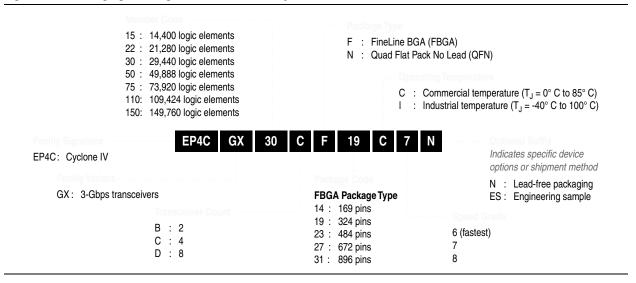

Figure 1–2 shows the ordering codes for Cyclone IV GX devices.

#### Figure 1–2. Packaging Ordering Information for the Cyclone IV GX Device

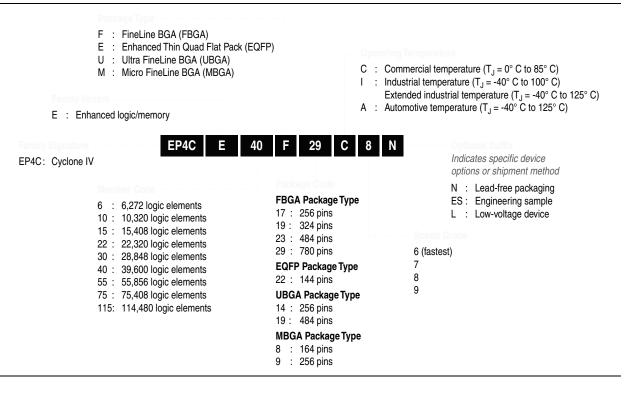

Figure 1–3 shows the ordering codes for Cyclone IV E devices.

# **Document Revision History**

Table 1–10 lists the revision history for this chapter.

#### Table 1–10. Document Revision History

| Date          | Version | Changes                                                                                                                                        |

|---------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------|

| March 2016    | 2.0     | ■ Updated Table 1–4 and Table 1–5 to remove support for the N148 package.                                                                      |

|               |         | <ul> <li>Updated Figure 1–2 to remove support for the N148 package.</li> </ul>                                                                 |

| April 2014    | 1.9     | Updated "Packaging Ordering Information for the Cyclone IV E Device".                                                                          |

| May 2013      | 1.8     | Updated Table 1–3, Table 1–6 and Figure 1–3 to add new device options and packages.                                                            |

| February 2013 | 1.7     | Updated Table 1–3, Table 1–6 and Figure 1–3 to add new device options and packages.                                                            |

| October 2012  | 1.6     | Updated Table 1–3 and Table 1–4.                                                                                                               |

| November 2011 | 1.5     | <ul> <li>Updated "Cyclone IV Device Family Features" section.</li> </ul>                                                                       |

|               |         | ■ Updated Figure 1–2 and Figure 1–3.                                                                                                           |

| December 2010 | 1.4     | <ul> <li>Updated for the Quartus II software version 10.1 release.</li> </ul>                                                                  |

|               |         | <ul> <li>Added Cyclone IV E new device package information.</li> </ul>                                                                         |

|               |         | ■ Updated Table 1–1, Table 1–2, Table 1–3, Table 1–5, and Table 1–6.                                                                           |

|               |         | ■ Updated Figure 1–3.                                                                                                                          |

|               |         | <ul> <li>Minor text edits.</li> </ul>                                                                                                          |

| July 2010     | 1.3     | Updated Table 1–2 to include F484 package information.                                                                                         |

| March 2010    | 1.2     | ■ Updated Table 1–3 and Table 1–6.                                                                                                             |

|               |         | ■ Updated Figure 1–3.                                                                                                                          |

|               |         | <ul> <li>Minor text edits.</li> </ul>                                                                                                          |

| February 2010 | 1.1     | <ul> <li>Added Cyclone IV E devices in Table 1–1, Table 1–3, and Table 1–6 for the<br/>Quartus II software version 9.1 SP1 release.</li> </ul> |

|               |         | <ul> <li>Added the "Cyclone IV Device Family Speed Grades" and "Configuration"<br/>sections.</li> </ul>                                        |

|               |         | <ul> <li>Added Figure 1–3 to include Cyclone IV E Device Packaging Ordering<br/>Information.</li> </ul>                                        |

|               |         | ■ Updated Table 1–2, Table 1–4, and Table 1–5 for Cyclone IV GX devices.                                                                       |

|               |         | <ul> <li>Minor text edits.</li> </ul>                                                                                                          |

| November 2009 | 1.0     | Initial release.                                                                                                                               |