Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

•XFI

| Details                    |                                                                                        |

|----------------------------|----------------------------------------------------------------------------------------|

| Product Status             | Active                                                                                 |

| Core Processor             | ARM® Cortex®-M0                                                                        |

| Core Size                  | 32-Bit Single-Core                                                                     |

| Speed                      | 72MHz                                                                                  |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                                     |

| Peripherals                | Brown-out Detect/Reset, LVR, POR, PWM, WDT                                             |

| Number of I/O              | 38                                                                                     |

| Program Memory Size        | 128KB (128K x 8)                                                                       |

| Program Memory Type        | FLASH                                                                                  |

| EEPROM Size                | -                                                                                      |

| RAM Size                   | 16К х 8                                                                                |

| Voltage - Supply (Vcc/Vdd) | 2.5V ~ 5.5V                                                                            |

| Data Converters            | A/D 16x12b                                                                             |

| Oscillator Type            | Internal                                                                               |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                     |

| Mounting Type              | Surface Mount                                                                          |

| Package / Case             | 48-LQFP                                                                                |

| Supplier Device Package    | 48-LQFP (7x7)                                                                          |

| Purchase URL               | https://www.e-xfl.com/product-detail/nuvoton-technology-corporation-america/m0519le3ae |

|                            |                                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1 GENERAL DESCRIPTION

The NuMicro<sup>®</sup> M0519 Series 32-bit microcontroller is embedded with the newest ARM<sup>®</sup> Cortex<sup>®</sup>-M0 core at a cost equivalent to traditional 8-bit microcontroller for industrial control and applications which need high performance.

The NuMicro<sup>®</sup> M0519 Series embedded with the Cortex<sup>®</sup>-M0 core runs up to 72 MHz and supports a variety of industrial control and applications which need high CPU performance. The NuMicro<sup>®</sup> M0519 Series provides 128K/64K bytes embedded flash, 4 Kbytes data flash, 8 Kbytes flash for the ISP, and 16K bytes embedded SRAM. This MCU includes advanced PWM function and input capture timer which are specially designed for motor driving application. It is also equipped with plenty of peripheral devices, such as Timers, Watchdog Timer, UART, SPI, I2C, PWM Timer, GPIO, 12-bit ADC, Low Voltage Detector and Brown-out detector. These useful functions make the NuMicro<sup>®</sup> M0519 Series powerful for a wide range of applications.

In addition, the NuMicro<sup>®</sup> M0519 Series is equipped with ISP (In-System Programming), ICP (In-Circuit Programming) functions and IAP (In-Application Programming) which allow user to update the program memory without removing the chip from the actual end product.

# nuvoTon

- Brown-out detector

- 4 levels: 4.4V/3.7V/2.7V/2.2V

- Optional brown-out interrupt or reset

- Built-in LDO for Wide Operating Voltage Range: 2.5V to 5.5V

- Low Voltage Reset

- 96-bit unique ID

- Operating Temperature: -40°C ~105°C

- Develop tools: parallel writer or In-Circuit Programming (ICP) writer

- Packages:

- All Green package (RoHS)

- LQFP 100/64/48-pin

# nuvoTon

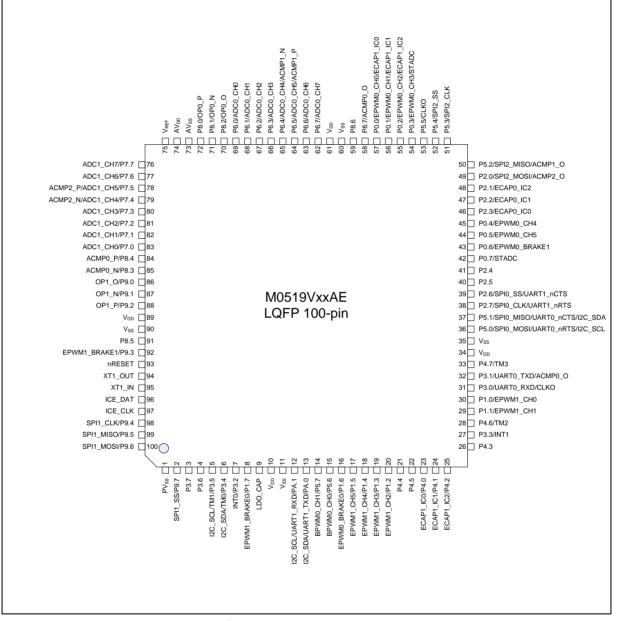

### 4.2 Pin Configuration

#### 4.2.1 LQFP 100-pin

Figure 4-2 NuMicro<sup>®</sup> M0519VxxAE Series LQFP-100 Pin Diagram

# 4.3 Pin Description

| Pi       | in Numbe | er     | <b>D</b> ' N     | Pin                 |                                                                                                                                                                                                                                                                                                                                                  |

|----------|----------|--------|------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 100- pin | 64-pin   | 48-pin | Pin Name         | Type <sup>[1]</sup> | Description                                                                                                                                                                                                                                                                                                                                      |

| 10       | 6        |        |                  |                     |                                                                                                                                                                                                                                                                                                                                                  |

| 34       | 0        | 7      | V <sub>DD</sub>  | Р                   | <b>POWER SUPPLY:</b> Supply voltage <b>Digital</b> V <sub>DD</sub> for operation.                                                                                                                                                                                                                                                                |

| 61       | 21       | ,      | • 00             |                     |                                                                                                                                                                                                                                                                                                                                                  |

| 89       | 21       |        |                  |                     |                                                                                                                                                                                                                                                                                                                                                  |

| 11       | 7        |        |                  |                     |                                                                                                                                                                                                                                                                                                                                                  |

| 35       |          | 8      | V <sub>ss</sub>  | Р                   | GROUND: Digital Ground potential.                                                                                                                                                                                                                                                                                                                |

| 60       | 22       | Ū      | . 55             |                     |                                                                                                                                                                                                                                                                                                                                                  |

| 90       |          |        |                  |                     |                                                                                                                                                                                                                                                                                                                                                  |

| 9        | 5        | 6      | LDO_CAP          | Р                   | LDO: LDO output pin                                                                                                                                                                                                                                                                                                                              |

| 4        |          |        |                  | Р                   | Note: It needs to be connected with a 1uF capacitor.                                                                                                                                                                                                                                                                                             |

| 1        | -        | -      | PVss             |                     | PLL GROUND: PLL Ground potential.                                                                                                                                                                                                                                                                                                                |

| 74       | 47       | 36     | AV <sub>DD</sub> | AP                  | Power supply for internal analog circuit                                                                                                                                                                                                                                                                                                         |

| 73       | 46       | 35     | AV <sub>SS</sub> | AP                  | Ground Pin for analog circuit                                                                                                                                                                                                                                                                                                                    |

| 75       | 48       | -      | V <sub>REF</sub> | AP                  | Voltage reference input for ADC<br>Note: It needs to be connected with a 1uF capacitor.                                                                                                                                                                                                                                                          |

| 93       | 60       | 48     | nRESET           | I<br>(ST)           | <b>RESET:</b> nRESET pin is a Schmitt trigger input pin for hardware device reset. A " <b>Low</b> " on this pin for 768 clock counter of Internal RC 22.1184 MHz while the system clock is running will reset the device. nRESET pin has an internal pull-up resistor allowing power-on reset by simply connecting an external capacitor to GND. |

| 94       | 61       | 4      | XT1_OUT          | о                   | CRYSTAL OUT: This is the output pin from the internal inverting amplifier. It emits the inverted signal of XT1_IN.                                                                                                                                                                                                                               |

| 95       | 62       | 3      | XT1_IN           | I<br>(ST)           | <b>CRYSTAL IN:</b> This is the input pin to the internal inverting amplifier.<br>The system clock is from external crystal or resonator when FOSC[1:0]<br>(CONFIG3[1:0]) are both logic 1 by default.                                                                                                                                            |

| 96       | 63       | 2      | ICE_DAT          | I/O                 | Serial Wired Debugger Data pin                                                                                                                                                                                                                                                                                                                   |

| 97       | 64       | 1      | ICE_CLK          | I                   | Serial Wired Debugger Clock pin                                                                                                                                                                                                                                                                                                                  |

|          |          |        | P0.0             | I/O                 | General purpose digital I/O pin                                                                                                                                                                                                                                                                                                                  |

| 57       | -        | -      | PWM0_CH0         | 0                   | PWM0 output of PWM Unit 0                                                                                                                                                                                                                                                                                                                        |

|          |          |        | ECAP1_IC0        | I                   | Input 0 of Enhanced Input Capture Unit 1                                                                                                                                                                                                                                                                                                         |

|          |          |        | P0.1             | I/O                 | General purpose digital I/O pin                                                                                                                                                                                                                                                                                                                  |

| 56       | -        | -      | PWM0_CH1         | 0                   | PWM1 output of PWM Unit 0                                                                                                                                                                                                                                                                                                                        |

|          |          |        | ECAP1_IC1        | I                   | Input 1 of Enhanced Input Capture Unit 1                                                                                                                                                                                                                                                                                                         |

| FF       |          |        | P0.2             | I/O                 | General purpose digital I/O pin                                                                                                                                                                                                                                                                                                                  |

| 55       | -        | -      | PWM0_CH2         | 0                   | PWM2 output of PWM Unit 0                                                                                                                                                                                                                                                                                                                        |

## **6** FUNCTIONAL DESCRIPTION

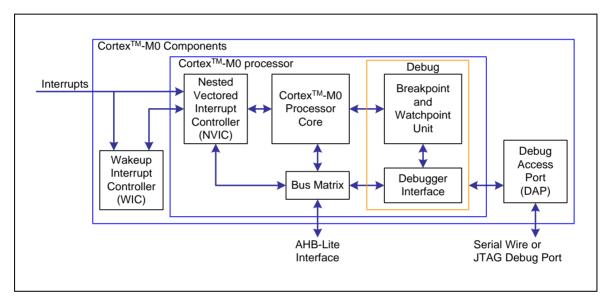

## 6.1 ARM<sup>®</sup> Cortex<sup>®</sup>-M0 Core

The Cortex<sup>®</sup>-M0 processor is a configurable, multistage, 32-bit RISC processor, which has an AMBA AHB-Lite interface and includes an NVIC component. It also has optional hardware debug functionality. The processor can execute Thumb code and is compatible with other Cortex<sup>®</sup>-M profile processor. The profile supports two modes -Thread mode and Handler mode. Handler mode is entered as a result of an exception. An exception return can only be issued in Handler mode. Thread mode is entered on Reset, and can be entered as a result of an exception return.

Figure 6-1 shows the functional controller of processor.

Figure 6-1 Functional Controller Diagram

The implemented device provides the following components and features:

- A low gate count processor:

- ARMv6-M Thumb<sup>®</sup> instruction set

- Thumb-2 technology

- ARMv6-M compliant 24-bit SysTick timer

- A 32-bit hardware multiplier

- System interface supported with little-endian data accesses

- Ability to have deterministic, fixed-latency, interrupt handling

- Load/store-multiples and multicycle-multiplies that can be abandoned and restarted to facilitate rapid interrupt handling

- C Application Binary Interface compliant exception model. This is the ARMv6-M, C Application Binary Interface (C-ABI) compliant exception model that enables the use of pure C functions as interrupt handlers

- Low Power Sleep mode entry using Wait For Interrupt (WFI), Wait For Event (WFE) instructions, or the return from interrupt sleep-on-exit feature

- NVIC:

# nuvoton

- 32 external interrupt inputs, each with four levels of priority

- Dedicated Non-maskable Interrupt (NMI) input

- Supports for both level-sensitive and pulse-sensitive interrupt lines

- Supports Wake-up Interrupt Controller (WIC) and, providing Ultra-low Power Sleep mode

- Debug support

- Four hardware breakpoints

- Two watchpoints

- Program Counter Sampling Register (PCSR) for non-intrusive code profiling

- Single step and vector catch capabilities

- Bus interfaces:

- Single 32-bit AMBA-3 AHB-Lite system interface that provides simple integration to all system peripherals and memory

- Single 32-bit slave port that supports the DAP (Debug Access Port)

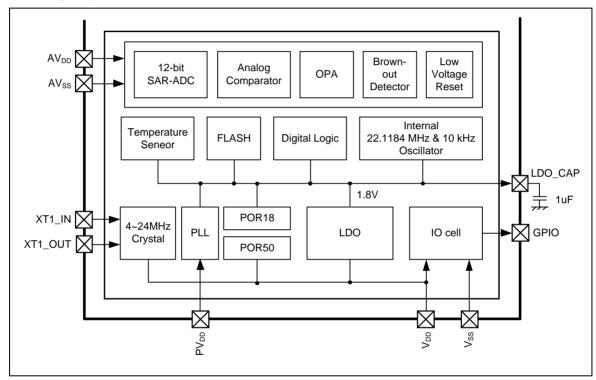

#### 6.2.3 System Power Distribution

In this chip, the power distribution is divided into two segments.

- Analog power from AV<sub>DD</sub> and AV<sub>SS</sub> provides the power for analog components operation.

- Digital power from V<sub>DD</sub> and V<sub>SS</sub> supplies the power to the I/O pins and internal regulator which provides a fixed 1.8V power for digital operation.

The output of internal voltage regulators, LDO\_CAP, requires an external capacitor which should be located close to the corresponding pin. Analog power ( $AV_{DD}$ ) should be the same voltage level of the digital power ( $V_{DD}$ ).

Figure 6-2 NuMicro<sup>®</sup> M0519 Series Power Distribution Diagram

#### 6.2.4 System Memory Map

The NuMicro<sup>®</sup> M0519 Series provides 4G-byte addressing space. The memory locations assigned to each on-chip controllers are shown in Table 6-1. The detailed register definition, memory space, and programming detailed will be described in the following sections for each on-chip peripheral. The NuMicro<sup>®</sup> M0519 Series only supports little-endian data format.

| Address Space                    | Token            | Controllers                                                |

|----------------------------------|------------------|------------------------------------------------------------|

| Flash and SRAM Memory Space      |                  |                                                            |

| 0x0000_0000 – 0x0001_FFFF        | FLASH_BA         | FLASH Memory Space (128 KB)                                |

| 0x2000_0000 – 0x2000_3FFF        | SRAM_BA          | SRAM Memory Space (16 KB)                                  |

| AHB Controllers Space (0x5000_00 | 00 – 0x501F_FFF  | F)                                                         |

| 0x5000_0000 – 0x5000_01FF        | GCR_BA           | System Global Control Registers                            |

| 0x5000_0200 – 0x5000_02FF        | CLK_BA           | Clock Control Registers                                    |

| 0x5000_0300 – 0x5000_03FF        | INT_BA           | Interrupt Multiplexer Control Registers                    |

| 0x5000_4000 – 0x5000_7FFF        | GPIO_BA          | GPIO Control Registers                                     |

| 0x5000_C000 – 0x5000_FFFF        | FMC_BA           | Flash Memory Control Registers                             |

| 0x5001_4000 – 0x5001_7FFF        | HDIV_BA          | Hardware Divider Register                                  |

| APB1 Controllers Space (0x4000_0 | 000 ~ 0x400F_FFF | F)                                                         |

| 0x4000_4000 – 0x4000_7FFF        | WDT_BA           | Watchdog Timer Control Registers                           |

| 0x4000_4100 – 0x4000_7FFF        | WWDT_BA          | Window Watchdog Timer Control Registers                    |

| 0x4001_0000 – 0x4001_3FFF        | TMR01_BA         | Timer0/Timer1 Control Registers                            |

| 0x4002_0000 – 0x4002_3FFF        | I2C0_BA          | I <sup>2</sup> C0 Interface Control Registers              |

| 0x4003_0000 – 0x4003_3FFF        | SPI0_BA          | SPI0 with master/slave function Control Registers          |

| 0x4003_4000 – 0x4003_7FFF        | SPI1_BA          | SPI1 with master/slave function Control Registers          |

| 0x4004_0000 – 0x4004_3FFF        | BPWM0_BA         | Basic PWM0 Control Registers                               |

| 0x4005_0000 – 0x4005_3FFF        | UART0_BA         | UART0 Control Registers                                    |

| 0x400D_0000 – 0x400D_3FFF        | ACMP_BA          | Analog Comparator Control Registers                        |

| 0x400E_0000 – 0x400E_3FFF        | EADC_BA          | Enhanced Analog-Digital-Converter (EADC) Control Registers |

| 0x400F_0000 – 0x400F_3FFF        | OPA_BA           | Operation Amplifier Control Registers                      |

| APB2 Controllers Space (0x4010_0 | 000 ~ 0x401F_FFF | F)                                                         |

| 0x4011_0000 – 0x4011_3FFF        | TMR23_BA         | Timer2/Timer3 Control Registers                            |

| 0x4013_0000 – 0x4013_3FFF        | SPI2_BA          | SPI2 with master/slave function Control Registers          |

| 0x4015_0000 – 0x4015_3FFF        | UART1_BA         | UART1 Control Registers                                    |

| Reserved                         | Reserved         | Reserved                                                   |

| 0x4019_0000 – 0x4019_3FFF        | EPWM0_BA         | Enhanced PWM0 Control Registers                            |

| 0x4019_4000 – 0x4019_7FFF        | EPWM1_BA         | Enhanced PWM1 Control Registers                            |

# nuvoTon

| Exception<br>Number | Vector<br>Address | Interrupt Number<br>(Bit In Interrupt<br>Registers) | Interrupt<br>Name | Source<br>Module  | Exception Description                                                 | Power<br>Down<br>Wake-Up              |

|---------------------|-------------------|-----------------------------------------------------|-------------------|-------------------|-----------------------------------------------------------------------|---------------------------------------|

| 29                  | 0x74              | 13                                                  | UART1_INT         | UART1             | UART1 interrupt                                                       | Yes                                   |

| 30                  | 0x78              | 14                                                  | SPI0_INT          | SPI0              | SPI0 interrupt                                                        | No                                    |

| 31                  | 0x7C              | 15                                                  | SPI1_INT          | SPI1              | SPI1 interrupt                                                        | No                                    |

| 32                  | 0x80              | 16                                                  | SPI2_INT          | SPI2              | SPI2 interrupt                                                        | No                                    |

| 33                  | 0x84              | 17                                                  | Reserved          | Reserved          | Reserved                                                              | -                                     |

| 33                  | 0x84              | 17                                                  | Reserved          | Reserved          | Reserved                                                              | No                                    |

| 34                  | 0x88              | 18                                                  | I2C0_INT          | I <sup>2</sup> C0 | I <sup>2</sup> C0 interrupt                                           | Yes                                   |

| 35                  | 0x8C              | 19                                                  | CKD_INT           | CKD               | CKD interrupt                                                         | No                                    |

| 36                  | 0x90              | 20                                                  | Reserved          | Reserved          | Reserved                                                              | -                                     |

| 36                  | 0x90              | 20                                                  | Reserved          | Reserved          | Reserved                                                              | -                                     |

| 37                  | 0x94              | 21                                                  | EPWM0_INT         | EPWM0             | Enhanced PWM0 interrupt                                               | No                                    |

| 38                  | 0x98              | 22                                                  | EPWM1_INT         | EPWM1             | Enhanced PWM1 interrupt                                               | No                                    |

| 39                  | 0x9C              | 23                                                  | ECAP0_INT         | ECAP0             | Enhanced input capture 0 interrupt                                    | No                                    |

| 40                  | 0xA0              | 24                                                  | ECAP1_INT         | ECAP1             | Enhanced input capture 1 interrupt                                    | No                                    |

| 41                  | 0xA4              | 25                                                  | ACMP_INT          | ACMP              | Analog Comparator 0 or 1, or OP<br>Amplifier digital output interrupt | Yes (only<br>by analog<br>comparator) |

| 42                  | 0xA8              | 26                                                  | Reserved          | Reserved          | Reserved                                                              | -                                     |

| 43                  | 0xAC              | 27                                                  | Reserved          | Reserved          | Reserved                                                              | -                                     |

| 42                  | 0xA8              | 26                                                  | Reserved          | Reserved          | Reserved                                                              | -                                     |

| 43                  | 0xAC              | 27                                                  | Reserved          | Reserved          | Reserved                                                              | -                                     |

| 44                  | 0xB0              | 28                                                  | PWRWU_INT         | CLKC              | Clock controller interrupt for chip wake up from power-down state     | -                                     |

| 45                  | 0xB4              | 29                                                  | EADC1_INT         | EADC1             | EADC1 interrupt                                                       | No                                    |

| 46                  | 0xB8              | 30                                                  | EADC2_INT         | EADC2             | EADC2 interrupt                                                       | No                                    |

| 47                  | 0xBC              | 31                                                  | EADC3_INT         | EADC3             | EADC3 interrupt                                                       | No                                    |

Table 6-3 System Interrupt Map Vector Table

#### 6.2.6.2 Vector Table

When an interrupt is accepted, the processor will automatically fetch the starting address of the interrupt service routine (ISR) from a vector table in memory. For ARMv6-M, the vector table base address is fixed at 0x00000000. The vector table contains the initialization value for the stack pointer on reset, and the entry point addresses for all exception handlers. The vector number on previous page defines the order of entries in the vector table associated with exception handler entry as illustrated in previous section.

| Vector Table Word Offset (Bytes) | Description                                      |

|----------------------------------|--------------------------------------------------|

| 0                                | SP_main – The Main stack pointer                 |

| Vector Number                    | Exception Entry Pointer using that Vector Number |

Table 6-4 Vector Table

#### 6.2.6.3 Operation Description

NVIC interrupts can be enabled and disabled by writing to their corresponding Interrupt Set-Enable or Interrupt Clear-Enable register bit-field. The registers use a write-1-to-enable and write-1-to-clear policy, both registers reading back the current enabled state of the corresponding interrupts. When an interrupt is disabled, interrupt assertion will cause the interrupt to become Pending, however, the interrupt will not be activated. If an interrupt is Active when it is disabled, it remains in its Active state until cleared by reset or an exception return. Clearing the enable bit prevents new activations of the associated interrupt.

NVIC interrupts can be pended/un-pended using a complementary pair of registers to those used to enable/disable the interrupts, named the Set-Pending Register and Clear-Pending Register respectively. The registers use a write-1-to-enable and write-1-to-clear policy, both registers reading back the current pended state of the corresponding interrupts. The Clear-Pending Register has no effect on the execution status of an Active interrupt.

NVIC interrupts are prioritized by updating an 8-bit field within a 32-bit register (each register supporting four interrupts).

The general registers associated with the NVIC are all accessible from a block of memory in the System Control Space and will be described in next section.

#### 6.3 Clock Controller

#### 6.3.1 Overview

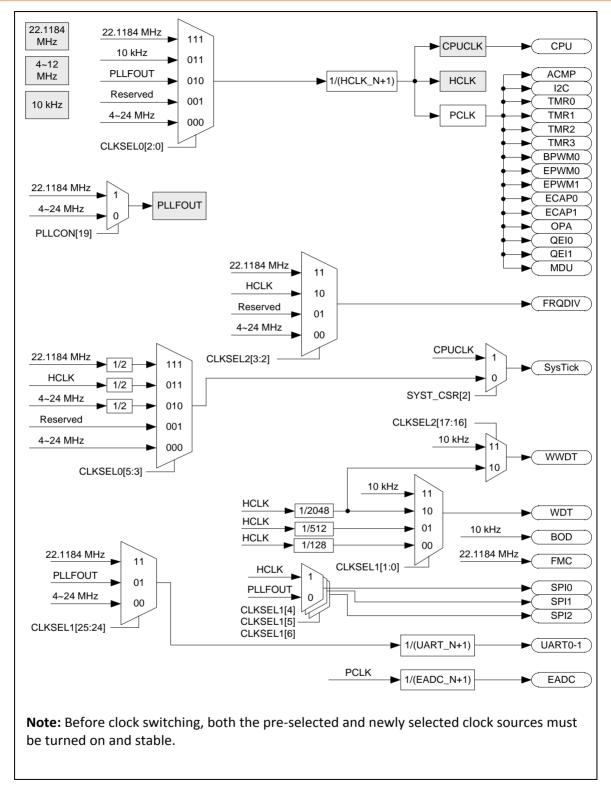

The clock controller generates the clocks for the whole chip, including system clocks and all peripheral clocks. The clock controller also implements the power control function with the individually clock ON/OFF control, clock source selection and clock divider. The chip enters Power-down mode when Cortex<sup>®</sup>-M0 core executes the WFI instruction only if the SLEEPDEEP (SCR[2]) bit is set to 1. After that, chip enters Power-down mode and wait for wake-up interrupt source triggered to leave Power-down mode. In the Power-down mode, the clock controller turns off the 4~24 MHz external high speed crystal oscillator and 22.1184 MHz internal high speed RC oscillator to reduce the overall system power consumption. Figure 6-3 shows the clock generator and the overview of the clock source control.

The clock generator consists of 4 clock sources as listed below:

- 4~24 MHz external high speed crystal oscillator (HXT)

- Programmable PLL output clock frequency (PLL\_FOUT), PLL source can be selected from 4~24 MHz external high speed crystal oscillator (HXT) or 22.1184 MHz internal high speed RC oscillator (HIRC)

- 22.1184 MHz internal high speed RC oscillator (HIRC)

- 10 kHz internal low speed RC oscillator (LIRC)

Each of these clock sources has certain stable time to wait for clock operating at stable frequency. When clock source is enabled, a stable counter start counting and correlated clock (OSC22M STB(CLKSTATUS[4]), OSC10K\_STB(CLKSTATUS[3]), stable index PLL STB(CLKSTATUS[2]) and XTL12M STB(CLKSTATUS[0])) are set to 1 after stable counter value reach a define value as Table 6-5. System and peripheral can use these clock as its operating clock only when correlate clock stable index is set to 1. The clock stable index will auto (OSC10K EN(PWRCON[3]), clear when user disables the clock source OSC22M\_EN(PWRCON[2]), XTL12M\_EN(PWRCON[0]) and PD(PLLCON[16])). Besides, the clock stable index of HXT, HIRC and PLL will auto clear when chip enter power-down and clock stable counter will re-counting after chip wake-up if correlate clock is enabled.

| Clock Source | Clock Stable Count Value                                                                              |

|--------------|-------------------------------------------------------------------------------------------------------|

| нхт          | 4096 HXT clock                                                                                        |

| PLL          | 6144 PLL source<br>(PLL source is HXT if PLL_SRC(PLLCON[19]) = 0, or HIRC if PLL_SRC(PLLCON[19]) = 1) |

| HIRC         | 256 HIRC clock                                                                                        |

| LIRC         | 1 LIRC                                                                                                |

Table 6-5 Clock Stable Count Value Table

## M0519

Figure 6-4 Clock Generator Global View Diagram

### 6.5 General Purpose I/O (GPIO)

#### 6.5.1 Overview

The NuMicro<sup>®</sup> M0519 Series has up to 82 General Purpose I/O pins to be shared with other function pins depending on the chip configuration. These 82 pins are arranged in 10 ports named as P0, P1, P2, P3, P4, P5, P6, P7, P8, P9 and PA. The P0/1/2/3/4/5/6/7/8/9 port has the maximum of 8 pins and PA port has the maximum of 2 pins. Each of the 82 pins is independent and has the corresponding register bits to control the pin mode function and data.

The I/O type of each of I/O pins can be configured by software individually as input, output, opendrain or Quasi-bidirectional mode. After reset, the I/O mode of all pins are stay at input mode. In Quasi-bidirectional mode, I/O pin has a very weak individual pull-up resistor which is about 110~300 K $\Omega$  for V<sub>DD</sub> is from 5.0 V to 2.5 V.

#### 6.5.2 Features

- Four I/O modes:

- Quasi-bidirectional

- Push-Pull output

- Open-Drain output

- Input only with high impendence

- TTL/Schmitt trigger input selectable by Px\_TYPE[7:0] in Px\_MFP[23:16]

- I/O pin configured as interrupt source with edge/level setting

- I/O pin internal pull-up resistor enabled only in Quasi-bidirectional I/O mode

- Enabling pin interrupt function will also enable the pin wake-up function

#### 6.8 Enhanced PWM Generator (EPWM)

#### 6.8.1 Overview

This device has two built-in PWM units with the same architecture whose function is specially designed for driving motor control applications.

#### 6.8.2 Features

Each unit supports the features below:

- Three independent 16-bit PWM duty control units with maximum 6 port pins:

- 3 independent PWM output: EPWM0\_CH0, EPWM0\_CH2 and EPWM0\_CH4 for Unit 0 EPWM1\_CH0, EPWM1\_CH2 and EPWM1\_CH4 for Unit 1

- 3 complementary PWM pairs, with each pin in a pair mutually complement to each other and capable of programmable dead-time insertion: (EPWMx\_CH0, EPWMx\_CH1), (PWMx\_CH2, EPWMx\_CH3) and (EPWMx\_CH4, EPWMx\_CH5) where x=0~1.

- 3 synchronous PWM pairs, with each pin in a pair in-phase: (EPWMx\_CH0, EPWMx\_CH1), (EPWMx\_CH2, EPWMx\_CH3) and (EPWMx\_CH4, EPWMx\_CH5) where x=0~1

- Group control bits: EPWMx\_CH2 and EPWMx\_CH4 are synchronized with EPWMx\_CH0

- Supports Edge aligned mode and Center aligned mode

- Programmable dead-time insertion between complementary paired PWMs

- Each pin of EPWMx\_CH0 to EPWMx\_CH5 has independent polarity setting control

- Mask output control for Electrically Commutated Motor operation

- Tri-state output at reset and brake state

- Hardware brake protection

- Two Interrupt Sources:

- Interrupt is synchronously requested at PWM frequency when up/down counter comparison matched (edge and center aligned modes) or underflow (center aligned mode).

- Interrupt is requested when external brake pins asserted

- PWM signals before polarity control stage are defined in the view of positive logic. The PWM ports is active high or active low are controlled by polarity control register.

- High Source/Sink current.

- Supports trigger EADC

### 6.10 Watchdog Timer (WDT)

#### 6.10.1 Overview

The purpose of Watchdog Timer (WDT) is to perform a system reset when system runs into an unknown state. This prevents system from hanging for an infinite period of time. Besides, this Watchdog Timer supports the function to wake-up system from Idle/Power-down mode.

#### 6.10.2 Features

- 18-bit free running up counter for WDT time-out interval

- Selectable time-out interval (2<sup>4</sup> ~ 2<sup>18</sup>) and the time-out interval is 1.6 ms ~ 26.214 s if WDT\_CLK = 10 kHz

- System kept in reset state for a period of (1 / WDT\_CLK) \* 63

- Supports selectable WDT reset delay period, including 1026

130

18 or 3 WDT\_CLK reset delay period

- Supports to force WDT enabled after chip powered on or reset by setting CWDTEN in Config0 register

- Supports WDT time-out wake-up function only if WDT clock source is selected as 10 kHz

### 6.16 Enhanced Analog-to-Digital Converter (EADC)

#### 6.16.1 Overview

The NuMicro<sup>®</sup> M0519 Series contains two 12-bit successive approximation analog-to-digital converters (SAR A/D converter) with 16 input channels. The two A/D converters ADCA and ADCB can be sampled with Simultaneous or Single Sampling mode. The A/D converters can be started by software, PWM triggers, timer0~3 overflow pulse triggers, ADINT0, ADINT1 interrupt EOC pulse trigger and external STADC pin input signal.

**Note:** The analog input port pins must be configured as input type before the EADC function is enabled.

#### 6.16.2 Features

- Analog input voltage range: 0~V<sub>REF</sub>(Max to 5.0V).

- 12-bit resolution and 10-bit accuracy is guaranteed.

- Up to 16 single-end analog input channels.

- Two SAR ADC converters.

- Four EADC interrupts with individual interrupt vector addresses.

- Maximum EADC clock frequency: 16MHz.

- Up to 1.6M SPS conversion rate, each of ADC converter conversion time less than 1.25µs.

- Two operating modes

- Single sampling mode: two ADC converters run at normal operation.

- Simultaneous sampling mode: Allow two ADC converters can be sampled simultaneously.

- An A/D conversion can be started by:

- Writing 1 to ADST(ADSSTR[n]) bit (n = 0~15) through software

- External pin STADC

- Timer0~3 overflow pulse triggers

- ADINT0, ADINT1 interrupt EOC pulse triggers

- PWM triggers

- Conversion results are held in 16 data registers with valid and overrun indicators.

- SAMPLEA0~7 ADC control logic modules, each of them is configurable for ADCA converter channel AINA0~7 and trigger source.

- SAMPLEB0~7 ADC control logic modules, each of them is configurable for ADCB converter channel AINB0~7 and trigger source.

- Channel AINA0 supports 2 input sources: external analog voltage and internal OP0 Amplifier output voltage.

- Channel AINB0 supports 2 input sources: external analog voltage and internal OP1 Amplifier output voltage.

- Channel AINA7 supports 4 input sources: external analog voltage, internal fixed band-gap voltage, internal temperature sensor output, and analog ground.

## 7 ELECTRICAL CHARACTERISTICS

### 7.1 Absolute Maximum Ratings

| SYMBOL                                    | PARAMETER           | MIN                  | MAX                  | UNIT |

|-------------------------------------------|---------------------|----------------------|----------------------|------|

| DC Power Supply                           | $V_{DD} - V_{SS}$   | -0.3                 | +6.3                 | V    |

| Input Voltage                             | V <sub>IN</sub>     | V <sub>SS</sub> -0.3 | V <sub>DD</sub> +0.3 | V    |

| Oscillator Frequency                      | 1/t <sub>CLCL</sub> | 4                    | 24                   | MHz  |

| Operating Temperature                     | ТА                  | -40                  | 105                  | °C   |

| Storage Temperature                       | T <sub>ST</sub>     | -55                  | +150                 | °C   |

| Maximum Current into VDD                  |                     | -                    | 120                  | mA   |

| Maximum Current out of VSS                |                     |                      | 120                  | mA   |

| Maximum Current sunk by a I/O pin         |                     |                      | 35                   | mA   |

| Maximum Current sourced by a I/O pin      |                     |                      | 35                   | mA   |

| Maximum Current sunk by total I/O pins    |                     |                      | 100                  | mA   |

| Maximum Current sourced by total I/O pins |                     |                      | 100                  | mA   |

Note: Exposure to conditions beyond those listed under absolute maximum ratings may adversely affects the lift and reliability of the device.

# nuvoton

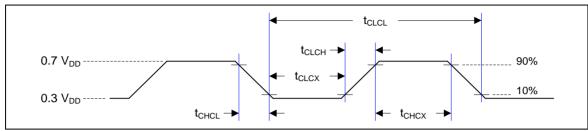

### 7.3 AC Electrical Characteristics

Note: Duty cycle is 50%.

| SYMBOL            | PARAMETER       | CONDITION | MIN. | TYP. | MAX. | UNIT |

|-------------------|-----------------|-----------|------|------|------|------|

| t <sub>CHCX</sub> | Clock High Time |           | 10   | -    | -    | nS   |

| t <sub>CLCX</sub> | Clock Low Time  |           | 10   | -    | -    | nS   |

| t <sub>CLCH</sub> | Clock Rise Time |           | 2    | -    | 15   | nS   |

| t <sub>CHCL</sub> | Clock Fall Time |           | 2    | -    | 15   | nS   |

### 7.3.1 External 4~24MHz Crystal

| PARAMETER                         | CONDITION               | MIN. | TYP | MAX. | UNIT |

|-----------------------------------|-------------------------|------|-----|------|------|

| Operation Voltage V <sub>DD</sub> | -                       | 2.5  | -   | 5.5  | V    |

| Temperature                       | -                       | -40  | -   | 85   | °C   |

| Operating Current                 | 12 MHz at $V_{DD} = 5V$ | -    | 1   | -    | mA   |

| Clock Frequency                   | External crystal        | 4    |     | 24   | MHz  |

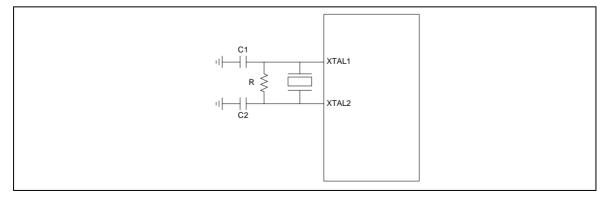

#### 7.3.1.1 Typical Crystal Application Circuits

| CRYSTAL        | C1       | C2       | R       |

|----------------|----------|----------|---------|

| 4 MHz ~ 24 MHz | 10~20 pF | 10~20 pF | without |

Figure 7–1 Typical Crystal Application Circuit

#### 7.3.2 Internal 22.1184 MHz Oscillator

| PARAMETER           | CONDITION                                     | MIN. | TYP.    | MAX. | UNIT |

|---------------------|-----------------------------------------------|------|---------|------|------|

| Supply voltage      | -                                             | 2.5  | -       | 5.5  | V    |

| Frequency           | -                                             | -    | 22.1184 | -    | MHz  |

|                     | +25°C; V <sub>DD</sub> = 5V                   | -1   | -       | +1   | %    |

| (After calibration) | -40 to +105°C;<br>V <sub>DD</sub> = 2.5V~5.5V | -2   | -       | +2   | %    |

| Operation Current   | V <sub>DD</sub> =5V                           | -    | 500     | -    | uA   |

#### 7.3.3 Internal 10 kHz Oscillator

| PARAMETER                                | CONDITION                                  | MIN. | TYP. | MAX. | UNIT |

|------------------------------------------|--------------------------------------------|------|------|------|------|

| Supply voltage                           | -                                          | 2.5  | -    | 5.5  | V    |

| Center Frequency                         | -                                          | -    | 10   | -    | kHz  |

| Calibrated Internal Oscillator Frequency | +25℃; V <sub>DD</sub> =5 V                 | -30  | -    | +30  | %    |

|                                          | -40℃~+85℃;<br>V <sub>DD</sub> =2.5 V~5.5 V | -50  | -    | +50  | %    |

# nuvoTon

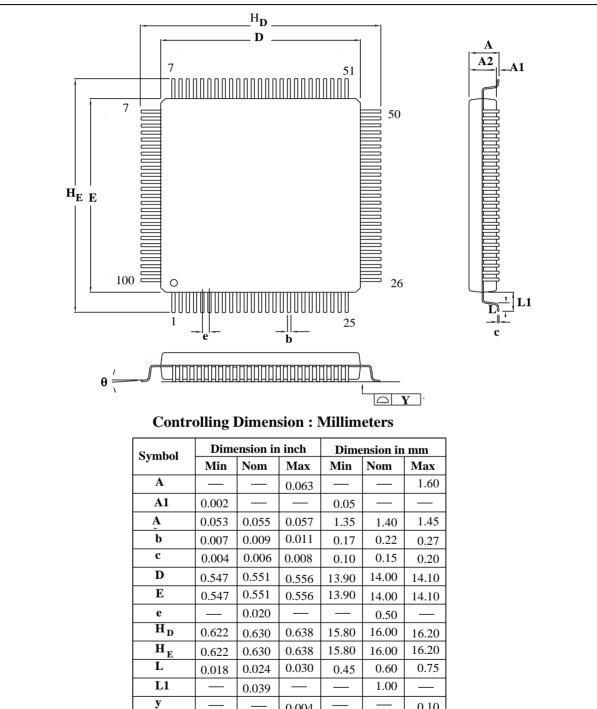

#### 8 PACKAGE DIMENSIONS

#### LQFP 100V (14x14x1.4 mm footprint 2.0mm) 8.1

0.004

7°

0°

0°

θ

0.10

7°