Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 16MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, PMP, SPI, UART/USART                                         |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                          |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 128KB (43K x 24)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                      |

| Data Converters            | A/D 16x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24fj128ga006-i-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

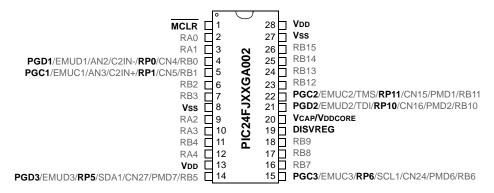

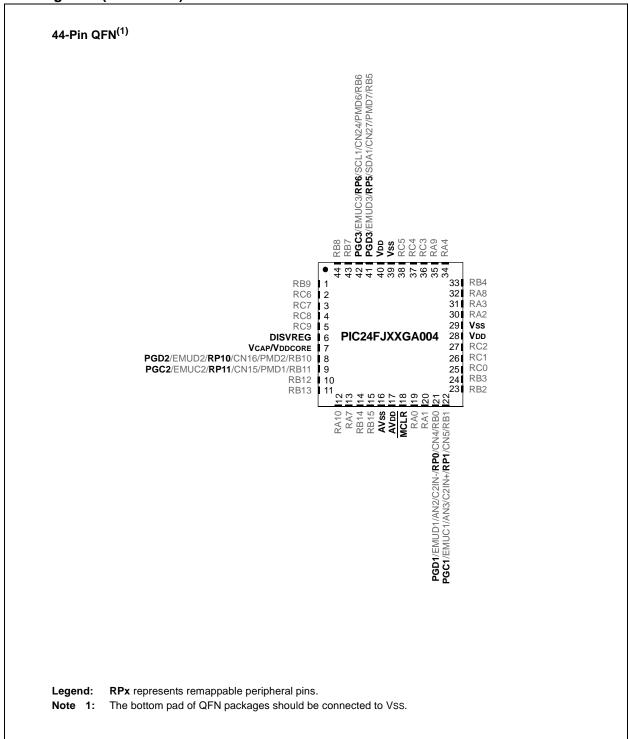

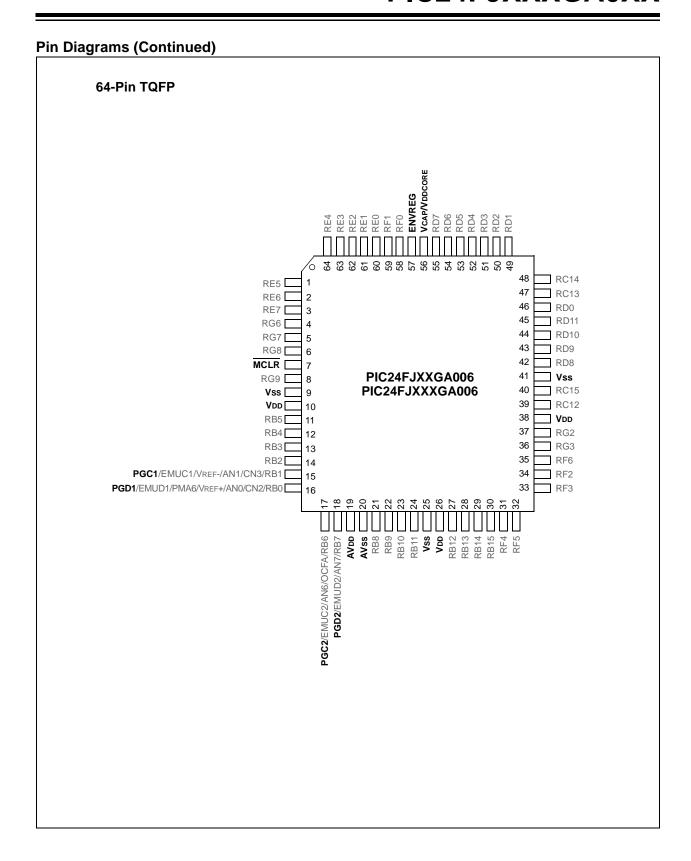

### **Pin Diagrams**

### 28-Pin PDIP, SSOP, SOIC

### 28-Pin QFN<sup>(1)</sup>

**Legend:** RPx represents remappable peripheral pins.

Note 1: The bottom pad of QFN packages should be connected to Vss.

## **Pin Diagrams (Continued)**

### 2.4 Memory Map

The program memory map extends from 000000h to FFFFFEh. Code storage is located at the base of the memory map and supports up to 44K instruction words (about 128 Kbytes). Table 2-3 shows the program memory size and number of erase and program blocks present in each device variant. Each erase block, or page, contains 512 instructions, and each program block, or row, contains 64 instructions.

Locations 800000h through 8007FEh are reserved for executive code memory. This region stores the programming executive and the debugging executive. The programming executive is used for device programming and the debugging executive is used for in-circuit debugging. This region of memory can not be used to store user code.

The last two implemented program memory locations are reserved for the device Configuration registers.

TABLE 2-2: FLASH CONFIGURATION WORD LOCATIONS FOR PIC24FJXXXGA0XX DEVICES

| Device         | _       | tion Word<br>esses |

|----------------|---------|--------------------|

|                | 1       | 2                  |

| PIC24FJ16GA    | 002BFEh | 002BFCh            |

| PIC24FJ32GA    | 0057FEh | 0057FCh            |

| PIC24FJ48GA    | 0083FEh | 0083FCh            |

| PIC24FJ64GA    | 00ABFEh | 00ABFCh            |

| PIC24FJ96GA    | 00FFFEh | 00FFFCh            |

| PIC24FJ128GAGA | 0157FEh | 0157FCh            |

Locations, FF0000h and FF0002h, are reserved for the Device ID registers. These bits can be used by the programmer to identify what device type is being programmed. They are described in **Section 6.1** "**Device ID**". The Device ID registers read out normally, even after code protection is applied.

Figure 2-4 shows the memory map for the PIC24FJXXXGA0XX family variants.

TABLE 2-3: CODE MEMORY SIZE

| Device       | User Memory<br>Address Limit<br>(Instruction Words) | Write<br>Blocks | Erase<br>Blocks |

|--------------|-----------------------------------------------------|-----------------|-----------------|

| PIC24FJ16GA  | 002BFEh (5.5K)                                      | 88              | 11              |

| PIC24FJ32GA  | 0057FEh (11K)                                       | 176             | 22              |

| PIC24FJ48GA  | 0083FEh (16.5K)                                     | 264             | 33              |

| PIC24FJ64GA  | 00ABFEh (22K)                                       | 344             | 43              |

| PIC24FJ96GA  | 00FFFEh (32K)                                       | 512             | 64              |

| PIC24FJ128GA | 0157FEh (44K)                                       | 688             | 86              |

### 3.6 Writing Code Memory

The procedure for writing code memory is the same as the procedure for writing the Configuration registers, except that 64 instruction words are programmed at a time. To facilitate this operation, working registers, W0:W5, are used as temporary holding registers for the data to be programmed.

Table 3-5 shows the ICSP programming details, including the serial pattern with the ICSP command code which must be transmitted, Least Significant bit first, using the PGCx and PGDx pins (see Figure 3-2).

In Step 1, the Reset vector is exited. In Step 2, the NVMCON register is initialized for programming a full row of code memory. In Step 3, the 24-bit starting destination address for programming is loaded into the TBLPAG register and W7 register. (The upper byte of the starting destination address is stored in TBLPAG and the lower 16 bits of the destination address are stored in W7.)

To minimize the programming time, A packed instruction format is used (Figure 3-6).

In Step 4, four packed instruction words are stored in working registers, W0:W5, using the MOV instruction, and the Read Pointer, W6, is initialized. The contents of W0:W5 (holding the packed instruction word data) are shown in Figure 3-6.

In Step 5, eight TBLWT instructions are used to copy the data from W0:W5 to the write latches of code memory. Since code memory is programmed 64 instruction words at a time, Steps 4 and 5 are repeated 16 times to load all the write latches (Step 6).

After the write latches are loaded, programming is initiated by writing to the NVMCON register in Steps 7 and 8. In Step 9, the internal PC is reset to 200h. This is a precautionary measure to prevent the PC from incrementing into unimplemented memory when large devices are being programmed. Lastly, in Step 10, Steps 3-9 are repeated until all of code memory is programmed.

FIGURE 3-6: PACKED INSTRUCTION WORDS IN W<0:5>

|    | 15 |      | 8   | 7  |      | 0 |

|----|----|------|-----|----|------|---|

| Wo |    |      | LS\ |    |      |   |

| W1 |    | MSB1 |     |    | MSB0 |   |

| W2 |    |      | LS\ | V1 |      |   |

| W3 |    |      | LS\ | V2 |      |   |

| W4 |    | MSB3 |     |    | MSB2 |   |

| W5 |    |      | LS\ | V3 |      |   |

|    |    |      |     |    |      |   |

TABLE 3-5: SERIAL INSTRUCTION EXECUTION FOR WRITING CODE MEMORY

| IADLE 3-3.          | OLIVIA II VOII        | STRUCTION EXECUTION OF WINTING CODE MEMORY |                                                                     |  |

|---------------------|-----------------------|--------------------------------------------|---------------------------------------------------------------------|--|

| Command<br>(Binary) | Data<br>(Hex)         | Description                                |                                                                     |  |

| Step 1: Exi         | t the Reset vector.   |                                            |                                                                     |  |

| 0000                | 000000                | NOP                                        |                                                                     |  |

| 0000                | 040200                | GOTO                                       | 0x200                                                               |  |

| 0000                | 000000                | NOP                                        |                                                                     |  |

| Step 2: Set         | the NVMCON to pr      | ogram 64                                   | 4 instruction words.                                                |  |

| 0000                | 24001A                | MOV                                        | #0x4001, W10                                                        |  |

| 0000                | 883B0A                | MOV                                        | W10, NVMCON                                                         |  |

| Step 3: Initi       | alize the Write Point | er (W7)                                    | for TBLWT instruction.                                              |  |

| 0000                | 200xx0                | MOV                                        | <pre>#<destinationaddress23:16>, W0</destinationaddress23:16></pre> |  |

| 0000                | 880190                | MOV                                        | WO, TBLPAG                                                          |  |

| 0000                | 2xxxx7                | MOV                                        | <pre>#<destinationaddress15:0>, W7</destinationaddress15:0></pre>   |  |

| Step 4: Loa         | ad W0:W5 with the n   | ext 4 ins                                  | truction words to program.                                          |  |

| 0000                | 2xxxx0                | MOV                                        | # <lsw0>, W0</lsw0>                                                 |  |

| 0000                | 2xxxx1                | MOV                                        | # <msb1:msb0>, W1</msb1:msb0>                                       |  |

| 0000                | 2xxxx2                | MOV                                        | # <lsw1>, W2</lsw1>                                                 |  |

| 0000                | 2xxxx3                | MOV                                        | # <lsw2>, W3</lsw2>                                                 |  |

| 0000                | 2xxxx4                | MOV                                        | # <msb3:msb2>, W4</msb3:msb2>                                       |  |

| 0000                | 2xxxx5                | MOV                                        | # <lsw3>, W5</lsw3>                                                 |  |

# 3.10 Verify Code Memory and Configuration Word

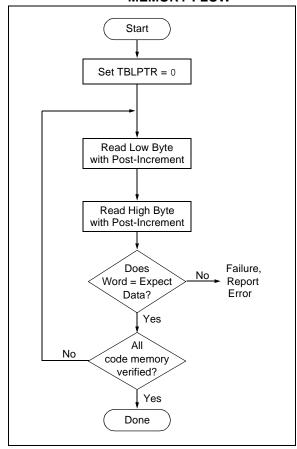

The verify step involves reading back the code memory space and comparing it against the copy held in the programmer's buffer. The Configuration registers are verified with the rest of the code.

The verify process is shown in the flowchart in Figure 3-8. Memory reads occur a single byte at a time, so two bytes must be read to compare against the word in the programmer's buffer. Refer to **Section 3.8** "**Reading Code Memory**" for implementation details of reading code memory.

Note: Because the Configuration registers include the device code protection bit, code memory should be verified immediately after writing if code protection is enabled. This is because the device will not be readable or verifiable if a device Reset occurs after the code-protect bit in CW1 has been cleared.

FIGURE 3-8: VERIFY CODE MEMORY FLOW

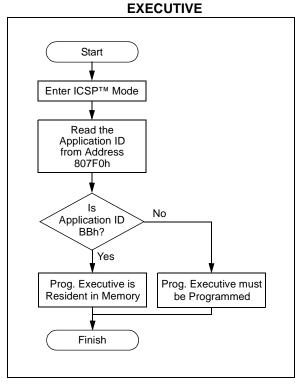

### 3.11 Reading the Application ID Word

The Application ID Word is stored at address 8005BEh in executive code memory. To read this memory location, you must use the SIX control code to move this program memory location to the VISI register. Then, the REGOUT control code must be used to clock the contents of the VISI register out of the device. The corresponding control and instruction codes that must be serially transmitted to the device to perform this operation are shown in Table 3-10.

After the programmer has clocked out the Application ID Word, it must be inspected. If the Application ID has the value, BBh, the programming executive is resident in memory and the device can be programmed using the mechanism described in **Section 4.0 "Device Programming – Enhanced ICSP"**. However, if the Application ID has any other value, the programming executive is not resident in memory; it must be loaded to memory before the device can be programmed. The procedure for loading the programming executive to memory is described in **Section 5.4 "Programming the Programming Executive to Memory"**.

### 3.12 Exiting ICSP Mode

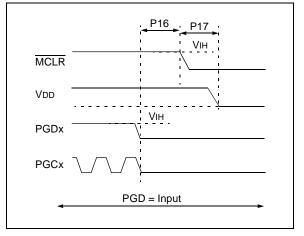

Exiting Program/Verify mode is done by removing VIH from MCLR, as shown in Figure 3-9. The only requirement for exit is that an interval, P16, should elapse between the last clock and program signals on PGCx and PGDx before removing VIH.

FIGURE 3-9: EXITING ICSP™ MODE

FIGURE 4-2: CONFIRMING PRESENCE OF PROGRAMMING

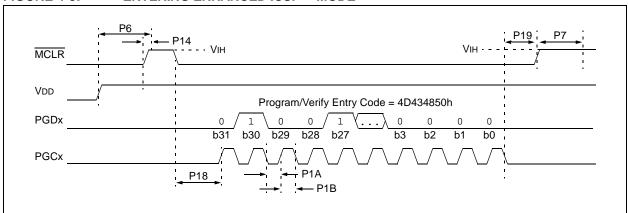

### 4.3 Entering Enhanced ICSP Mode

As shown in Figure 4-3, entering Enhanced ICSP Program/Verify mode requires three steps:

- 1. The  $\overline{\text{MCLR}}$  pin is briefly driven high, then low.

- 2. A 32-bit key sequence is clocked into PGDx.

- 3. MCLR is then driven high within a specified period of time and held.

The programming voltage applied to MCLR is VIH, which is essentially VDD in the case of PIC24FJXXXGA0XX devices. There is no minimum time requirement for holding at VIH. After VIH is removed, an interval of at least P18 must elapse before presenting the key sequence on PGDx.

The key sequence is a specific 32-bit pattern: '0100 1101 0100 0011 0100 1000 0101 0000' (more easily remembered as 4D434850h in hexadecimal format). The device will enter Program/Verify mode only if the key sequence is valid. The Most Significant bit (MSb) of the most significant nibble must be shifted in first.

Once the key sequence is complete, VIH must be applied to MCLR and held at that level for as long as Program/Verify mode is to be maintained. An interval of at least time P19 and P7 must elapse before presenting data on PGDx. Signals appearing on PGDx before P7 has elapsed will not be interpreted as valid.

On successful entry, the program memory can be accessed and programmed in serial fashion. While in the Program/Verify mode, all unused I/Os are placed in the high-impedance state.

FIGURE 4-3: ENTERING ENHANCED ICSP™ MODE

### 4.5.2 PROGRAMMING VERIFICATION

After code memory is programmed, the contents of memory can be verified to ensure that programming was successful. Verification requires code memory to be read back and compared against the copy held in the programmer's buffer.

The READP command can be used to read back all of the programmed code memory.

Alternatively, you can have the programmer perform the verification after the entire device is programmed using a checksum computation.

### 4.6 Configuration Bits Programming

### 4.6.1 OVERVIEW

The PIC24FJXXXGA0XX family has Configuration bits stored in the last two locations of implemented program memory (see Table 2-2 for locations). These bits can be set or cleared to select various device configurations. There are three types of Configuration bits: system operation bits, code-protect bits and unit ID bits. The system operation bits determine the power-on settings for system level components, such as oscillator and Watchdog Timer. The code-protect bits prevent program memory from being read and written.

The register descriptions for the CW1 and CW2 Configuration registers are shown in Table 4-2.

TABLE 4-2: PIC24FJXXXGA0XX FAMILY CONFIGURATION BITS DESCRIPTION

| Bit Field              | Register  | Description                                                                                                                                                                                                                                                                                                                                                                                       |

|------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I2C1SEL <sup>(1)</sup> | CW2<2>    | I2C1 Pin Mapping bit  1 = Default location for SCL1/SDA1 pins  0 = Alternate location for SCL1/SDA1 pins                                                                                                                                                                                                                                                                                          |

| DEBUG                  | CW1<11>   | Background Debug Enable bit  1 = Device will reset in User mode  0 = Device will reset in Debug mode                                                                                                                                                                                                                                                                                              |

| FCKSM1:FCKSM0          | CW2<7:6>  | Clock Switching Mode bits  1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled  01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled  00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                                                                                                                       |

| FNOSC2:FNOSC0          | CW2<10:8> | Initial Oscillator Source Selection bits  111 = Internal Fast RC (FRCDIV) oscillator with postscaler  110 = Reserved  101 = Low-Power RC (LPRC) oscillator  100 = Secondary (SOSC) oscillator  011 = Primary (XTPLL, HSPLL, ECPLL) oscillator with PLL  010 = Primary (XT, HS, EC) oscillator  001 = Internal Fast RC (FRCPLL) oscillator with postscaler and PLL  000 = Fast RC (FRC) oscillator |

| FWDTEN                 | CW1<7>    | Watchdog Timer Enable bit  1 = Watchdog Timer always enabled (LPRC oscillator cannot be disabled; clearing the SWDTEN bit in the RCON register will have no effect)  0 = Watchdog Timer enabled/disabled by user software (LPRC can be disabled by clearing the SWDTEN bit in the RCON register)                                                                                                  |

| GCP                    | CW1<13>   | General Segment Code-Protect bit  1 = User program memory is not code-protected  0 = User program memory is code-protected                                                                                                                                                                                                                                                                        |

| GWRP                   | CW1<12>   | General Segment Write-Protect bit  1 = User program memory is not write-protected  0 = User program memory is write-protected                                                                                                                                                                                                                                                                     |

| ICS                    | CW1<8>    | ICD Communication Channel Select bit  1 = Communicate on PGC2/EMUC2 and PGD2/EMUD2  0 = Communicate on PGC1/EMUC1 and PGD1/EMUD1                                                                                                                                                                                                                                                                  |

Note 1: Available on 28 and 44-pin packages only.

2: Available only on 28 and 44-pin devices with a silicon revision of 3042h or higher.

TABLE 4-2: PIC24FJXXXGA0XX FAMILY CONFIGURATION BITS DESCRIPTION (CONTINUED)

| Bit Field                            | Register   | Description                                                                                                                                                                                                                                                                                                                           |  |

|--------------------------------------|------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ICS <sup>(1)</sup>                   | CW1<8>     | ICD Pin Placement Select bit  11 = ICD EMUC/EMUD pins are shared with PGC1/PGD1  10 = ICD EMUC/EMUD pins are shared with PGC2/PGD2  01 = ICD EMUC/EMUD pins are shared with PGC3/PGD3  00 = Reserved; do not use                                                                                                                      |  |

| IESO                                 | CW2<15>    | Internal External Switchover bit  1 = Two-Speed Start-up enabled  0 = Two-Speed Start-up disabled                                                                                                                                                                                                                                     |  |

| IOL1WAY <sup>(1)</sup>               | CW2<4>     | IOLOCK Bit One-Way Set Enable bit  0 = The OSCCON <iolock> bit can be set and cleared as needed (provide an unlocking sequence is executed)  1 = The OSCCON<iolock> bit can only be set once (provided an unlockin sequence is executed). Once IOLOCK is set, this prevents any possible future RP register changes</iolock></iolock> |  |

| JTAGEN                               | CW1<14>    | JTAG Enable bit  1 = JTAG enabled  0 = JTAG disabled                                                                                                                                                                                                                                                                                  |  |

| OSCIOFNC                             | CW2<5>     | OSC2 Pin Function bit (except in XT and HS modes)  1 = OSC2 is clock output  0 = OSC2 is general purpose digital I/O pin                                                                                                                                                                                                              |  |

| SOSCSEL1:<br>SOSCSEL0 <sup>(2)</sup> | CW2<12:11> | Secondary Oscillator Power Mode Select bits  11 = Default (high drive strength) mode  01 = Low-Power (low drive strength) mode  x0 = Reserved; do not use                                                                                                                                                                             |  |

| POSCMD1:<br>POSCMD0                  | CW2<1:0>   | Primary Oscillator Mode Select bits  11 = Primary oscillator disabled  10 = HS Crystal Oscillator mode  01 = XT Crystal Oscillator mode  00 = EC (External Clock) mode                                                                                                                                                                |  |

| WDTPOST3:<br>WDTPOST0                | CW1<3:0>   | Watchdog Timer Prescaler bit  1111 = 1:32,768  1110 = 1:16,384                                                                                                                                                                                                                                                                        |  |

| WDTPRE                               | CW1<4>     | Watchdog Timer Postscaler bit  1 = 1:128  0 = 1:32                                                                                                                                                                                                                                                                                    |  |

| WINDIS                               | CW1<6>     | Windowed WDT bit  1 = Watchdog Timer in Non-Window mode  0 = Watchdog Timer in Window mode; FWDTEN must be '1'                                                                                                                                                                                                                        |  |

| WUTSEL1:<br>WUTSEL0 <sup>(2)</sup>   | CW2<14:13> | Voltage Regulator Standby Mode Wake-up Time Select bits  11 = Default regulator wake time used  01 = Fast regulator wake time used  x0 = Reserved; do not use                                                                                                                                                                         |  |

Note 1: Available on 28 and 44-pin packages only.

2: Available only on 28 and 44-pin devices with a silicon revision of 3042h or higher.

#### 4.6.2 PROGRAMMING METHODOLOGY

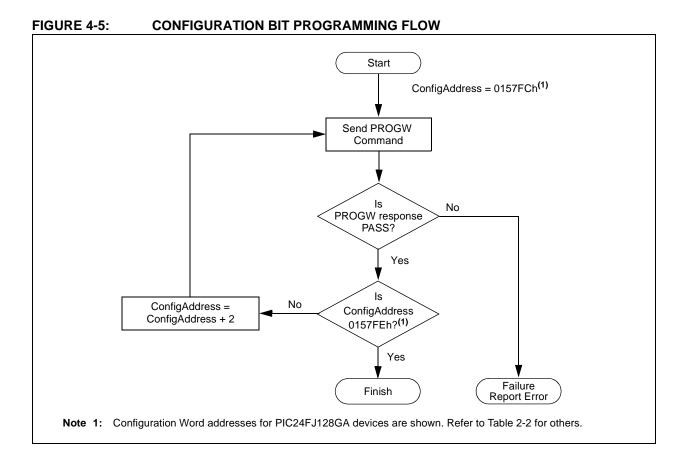

Configuration bits may be programmed a single byte at a time using the PROGW command. This command specifies the configuration data and Configuration register address. When Configuration bits are programmed, any unimplemented or reserved bits must be programmed with a '1'.

Two PROGW commands are required to program the Configuration bits. A flowchart for Configuration bit programming is shown in Figure 4-5.

#### Note:

If the General Segment Code-Protect bit (GCP) is programmed to '0', code memory is code-protected and can not be read. Code memory must be verified before enabling read protection. See Section 4.6.4 "Code-Protect Configuration Bits" for more information about code-protect Configuration bits.

### 4.6.3 PROGRAMMING VERIFICATION

After the Configuration bits are programmed, the contents of memory should be verified to ensure that the programming was successful. Verification requires the Configuration bits to be read back and compared against the copy held in the programmer's buffer. The READP command reads back the programmed Configuration bits and verifies that the programming was successful.

# 4.6.4 CODE-PROTECT CONFIGURATION BITS

CW1 Configuration register controls code protection for the PIC24FJXXXGA0XX family. Two forms of code protection are provided. One form prevents code memory from being written (write protection) and the other prevents code memory from being read (read protection).

GWRP (CW1<12>) controls write protection and GCP (CW1<13>) controls read protection. Protection is enabled when the respective bit is '0'.

Erasing sets GWRP and GCP to '1', which allows the device to be programmed.

When write protection is enabled (GWRP = 0), any programming operation to code memory will fail.

When read protection is enabled (GCP = 0), any read from code memory will cause a 0h to be read, regardless of the actual contents of code memory. Since the programming executive always verifies what it programs, attempting to program code memory with read protection enabled also will result in failure.

It is imperative that both GWRP and GCP are '1' while the device is being programmed and verified. Only after the device is programmed and verified should either GWRP or GCP be programmed to '0' (see **Section 4.6** "Configuration Bits Programming").

Note:

Bulk Erasing in ICSP mode is the only way to reprogram code-protect bits from an ON state ('0') to an Off state ('1').

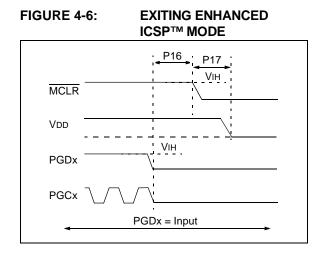

### 4.7 Exiting Enhanced ICSP Mode

Exiting Program/Verify mode is done by removing VIH from MCLR, as shown in Figure 4-6. The only requirement for exit is that an interval, P16, should elapse between the last clock and program signals on PGCx and PGDx before removing VIH.

# 5.2 Programming Executive Commands

The programming executive command set is shown in Table 5-1. This table contains the opcode, mnemonic, length, time-out and description for each command. Functional details on each command are provided in **Section 5.2.4 "Command Descriptions"**.

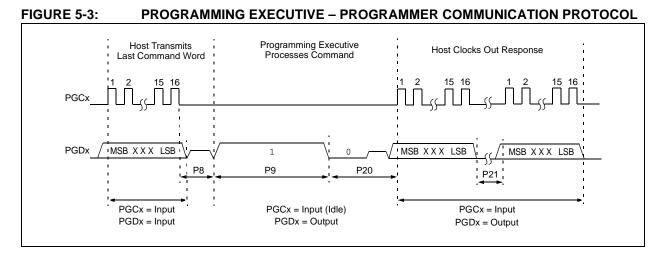

#### 5.2.1 COMMAND FORMAT

All programming executive commands have a general format consisting of a 16-bit header and any required data for the command (see Figure 5-4). The 16-bit header consists of a 4-bit opcode field, which is used to identify the command, followed by a 12-bit command length field.

FIGURE 5-4: COMMAND FORMAT

| 15 12                                | 11                                    | 0 |  |  |

|--------------------------------------|---------------------------------------|---|--|--|

| Opcode                               | Length                                |   |  |  |

| Comm                                 | Command Data First Word (if required) |   |  |  |

| •                                    |                                       |   |  |  |

| •                                    |                                       |   |  |  |

| Command Data Last Word (if required) |                                       |   |  |  |

|                                      |                                       |   |  |  |

The command opcode must match one of those in the command set. Any command that is received which does not match the list in Table 5-1 will return a "NACK" response (see **Section 5.3.1.1 "Opcode Field"**).

The command length is represented in 16-bit words since the SPI operates in 16-bit mode. The programming executive uses the command length field to determine the number of words to read from the SPI port. If the value of this field is incorrect, the command will not be properly received by the programming executive.

#### 5.2.2 PACKED DATA FORMAT

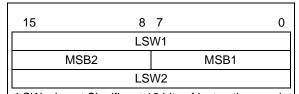

When 24-bit instruction words are transferred across the 16-bit SPI interface, they are packed to conserve space using the format shown in Figure 5-5. This format minimizes traffic over the SPI and provides the programming executive with data that is properly aligned for performing table write operations.

FIGURE 5-5: PACKED INSTRUCTION WORD FORMAT

LSWx: Least Significant 16 bits of instruction word MSBx: Most Significant Bytes of instruction word

Note: When the number of instruction words transferred is odd, MSB2 is zero and LSW2 can not be transmitted.

# 5.2.3 PROGRAMMING EXECUTIVE ERROR HANDLING

The programming executive will "NACK" all unsupported commands. Additionally, due to the memory constraints of the programming executive, no checking is performed on the data contained in the programmer command. It is the responsibility of the programmer to command the programming executive with valid command arguments or the programming operation may fail. Additional information on error handling is provided in **Section 5.3.1.3** "QE\_Code Field".

### 5.2.8 PROGC COMMAND

| 15       | 12      | 11 8 7 |  | 0        |      |  |

|----------|---------|--------|--|----------|------|--|

| Opcode   |         |        |  | Le       | ngth |  |

| Reserved |         |        |  | Addr_MSB |      |  |

|          | Addr_LS |        |  |          |      |  |

|          | Data    |        |  |          |      |  |

| Field    | Description                                             |  |  |

|----------|---------------------------------------------------------|--|--|

| Opcode   | 4h                                                      |  |  |

| Length   | 4h                                                      |  |  |

| Reserved | 0h                                                      |  |  |

| Addr_MSB | MSB of 24-bit destination address                       |  |  |

| Addr_LS  | Least Significant 16 bits of 24-bit destination address |  |  |

| Data     | 8-bit data word                                         |  |  |

The PROGC command instructs the programming executive to program a single Device ID register located at the specified memory address.

After the specified data word has been programmed to code memory, the programming executive verifies the programmed data against the data in the command.

### **Expected Response (2 words):**

1400h 0002h

### 5.2.9 PROGP COMMAND

D\_96

| Field    | Description                                             |  |

|----------|---------------------------------------------------------|--|

| Opcode   | 5h                                                      |  |

| Length   | 63h                                                     |  |

| Reserved | 0h                                                      |  |

| Addr_MSB | MSB of 24-bit destination address                       |  |

| Addr_LS  | Least Significant 16 bits of 24-bit destination address |  |

| D_1      | 16-bit data word 1                                      |  |

| D_2      | 16-bit data word 2                                      |  |

| •••      | 16-bit data word 3 through 95                           |  |

| D_96     | 16-bit data word 96                                     |  |

The PROGP command instructs the programming executive to program one row of code memory, including Configuration Words (64 instruction words), to the specified memory address. Programming begins with the row address specified in the command. The destination address should be a multiple of 80h.

The data to program to memory, located in command words, D\_1 through D\_96, must be arranged using the packed instruction word format shown in Figure 5-5.

After all data has been programmed to code memory, the programming executive verifies the programmed data against the data in the command.

### **Expected Response (2 words):**

1500h 0002h

**Note:** Refer to Table 2-3 for code memory size information.

# 5.4 Programming the Programming Executive to Memory

### 5.4.1 OVERVIEW

If it is determined that the programming executive is not present in executive memory (as described in Section 4.2 "Confirming the Presence of the Programming Executive"), it must be programmed into executive memory using ICSP, as described in Section 3.0 "Device Programming – ICSP".

Storing the programming executive to executive memory is similar to normal programming of code memory. Namely, the executive memory must be erased, and then the programming executive must be programmed 64 words at a time. Erasing the last page of executive memory will cause the FRC oscillator calibration settings and device diagnostic data in the Diagnostic and Calibration Words, at addresses 8007F0h to 8007FEh, to be erased. In order to retain this calibration, these memory locations should be read and stored prior to erasing executive memory. They should then be reprogrammed in the last words of program memory. This control flow is summarized in Table 5-5.

TABLE 5-5: PROGRAMMING THE PROGRAMMING EXECUTIVE

| IABLE 3-3.          | ABLE 5-5: PROGRAMMING THE PROGRAMMING EXECUTIVE |                  |                                                                    |

|---------------------|-------------------------------------------------|------------------|--------------------------------------------------------------------|

| Command<br>(Binary) | Data<br>(Hex)                                   |                  | Description                                                        |

| Step 1: Exit        | Reset vector and e                              | rase executive   | e memory.                                                          |

| 0000                | 000000                                          | NOP              |                                                                    |

| 0000                | 040200                                          | GOTO             | 0x200                                                              |

| 0000                | 000000                                          | NOP              |                                                                    |

| Step 2: Initia      | alize pointers to rea                           | d Diagnostic a   | and Calibration Words for storage in W6-W13.                       |

| 0000                | 200800                                          | MOV              | #0x80, W0                                                          |

| 0000                | 880190                                          | MOV              | WO, TBLPAG                                                         |

| 0000                | 207F00                                          | MOV              | #0x07F0, W1                                                        |

| 0000                | 2000C2                                          | MOV              | #0xC, W2                                                           |

| 0000                | 000000                                          | NOP              |                                                                    |

| Step 3: Rep         | eat this step 8 times                           | s to read Diag   | nostic and Calibration Words, storing them in W registers, W6-W13. |

| 0000                | BA1931                                          | TBLRDL           | [W1++].[W2++]                                                      |

| 0000                | 000000                                          | NOP              |                                                                    |

| 0000                | 000000                                          | NOP              |                                                                    |

| Step 4: Initia      | alize the NVMCON                                | to erase exec    | utive memory.                                                      |

| 0000                | 240420                                          | MOV              | #0x4042, W0                                                        |

| 0000                | 883B00                                          | MOV              | WO, NVMCON                                                         |

| Step 5: Initia      | alize Erase Pointers                            | to first page of | of executive and then initiate the erase cycle.                    |

| 0000                | 200800                                          | MOV              | #0x80, W0                                                          |

| 0000                | 880190                                          | MOV              | WO, TBLPAG                                                         |

| 0000                | 200001                                          | MOV              | #0x0, W1                                                           |

| 0000                | 000000                                          | NOP              |                                                                    |

| 0000                | BB0881                                          | TBLWTL           | W1, [W1]                                                           |

| 0000                | 000000                                          | NOP              |                                                                    |

| 0000                | 000000                                          | NOP              |                                                                    |

| 0000                | A8E761                                          | BSET             | NVMCON, #15                                                        |

| 00000               | 000000                                          | NOP              |                                                                    |

| 0000                | 000000                                          | NOP              |                                                                    |

| Stop 6: Don         | oot this stan to noll                           | the MP hit (hi   | t 15 of NV/MCON) until it is algored by the hardware               |

|                     |                                                 | `                | it 15 of NVMCON) until it is cleared by the hardware.              |

| 0000                | 040200                                          | GOTO             | 0x200                                                              |

| 0000                | 000000                                          | NOP              | NUMCON 110                                                         |

| 0000                | 803B02                                          | MOV              | NVMCON, W2                                                         |

| 0000                | 883C22                                          | MOV              | W2, VISI                                                           |

| 0001                | 000000                                          | NOP              | and only of the MICI wenighted                                     |

| 0000                | <visi><br/>000000</visi>                        | NOP              | contents of the VISI register.                                     |

| 0000                | 00000                                           | 1101             |                                                                    |

| Command Data (Binary) (Hex) |                                                                    | Description                                                                                     |  |  |  |

|-----------------------------|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|--|--|--|

|                             |                                                                    | o erase the second page of executive memory. The W1 Pointer should be point to the second page. |  |  |  |

|                             |                                                                    | IVMCON to write stored diagnostic and calibration as single words. Initialize W1                |  |  |  |

|                             |                                                                    | ead Pointers to rewrite stored Diagnostic and Calibration Words.                                |  |  |  |

|                             |                                                                    |                                                                                                 |  |  |  |

| 0000                        | 200800                                                             | MOV #0x80, W0                                                                                   |  |  |  |

| 0000<br>0000                | 880190                                                             | MOV W0, TBLPAG MOV #0x4003, W1                                                                  |  |  |  |

| 0000                        | 240031<br>883B01                                                   | MOV #0x4003, W1<br>MOV W1, NVMCON                                                               |  |  |  |

| 0000                        | 207F00                                                             | MOV #0x07F0, W1                                                                                 |  |  |  |

| 0000                        | 207F00<br>2000C2                                                   | MOV #0xC, W2                                                                                    |  |  |  |

| 0000                        | 000000                                                             | NOP                                                                                             |  |  |  |

|                             |                                                                    | e word of calibration data and initiate single-word write cycle.                                |  |  |  |

|                             |                                                                    |                                                                                                 |  |  |  |

| 0000                        | BB18B2                                                             | TBLWTL [W2++], [W1++]                                                                           |  |  |  |

| 0000                        | 000000                                                             | NOP                                                                                             |  |  |  |

| 0000                        | 000000                                                             | NOP                                                                                             |  |  |  |

| 0000                        | A8E761                                                             | BSET NVMCON, #15                                                                                |  |  |  |

| 0000<br>0000                | 000000                                                             | NOP<br>NOD                                                                                      |  |  |  |

|                             |                                                                    | NOP                                                                                             |  |  |  |

|                             |                                                                    | the WR bit (bit 15 of NVMCON) until it is cleared by the hardware.                              |  |  |  |

| 0000                        | 040200                                                             | GOTO 0x200                                                                                      |  |  |  |

| 0000                        | 000000                                                             | NOP                                                                                             |  |  |  |

| 0000                        | 803B00                                                             | MOV NVMCON, W0                                                                                  |  |  |  |

| 0000                        | 883C20                                                             | MOV W0, VISI                                                                                    |  |  |  |

| 0000                        | 000000                                                             | NOP                                                                                             |  |  |  |

| 0001                        | <visi></visi>                                                      | Clock out contents of VISI register.                                                            |  |  |  |

| 0000                        | 000000                                                             | NOP                                                                                             |  |  |  |

|                             | eat steps 9-10 seve<br>k into program mem                          | en more times to program the remainder of the Diagnostic and Calibration Words                  |  |  |  |

|                             |                                                                    | to program 64 instruction words.                                                                |  |  |  |

|                             |                                                                    |                                                                                                 |  |  |  |

| 0000                        | 240010                                                             | MOV #0x4001, W0                                                                                 |  |  |  |

| 0000                        | 883B00                                                             | MOV W0, NVMCON                                                                                  |  |  |  |

| Step 13: Initia             | alize TBLPAG and th                                                | he Write Pointer (W7).                                                                          |  |  |  |

| 0000                        | 200800                                                             | MOV #0x80, W0                                                                                   |  |  |  |

| 0000                        | 880190                                                             | MOV W0, TBLPAG                                                                                  |  |  |  |

| 0000                        | EB0380                                                             | CLR W7                                                                                          |  |  |  |

| 0000                        | 000000                                                             | NOP                                                                                             |  |  |  |

| Step 14: Loa                | d W0:W5 with the no                                                | ext four words of packed programming executive code and initialize W6 for                       |  |  |  |

| 5.50                        | gramming. Programr<br>nter and W7 as a Wr                          | ming starts from the base of executive memory (800000h) using W6 as a Read                      |  |  |  |

|                             |                                                                    |                                                                                                 |  |  |  |

| Poir                        |                                                                    | MOSZ # <i cwo=""> WO</i>                                                                        |  |  |  |

| Poir<br>0000                | 2 <lsw0>0</lsw0>                                                   | MOV # <lsw0>, W0</lsw0>                                                                         |  |  |  |

| 9000<br>0000                | 2 <lsw0>0<br/>2<msb1:msb0>1</msb1:msb0></lsw0>                     | MOV # <msb1:msb0>, W1</msb1:msb0>                                                               |  |  |  |

| 9000<br>0000<br>0000        | 2 <lsw0>0<br/>2<msb1:msb0>1<br/>2<lsw1>2</lsw1></msb1:msb0></lsw0> | MOV # <msb1:msb0>, W1<br/>MOV #<lsw1>, W2</lsw1></msb1:msb0>                                    |  |  |  |

| 9000<br>0000                | 2 <lsw0>0<br/>2<msb1:msb0>1</msb1:msb0></lsw0>                     | MOV # <msb1:msb0>, W1</msb1:msb0>                                                               |  |  |  |

TABLE 5-5: PROGRAMMING THE PROGRAMMING EXECUTIVE (CONTINUED)

| Command<br>(Binary) | Data<br>(Hex)       | Description                                                                       |

|---------------------|---------------------|-----------------------------------------------------------------------------------|

| Step 15: Set t      | the Read Pointer    | (W6) and load the (next four write) latches.                                      |

| 0000                | EB0300              | CLR W6                                                                            |

| 0000                | 000000              | NOP                                                                               |

| 0000                | BB0BB6              | TBLWTL [W6++], [W7]                                                               |

| 0000                | 000000              | NOP                                                                               |

| 0000                | 000000              | NOP                                                                               |

| 0000                | BBDBB6              | TBLWTH.B[W6++], [W7++]                                                            |

| 0000                | 000000              | NOP                                                                               |

| 0000                | 000000              | NOP                                                                               |

| 0000                | BBEBB6              | TBLWTH.B[W6++], [++W7]                                                            |

| 0000                | 000000              | NOP                                                                               |

| 0000                | 000000              | NOP                                                                               |

| 0000                | BB1BB6              | TBLWTL [W6++], [W7++]                                                             |

| 0000                | 000000              | NOP                                                                               |

| 0000                | 000000              | NOP                                                                               |

| 0000                | BB0BB6              | TBLWTL [W6++], [W7]                                                               |

| 0000                | 000000              | NOP                                                                               |

| 0000                | 000000              | NOP                                                                               |

| 0000                | BBDBB6              | TBLWTH.B[W6++], [W7++]                                                            |

| 0000                | 000000              | NOP                                                                               |

| 0000                | 000000              | NOP                                                                               |

| 0000                | BBEBB6              | TBLWTH.B[W6++], [++W7]                                                            |

| 0000                | 000000              | NOP                                                                               |

| 0000                | 000000              | NOP                                                                               |

| 0000                | BB1BB6              | TBLWTL [W6++], [W7++]                                                             |

| 0000                | 000000              | NOP                                                                               |

| 0000                | 000000              | NOP                                                                               |

| Step 16: Rep        | eat Steps 14-15,    | sixteen times, to load the write latches for the 64 instructions.                 |

| Step 17: Initia     | ate the programm    | ing cycle.                                                                        |

| 0000                | A8E761              | BSET NVMCON, #15                                                                  |

| 0000                | 000000              | NOP                                                                               |

| 0000                | 000000              | NOP                                                                               |

| Step 18: Rep        | eat this step to po | oll the WR bit (bit 15 of NVMCON) until it is cleared by the hardware.            |

| 0000                | 040200              | GOTO 0x200                                                                        |

| 0000                | 000000              | NOP                                                                               |

| 0000                | 803B02              | MOV NVMCON, W2                                                                    |

| 0000                | 883C22              | MOV W2, VISI                                                                      |

| 0000                | 000000              | NOP                                                                               |

| 0001                | <visi></visi>       | Clock out contents of the VISI register.                                          |

| 0000                | 000000              | NOP                                                                               |

| Step 19: Rese       | et the device inter | nal PC.                                                                           |

| 0000                | 040200              | GOTO 0x200                                                                        |

| 0000                | 000000              | NOP                                                                               |

| •                   | •                   | ntil all 16 rows of executive memory have been programmed. On the final row, make |

**Step 20:** Repeat Steps 14-19 until all 16 rows of executive memory have been programmed. On the final row, make sure to initialize the write latches at the Diagnostic and Calibration Words locations with 0xFFFFFF to ensure that the calibration is not overwritten.

### 5.4.2 PROGRAMMING VERIFICATION

After the programming executive has been programmed to executive memory using ICSP, it must be verified. Verification is performed by reading out the contents of executive memory and comparing it with the image of the programming executive stored in the programmer.

Reading the contents of executive memory can be performed using the same technique described in **Section 3.8** "**Reading Code Memory**". A procedure for reading executive memory is shown in Table 5-6. Note that in Step 2, the TBLPAG register is set to 80h, such that executive memory may be read. The last eight words of executive memory should be verified with stored values of the Diagnostic and Calibration Words to ensure accuracy.

TABLE 5-6: READING EXECUTIVE MEMORY

| IABLE 5-6:                     | KEADING                         | EXECUTIVE MEMORY                                                                              |  |  |  |

|--------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------|--|--|--|

| Command<br>(Binary)            | Data<br>(Hex)                   | Description                                                                                   |  |  |  |

| Step 1: Exit the Reset vector. |                                 |                                                                                               |  |  |  |

| 0000                           | 000000                          | NOP                                                                                           |  |  |  |

| 0000                           | 040200                          | GOTO 0x200                                                                                    |  |  |  |

| 0000                           | 000000                          | NOP                                                                                           |  |  |  |

| Step 2: Initia                 | lize TBLPAG a                   | nd the Read Pointer (W6) for TBLRD instruction.                                               |  |  |  |

| 0000                           | 200800                          | MOV #0x80, W0                                                                                 |  |  |  |

| 0000                           | 880190                          | MOV W0, TBLPAG                                                                                |  |  |  |

| 0000                           | EB0300                          | CLR W6                                                                                        |  |  |  |

| Step 3: Initia                 | lize the Write P                | ointer (W7) to point to the VISI register.                                                    |  |  |  |

| 0000                           | 207847                          | MOV #VISI, W7                                                                                 |  |  |  |

| 0000                           | 000000                          | NOP                                                                                           |  |  |  |

|                                | d and clock out<br>g the REGOUT | the contents of the next two locations of executive memory through the VISI register command. |  |  |  |

| 0000                           | BA0B96                          | TBLRDL [W6], [W7]                                                                             |  |  |  |

| 0000                           | 000000                          | NOP                                                                                           |  |  |  |

| 0000                           | 000000                          | NOP                                                                                           |  |  |  |

| 0001                           | <visi></visi>                   | Clock out contents of VISI register                                                           |  |  |  |

| 0000                           | 000000                          | NOP                                                                                           |  |  |  |

| 0000                           | BADBB6                          | TBLRDH.B[W6++], [W7++]                                                                        |  |  |  |

| 0000                           | 000000                          | NOP                                                                                           |  |  |  |

| 0000                           | 000000                          | NOP                                                                                           |  |  |  |

| 0000                           | BAD3D6                          | TBLRDH.B[++W6], [W7]                                                                          |  |  |  |

| 0000                           | 000000                          | NOP                                                                                           |  |  |  |

| 0000                           | 000000                          | NOP                                                                                           |  |  |  |

| 0001                           | <visi></visi>                   | Clock out contents of VISI register                                                           |  |  |  |

| 0000                           | 000000                          | NOP                                                                                           |  |  |  |

| 0000                           | BA0BB6                          | TBLRDL [W6++], [W7]                                                                           |  |  |  |

| 0000                           | 000000                          | NOP                                                                                           |  |  |  |

| 0000                           | 000000                          | NOP                                                                                           |  |  |  |

| 0001                           | <visi></visi>                   | Clock out contents of VISI register                                                           |  |  |  |

| 0000                           | 000000                          | NOP                                                                                           |  |  |  |

| Step 5: Rese                   | et the device int               | ernal PC.                                                                                     |  |  |  |

| 0000                           | 040200                          | GOTO 0x200                                                                                    |  |  |  |

| 0000                           | 000000                          | NOP                                                                                           |  |  |  |

| Step 6: Repe                   | eat Steps 4 and                 | 5 until all desired code memory is read.                                                      |  |  |  |

### 6.2 Checksum Computation

Checksums for the PIC24FJXXXGA0XX family are 16 bits in size. The checksum is calculated by summing the following:

- · Contents of code memory locations

- · Contents of Configuration registers

Table 6-4 describes how to calculate the checksum for each device. All memory locations are summed, one byte at a time, using only their native data size. More specifically, Configuration registers are summed by adding the lower two bytes of these locations (the upper byte is ignored), while code memory is summed by adding all three bytes of code memory.

TABLE 6-4: CHECKSUM COMPUTATION

| Device             | Read Code<br>Protection | Checksum Computation | Erased<br>Checksum<br>Value | Checksum with<br>0xAAAAAA at 0x0 and Last<br>Code Address |

|--------------------|-------------------------|----------------------|-----------------------------|-----------------------------------------------------------|

| DIO045 1400 4000   | Disabled                | CFGB + SUM(0:02BFB)  | 0xBB5A                      | 0xB95C                                                    |

| PIC24FJ16GA002     | Enabled                 | 0                    | 0x0000                      | 0x0000                                                    |

| DIC 24E 146C 4004  | Disabled                | CFGB + SUM(0:02BFB)  | 0xBB5A                      | 0xB95C                                                    |

| PIC24FJ16GA004     | Enabled                 | 0                    | 0x0000                      | 0x0000                                                    |

| DIC 24E 122C A 002 | Disabled                | CFGB + SUM(0:057FB)  | 0x795A                      | 0x775C                                                    |

| PIC24FJ32GA002     | Enabled                 | 0                    | 0x0000                      | 0x0000                                                    |

| DIC 24E 122C A004  | Disabled                | CFGB + SUM(0:057FB)  | 0x795A                      | 0x775C                                                    |

| PIC24FJ32GA004     | Enabled                 | 0                    | 0x0000                      | 0x0000                                                    |

| DICO4E 140C 4000   | Disabled                | CFGB + SUM(0:083FB)  | 0x375A                      | 0x355C                                                    |

| PIC24FJ48GA002     | Enabled                 | 0                    | 0x0000                      | 0x0000                                                    |

| DICO4E 140C 4004   | Disabled                | CFGB + SUM(0:083FB)  | 0x375A                      | 0x355C                                                    |

| PIC24FJ48GA004     | Enabled                 | 0                    | 0x0000                      | 0x0000                                                    |

| DICOAE ICAC A000   | Disabled                | CFGB + SUM(0:0ABFB)  | 0xFB5A                      | 0xF95C                                                    |

| PIC24FJ64GA002     | Enabled                 | 0                    | 0x0000                      | 0x0000                                                    |

| DICOAE IGAC AGGA   | Disabled                | CFGB + SUM(0:0ABFB)  | 0xFB5A                      | 0xF95C                                                    |

| PIC24FJ64GA004     | Enabled                 | 0                    | 0x0000                      | 0x0000                                                    |

| DIO045 1040 4000   | Disabled                | CFGB + SUM(0:0ABFB)  | 0xFACC                      | 0xF8CE                                                    |

| PIC24FJ64GA006     | Enabled                 | 0                    | 0x0000                      | 0x0000                                                    |

| DICO 45 10 40 4000 | Disabled                | CFGB + SUM(0:0ABFB)  | 0xFACC                      | 0xF8CE                                                    |

| PIC24FJ64GA008     | Enabled                 | 0                    | 0x0000                      | 0x0000                                                    |

| DICOAE ICACAGAG    | Disabled                | CFGB + SUM(0:0ABFB)  | 0xFACC                      | 0xF8CE                                                    |

| PIC24FJ64GA010     | Enabled                 | 0                    | 0x0000                      | 0x0000                                                    |

| DIO045 1000 1000   | Disabled                | CFGB + SUM(0:0FFFB)  | 0x7CCC                      | 0x7ACE                                                    |

| PIC24FJ96GA006     | Enabled                 | 0                    | 0x0000                      | 0x0000                                                    |

| DIC24E 1000 A000   | Disabled                | CFGB + SUM(0:0FFFB)  | 0x7CCC                      | 0x7ACE                                                    |

| PIC24FJ96GA008     | Enabled                 | 0                    | 0x0000                      | 0x0000                                                    |

| DIC24E 1000 A040   | Disabled                | CFGB + SUM(0:0FFFB)  | 0x7CCC                      | 0x7ACE                                                    |

| PIC24FJ96GA010     | Enabled                 | 0                    | 0x0000                      | 0x0000                                                    |

Legend: <u>Item</u> <u>Description</u>

SUM[a:b] = Byte sum of locations, a to b inclusive (all 3 bytes of code memory)

CFGB = Configuration Block (masked),

64/80/100-Pin Devices = Byte sum of (CW1 & 0x7DDF + CW2 & 0x87E3) 28/44-Pin Devices = Byte sum of (CW1 & 0x7FDF + CW2 & 0xFFF7)

Note: CW1 address is last location of implemented program memory; CW2 is (last location – 2).

### 7.0 AC/DC CHARACTERISTICS AND TIMING REQUIREMENTS

Standard Operating Conditions

Operating Temperature: 0°C to +70°C. Programming at +25°C is recommended.

| Operating Temperature: 0°C to +70°C. Programming at +25°C is recommended. |                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                               |                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |

|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|