Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 53                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 8K x 8                                                                            |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 18x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp206t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the dsPIC33FJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the latest family reference sections of the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

This document contains device specific information for the following devices:

- dsPIC33FJ64GP206

- dsPIC33FJ64GP306

- dsPIC33FJ64GP310

- dsPIC33FJ64GP706

- dsPIC33FJ64GP708

- dsPIC33FJ64GP710

- dsPIC33FJ128GP206

- dsPIC33FJ128GP306

- dsPIC33FJ128GP310

- dsPIC33FJ128GP706

- dsPIC33FJ128GP708

- dsPIC33FJ128GP710

- dsPIC33FJ256GP506

- dsPIC33FJ256GP510

- dsPIC33FJ256GP710

The dsPIC33FJXXXGPX06/X08/X10 General Purpose Family of device includes devices with a wide range of pin counts (64, 80 and 100), different program memory sizes (64 Kbytes, 128 Kbytes and 256 Kbytes) and different RAM sizes (8 Kbytes, 16 Kbytes and 30 Kbytes). This feature makes the family suitable for a wide variety of high-performance digital signal control applications. The device is pin compatible with the PIC24H family of devices, and also share a very high degree of compatibility with the dsPIC30F family devices. This allows for easy migration between device families as may be necessitated by the specific functionality, computational resource and system cost requirements of the application.

The dsPIC33FJXXXGPX06/X08/X10 device family employs a powerful 16-bit architecture that seamlessly integrates the control features of a Microcontroller (MCU) with the computational capabilities of a Digital Signal Processor (DSP). The resulting functionality is ideal for applications that rely on high-speed, repetitive computations, as well as control.

The DSP engine, dual 40-bit accumulators, hardware support for division operations, barrel shifter, 17 x 17 multiplier, a large array of 16-bit working registers and a wide variety of data addressing modes, together provide the dsPIC33FJXXXGPX06/X08/X10 Central Processing Unit (CPU) with extensive mathematical processing capability. Flexible and deterministic interrupt handling, coupled with a powerful array of peripherals, renders the dsPIC33FJXXXGPX06/X08/X10 devices suitable for control applications. Further, Direct Memory Access (DMA) enables overhead-free transfer of data between several peripherals and a dedicated DMA RAM. Reliable, field programmable Flash program memory ensures scalability of applications that use dsPIC33FJXXXGPX06/X08/X10 devices.

Figure 1-1 illustrates a general block diagram of the various core and peripheral modules in the dsPIC33FJXXXGPX06/X08/X10 family of devices. Table 1-1 provides the functions of the various pins illustrated in the pinout diagrams.

### 3.6.1 MULTIPLIER

The 17-bit x 17-bit multiplier is capable of signed or unsigned operation and can multiplex its output using a scaler to support either 1.31 fractional (Q31) or 32-bit integer results. Unsigned operands are zero-extended into the 17th bit of the multiplier input value. Signed operands are sign-extended into the 17th bit of the multiplier input value. The output of the 17-bit x 17-bit multiplier/scaler is a 33-bit value which is sign-extended to 40 bits. Integer data is inherently represented as a signed two's complement value, where the Most Significant bit (MSb) is defined as a sign bit. Generally speaking, the range of an N-bit two's complement integer is  $-2^{N-1}$  to  $2^{N-1}$  - 1. For a 16-bit integer, the data range is -32768 (0x8000) to 32767 (0x7FFF) including 0. For a 32-bit integer, the data range is -2,147,483,648 (0x8000 0000) to 2,147,483,647 (0x7FFF FFFF).

When the multiplier is configured for fractional multiplication, the data is represented as a two's complement fraction, where the MSb is defined as a sign bit and the radix point is implied to lie just after the sign bit (QX format). The range of an N-bit two's complement fraction with this implied radix point is -1.0 to  $(1 - 2^{1-N})$ . For a 16-bit fraction, the Q15 data range is -1.0 (0x8000) to 0.999969482 (0x7FFF) including 0 and has a precision of  $3.01518 \times 10^{-5}$ . In Fractional mode, the 16 x 16 multiply operation generates a 1.31 product which has a precision of  $4.65661 \times 10^{-10}$ .

The same multiplier is used to support the MCU multiply instructions which include integer 16-bit signed, unsigned and mixed sign multiplies.

The MUL instruction may be directed to use byte or word sized operands. Byte operands will direct a 16-bit result, and word operands will direct a 32-bit result to the specified register(s) in the W array.

## 3.6.2 DATA ACCUMULATORS AND ADDER/SUBTRACTER

The data accumulator consists of a 40-bit adder/subtracter with automatic sign extension logic. It can select one of two accumulators (A or B) as its pre-accumulation source and post-accumulation destination. For the ADD and LAC instructions, the data to be accumulated or loaded can be optionally scaled via the barrel shifter prior to accumulation.

## 3.6.2.1 Adder/Subtracter, Overflow and Saturation

The adder/subtracter is a 40-bit adder with an optional zero input into one side, and either true, or complement data into the other input. In the case of addition, the Carry/Borrow input is active-high and the other input is true data (not complemented), whereas in the case of subtraction, the Carry/Borrow input is active-low and the other input is complemented. The adder/subtracter generates Overflow Status bits, SA/SB and OA/OB, which are latched and reflected in the STATUS register:

- Overflow from bit 39: this is a catastrophic overflow in which the sign of the accumulator is destroyed.

- Overflow into guard bits 32 through 39: this is a recoverable overflow. This bit is set whenever all the guard bits are not identical to each other.

The adder has an additional saturation block which controls accumulator data saturation, if selected. It uses the result of the adder, the Overflow Status bits described above and the SAT<A:B> (CORCON<7:6>) and ACCSAT (CORCON<4>) mode control bits to determine when and to what value to saturate.

Six STATUS register bits have been provided to support saturation and overflow; they are:

- 1. OA:

- AccA overflowed into guard bits

- 2. OB:

AccB overflowed into guard bits

3. SA:

AccA saturated (bit 31 overflow and saturation) or

AccA overflowed into guard bits and saturated (bit 39 overflow and saturation)

4. SB:

AccB saturated (bit 31 overflow and saturation) or

AccB overflowed into guard bits and saturated (bit 39 overflow and saturation)

- 5. OAB:

- Logical OR of OA and OB

- SAB: Logical OR of SA and SB

The OA and OB bits are modified each time data passes through the adder/subtracter. When set, they indicate that the most recent operation has overflowed into the accumulator guard bits (bits 32 through 39). The OA and OB bits can also optionally generate an arithmetic warning trap when set and the corresponding Overflow Trap Flag Enable bits (OVATE, OVBTE) in the INTCON1 register (refer to **Section 7.0 "Interrupt Controller"**) are set. This allows the user to take immediate action, for example, to correct system gain.

### TABLE 4-27: PORTC REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|-----------|------|---------|---------|---------|---------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|-------|---------------|

| TRISC     | 02CC | TRISC15 | TRISC14 | TRISC13 | TRISC12 | _      | _      | _     | -     | —     | —     | _     | TRISC4 | TRISC3 | TRISC2 | TRISC1 | —     | F01E          |

| PORTC     | 02CE | RC15    | RC14    | RC13    | RC12    | _      | -      | -     | _     | _     | _     | _     | RC4    | RC3    | RC2    | RC1    | _     | xxxx          |

| LATC      | 02D0 | LATC15  | LATC14  | LATC13  | LATC12  | _      | -      | -     | _     | _     | _     | _     | LATC4  | LATC3  | LATC2  | LATC1  | _     | XXXX          |

|           |      |         |         |         |         |        |        |       |       |       |       |       |        |        |        |        |       |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

## TABLE 4-28: PORTD REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISD     | 02D2 | TRISD15 | TRISD14 | TRISD13 | TRISD12 | TRISD11 | TRISD10 | TRISD9 | TRISD8 | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | FFFF          |

| PORTD     | 02D4 | RD15    | RD14    | RD13    | RD12    | RD11    | RD10    | RD9    | RD8    | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | xxxx          |

| LATD      | 02D6 | LATD15  | LATD14  | LATD13  | LATD12  | LATD11  | LATD10  | LATD9  | LATD8  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | xxxx          |

| ODCD      | 06D2 | ODCD15  | ODCD14  | ODCD13  | ODCD12  | ODCD11  | ODCD10  | ODCD9  | ODCD8  | ODCD7  | ODCD6  | ODCD5  | ODCD4  | ODCD3  | ODCD2  | ODCD1  | ODCD0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

#### TABLE 4-29: PORTE REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISE     | 02D8 | —      | -      | —      | —      | —      | _      | -     | -     | TRISE7 | TRISE6 | TRISE5 | TRISE4 | TRISE3 | TRISE2 | TRISE1 | TRISE0 | 00FF          |

| PORTE     | 02DA | _      | _      | _      | _      | _      | _      | _     | _     | RE7    | RE6    | RE5    | RE4    | RE3    | RE2    | RE1    | RE0    | xxxx          |

| LATE      | 02DC | _      | _      | _      | _      | _      | _      | _     | _     | LATE7  | LATE6  | LATE5  | LATE4  | LATE3  | LATE2  | LATE1  | LATE0  | xxxx          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

### TABLE 4-30: PORTF REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All Resets |

|-----------|------|--------|--------|---------|---------|--------|--------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| TRISF     | 02DE | _      | -      | TRISF13 | TRISF12 | _      | _      | _     | TRISF8 | TRISF7 | TRISF6 | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 | TRISF0 | 31FF       |

| PORTF     | 02E0 | _      | _      | RF13    | RF12    | _      | _      | _     | RF8    | RF7    | RF6    | RF5    | RF4    | RF3    | RF2    | RF1    | RF0    | xxxx       |

| LATF      | 02E2 | _      | -      | LATF13  | LATF12  | _      | -      | _     | LATF8  | LATF7  | LATF6  | LATF5  | LATF4  | LATF3  | LATF2  | LATF1  | LATF0  | xxxx       |

| ODCF      | 06DE | _      | -      | ODCF13  | ODCF12  | _      | -      | _     | ODCF8  | ODCF7  | ODCF6  | ODCF5  | ODCF4  | ODCF3  | ODCF2  | ODCF1  | ODCF0  | 0000       |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

### REGISTER 7-12: IEC2: INTERRUPT ENABLE CONTROL REGISTER 2 (CONTINUED)

- bit 2 C1RXIE: ECAN1 Receive Data Ready Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

- bit 1 SPI2IE: SPI2 Event Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

- bit 0 SPI2EIE: SPI2 Error Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

| REGISTER 7      | -13: IEC3:                                                                | INTERRUPT                            | ENABLE C        | ONTROL RE        | GISTER 3         |                 |       |  |  |

|-----------------|---------------------------------------------------------------------------|--------------------------------------|-----------------|------------------|------------------|-----------------|-------|--|--|

| U-0             | U-0                                                                       | R/W-0                                | R/W-0           | R/W-0            | U-0              | U-0             | R/W-0 |  |  |

| —               | _                                                                         | DMA5IE                               | DCIIE           | DCIEIE           | _                | —               | C2IE  |  |  |

| bit 15          |                                                                           |                                      |                 |                  |                  |                 | bit 8 |  |  |

| R/W-0           | R/W-0                                                                     | R/W-0                                | R/W-0           | R/W-0            | R/W-0            | R/W-0           | R/W-0 |  |  |

| C2RXIE          | INT4IE                                                                    | INT3IE                               | T9IE            | T8IE             | MI2C2IE          | SI2C2IE         | T7IE  |  |  |

| bit 7           |                                                                           | INTOL                                | TOL             | TOL              | WIZOZIE          | OIZOZIL         | bit C |  |  |

|                 |                                                                           |                                      |                 |                  |                  |                 |       |  |  |

| Legend:         |                                                                           |                                      |                 |                  |                  |                 |       |  |  |

| R = Readable    | bit                                                                       | W = Writable                         | bit             | U = Unimple      | mented bit, read | as '0'          |       |  |  |

| -n = Value at F | POR                                                                       | '1' = Bit is set                     |                 | '0' = Bit is cle | eared            | x = Bit is unkr | nown  |  |  |

| bit 15-14       | Unimplomon                                                                | ted: Read as '                       | o'              |                  |                  |                 |       |  |  |

| bit 13          | -                                                                         |                                      |                 | Complete Inter   | rupt Enable bit  |                 |       |  |  |

| bit 15          | 1 = Interrupt r                                                           | request enable<br>request not enable | d               |                  | iupt Enable bit  |                 |       |  |  |

| bit 12          | •                                                                         | vent Interrupt E                     |                 |                  |                  |                 |       |  |  |

|                 |                                                                           | equest enable                        |                 |                  |                  |                 |       |  |  |

| bit 11          | •                                                                         | request not ena<br>Error Interrupt   |                 |                  |                  |                 |       |  |  |

|                 |                                                                           | request enable                       |                 |                  |                  |                 |       |  |  |

|                 |                                                                           | request not enable                   |                 |                  |                  |                 |       |  |  |

| bit 10-9        | Unimplemen                                                                | ted: Read as '                       | 0'              |                  |                  |                 |       |  |  |

| bit 8           | C2IE: ECAN2                                                               | 2 Event Interrup                     | ot Enable bit   |                  |                  |                 |       |  |  |

|                 |                                                                           | request enable<br>request not ena    |                 |                  |                  |                 |       |  |  |

| bit 7           | C2RXIE: ECA                                                               | AN2 Receive D                        | ata Ready Int   | errupt Enable    | bit              |                 |       |  |  |

|                 |                                                                           | request enable                       |                 |                  |                  |                 |       |  |  |

| <b>h</b> # 0    | •                                                                         | request not ena                      |                 |                  |                  |                 |       |  |  |

| bit 6           |                                                                           | nal Interrupt 4 request enable       |                 |                  |                  |                 |       |  |  |

|                 | •                                                                         | request not enable                   |                 |                  |                  |                 |       |  |  |

| bit 5           | INT3IE: Exter                                                             | mal Interrupt 3                      | Enable bit      |                  |                  |                 |       |  |  |

|                 |                                                                           | request enable<br>request not ena    |                 |                  |                  |                 |       |  |  |

| bit 4           | T9IE: Timer9                                                              | Interrupt Enab                       | le bit          |                  |                  |                 |       |  |  |

|                 |                                                                           | request enable                       |                 |                  |                  |                 |       |  |  |

| hit 2           | -                                                                         | request not ena                      |                 |                  |                  |                 |       |  |  |

| bit 3           | <b>T8IE:</b> Timer8 Interrupt Enable bit<br>1 = Interrupt request enabled |                                      |                 |                  |                  |                 |       |  |  |

|                 |                                                                           | request not ena                      |                 |                  |                  |                 |       |  |  |

| bit 2           | MI2C2IE: 12C                                                              | 2 Master Even                        | its Interrupt E | nable bit        |                  |                 |       |  |  |

|                 |                                                                           | request enable<br>request not ena    |                 |                  |                  |                 |       |  |  |

| bit 1           | SI2C2IE: 12C                                                              | 2 Slave Events                       | Interrupt Ena   | able bit         |                  |                 |       |  |  |

|                 |                                                                           | equest enable                        |                 |                  |                  |                 |       |  |  |

|                 | -                                                                         | request not ena                      |                 |                  |                  |                 |       |  |  |

| bit 0           |                                                                           | Interrupt Enab                       |                 |                  |                  |                 |       |  |  |

|                 |                                                                           | request enable<br>request not ena    |                 |                  |                  |                 |       |  |  |

#### REGISTER 8-2: DMAxREQ: DMA CHANNEL x IRQ SELECT REGISTER

| R/W-0                | U-0   |

|----------------------|-----|-----|-----|-----|-----|-----|-------|

| FORCE <sup>(1)</sup> | —   | —   | —   | —   | —   | —   | —     |

| bit 15               |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-0                  |

|-------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| —     | IRQSEL6 <sup>(2)</sup> | IRQSEL5 <sup>(2)</sup> | IRQSEL4 <sup>(2)</sup> | IRQSEL3 <sup>(2)</sup> | IRQSEL2 <sup>(2)</sup> | IRQSEL1 <sup>(2)</sup> | IRQSEL0 <sup>(2)</sup> |

| bit 7 |                        |                        |                        |                        |                        |                        | bit 0                  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15 **FORCE:** Force DMA Transfer bit<sup>(1)</sup>

1 = Force a single DMA transfer (Manual mode)

0 = Automatic DMA transfer initiation by DMA request

bit 14-7 Unimplemented: Read as '0'

- bit 6-0 IRQSEL<6:0>: DMA Peripheral IRQ Number Select bits<sup>(2)</sup> 0000000-1111111 = DMAIRQ0-DMAIRQ127 selected to be Channel DMAREQ

- **Note 1:** The FORCE bit cannot be cleared by the user. The FORCE bit is cleared by hardware when the forced DMA transfer is complete.

2: Please see Table 8-1 for a complete listing of IRQ numbers for all interrupt sources.

## 11.0 I/O PORTS

Note: This data sheet summarizes the features of the dsPIC33FJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 10. "I/O Ports" (DS70193) in the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

All of the device pins (except VDD, VSS, MCLR and OSC1/CLKIN) are shared between the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

## 11.1 Parallel I/O (PIO) Ports

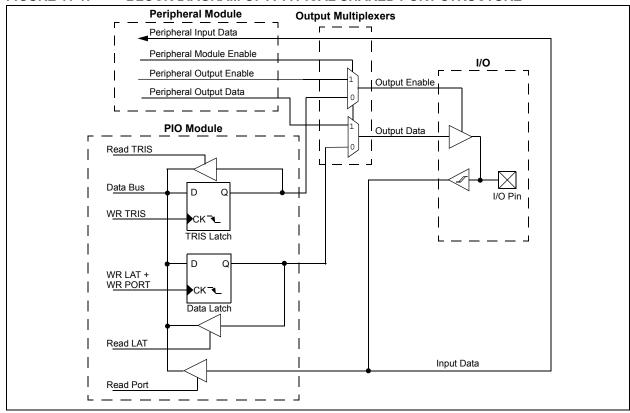

A parallel I/O port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected. When a peripheral is enabled and actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read, but the output driver for the parallel port bit will be disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin may be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx), read the latch. Writes to the latch, write the latch. Reads from the port (PORTx), read the port pins, while writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers and the port pins will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs. An example is the INT4 pin.

Note: The voltage on a digital input pin can be between -0.3V to 5.6V.

#### FIGURE 11-1: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

© 2009 Microchip Technology Inc.

| REGISTER      | 12-1: T1CO                    | N: TIMER1 C                     | ONTROL R        | EGISTER          |                  |                 |       |

|---------------|-------------------------------|---------------------------------|-----------------|------------------|------------------|-----------------|-------|

| R/W-0         | U-0                           | R/W-0                           | U-0             | U-0              | U-0              | U-0             | U-0   |

| TON           | _                             | TSIDL                           | _               | —                | _                | —               | _     |

| bit 15        |                               |                                 |                 |                  |                  |                 | bit 8 |

| U-0           | R/W-0                         | R/W-0                           | R/W-0           | U-0              | R/W-0            | R/W-0           | U-0   |

| _             | TGATE                         |                                 | S<1:0>          | _                | TSYNC            | TCS             | _     |

| bit 7         |                               |                                 | <b>-</b>        |                  |                  |                 | bit ( |

| Legend:       |                               |                                 |                 |                  |                  |                 |       |

| R = Readabl   | lo hit                        | W = Writable                    | bit             | II – Unimplo     | mented bit, read | d ac (0)        |       |

|               |                               |                                 |                 | -                |                  |                 |       |

| -n = Value at | POR                           | '1' = Bit is set                |                 | '0' = Bit is cle | eared            | x = Bit is unkn | own   |

| bit 15        | TON: Timer1                   | On bit                          |                 |                  |                  |                 |       |

|               | 1 = Starts 16                 |                                 |                 |                  |                  |                 |       |

|               | 0 = Stops 16                  |                                 |                 |                  |                  |                 |       |

| bit 14        | -                             | nted: Read as '                 |                 |                  |                  |                 |       |

| bit 13        | -                             | in Idle Mode bi                 |                 |                  |                  |                 |       |

|               |                               | nue module ope<br>module operat |                 |                  | dle mode         |                 |       |

| bit 12-7      |                               | nted: Read as '                 |                 |                  |                  |                 |       |

| bit 6         | TGATE: Time                   | er1 Gated Time                  | Accumulatio     | n Enable bit     |                  |                 |       |

|               | When T1CS                     | = 1:                            |                 |                  |                  |                 |       |

|               | This bit is ign               | nored.                          |                 |                  |                  |                 |       |

|               | When T1CS                     |                                 |                 |                  |                  |                 |       |

|               |                               | ne accumulatio                  |                 |                  |                  |                 |       |

|               |                               | ne accumulatio                  |                 |                  |                  |                 |       |

| bit 5-4       |                               | Timer1 Input                    | Clock Presca    | ale Select bits  |                  |                 |       |

|               | 11 = 1:256<br>10 = 1:64       |                                 |                 |                  |                  |                 |       |

|               | 01 = 1:8                      |                                 |                 |                  |                  |                 |       |

|               | 00 = 1:1                      |                                 |                 |                  |                  |                 |       |

| bit 3         | Unimplemer                    | nted: Read as '                 | 0'              |                  |                  |                 |       |

| bit 2         | TSYNC: Time                   | er1 External Cl                 | ock Input Syr   | hchronization S  | elect bit        |                 |       |

|               | When TCS =                    | : 1:                            |                 |                  |                  |                 |       |

|               |                               | nize external clo               |                 |                  |                  |                 |       |

|               | -                             | ynchronize exte                 | ernal clock inp | but              |                  |                 |       |

|               | When TCS =<br>This bit is ign |                                 |                 |                  |                  |                 |       |

| bit 1         | -                             | Clock Source                    | Select bit      |                  |                  |                 |       |

| -             |                               | clock from pin                  |                 | rising edge)     |                  |                 |       |

| hit 0         |                               |                                 | o'              |                  |                  |                 |       |

| bit 0         | Unimplemen                    | nted: Read as '                 | U               |                  |                  |                 |       |

## 14.1 Input Capture Registers

#### REGISTER 14-1: ICxCON: INPUT CAPTURE x CONTROL REGISTER

| U-0                  | U-0                                                                                                   | R/W-0                                                                                                                                                             | U-0                                                                                                                                   | U-0                                     | U-0             | U-0                    | U-0   |

|----------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----------------|------------------------|-------|

| —                    |                                                                                                       | ICSIDL                                                                                                                                                            |                                                                                                                                       |                                         |                 | _                      | —     |

| bit 15               |                                                                                                       |                                                                                                                                                                   |                                                                                                                                       |                                         |                 |                        | bit   |

|                      |                                                                                                       |                                                                                                                                                                   |                                                                                                                                       |                                         |                 |                        |       |

| R/W-0                | R/W-0                                                                                                 | R/W-0                                                                                                                                                             | R-0, HC                                                                                                                               | R-0, HC                                 | R/W-0           | R/W-0                  | R/W-0 |

| ICTMR <sup>(1)</sup> | ICI<                                                                                                  | <1:0>                                                                                                                                                             | ICOV                                                                                                                                  | ICBNE                                   |                 | ICM<2:0>               |       |

| bit 7                |                                                                                                       |                                                                                                                                                                   |                                                                                                                                       |                                         |                 |                        | bit   |

| Legend:              |                                                                                                       |                                                                                                                                                                   |                                                                                                                                       |                                         |                 |                        |       |

| R = Readable         | e bit                                                                                                 | W = Writable                                                                                                                                                      | bit                                                                                                                                   | U = Unimplen                            | nented bit, rea | d as '0'               |       |

| -n = Value at        | POR                                                                                                   | '1' = Bit is set                                                                                                                                                  | :                                                                                                                                     | '0' = Bit is cle                        | ared            | x = Bit is unkn        | own   |

|                      |                                                                                                       |                                                                                                                                                                   |                                                                                                                                       |                                         |                 |                        |       |

| bit 15-14            | Unimplemen                                                                                            | nted: Read as '                                                                                                                                                   | 0'                                                                                                                                    |                                         |                 |                        |       |

| bit 13               | ICSIDL: Inpu                                                                                          | t Capture Mod                                                                                                                                                     | ule Stop in Idle                                                                                                                      | e Control bit                           |                 |                        |       |

|                      |                                                                                                       | ture module wi                                                                                                                                                    |                                                                                                                                       |                                         |                 |                        |       |

|                      |                                                                                                       |                                                                                                                                                                   |                                                                                                                                       | operate in CPU                          | Idle mode       |                        |       |

| bit 12-8             | •                                                                                                     | nted: Read as                                                                                                                                                     |                                                                                                                                       |                                         |                 |                        |       |

| bit 7                |                                                                                                       | t Capture Time                                                                                                                                                    |                                                                                                                                       |                                         |                 |                        |       |

|                      |                                                                                                       | ntents are capt<br>ntents are capt                                                                                                                                | •                                                                                                                                     |                                         |                 |                        |       |

| bit 6-5              | ICI<1:0>: Se                                                                                          | lect Number of                                                                                                                                                    | Captures per                                                                                                                          | Interrupt bits                          |                 |                        |       |

|                      | 10 = Interrup<br>01 = Interrup                                                                        | t on every four<br>t on every third<br>t on every seco<br>t on every capt                                                                                         | capture even                                                                                                                          | t                                       |                 |                        |       |

| bit 4                | -                                                                                                     |                                                                                                                                                                   |                                                                                                                                       | ) bit (read-only)                       |                 |                        |       |

|                      | 1 = Input cap                                                                                         | ture overflow c<br>capture overflo                                                                                                                                | ccurred                                                                                                                               | , , , , , , , , , , , , , , , , , , , , |                 |                        |       |

| bit 3                | ICBNE: Input                                                                                          | t Capture Buffe                                                                                                                                                   | r Empty Statu                                                                                                                         | s bit (read-only                        | )               |                        |       |

|                      |                                                                                                       |                                                                                                                                                                   |                                                                                                                                       | ast one more c                          | apture value c  | an be read             |       |

|                      |                                                                                                       | ture buffer is e                                                                                                                                                  |                                                                                                                                       |                                         |                 |                        |       |

| bit 2-0              |                                                                                                       | put Capture M                                                                                                                                                     |                                                                                                                                       |                                         |                 |                        |       |

|                      | (Risin<br>110 = Unuse<br>101 = Captur<br>100 = Captur<br>011 = Captur<br>010 = Captur<br>001 = Captur | g edge detect of<br>d (module disa<br>re mode, every<br>re mode, every<br>re mode, every<br>re mode, every<br>re mode, every<br>re mode, every<br>:0> bits do not | only, all other of<br>bled)<br>16th rising edg<br>4th rising edge<br>rising edge<br>falling edge<br>edge (rising a<br>control interru | control bits are<br>lge<br>le           | not applicable  | eep or Idle mode<br>.) | 2     |

Note 1: Timer selections may vary. Refer to the device data sheet for details.

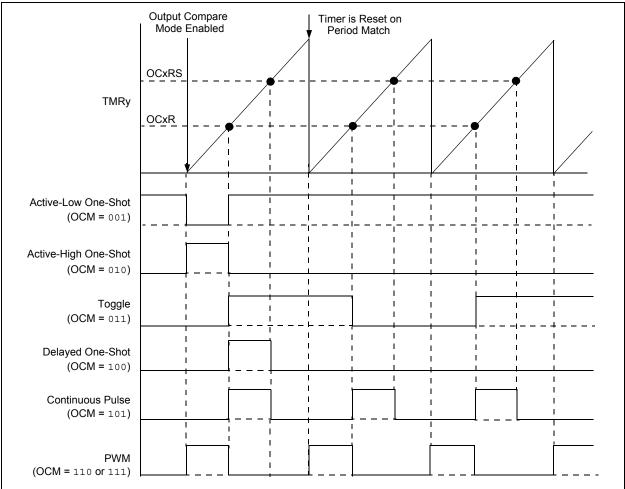

## 15.1 Output Compare Modes

Configure the Output Compare modes by setting the appropriate Output Compare Mode (OCM<2:0>) bits in the Output Compare Control (OCxCON<2:0>) register. Table 15-1 lists the different bit settings for the Output Compare modes. Figure 15-2 illustrates the output compare operation for various modes. The user

TABLE 15-1: OUTPUT COMPARE MODES

application must disable the associated timer when writing to the Output Compare Control registers to avoid malfunctions.

| Note: | See Section 13. "Output Compare"       |

|-------|----------------------------------------|

|       | (DS70209) in the "dsPIC33F Family Ref- |

|       | erence Manual" for OCxR and OCxRS      |

|       | register restrictions.                 |

| OCM<2:0> | Mode                         | OCx Pin Initial State                                                   | OCx Interrupt Generation         |

|----------|------------------------------|-------------------------------------------------------------------------|----------------------------------|

| 000      | Module Disabled              | Controlled by GPIO register                                             | —                                |

| 001      | Active-Low One-Shot          | 0                                                                       | OCx rising edge                  |

| 010      | Active-High One-Shot         | 1                                                                       | OCx falling edge                 |

| 011      | Toggle                       | Current output is maintained                                            | OCx rising and falling edge      |

| 100      | Delayed One-Shot             | 0                                                                       | OCx falling edge                 |

| 101      | Continuous Pulse             | 0                                                                       | OCx falling edge                 |

| 110      | PWM without Fault Protection | '0', if OCxR is zero '1', if OCxR is non-zero                           | No interrupt                     |

| 111      | PWM with Fault Protection    | <ul><li>'0', if OCxR is zero</li><li>'1', if OCxR is non-zero</li></ul> | OCFA falling edge for OC1 to OC4 |

#### FIGURE 15-2: OUTPUT COMPARE OPERATION

## **REGISTER 15-1:** OCxCON: OUTPUT COMPARE x CONTROL REGISTER (x = 1, 2)

| bit 15 |     |        |     |     |     |     | bit 8 |

|--------|-----|--------|-----|-----|-----|-----|-------|

| —      | —   | OCSIDL | —   | _   | —   | —   | —     |

| U-0    | U-0 | R/W-0  | U-0 | U-0 | U-0 | U-0 | U-0   |

| U-0   | U-0 | U-0 | R-0, HC | R/W-0  | R/W-0 | R/W-0    | R/W-0 |

|-------|-----|-----|---------|--------|-------|----------|-------|

| —     | —   | _   | OCFLT   | OCTSEL |       | OCM<2:0> |       |

| bit 7 |     |     |         |        |       |          | bit 0 |

| Legend:           | HC = Hardware Clearable bit |                           |                    |

|-------------------|-----------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared      | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                                                                                                                             |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 13    | OCSIDL: Stop Output Compare in Idle Mode Control bit                                                                                                                                   |

|           | <ul> <li>1 = Output Compare x halts in CPU Idle mode</li> <li>0 = Output Compare x continues to operate in CPU Idle mode</li> </ul>                                                    |

| bit 12-5  | Unimplemented: Read as '0'                                                                                                                                                             |

| bit 4     | OCFLT: PWM Fault Condition Status bit                                                                                                                                                  |

|           | <ul> <li>1 = PWM Fault condition has occurred (cleared in hardware only)</li> <li>0 = No PWM Fault condition has occurred (this bit is only used when OCM&lt;2:0&gt; = 111)</li> </ul> |

| bit 3     | OCTSEL: Output Compare Timer Select bit                                                                                                                                                |

|           | <ul> <li>1 = Timer3 is the clock source for Compare x</li> <li>0 = Timer2 is the clock source for Compare x</li> </ul>                                                                 |

| bit 2-0   | OCM<2:0>: Output Compare Mode Select bits                                                                                                                                              |

|           | 111 = PWM mode on OCx, Fault pin enabled<br>110 = PWM mode on OCx, Fault pin disabled                                                                                                  |

|           | 101 = Initialize OCx pin low, generate continuous output pulses on OCx pin                                                                                                             |

|           | 100 = Initialize OCx pin low, generate single output pulse on OCx pin                                                                                                                  |

|           | <ul> <li>011 = Compare event toggles OCx pin</li> <li>010 = Initialize OCx pin high, compare event forces OCx pin low</li> </ul>                                                       |

|           | 001 = Initialize OCx pin low, compare event forces OCx pin high                                                                                                                        |

|           | 000 = Output compare channel is disabled                                                                                                                                               |

|           |                                                                                                                                                                                        |

### REGISTER 16-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- - **Note 1:** The CKE bit is not used in the Framed SPI modes. The user should program this bit to '0' for the Framed SPI modes (FRMEN = 1).

- 2: Do not set both Primary and Secondary prescalers to a value of 1:1.

- 3: This bit must be cleared when FRMEN = 1.

| REGISTER                                    | 19-5: CiFIF                             | O: ECAN™ F                             | FO STATU        | S REGISTER                         |        |                 |       |

|---------------------------------------------|-----------------------------------------|----------------------------------------|-----------------|------------------------------------|--------|-----------------|-------|

| U-0                                         | U-0                                     | R-0                                    | R-0             | R-0                                | R-0    | R-0             | R-0   |

| _                                           | —                                       |                                        |                 | FBP                                | <5:0>  |                 |       |

| bit 15                                      |                                         |                                        |                 |                                    |        |                 | bit 8 |

| U-0                                         | U-0                                     | R-0                                    | R-0             | R-0                                | R-0    | R-0             | R-0   |

| _                                           | —                                       |                                        |                 | FNRI                               | 3<5:0> |                 |       |

| bit 7                                       | ·                                       |                                        |                 |                                    |        |                 | bit 0 |

|                                             |                                         |                                        |                 |                                    |        |                 |       |

| Legend:                                     |                                         |                                        |                 |                                    |        |                 |       |

| R = Readabl                                 | le bit                                  | W = Writable bit                       |                 | U = Unimplemented bit, read as '0' |        |                 |       |

| -n = Value at                               | t POR                                   | '1' = Bit is set                       |                 | '0' = Bit is clea                  | ared   | x = Bit is unkr | nown  |

| bit 15-14<br>bit 13-8<br>bit 7-6<br>bit 5-0 | FBP<5:0>: F<br>011111 = R<br>011110 = R | B30 buffer<br>RB1 buffer               | er Pointer bits |                                    |        |                 |       |

|                                             | 011111 = RI<br>011110 = RI              | B31 buffer<br>B30 buffer<br>RB1 buffer |                 |                                    |        |                 |       |

| REGISTER      | 21-2: ADxC0                   | ON2: ADCx                                   | CONTROL RE                             | EGISTER 2        | (where x = 1      | or 2)            |            |

|---------------|-------------------------------|---------------------------------------------|----------------------------------------|------------------|-------------------|------------------|------------|

| R/W-0         | R/W-0                         | R/W-0                                       | U-0                                    | U-0              | R/W-0             | R/W-0            | R/W-0      |

|               | VCFG<2:0>                     |                                             |                                        |                  | CSCNA             | CHPS             | <1:0>      |

| bit 15        |                               |                                             |                                        |                  |                   |                  | bit        |

| R-0           | U-0                           | R/W-0                                       | R/W-0                                  | R/W-0            | R/W-0             | R/W-0            | R/W-0      |

| BUFS          |                               |                                             | SMP                                    | <3:0>            |                   | BUFM             | ALTS       |

| bit 7         |                               |                                             |                                        |                  |                   |                  | bit        |

| Legend:       |                               |                                             |                                        |                  |                   |                  |            |

| R = Readable  | e bit                         | W = Writable                                | e bit                                  | U = Unimple      | mented bit, read  | d as '0'         |            |

| -n = Value at | POR                           | '1' = Bit is se                             | t                                      | '0' = Bit is cle | eared             | x = Bit is unkn  | own        |

| bit 15-13     | VCEG<2.0>                     | Converter Vol                               | tage Reference                         | Configuration    | hite              |                  |            |

| 511 15-15     |                               | VREF+                                       | VREF-                                  |                  |                   |                  |            |

|               | 000                           | AVDD                                        | Avss                                   | =                |                   |                  |            |

|               |                               | rnal VREF+                                  | Avss                                   | -                |                   |                  |            |

|               | 010                           | AVDD                                        | External VREF-                         | -                |                   |                  |            |

|               | 011 Exte                      | rnal VREF+                                  | External VREF-                         |                  |                   |                  |            |

|               | 1xx                           | Avdd                                        | Avss                                   |                  |                   |                  |            |

| bit 12-11     | Unimplemen                    | ted: Read as                                | ʻ0'                                    |                  |                   |                  |            |

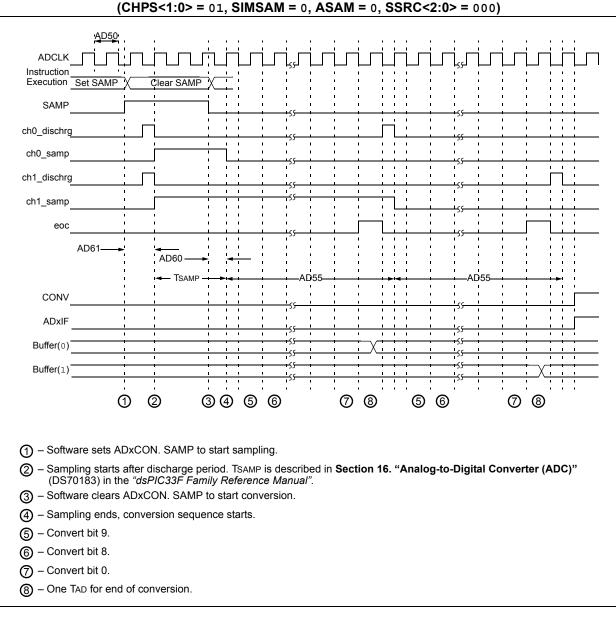

| bit 10        | CSCNA: Scar                   | n Input Select                              | ions for CH0+ d                        | uring Sample     | A bit             |                  |            |

|               | 1 = Scan inp                  | uts                                         |                                        | <b>C</b> .       |                   |                  |            |

|               | 0 = Do not so                 | can inputs                                  |                                        |                  |                   |                  |            |

| bit 9-8       | CHPS<1:0>:                    | Selects Chan                                | nels Utilized bits                     | 3                |                   |                  |            |

|               |                               |                                             | 1:0> is: U-0, Ur                       | nimplementee     | d, Read as '0'    |                  |            |

|               |                               |                                             | CH2 and CH3                            |                  |                   |                  |            |

|               | 01 = Convert                  |                                             | -11                                    |                  |                   |                  |            |

| bit 7         |                               |                                             | (only valid whe                        | n BIJEM = 1)     |                   |                  |            |

|               | 1 = ADC is c                  | urrently filling                            | second half of b                       | ouffer, user sh  | ould access dat   |                  |            |

|               |                               | , ,                                         |                                        | er, user should  | l access data in  | second half      |            |

| bit 6         | Unimplemen                    | ted: Read as                                | '0'                                    |                  |                   |                  |            |

| bit 5-2       | SMPI<3:0>: S<br>operations pe |                                             | ent Rate for DN                        | IA Addresses     | bits or number    | of sample/conv   | ersion     |

|               | 1111 = Increi                 | ments the D                                 | MA address o                           | or generates     | interrupt after   | completion of    | every 16t  |

|               | 1110 = Increi                 |                                             | MA address c                           | or generates     | interrupt after   | completion of    | every 15t  |

|               | samp                          | le/conversion                               | operation                              |                  |                   |                  |            |

|               | •                             |                                             |                                        |                  |                   |                  |            |

|               |                               |                                             |                                        | or generates     | interrupt after   | completion o     | f every 2r |

|               | 0000 = Increi                 | e/conversion<br>ments the l<br>e/conversion | DMA address                            | or generate      | es interrupt a    | fter completio   | n of eve   |

| bit 1         | BUFM: Buffer                  | Fill Mode Se                                | lect bit                               |                  |                   |                  |            |

|               |                               | -                                           | buffer on first ir<br>fer from the beg |                  | econd half of the | e buffer on next | interrupt  |

| bit 0         | -                             | -                                           | ple Mode Selec                         | -                |                   |                  |            |

|               |                               | -                                           | -                                      |                  | nple and Sample   | e B on next san  | nple       |

|               |                               |                                             | nput selects for                       |                  | ,                 |                  |            |

| REGISTER                       | 21-6: ADxC                                                                                                                | HS0: ADCx IN                                                                                                                                                         | IPUT CHAN                                                      | NEL 0 SELE       | CT REGISTI      | ER             |       |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------|-----------------|----------------|-------|

| R/W-0                          | U-0                                                                                                                       | U-0                                                                                                                                                                  | R/W-0                                                          | R/W-0            | R/W-0           | R/W-0          | R/W-0 |

| CH0NB                          |                                                                                                                           | —                                                                                                                                                                    |                                                                |                  | CH0SB<4:03      | >              |       |

| bit 15                         |                                                                                                                           |                                                                                                                                                                      | •                                                              |                  |                 |                | bit 8 |

| R/W-0                          | U-0                                                                                                                       | U-0                                                                                                                                                                  | R/W-0                                                          | R/W-0            | R/W-0           | R/W-0          | R/W-0 |

| CH0NA                          |                                                                                                                           | —                                                                                                                                                                    |                                                                |                  | CH0SA<4:0       | >              |       |

| bit 7                          |                                                                                                                           |                                                                                                                                                                      |                                                                |                  |                 |                | bit ( |

| Legend:                        |                                                                                                                           |                                                                                                                                                                      |                                                                |                  |                 |                |       |

| R = Readabl                    | e bit                                                                                                                     | W = Writable b                                                                                                                                                       | oit                                                            | U = Unimple      | mented bit, rea | ad as '0'      |       |

| -n = Value at                  | POR                                                                                                                       | '1' = Bit is set                                                                                                                                                     |                                                                | '0' = Bit is cle | eared           | x = Bit is unk | nown  |

| bit 14-13<br>bit 12-8<br>bit 7 | CH0SB<4:0><br>Same definition<br>CH0NA: Cha<br>1 = Channel (                                                              | <ul> <li>ited: Read as '0</li> <li>: Channel 0 Poi<br/>on as bit&lt;4:0&gt;.</li> <li>nnel 0 Negative</li> <li>0 negative input</li> <li>0 negative input</li> </ul> | sitive Input S<br>Input Select<br>t is AN1                     |                  |                 |                |       |

| bit 6-5                        | Unimplemen                                                                                                                | ted: Read as 'c                                                                                                                                                      | )'                                                             |                  |                 |                |       |

| bit 4-0                        | 11111 = Cha<br>11110 = Cha<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>• | Channel 0 Positive i<br>innel 0 positive i                                   | input is AN31<br>input is AN30<br>input is AN2<br>input is AN1 |                  | e A bits        |                |       |

#### **Note:** ADC2 can only select AN0 through AN15 as positive input.

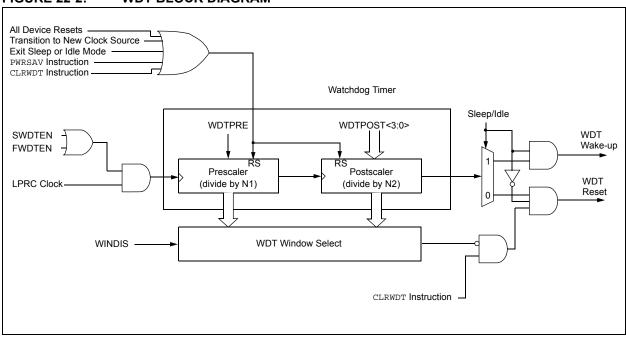

## 22.4 Watchdog Timer (WDT)

For dsPIC33FJXXXGPX06/X08/X10 devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler and then can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a nominal WDT time-out period (TWDT) of 1 ms in 5-bit mode, or 4 ms in 7-bit mode.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>) which allow the selection of a total of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- · On any device Reset