Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Obsolete                                                                          |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                   |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 32x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp310t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 4-2: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJXXXGPX10 DEVICES

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|---------|---------|---------|---------|---------|---------|---------|---------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | CN7IE   | CN6IE   | CN5IE   | CN4IE   | CN3IE   | CN2IE   | CN1IE   | CN0IE   | 0000          |

| CNEN2       | 0062        | _       |         | _       | _       | _       | _       | _      | —      | CN23IE  | CN22IE  | CN21IE  | CN20IE  | CN19IE  | CN18IE  | CN17IE  | CN16IE  | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | CN7PUE  | CN6PUE  | CN5PUE  | CN4PUE  | CN3PUE  | CN2PUE  | CN1PUE  | CN0PUE  | 0000          |

| CNPU2       | 006A        |         | _       | -       | _       | —       | _       | _      | _      | CN23PUE | CN22PUE | CN21PUE | CN20PUE | CN19PUE | CN18PUE | CN17PUE | CN16PUE | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-3: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJXXXGPX08 DEVICES

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3         | Bit 2   | Bit 1   | Bit 0         | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|---------|---------|---------------|---------|---------|---------------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | CN7IE  | CN6IE  | CN5IE   | CN4IE   | CN3IE         | CN2IE   | CN1IE   | CN0IE         | 0000          |

| CNEN2       | 0062        | —       |         |         | _       |         | —       |        |        | _      | —      | CN21IE  | CN20IE  | CN19IE        | CN18IE  | CN17IE  | CN16IE        | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | CN7PUE | CN6PUE | CN5PUE  | CN4PUE  | <b>CN3PUE</b> | CN2PUE  | CN1PUE  | <b>CN0PUE</b> | 0000          |

| CNPU2       | 006A        | _       |         |         |         |         | —       |        |        | _      | —      | CN21PUE | CN20PUE | CN19PUE       | CN18PUE | CN17PUE | CN16PUE       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-4: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJXXXGPX06 DEVICES

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3  | Bit 2   | Bit 1   | Bit 0         | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|---------|---------|--------|---------|---------|---------------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | CN7IE  | CN6IE  | CN5IE   | CN4IE   | CN3IE  | CN2IE   | CN1IE   | CN0IE         | 0000          |

| CNEN2       | 0062        | _       | _       | _       | _       | _       | _       | _      | _      | _      | _      | CN21IE  | CN20IE  | -      | CN18IE  | CN17IE  | CN16IE        | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | CN7PUE | CN6PUE | CN5PUE  | CN4PUE  | CN3PUE | CN2PUE  | CN1PUE  | <b>CN0PUE</b> | 0000          |

| CNPU2       | 006A        | —       | _       | _       | _       | _       | —       | _      | _      | -      |        | CN21PUE | CN20PUE | _      | CN18PUE | CN17PUE | CN16PUE       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-17: DMA REGISTER MAP

|           |      | -      |        | -      | -      | -      | -      | -     |       |           |       | -     |        |           |       |       |       | All    |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-----------|-------|-------|--------|-----------|-------|-------|-------|--------|

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7     | Bit 6 | Bit 5 | Bit 4  | Bit 3     | Bit 2 | Bit 1 | Bit 0 | Resets |

| DMA0CON   | 0380 | CHEN   | SIZE   | DIR    | HALF   | NULLW  |        | _     | _     | _         |       | AMOD  | E<1:0> | —         | _     | MODE  | <1:0> | 0000   |

| DMA0REQ   | 0382 | FORCE  | _      | —      |        | —      | _      | —     |       | —         |       |       | I      | RQSEL<6:0 | >     |       |       | 0000   |

| DMA0STA   | 0384 |        |        |        |        |        |        |       | S     | STA<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA0STB   | 0386 |        |        |        |        |        |        |       | S     | STB<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA0PAD   | 0388 |        |        |        | -      |        |        |       | P     | AD<15:0>  |       |       |        |           |       |       |       | 0000   |

| DMA0CNT   | 038A | —      | —      | _      | —      | —      | _      |       |       |           |       | CN    | <9:0>  |           |       |       |       | 0000   |

| DMA1CON   | 038C | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | —     | —     | —         | —     | AMOD  | E<1:0> | —         | —     | MODE  | <1:0> | 0000   |

| DMA1REQ   | 038E | FORCE  | —      | —      | —      | —      | _      | —     | —     | —         |       |       | I      | RQSEL<6:0 | >     |       |       | 0000   |

| DMA1STA   | 0390 |        |        |        |        |        |        |       | S     | STA<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA1STB   | 0392 |        |        |        |        |        |        |       | S     | TB<15:0>  |       |       |        |           |       |       |       | 0000   |

| DMA1PAD   | 0394 |        |        |        |        |        |        |       | P     | AD<15:0>  |       |       |        |           |       |       |       | 0000   |

| DMA1CNT   | 0396 | _      | _      | _      | —      | _      |        |       |       |           |       | CN    | <9:0>  |           |       |       |       | 0000   |

| DMA2CON   | 0398 | CHEN   | SIZE   | DIR    | HALF   | NULLW  |        | —     | —     | —         | _     | AMOD  | E<1:0> | -         | —     | MODE  | <1:0> | 0000   |

| DMA2REQ   | 039A | FORCE  | -      | _      | _      | _      | _      | _     | _     | _         |       |       | I      | RQSEL<6:0 | >     |       |       | 0000   |

| DMA2STA   | 039C |        |        |        |        |        |        |       | S     | STA<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA2STB   | 039E |        |        |        |        |        |        |       | S     | TB<15:0>  |       |       |        |           |       |       |       | 0000   |

| DMA2PAD   | 03A0 |        |        |        |        |        |        |       | P     | AD<15:0>  |       |       |        |           |       |       |       | 0000   |

| DMA2CNT   | 03A2 | _      | _      | _      | _      | —      | _      |       |       |           |       | CN    | <9:0>  |           |       |       |       | 0000   |

| DMA3CON   | 03A4 | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _     | —         | —     | AMOD  | E<1:0> | _         | _     | MODE  | <1:0> | 0000   |

| DMA3REQ   | 03A6 | FORCE  | _      | _      | _      | —      | _      | _     | _     | —         |       |       | I      | RQSEL<6:0 | >     |       |       | 0000   |

| DMA3STA   | 03A8 |        |        |        |        |        |        |       | S     | STA<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA3STB   | 03AA |        |        |        |        |        |        |       | S     | TB<15:0>  |       |       |        |           |       |       |       | 0000   |

| DMA3PAD   | 03AC |        |        |        |        |        |        |       | P     | AD<15:0>  |       |       |        |           |       |       |       | 0000   |

| DMA3CNT   | 03AE | _      | _      | _      | _      | —      | _      |       |       |           |       | CN    | <9:0>  |           |       |       |       | 0000   |

| DMA4CON   | 03B0 | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _     | _         | _     | AMOD  | E<1:0> | _         | _     | MODE  | <1:0> | 0000   |

| DMA4REQ   | 03B2 | FORCE  | _      | _      | _      | _      | _      | _     | _     | _         |       |       | I      | RQSEL<6:0 | >     |       |       | 0000   |

| DMA4STA   | 03B4 |        |        |        | •      |        |        | •     | S     | TA<15:0>  | •     |       |        |           |       |       |       | 0000   |

| DMA4STB   | 03B6 |        |        |        |        |        |        |       | S     | TB<15:0>  |       |       |        |           |       |       |       | 0000   |

| DMA4PAD   | 03B8 |        |        |        |        |        |        |       | P     | AD<15:0>  |       |       |        |           |       |       |       | 0000   |

| DMA4CNT   | 03BA | _      | _      | _      | —      | —      | —      |       |       |           |       | CN    | <9:0>  |           |       |       |       | 0000   |

| DMA5CON   | 03BC | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | —     | —         | _     | AMOD  | E<1:0> | —         | —     | MODE  | <1:0> | 0000   |

| DMA5REQ   | 03BE | FORCE  | _      | —      | —      | —      | —      | _     | _     | _         |       | •     | I      | RQSEL<6:0 | >     | •     |       | 0000   |

| DMA5STA   | 03C0 |        |        |        |        |        |        |       | S     | TA<15:0>  | •     |       |        |           |       |       |       | 0000   |

| DMA5STB   | 03C2 |        |        |        |        |        |        |       | S     | TB<15:0>  |       |       |        |           |       |       |       | 0000   |

| DMA5PAD   | 03C4 |        |        |        |        |        |        |       | P     | AD<15:0>  |       |       |        |           |       |       |       | 0000   |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# DS70286C-page 50

can operate on any W register pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can only be configured to operate in one direction as there are certain restrictions on the buffer start address (for incrementing buffers), or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers which have a power-of-2 length. As these buffers satisfy the start and end address criteria, they may operate in a bidirectional mode (i.e., address boundary checks will be performed on both the lower and upper address boundaries).

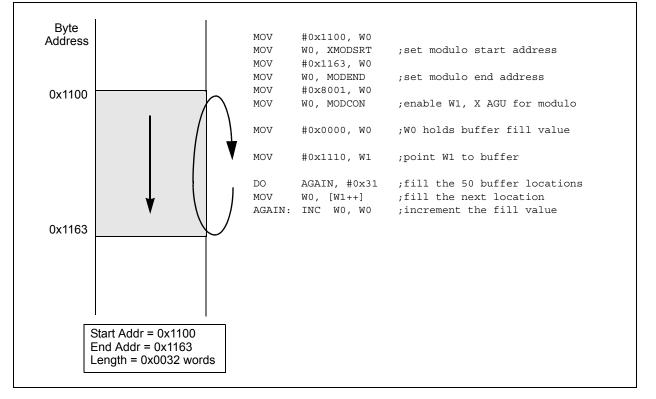

#### 4.4.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

Note: Y space Modulo Addressing EA calculations assume word sized data (LSb of every EA is always clear).

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

#### 4.4.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select which registers will operate with Modulo Addressing. If XWM = 15, X RAGU and X WAGU Modulo Addressing is disabled. Similarly, if YWM = 15, Y AGU Modulo Addressing is disabled.

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X data space when XWM is set to any value other than '15' and the XMODEN bit is set at MODCON<15>.

The Y Address Space Pointer W register (YWM) to which Modulo Addressing is to be applied is stored in MODCON<7:4>. Modulo Addressing is enabled for Y data space when YWM is set to any value other than '15' and the YMODEN bit is set at MODCON<14>.

#### FIGURE 4-7: MODULO ADDRESSING OPERATION EXAMPLE

| Legend:<br>R = Readable bit<br>-n = Value at POI<br>bit 15 V<br>bit 14 V<br>bit 14 1<br>0<br>bit 13 V<br>1<br>0 | R<br>VR: Write Co<br>= Initiates a<br>cleared b<br>= Program<br>VREN: Write<br>= Enable Fl<br>= Inhibit Fla                                    | a Flash memory<br>y hardware ond<br>or erase operation                                                                                                       | y program or<br>ce operation<br>tion is compl                    | ʻ0' = Bit is clea<br>r erase operatio                                | nented bit, reac<br>ared<br>n. The operatio          | x = Bit is unkr                                      |                             |

|-----------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|----------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------|-----------------------------|

| U-0<br>                                                                                                         | ERASE<br>R<br>WR: Write Co<br>= Initiates a<br>cleared b<br>= Program<br>WREN: Write<br>= Enable Fl<br>= Inhibit Fla                           | —<br>SO = Settable<br>W = Writable t<br>'1' = Bit is set<br>ntrol bit<br>a Flash memory<br>y hardware ond<br>or erase operat<br>Enable bit<br>lash program/e | only bit<br>bit<br>y program or<br>ce operation<br>tion is compl | U = Unimplen<br>'0' = Bit is clea<br>r erase operatio<br>is complete | NVMOF<br>nented bit, read<br>ared<br>n. The operatio | 9<3:0> <sup>(2)</sup><br>I as '0'<br>x = Bit is unkr | R/W-0 <sup>(1)</sup><br>bit |

|                                                                                                                 | ERASE<br>R<br>WR: Write Co<br>= Initiates a<br>cleared b<br>= Program<br>WREN: Write<br>= Enable Fl<br>= Inhibit Fla                           | —<br>SO = Settable<br>W = Writable t<br>'1' = Bit is set<br>ntrol bit<br>a Flash memory<br>y hardware ond<br>or erase operat<br>Enable bit<br>lash program/e | only bit<br>bit<br>y program or<br>ce operation<br>tion is compl | U = Unimplen<br>'0' = Bit is clea<br>r erase operatio<br>is complete | NVMOF<br>nented bit, read<br>ared<br>n. The operatio | 9<3:0> <sup>(2)</sup><br>I as '0'<br>x = Bit is unkr | bit                         |

|                                                                                                                 | ERASE<br>R<br>WR: Write Co<br>= Initiates a<br>cleared b<br>= Program<br>WREN: Write<br>= Enable Fl<br>= Inhibit Fla                           | —<br>SO = Settable<br>W = Writable t<br>'1' = Bit is set<br>ntrol bit<br>a Flash memory<br>y hardware ond<br>or erase operat<br>Enable bit<br>lash program/e | only bit<br>bit<br>y program or<br>ce operation<br>tion is compl | U = Unimplen<br>'0' = Bit is clea<br>r erase operatio<br>is complete | NVMOF<br>nented bit, read<br>ared<br>n. The operatio | 9<3:0> <sup>(2)</sup><br>I as '0'<br>x = Bit is unkr | bit                         |

| R = Readable bit<br>-n = Value at POI<br>bit 15 V<br>bit 14 V<br>bit 14 1<br>0<br>bit 13 V<br>1                 | t<br>R<br>VR: Write Co<br>= Initiates a<br>cleared b<br>= Program<br>VREN: Write<br>= Enable Fl<br>= Inhibit Fla                               | W = Writable k<br>'1' = Bit is set<br>ontrol bit<br>a Flash memory<br>y hardware ond<br>or erase operat<br>Enable bit<br>lash program/e                      | y program or<br>ce operation<br>tion is compl                    | '0' = Bit is clea<br>r erase operatio<br>is complete                 | nented bit, reac<br>ared<br>n. The operatio          | l as '0'<br>x = Bit is unkr                          | nown                        |

| Legend:<br>R = Readable bit<br>-n = Value at POI<br>bit 15 V<br>bit 14 V<br>bit 14 1<br>0<br>bit 13 V<br>1<br>0 | R<br>VR: Write Co<br>= Initiates a<br>cleared b<br>= Program<br>VREN: Write<br>= Enable Fl<br>= Inhibit Fla                                    | W = Writable k<br>'1' = Bit is set<br>ontrol bit<br>a Flash memory<br>y hardware ond<br>or erase operat<br>Enable bit<br>lash program/e                      | y program or<br>ce operation<br>tion is compl                    | '0' = Bit is clea<br>r erase operatio<br>is complete                 | ared<br>n. The operatio                              | x = Bit is unkr                                      | nown                        |

| R = Readable bit<br>-n = Value at POI<br>bit 15 V<br>bit 14 V<br>bit 14 1<br>0<br>bit 13 V<br>1                 | R<br>VR: Write Co<br>= Initiates a<br>cleared b<br>= Program<br>VREN: Write<br>= Enable Fl<br>= Inhibit Fla                                    | W = Writable k<br>'1' = Bit is set<br>ontrol bit<br>a Flash memory<br>y hardware ond<br>or erase operat<br>Enable bit<br>lash program/e                      | y program or<br>ce operation<br>tion is compl                    | '0' = Bit is clea<br>r erase operatio<br>is complete                 | ared<br>n. The operatio                              | x = Bit is unkr                                      |                             |

| -n = Value at POI<br>bit 15 V<br>bit 14 V<br>bit 14 V<br>bit 13 V<br>1                                          | R<br>VR: Write Co<br>= Initiates a<br>cleared b<br>= Program<br>VREN: Write<br>= Enable Fl<br>= Inhibit Fla                                    | '1' = Bit is set<br>introl bit<br>a Flash memory<br>y hardware ond<br>or erase operat<br>Enable bit<br>lash program/e                                        | y program or<br>ce operation<br>tion is compl                    | '0' = Bit is clea<br>r erase operatio<br>is complete                 | ared<br>n. The operatio                              | x = Bit is unkr                                      |                             |

| 1<br>bit 14<br>bit 13<br>0<br>0                                                                                 | <ul> <li>VR: Write Co</li> <li>Initiates a cleared b</li> <li>Program</li> <li>VREN: Write</li> <li>Enable Fl</li> <li>Inhibit Flat</li> </ul> | ntrol bit<br>a Flash memory<br>y hardware ond<br>or erase operat<br>Enable bit<br>lash program/e                                                             | ce operation<br>tion is compl                                    | r erase operatio<br>is complete                                      | n. The operatio                                      |                                                      |                             |

| 1<br>bit 14 <b>V</b><br>1<br>0<br>bit 13 <b>V</b><br>1                                                          | <ul> <li>Initiates a<br/>cleared b</li> <li>Program</li> <li>VREN: Write</li> <li>Enable Fl</li> <li>Inhibit Fla</li> </ul>                    | a Flash memory<br>y hardware ond<br>or erase operat<br>Enable bit<br>lash program/e                                                                          | ce operation<br>tion is compl                                    | is complete                                                          |                                                      | on is self-timed                                     | and the bit i               |

| 1<br>bit 14<br>bit 13<br>0<br>0                                                                                 | <ul> <li>Initiates a<br/>cleared b</li> <li>Program</li> <li>VREN: Write</li> <li>Enable Fl</li> <li>Inhibit Fla</li> </ul>                    | a Flash memory<br>y hardware ond<br>or erase operat<br>Enable bit<br>lash program/e                                                                          | ce operation<br>tion is compl                                    | is complete                                                          |                                                      | on is self-timed                                     | and the bit i               |

| 0<br>bit 14 V<br>1<br>0<br>bit 13 V<br>1                                                                        | cleared b<br>= Program<br><b>VREN:</b> Write<br>= Enable Fl<br>= Inhibit Fla                                                                   | y hardware ond<br>or erase opera<br>Enable bit<br>lash program/e                                                                                             | ce operation<br>tion is compl                                    | is complete                                                          |                                                      | on is self-timed                                     | and the bit                 |

| bit 14 V<br>1<br>0<br>bit 13 V<br>1<br>0                                                                        | <ul> <li>Program</li> <li>VREN: Write</li> <li>Enable Flate</li> <li>Inhibit Flate</li> </ul>                                                  | or erase operation<br>Enable bit<br>lash program/e                                                                                                           | tion is compl                                                    |                                                                      |                                                      |                                                      |                             |

| bit 14 V<br>1<br>0<br>bit 13 V<br>1<br>0                                                                        | <b>VREN:</b> Write<br>= Enable Fl<br>= Inhibit Fla                                                                                             | Enable bit<br>lash program/e                                                                                                                                 |                                                                  |                                                                      |                                                      |                                                      |                             |

| 1<br>0<br>bit 13 V<br>1<br>0                                                                                    | = Enable Fl<br>= Inhibit Fla                                                                                                                   | lash program/e                                                                                                                                               | rase operatio                                                    |                                                                      |                                                      |                                                      |                             |

| 0<br>bit 13 V<br>1<br>0                                                                                         | ) = Inhibit Fla                                                                                                                                |                                                                                                                                                              |                                                                  | ons                                                                  |                                                      |                                                      |                             |

| bit 13 V<br>1                                                                                                   |                                                                                                                                                |                                                                                                                                                              |                                                                  |                                                                      |                                                      |                                                      |                             |

| 0                                                                                                               |                                                                                                                                                | e Sequence Er                                                                                                                                                | ror Flag bit                                                     |                                                                      |                                                      |                                                      |                             |

|                                                                                                                 | . = An improj                                                                                                                                  | per program or                                                                                                                                               | erase seque                                                      | ence attempt or                                                      | termination has                                      | s occurred (bit i                                    | s set                       |

|                                                                                                                 |                                                                                                                                                | cally on any set                                                                                                                                             |                                                                  |                                                                      |                                                      |                                                      |                             |

| hit 10 7                                                                                                        |                                                                                                                                                | -                                                                                                                                                            |                                                                  | pleted normally                                                      |                                                      |                                                      |                             |

|                                                                                                                 | -                                                                                                                                              | ted: Read as 'o                                                                                                                                              |                                                                  |                                                                      |                                                      |                                                      |                             |

|                                                                                                                 |                                                                                                                                                | e/Program Ena                                                                                                                                                |                                                                  |                                                                      | 0                                                    |                                                      |                             |

|                                                                                                                 |                                                                                                                                                |                                                                                                                                                              |                                                                  | d by NVMOP<3<br>ified by NVMOP                                       |                                                      |                                                      |                             |

|                                                                                                                 |                                                                                                                                                | ted: Read as '0                                                                                                                                              | -                                                                |                                                                      |                                                      |                                                      |                             |

|                                                                                                                 | •                                                                                                                                              | NVM Operati                                                                                                                                                  |                                                                  | . <sub>s</sub> (2)                                                   |                                                      |                                                      |                             |

|                                                                                                                 | f ERASE = 1:                                                                                                                                   |                                                                                                                                                              |                                                                  | .0                                                                   |                                                      |                                                      |                             |

|                                                                                                                 |                                                                                                                                                | <u>.</u><br>ory bulk erase c                                                                                                                                 | peration                                                         |                                                                      |                                                      |                                                      |                             |

|                                                                                                                 | 110 <b>= Reser</b>                                                                                                                             |                                                                                                                                                              |                                                                  |                                                                      |                                                      |                                                      |                             |

|                                                                                                                 |                                                                                                                                                | General Segm                                                                                                                                                 |                                                                  |                                                                      |                                                      |                                                      |                             |

|                                                                                                                 | .100 = Erase<br>.011 = Reser                                                                                                                   | Secure Segme                                                                                                                                                 | ent                                                              |                                                                      |                                                      |                                                      |                             |

|                                                                                                                 | 011 - Reser<br>011 - No op                                                                                                                     |                                                                                                                                                              |                                                                  |                                                                      |                                                      |                                                      |                             |

|                                                                                                                 |                                                                                                                                                | bry page erase                                                                                                                                               | operation                                                        |                                                                      |                                                      |                                                      |                             |

|                                                                                                                 | 0001 <b>= No op</b>                                                                                                                            |                                                                                                                                                              |                                                                  |                                                                      |                                                      |                                                      |                             |

| 0                                                                                                               | 0000 <b>= Erase</b>                                                                                                                            | a single Config                                                                                                                                              | guration regi                                                    | ster byte                                                            |                                                      |                                                      |                             |

|                                                                                                                 | f ERASE = 0:                                                                                                                                   |                                                                                                                                                              |                                                                  |                                                                      |                                                      |                                                      |                             |

|                                                                                                                 | .111 = No op                                                                                                                                   |                                                                                                                                                              |                                                                  |                                                                      |                                                      |                                                      |                             |

|                                                                                                                 | .110 = Reser<br>.101 = No op                                                                                                                   |                                                                                                                                                              |                                                                  |                                                                      |                                                      |                                                      |                             |

|                                                                                                                 | 101 <b>– No op</b>                                                                                                                             |                                                                                                                                                              |                                                                  |                                                                      |                                                      |                                                      |                             |

|                                                                                                                 | .011 = Reser                                                                                                                                   |                                                                                                                                                              |                                                                  |                                                                      |                                                      |                                                      |                             |

|                                                                                                                 |                                                                                                                                                | ory word progra                                                                                                                                              | m operation                                                      |                                                                      |                                                      |                                                      |                             |

|                                                                                                                 | 010 = No op                                                                                                                                    |                                                                                                                                                              | oporation                                                        |                                                                      |                                                      |                                                      |                             |

|                                                                                                                 |                                                                                                                                                | ory row progran<br>am a single Co                                                                                                                            |                                                                  | egister byte                                                         |                                                      |                                                      |                             |

2: All other combinations of NVMOP<3:0> are unimplemented.

#### 5.4.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of program Flash memory at a time. To do this, it is necessary to erase the 8-row erase page that contains the desired row. The general process is:

- 1. Read eight rows of program memory (512 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase the block (see Example 5-1):

- a) Set the NVMOP bits (NVMCON<3:0>) to '0010' to configure for block erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the page to be erased into the TBLPAG and W registers.

- c) Write 55h to NVMKEY.

- d) Write AAh to NVMKEY.

- e) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 64 instructions from data RAM into the program memory buffers (see Example 5-2).

- 5. Write the program block to Flash memory:

- a) Set the NVMOP bits to '0001' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write #0x55 to NVMKEY.

- c) Write #0xAA to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

- Repeat steps 4 and 5, using the next available 64 instructions from the block in data RAM by incrementing the value in TBLPAG, until all 512 instructions are written back to Flash memory.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as shown in Example 5-3.

#### EXAMPLE 5-1: ERASING A PROGRAM MEMORY PAGE

| ; Set up NVMCON for block erase operation |                                         |

|-------------------------------------------|-----------------------------------------|

| MOV #0x4042, W0                           | ;                                       |

| MOV W0, NVMCON                            | ; Initialize NVMCON                     |

| ; Init pointer to row to be ERASED        |                                         |

| MOV #tblpage(PROG_ADDR), W0               | ;                                       |

| MOV W0, TBLPAG                            | ; Initialize PM Page Boundary SFR       |

| MOV #tbloffset(PROG_ADDR), W0             | ; Initialize in-page EA[15:0] pointer   |

| TBLWTL W0, [W0]                           | ; Set base address of erase block       |

| DISI #5                                   | ; Block all interrupts with priority <7 |

|                                           | ; for next 5 instructions               |

| MOV #0x55, W0                             |                                         |

| MOV W0, NVMKEY                            | ; Write the 55 key                      |

| MOV #0xAA, W1                             | ;                                       |

| MOV W1, NVMKEY                            | ; Write the AA key                      |

| BSET NVMCON, #WR                          | ; Start the erase sequence              |

| NOP                                       | ; Insert two NOPs after the erase       |

| NOP                                       | ; command is asserted                   |

|                                           |                                         |

| REGISTER      | 7-5: IFS0:    | INTERRUPT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | FLAG STAT         | US REGISTE       | R 0              |                 |        |

|---------------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------------|------------------|-----------------|--------|

| U-0           | R/W-0         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0             | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| —             | DMA1IF        | AD1IF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | U1TXIF            | U1RXIF           | SPI1IF           | SPI1EIF         | T3IF   |

| bit 15        |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |                  |                  |                 | bit 8  |

| R/W-0         | R/W-0         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | R/W-0             | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| T2IF          | OC2IF         | IC2IF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DMA01IF           | T1IF             | OC1IF            | IC1IF           | INTOIF |

| bit 7         | 002li         | 10211                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Division in       |                  | 00111            | 10111           | bit 0  |

| Legend:       |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |                  |                  |                 |        |

| R = Readabl   | e bit         | W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | e bit             | U = Unimplen     | nented bit, read | d as '0'        |        |

| -n = Value at | POR           | '1' = Bit is se                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | et                | '0' = Bit is cle | ared             | x = Bit is unkn | iown   |

|               |               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                   |                  |                  |                 |        |