Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Detuns                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | · ·                                                                              |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 18x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

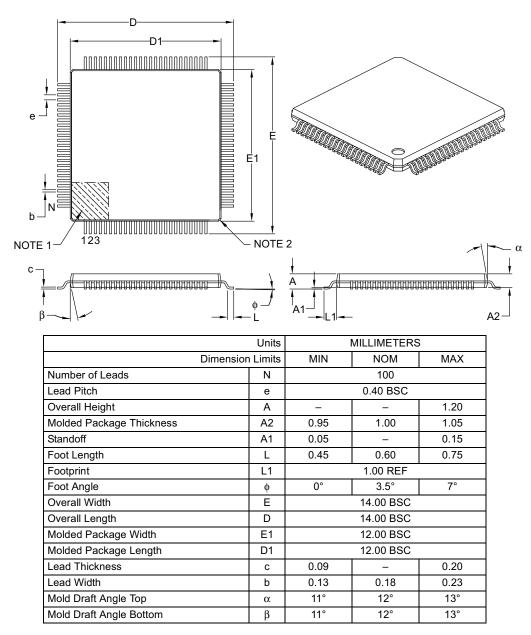

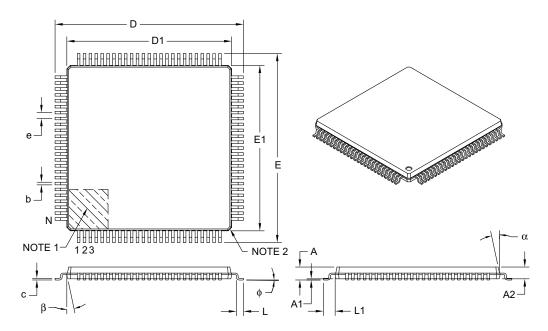

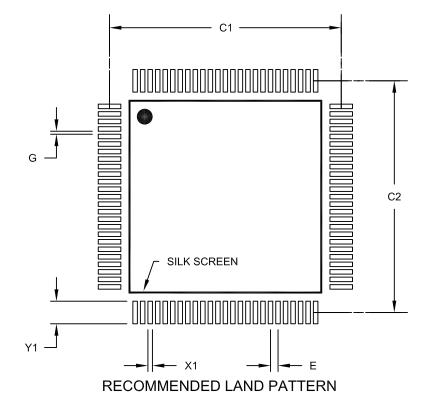

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp706-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                                | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8         | Bit 7         | Bit 6  | Bit 5     | Bit 4         | Bit 3        | Bit 2       | Bit 1   | Bit 0 | All<br>Reset |

|----------|-------------|--------|---------------------------------------|--------|--------|--------|--------|---------|---------------|---------------|--------|-----------|---------------|--------------|-------------|---------|-------|--------------|

| WREG0    | 0000        |        |                                       |        |        |        |        |         | Working Re    | gister 0      |        |           |               |              |             |         |       | 0000         |

| WREG1    | 0002        |        |                                       |        |        |        |        |         | Working Re    | gister 1      |        |           |               |              |             |         |       | 0000         |

| WREG2    | 0004        |        |                                       |        |        |        |        |         | Working Re    | gister 2      |        |           |               |              |             |         |       | 0000         |

| WREG3    | 0006        |        |                                       |        |        |        |        |         | Working Re    | gister 3      |        |           |               |              |             |         |       | 0000         |

| WREG4    | 0008        |        |                                       |        |        |        |        |         | Working Re    | gister 4      |        |           |               |              |             |         |       | 0000         |

| WREG5    | 000A        |        |                                       |        |        |        |        |         | Working Re    | gister 5      |        |           |               |              |             |         |       | 0000         |

| WREG6    | 000C        |        |                                       |        |        |        |        |         | Working Re    | gister 6      |        |           |               |              |             |         |       | 0000         |

| WREG7    | 000E        |        |                                       |        |        |        |        |         | Working Re    | gister 7      |        |           |               |              |             |         |       | 0000         |

| WREG8    | 0010        |        |                                       |        |        |        |        |         | Working Re    | gister 8      |        |           |               |              |             |         |       | 0000         |

| WREG9    | 0012        |        |                                       |        |        |        |        |         | Working Re    | gister 9      |        |           |               |              |             |         |       | 0000         |

| WREG10   | 0014        |        |                                       |        |        |        |        |         | Working Re    | gister 10     |        |           |               |              |             |         |       | 0000         |

| WREG11   | 0016        |        |                                       |        |        |        |        |         | Working Re    | gister 11     |        |           |               |              |             |         |       | 0000         |

| WREG12   | 0018        |        |                                       |        |        |        |        |         | Working Re    | gister 12     |        |           |               |              |             |         |       | 0000         |

| WREG13   | 001A        |        |                                       |        |        |        |        |         | Working Re    | gister 13     |        |           |               |              |             |         |       | 0000         |

| WREG14   | 001C        |        |                                       |        |        |        |        |         | Working Re    | gister 14     |        |           |               |              |             |         |       | 0000         |

| WREG15   | 001E        |        |                                       |        |        |        |        |         |               |               |        |           | 0800          |              |             |         |       |              |

| SPLIM    | 0020        |        | ·                                     |        |        |        |        |         |               |               |        |           | XXXX          |              |             |         |       |              |

| ACCAL    | 0022        |        |                                       |        |        |        |        |         |               |               |        |           | 0000          |              |             |         |       |              |

| ACCAH    | 0024        |        | Accumulator A High Word Register      |        |        |        |        |         |               |               |        | 0000      |               |              |             |         |       |              |

| ACCAU    | 0026        |        | Accumulator A Upper Word Register     |        |        |        |        |         |               |               |        | 0000      |               |              |             |         |       |              |

| ACCBL    | 0028        |        | Accumulator B Low Word Register       |        |        |        |        |         |               |               |        | 0000      |               |              |             |         |       |              |

| ACCBH    | 002A        |        |                                       |        |        |        |        | Accum   | ulator B Higł | n Word Regi   | ster   |           |               |              |             |         |       | 0000         |

| ACCBU    | 002C        |        |                                       |        |        |        |        | Accumu  | lator B Uppe  | er Word Reg   | ister  |           |               |              |             |         |       | 0000         |

| PCL      | 002E        |        |                                       |        |        |        |        | Program | n Counter Lo  | w Word Reg    | gister |           |               |              |             |         |       | 0000         |

| PCH      | 0030        | _      | _                                     | _      | _      | _      |        | _       | _             |               |        | Progra    | m Counter I   | -ligh Byte R | egister     |         |       | 0000         |

| TBLPAG   | 0032        | _      | _                                     |        |        |        | _      | _       | —             |               |        | Table F   | Page Addres   | s Pointer F  | legister    |         |       | 0000         |

| PSVPAG   | 0034        | _      | _                                     |        |        |        | _      | _       | —             |               | Progra | am Memory | Visibility Pa | age Addres   | s Pointer R | egister |       | 0000         |

| RCOUNT   | 0036        |        |                                       |        |        |        |        | Repe    | eat Loop Cou  | inter Registe | er     |           |               |              |             |         |       | XXXX         |

| DCOUNT   | 0038        |        |                                       |        |        |        |        |         | DCOUNT        | <15:0>        |        |           |               |              |             |         |       | XXXX         |

| DOSTARTL | 003A        |        |                                       |        |        |        |        | DOS     | TARTL<15:     | 1>            |        |           |               |              |             |         | 0     | XXXX         |

| DOSTARTH | 003C        | _      | —                                     | —      | _      | —      |        | —       | —             | —             | —      |           |               | DOSTAF       | TH<5:0>     |         |       | 00xx         |

| DOENDL   | 003E        |        |                                       |        |        |        |        | DO      | ENDL<15:1     | >             |        |           |               |              |             |         | 0     | XXXX         |

| DOENDH   | 0040        | _      | —                                     | —      | _      | —      |        | —       | _             | —             | —      |           |               | DOE          | NDH         |         |       | 00xx         |

| SR       | 0042        | OA     | OB                                    | SA     | SB     | OAB    | SAB    | DA      | DC            | IPL2          | IPL1   | IPL0      | RA            | Ν            | OV          | Z       | С     | 0000         |

| CORCON   | 0044        | _      | _                                     | _      | US     | EDT    |        | DL<2:0> |               | SATA          | SATB   | SATDW     | ACCSAT        | IPL3         | PSV         | RND     | IF    | 0020         |

| MODCON   | 0046        | XMODEN | DEN YMODEN BWM<3:0> YWM<3:0> XWM<3:0> |        |        |        |        |         |               |               | 0000   |           |               |              |             |         |       |              |

| XMODSRT  | 0048        |        |                                       |        |        |        |        | )       | KS<15:1>      | •             |        |           |               |              |             |         | 0     | XXXX         |

| XMODEND  | 004A        |        |                                       |        |        |        |        | )       | KE<15:1>      |               |        |           |               |              |             |         | 1     | XXXX         |

| YMODSRT  | 004C        |        |                                       |        |        |        |        | `       | YS<15:1>      |               |        |           |               |              |             |         | 0     | XXXX         |

| YMODEND  | 004E        |        |                                       |        |        |        |        | `       | YE<15:1>      |               |        |           |               |              |             |         | 1     | XXXX         |

# DS70286C-page 40

# dsPIC33FJXXXGPX06/X08/X10

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                              | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8       | Bit 7       | Bit 6        | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

|----------|-------------|--------|-------------------------------------|--------|--------|--------|--------|-------|-------------|-------------|--------------|-------|-------|--------|-------|----------|-------|---------------|

| OC1RS    | 0180        |        |                                     |        |        |        |        | Ou    | put Compai  | re 1 Second | ary Register |       |       |        |       |          |       | xxxx          |

| OC1R     | 0182        |        |                                     |        |        |        |        |       | Output Co   | ompare 1 R  | egister      |       |       |        |       |          |       | xxxx          |

| OC1CON   | 0184        | _      |                                     | OCSIDL | _      | _      | _      | _     | —           |             |              |       | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC2RS    | 0186        |        | •                                   |        | •      | •      | •      | Ou    | put Compar  | e 2 Second  | ary Register |       | •     | •      |       |          |       | xxxx          |

| OC2R     | 0188        |        |                                     |        |        |        |        |       | Output Co   | ompare 2 Re | egister      |       |       |        |       |          |       | xxxx          |

| OC2CON   | 018A        | _      | —                                   | OCSIDL | _      | _      | —      | —     | _           | _           | _            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC3RS    | 018C        |        |                                     |        |        |        |        | Ou    | put Compar  | e 3 Second  | ary Register |       |       |        |       |          |       | xxxx          |

| OC3R     | 018E        |        |                                     |        |        |        |        |       | Output Co   | ompare 3 Re | egister      |       |       |        |       |          |       | xxxx          |

| OC3CON   | 0190        | _      | —                                   | OCSIDL | _      | _      | —      | _     | _           | —           | —            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC4RS    | 0192        |        | Output Compare 4 Secondary Register |        |        |        |        |       |             |             |              | xxxx  |       |        |       |          |       |               |

| OC4R     | 0194        |        | Output Compare 4 Register           |        |        |        |        |       |             |             | xxxx         |       |       |        |       |          |       |               |

| OC4CON   | 0196        | _      | —                                   | OCSIDL | —      | —      | —      |       | —           | _           | —            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC5RS    | 0198        |        |                                     |        |        |        |        | Ou    | tput Compai | re 5 Second | ary Register |       |       |        |       |          |       | xxxx          |

| OC5R     | 019A        |        |                                     |        |        |        |        |       | Output Co   | ompare 5 Re | egister      |       |       |        |       |          |       | xxxx          |

| OC5CON   | 019C        | _      | —                                   | OCSIDL | —      | —      | —      |       | —           |             | —            |       | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC6RS    | 019E        |        |                                     |        |        |        |        | Ou    | tput Compai | re 6 Second | ary Register |       |       |        |       |          |       | xxxx          |

| OC6R     | 01A0        |        |                                     |        |        |        |        |       | Output Co   | ompare 6 Re | egister      |       |       |        |       |          |       | xxxx          |

| OC6CON   | 01A2        | _      | _                                   | OCSIDL | _      | _      | —      |       | _           | _           | —            |       | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC7RS    | 01A4        |        |                                     |        |        |        |        | Ou    | tput Compai | re 7 Second | ary Register |       |       |        |       |          |       | xxxx          |

| OC7R     | 01A6        |        |                                     |        |        |        |        |       | Output Co   | ompare 7 Re | egister      |       |       |        |       |          |       | xxxx          |

| OC7CON   | 01A8        |        |                                     | OCSIDL | —      | _      | —      | _     | —           |             | _            |       | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC8RS    | 01AA        |        | Output Compare 8 Secondary Register |        |        |        |        |       |             | xxxx        |              |       |       |        |       |          |       |               |

| OC8R     | 01AC        |        |                                     |        |        |        |        |       | Output Co   | ompare 8 Re | egister      |       |       |        |       |          |       | xxxx          |

| OC8CON   | 01AE        | —      | —                                   | OCSIDL | _      | _      | _      | _     | _           | _           | _            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# 5.2 RTSP Operation

The dsPIC33FJXXXGPX06/X08/X10 Flash program memory array is organized into rows of 64 instructions or 192 bytes. RTSP allows the user to erase a page of memory, which consists of eight rows (512 instructions) at a time, and to program one row or one word at a time. Table 25-12 illustrates typical erase and programming times. The 8-row erase pages and single row write rows are edge-aligned, from the beginning of program memory, on boundaries of 1536 bytes and 192 bytes, respectively.

The program memory implements holding buffers that can contain 64 instructions of programming data. Prior to the actual programming operation, the write data must be loaded into the buffers in sequential order. The instruction words loaded must always be from a group of 64 boundary.

The basic sequence for RTSP programming is to set up a Table Pointer, then do a series of TBLWT instructions to load the buffers. Programming is performed by setting the control bits in the NVMCON register. A total of 64 TBLWTL and TBLWTH instructions are required to load the instructions.

All of the table write operations are single-word writes (two instruction cycles) because only the buffers are written. A programming cycle is required for programming each row.

# 5.3 Programming Operations

A complete programming sequence is necessary for programming or erasing the internal Flash in RTSP mode. The processor stalls (waits) until the programming operation is finished.

The programming time depends on the FRC accuracy (see Table 25-19) and the value of the FRC Oscillator Tuning register (see Register 9-4). Use the following formula to calculate the minimum and maximum values for the Row Write Time, Page Erase Time and Word Write Cycle Time parameters (see Table 25-12).

## EQUATION 5-1: PROGRAMMING TIME

For example, if the device is operating at +85°C, the FRC accuracy will be  $\pm 2\%$ . If the TUN<5:0> bits (see Register 9-4) are set to `b111111, the Minimum Row Write Time is:

$$T_{RW} = \frac{11064 \ Cycles}{7.37 \ MHz \times (1 + 0.02) \times (1 - 0.00375)} = 1.48 ms$$

and, the Maximum Row Write Time is:

$$T_{RW} = \frac{11064 \ Cycles}{7.37 \ MHz \times (1 - 0.02) \times (1 - 0.00375)} = 1.54 ms$$

Setting the WR bit (NVMCON<15>) starts the operation, and the WR bit is automatically cleared when the operation is finished.

# 5.4 Control Registers

There are two SFRs used to read and write the program Flash memory:

- NVMCON: Flash Memory Control Register

- NVMKEY: Non-Volatile Memory Key Register

The NVMCON register (Register 5-1) controls which blocks are to be erased, which memory type is to be programmed and the start of the programming cycle.

NVMKEY (Register 5-2) is a write-only register that is used for write protection. To start a programming or erase sequence, the user must consecutively write 55h and AAh to the NVMKEY register. Refer to **Section 5.3 "Programming Operations"** for further details.

## REGISTER 7-10: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 (CONTINUED)

- bit 2 OC1IE: Output Compare Channel 1 Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

- bit 1 IC1IE: Input Capture Channel 1 Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

- bit 0 INTOIE: External Interrupt 0 Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

| REGISTER     |                                 |                                       |          |                   |                 |                 |       |

|--------------|---------------------------------|---------------------------------------|----------|-------------------|-----------------|-----------------|-------|

| R/W-0        | R/W-0                           | R/W-0                                 | R/W-0    | R/W-0             | U-0             | U-0             | R/W-0 |

| T5MD         | T4MD                            | T3MD                                  | T2MD     | T1MD              |                 | —               | DCIMD |

| bit 15       |                                 |                                       |          |                   |                 |                 | bit 8 |

| R/W-0        | R/W-0                           | R/W-0                                 | R/W-0    | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| I2C1MD       | U2MD                            | U1MD                                  | SPI2MD   | SPI1MD            | C2MD            | C1MD            | AD1MD |

| bit 7        |                                 |                                       |          |                   |                 |                 | bit ( |

| Legend:      |                                 |                                       |          |                   |                 |                 |       |

| R = Readab   | le bit                          | W = Writable                          | bit      | U = Unimplen      | nented bit, rea | d as '0'        |       |

| -n = Value a | t POR                           | '1' = Bit is set                      |          | '0' = Bit is clea | ared            | x = Bit is unkr | nown  |

|              |                                 |                                       |          |                   |                 |                 |       |

| bit 15       |                                 | <sup>-5</sup> Module Disal            |          |                   |                 |                 |       |

|              |                                 | nodule is disable<br>nodule is enable |          |                   |                 |                 |       |

| bit 14       |                                 | 4 Module Disa                         |          |                   |                 |                 |       |

| bit i i      |                                 | nodule is disable                     |          |                   |                 |                 |       |

|              | -                               | nodule is enable                      |          |                   |                 |                 |       |

| bit 13       | T3MD: Timer                     | 3 Module Disa                         | ble bit  |                   |                 |                 |       |

|              |                                 | nodule is disable                     |          |                   |                 |                 |       |

|              |                                 | nodule is enable                      |          |                   |                 |                 |       |

| bit 12       | _                               | 2 Module Disa                         |          |                   |                 |                 |       |

|              | -                               | odule is disable<br>odule is enable   |          |                   |                 |                 |       |

| bit 11       |                                 | 1 Module Disal                        |          |                   |                 |                 |       |

|              | -                               | nodule is disable                     |          |                   |                 |                 |       |

|              | -                               | odule is enable                       |          |                   |                 |                 |       |

| bit 10-9     | Unimplemer                      | nted: Read as '                       | 0'       |                   |                 |                 |       |

| bit 8        | DCIMD: DCI                      | Module Disable                        | e bit    |                   |                 |                 |       |

|              |                                 | ule is disabled<br>ule is enabled     |          |                   |                 |                 |       |

| bit 7        | <b>I2C1MD:</b> I <sup>2</sup> C | 1 Module Disat                        | ole bit  |                   |                 |                 |       |

|              |                                 | dule is disabled<br>dule is enabled   |          |                   |                 |                 |       |

| bit 6        | U2MD: UAR                       | T2 Module Disa                        | ble bit  |                   |                 |                 |       |

|              | 1 = UART2 n                     | nodule is disabl                      | ed       |                   |                 |                 |       |

|              | 0 <b>= UART2 n</b>              | nodule is enable                      | ed       |                   |                 |                 |       |

| bit 5        | U1MD: UAR                       | T1 Module Disa                        | ible bit |                   |                 |                 |       |

|              | -                               | nodule is disabl<br>nodule is enabl   |          |                   |                 |                 |       |

| bit 4        |                                 | I2 Module Disa                        |          |                   |                 |                 |       |

| ~            | 1 = SPI2 mo                     | dule is disabled                      |          |                   |                 |                 |       |

| bit 3        |                                 | I1 Module Disa                        | ble bit  |                   |                 |                 |       |

|              |                                 | dule is disabled                      |          |                   |                 |                 |       |

|              | 0 = SPI1 mo                     | dule is enabled                       |          |                   |                 |                 |       |

| bit 2        | C2MD: ECA                       | N2 Module Disa                        | able bit |                   |                 |                 |       |

|              | -                               | nodule is disab                       |          |                   |                 |                 |       |

|              | 0 = ECAN2 n                     | nodule is enabl                       | ed       |                   |                 |                 |       |

### © 2009 Microchip Technology Inc.

| REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER |                                                                                                                                              |                                                                                                                                                      |                                                                     |                                                               |                                     |                    |                |  |  |  |  |

|---------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------|--------------------|----------------|--|--|--|--|

| R/W-0                                                   | R/W-0                                                                                                                                        | R/W-0                                                                                                                                                | U-0                                                                 | R/W-0 HC                                                      | R/W-0                               | R-0                | R-1            |  |  |  |  |

| UTXISEL1                                                | UTXINV                                                                                                                                       | UTXISEL0                                                                                                                                             |                                                                     | UTXBRK                                                        | UTXEN <sup>(1)</sup>                | UTXBF              | TRMT           |  |  |  |  |

| bit 15                                                  |                                                                                                                                              |                                                                                                                                                      |                                                                     |                                                               |                                     |                    | bit 8          |  |  |  |  |

| R/W-0                                                   | R/W-0                                                                                                                                        | R/W-0                                                                                                                                                | R-1                                                                 | R-0                                                           | R-0                                 | R/C-0              | R-0            |  |  |  |  |

|                                                         | EL<1:0>                                                                                                                                      | ADDEN                                                                                                                                                | RIDLE                                                               | PERR                                                          | FERR                                | OERR               | URXDA          |  |  |  |  |

| bit 7                                                   |                                                                                                                                              |                                                                                                                                                      |                                                                     |                                                               |                                     |                    | bit C          |  |  |  |  |

| Logondi                                                 |                                                                                                                                              |                                                                                                                                                      |                                                                     |                                                               |                                     |                    |                |  |  |  |  |

| Legend:                                                 | . L. 14                                                                                                                                      | HC = Hardwar                                                                                                                                         |                                                                     |                                                               | mented bit mee                      |                    |                |  |  |  |  |

| R = Readable                                            |                                                                                                                                              | W = Writable k                                                                                                                                       | DIT                                                                 | -                                                             | mented bit, read                    |                    |                |  |  |  |  |

| -n = Value at I                                         | POR                                                                                                                                          | '1' = Bit is set                                                                                                                                     |                                                                     | '0' = Bit is cle                                              | ared                                | x = Bit is unkı    | nown           |  |  |  |  |

| bit 15,13                                               | <ul> <li>11 = Reserve</li> <li>10 = Interrupt</li> <li>transmit</li> <li>01 = Interrupt</li> <li>operatio</li> <li>00 = Interrupt</li> </ul> | D>: Transmissioned; do not use<br>t when a charact<br>buffer become<br>t when the last of<br>t when a charact<br>t when a charact<br>one character o | ter is transfe<br>s empty<br>character is s<br>ed<br>ter is transfe | erred to the Trais<br>shifted out of th<br>erred to the Trais | nsmit Shift Regi<br>e Transmit Shif | t Register; all tr | ansmit         |  |  |  |  |

| bit 14                                                  |                                                                                                                                              | nsmit Polarity In                                                                                                                                    |                                                                     | ansmit buller)                                                |                                     |                    |                |  |  |  |  |

|                                                         |                                                                                                                                              |                                                                                                                                                      |                                                                     |                                                               |                                     |                    |                |  |  |  |  |

| bit 12                                                  |                                                                                                                                              | ted: Read as 'o                                                                                                                                      |                                                                     |                                                               |                                     |                    |                |  |  |  |  |

| bit 11                                                  | -                                                                                                                                            | ansmit Break bit                                                                                                                                     |                                                                     |                                                               |                                     |                    |                |  |  |  |  |

|                                                         | 1 = Send Syn<br>cleared b<br>0 = Sync Bre                                                                                                    | nc Break on new<br>by hardware upo<br>eak transmissior                                                                                               | t transmission<br>on completion<br>n disabled or                    | n                                                             | llowed by twelve                    | e '0' bits, follow | ed by Stop bit |  |  |  |  |

| bit 10                                                  | 1 = Transmit                                                                                                                                 | ismit Enable bit<br>enabled, UxTX<br>disabled, any p                                                                                                 | pin controlle                                                       |                                                               | rted and buffer                     | is reset. UxTX     | pin controlled |  |  |  |  |

| bit 9                                                   | 1 = Transmit                                                                                                                                 | smit Buffer Full<br>buffer is full<br>buffer is not ful                                                                                              |                                                                     |                                                               | er can be writte                    | n                  |                |  |  |  |  |

| bit 8                                                   | 1 = Transmit                                                                                                                                 | mit Shift Registe<br>Shift Register is<br>Shift Register i                                                                                           | empty and t                                                         | ransmit buffer is                                             |                                     |                    | as completed   |  |  |  |  |

| bit 7-6                                                 | 11 = Interrupt<br>10 = Interrupt<br>0x = Interrupt                                                                                           | <b>0&gt;:</b> Receive Intention<br>t is set on UxRS<br>t is set on UxRS<br>t is set when ar<br>Receive buffer h                                      | R transfer m<br>R transfer m<br>y character                         | naking the rece<br>naking the rece<br>is received and         | ive buffer 3/4 fu                   | ll (i.e., has 3 da | ata characters |  |  |  |  |

# **Note 1:** Refer to **Section 17. "UART"** (DS70188) in the *"dsPIC33F Family Reference Manual"* for information on enabling the UART module for transmit operation.

# REGISTER 19-1: CICTRL1: ECAN™ CONTROL REGISTER 1

| U-0          | U-0                            | R/W-0                  | R/W-0          | r-0              | R/W-1              | R/W-0            | R/W-0    |

|--------------|--------------------------------|------------------------|----------------|------------------|--------------------|------------------|----------|

|              | —                              | CSIDL                  | ABAT           |                  |                    | REQOP<2:0>       |          |

| bit 15       |                                |                        |                |                  |                    |                  | bit 8    |

| R-1          | R-0                            | R-0                    | U-0            | R/W-0            | U-0                | U-0              | R/W-0    |

|              | OPMODE<2:0>                    |                        | _              | CANCAP           |                    | _                | WIN      |

| bit 7        |                                |                        |                |                  |                    |                  | bit 0    |

| Legend:      |                                |                        |                |                  |                    |                  |          |

| R = Readab   | le bit                         | W = Writable           | bit            | U = Unimpler     | mented bit, read   | d as '0'         |          |

| -n = Value a | t POR                          | '1' = Bit is set       |                | '0' = Bit is cle | ared               | r = Bit is Rese  | erved    |

|              |                                |                        |                |                  |                    |                  |          |

| bit 15-14    | Unimplemen                     | ted: Read as '         | 0'             |                  |                    |                  |          |

| bit 13       | CSIDL: Stop                    | in Idle Mode b         | oit            |                  |                    |                  |          |

|              | 1 = Discontinu                 | ue module ope          | ration when d  | evice enters Id  | lle mode           |                  |          |

|              | 0 = Continue                   | module operat          | ion in Idle mo | de               |                    |                  |          |

| bit 12       | ABAT: Abort                    | -                      |                |                  |                    |                  |          |

|              | Signal all tran<br>are aborted | smit buffers to        | abort transmi  | ssion. Module    | will clear this bi | t when all trans | missions |

| oit 11       | Reserved: Do                   | o not use              |                |                  |                    |                  |          |

| bit 10-8     | REQOP<2:0>                     | Request Op             | eration Mode   | bits             |                    |                  |          |

|              | 000 <b>= Set No</b>            | rmal Operation         | n mode         |                  |                    |                  |          |

|              | 001 = Set Dis                  |                        |                |                  |                    |                  |          |

|              | 010 = Set Loc<br>011 = Set Lis | ten Only Mode          | 1              |                  |                    |                  |          |

|              |                                | nfiguration mo         |                |                  |                    |                  |          |

|              |                                | ed - do not us         |                |                  |                    |                  |          |

|              |                                | ed - do not us         |                |                  |                    |                  |          |

| 6:4 7 F      |                                | ten All Messag         |                |                  |                    |                  |          |

| bit 7-5      |                                | is in Normal (         |                | 10               |                    |                  |          |

|              |                                | is in Disable          | •              | le               |                    |                  |          |

|              | 010 = Module                   | is in Loopbac          | k mode         |                  |                    |                  |          |

|              |                                | is in Listen O         |                |                  |                    |                  |          |

|              | 100 = Module<br>101 = Reserv   | e is in Configur<br>ed | ation mode     |                  |                    |                  |          |

|              | 110 = Reserv                   |                        |                |                  |                    |                  |          |

|              | 111 = Module                   | is in Listen A         | I Messages m   | ode              |                    |                  |          |

| bit 4        | Unimplemen                     | ted: Read as '         | 0'             |                  |                    |                  |          |

| bit 3        | CANCAP: C                      | AN Message F           | Receive Timer  | Capture Event    | t Enable bit       |                  |          |

|              | 1 = Enable in<br>0 = Disable C |                        | sed on CAN n   | nessage receiv   | /e                 |                  |          |

| bit 2-1      |                                | ted: Read as '         | 0'             |                  |                    |                  |          |

| bit 0        | WIN: SFR M                     |                        |                |                  |                    |                  |          |

|              | 1 = Use filter                 | •                      | -              |                  |                    |                  |          |

|              | 0 = Use buffe                  |                        |                |                  |                    |                  |          |

| U-0                               | U-0                      | U-0              | U-0        | U-0              | U-0              | U-0             | U-0   |

|-----------------------------------|--------------------------|------------------|------------|------------------|------------------|-----------------|-------|

| _                                 | —                        | _                | _          | —                | —                | _               | _     |

| bit 15                            |                          |                  |            |                  |                  |                 | bit   |

|                                   |                          | DAMO             |            |                  |                  |                 |       |

| R/W-0                             | R/W-0                    | R/W-0            | R/W-0      | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

|                                   | IW<1:0>                  |                  |            | BRF              | P<5:0>           |                 |       |

| bit 7                             |                          |                  |            |                  |                  |                 | bit   |

|                                   |                          |                  |            |                  |                  |                 |       |

| Legend:                           |                          |                  |            |                  |                  |                 |       |

| R = Readable bit W = Writable bit |                          |                  |            | U = Unimpler     | mented bit, read | l as '0'        |       |

| -n = Value a                      | at POR                   | '1' = Bit is set |            | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|                                   |                          |                  |            |                  |                  |                 |       |

| bit 15-8                          | Unimplemen               | ted: Read as '   | 0'         |                  |                  |                 |       |

| bit 7-6                           | <b>SJW&lt;1:0&gt;:</b> S | ynchronization   | Jump Width | bits             |                  |                 |       |

|                                   | 11 = Length is           | s 4 x Tq         |            |                  |                  |                 |       |

|                                   | 10 = Length is           |                  |            |                  |                  |                 |       |

|                                   | 01 = Length is           |                  |            |                  |                  |                 |       |

|                                   | 00 = Length is           |                  |            |                  |                  |                 |       |

| bit 5-0                           |                          | Baud Rate Pres   |            |                  |                  |                 |       |

|                                   | 11 1111 <b>=</b> T       | Q = 2 x 64 x 1/  | FCAN       |                  |                  |                 |       |

|                                   | •                        |                  |            |                  |                  |                 |       |

|                                   | •                        |                  |            |                  |                  |                 |       |

|                                   | •                        |                  |            |                  |                  |                 |       |

|                                   |                          | Q = 2 x 3 x 1/F  |            |                  |                  |                 |       |

|                                   | 00 0001 = T              | q = 2 x 2 x 1/F  | CAN        |                  |                  |                 |       |

00 0000 = TQ = 2 x 1 x 1/FCAN

# **REGISTER 19-11:** CIFEN1: ECAN™ ACCEPTANCE FILTER ENABLE REGISTER

| R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1   | R/W-1  | R/W-1  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| FLTEN15 | FLTEN14 | FLTEN13 | FLTEN12 | FLTEN11 | FLTEN10 | FLTEN9 | FLTEN8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/W-1  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| FLTEN7 | FLTEN6 | FLTEN5 | FLTEN4 | FLTEN3 | FLTEN2 | FLTEN1 | FLTEN0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0

FLTENn: Enable Filter n to Accept Messages bits

1 = Enable Filter n

0 = Disable Filter n

# REGISTER 19-12: CiBUFPNT1: ECAN™ FILTER 0-3 BUFFER POINTER REGISTER

| R/W-0         | R/W-0      | R/W-0                             | R/W-0         | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |  |  |

|---------------|------------|-----------------------------------|---------------|------------------------------------|-------|-----------------|-------|--|--|--|

|               | F3BP       | <3:0>                             |               |                                    | F2BI  | ><3:0>          |       |  |  |  |

| bit 15        |            |                                   |               |                                    |       |                 | bit 8 |  |  |  |

| R/W-0         | R/W-0      | R/W-0                             | R/W-0         | R/W-0                              | R/W-0 | R/W-0           | R/W-0 |  |  |  |

|               | F1BP       | <3:0>                             |               |                                    | F0BI  | ><3:0>          |       |  |  |  |

| bit 7         |            |                                   |               |                                    |       |                 | bit 0 |  |  |  |

| Legend:       |            |                                   |               |                                    |       |                 |       |  |  |  |

| R = Readabl   | le bit     | W = Writable                      | bit           | U = Unimplemented bit, read as '0' |       |                 |       |  |  |  |

| -n = Value at | t POR      | '1' = Bit is set                  |               | '0' = Bit is clea                  | ared  | x = Bit is unkr | nown  |  |  |  |

| bit 15-12     | F3BP<3:0>: | RX Buffer Writt                   | en when Filte | r 3 Hits bits                      |       |                 |       |  |  |  |

| bit 11-8      | F2BP<3:0>: | RX Buffer Writt                   | en when Filte | r 2 Hits bits                      |       |                 |       |  |  |  |

| bit 7-4       | F1BP<3:0>: | RX Buffer Writt                   | en when Filte | r 1 Hits bits                      |       |                 |       |  |  |  |

| bit 3-0       | F0BP<3:0>: | RX Buffer Writt                   | en when Filte | r 0 Hits bits                      |       |                 |       |  |  |  |

|               |            | hits received ir hits received ir |               |                                    |       |                 |       |  |  |  |

- :

- 0001 = Filter hits received in RX Buffer 1 0000 = Filter hits received in RX Buffer 0

# REGISTER 19-16: CIRXFnSID: ECAN™ ACCEPTANCE FILTER n STANDARD IDENTIFIER (n = 0, 1, ..., 15)

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| SID10  | SID9  | SID8  | SID7  | SID6  | SID5  | SID4  | SID3  |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-x | R/W-x | R/W-x | U-0 | R/W-x | U-0 | R/W-x | R/W-x |

|-------|-------|-------|-----|-------|-----|-------|-------|

| SID2  | SID1  | SID0  | —   | EXIDE | —   | EID17 | EID16 |

| bit 7 |       |       |     |       |     |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

| bit 15-5 | SID<10:0>: Standard Identifier bits<br>1 = Message address bit SIDx must be '1' to match filter<br>0 = Message address bit SIDx must be '0' to match filter |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 4    | Unimplemented: Read as '0'                                                                                                                                  |

| bit 3    | EXIDE: Extended Identifier Enable bit                                                                                                                       |

|          | If MIDE = 1 then:                                                                                                                                           |

|          | 1 = Match only messages with extended identifier addresses                                                                                                  |

|          | 0 = Match only messages with standard identifier addresses                                                                                                  |

|          | If MIDE = 0 then:                                                                                                                                           |

|          | Ignore EXIDE bit.                                                                                                                                           |

| bit 2    | Unimplemented: Read as '0'                                                                                                                                  |

| bit 1-0  | EID<17:16>: Extended Identifier bits                                                                                                                        |

|          | 1 = Message address bit EIDx must be '1' to match filter                                                                                                    |

|          | 0 = Message address bit EIDx must be '0' to match filter                                                                                                    |

# REGISTER 19-17: CiRXFnEID: ECAN™ ACCEPTANCE FILTER n EXTENDED IDENTIFIER (n = 0, 1, ..., 15)

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| EID15  | EID14 | EID13 | EID12 | EID11 | EID10 | EID9  | EID8  |

| bit 15 |       |       |       |       |       |       | bit 8 |

| R/W-x |

|-------|-------|-------|-------|-------|-------|-------|-------|

| EID7  | EID6  | EID5  | EID4  | EID3  | EID2  | EID1  | EID0  |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0

EID<15:0>: Extended Identifier bits

1 = Message address bit EIDx must be '1' to match filter

0 = Message address bit EIDx must be '0' to match filter

| REGISTER 19-29: | CiTRBnDLC: ECAN™ | ' BUFFER n DATA LEN | GTH CONTROL (r | n = 0, 1,, 31) |

|-----------------|------------------|---------------------|----------------|----------------|

|-----------------|------------------|---------------------|----------------|----------------|

| R/W-x  | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

|--------|-------|-------|-------|-------|-------|-------|-------|

| EID5   | EID4  | EID3  | EID2  | EID1  | EID0  | RTR   | RB1   |

| bit 15 |       |       |       |       |       |       | bit 8 |

|        |       |       |       |       |       |       |       |

| U-0    | U-0   | U-0   | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |

| _      | —     | —     | RB0   | DLC3  | DLC2  | DLC1  | DLC0  |

| bit 7             |                  |                                    |                    | bit 0 |

|-------------------|------------------|------------------------------------|--------------------|-------|

| [                 |                  |                                    |                    |       |

| Legend:           |                  |                                    |                    |       |

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |       |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |       |

| bit 15-10 | EID<5:0>: Extended Identifier bits                                                           |

|-----------|----------------------------------------------------------------------------------------------|

| bit 9     | RTR: Remote Transmission Request bit                                                         |

|           | <ol> <li>1 = Message will request remote transmission</li> <li>0 = Normal message</li> </ol> |

| bit 8     | RB1: Reserved Bit 1                                                                          |

|           | User must set this bit to '0' per CAN protocol.                                              |

| bit 7-5   | Unimplemented: Read as '0'                                                                   |

| bit 4     | RB0: Reserved Bit 0                                                                          |

|           | User must set this bit to '0' per CAN protocol.                                              |

| bit 3-0   | DLC<3:0>: Data Length Code bits                                                              |

## REGISTER 19-30: CiTRBnDm: ECAN™ BUFFER n DATA FIELD BYTE m (n = 0, 1, ..., 31; m = 0, 1, ..., 7)<sup>(1)</sup>

| R/W-x   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| TRBnDm7 | TRBnDm6 | TRBnDm5 | TRBnDm4 | TRBnDm3 | TRBnDm2 | TRBnDm1 | TRBnDm0 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

### bit 7-0 TRBnDm<7:0>: Data Field Buffer 'n' Byte 'm' bits

Note 1: The Most Significant Byte contains byte (m + 1) of the buffer.

| REGISTER      | 21-2: ADxC0                                                                                          | ON2: ADCx                                         | CONTROL RE                             | EGISTER 2        | (where x = 1      | or 2)            |            |  |  |  |

|---------------|------------------------------------------------------------------------------------------------------|---------------------------------------------------|----------------------------------------|------------------|-------------------|------------------|------------|--|--|--|

| R/W-0         | R/W-0                                                                                                | R/W-0                                             | U-0                                    | U-0              | R/W-0             | R/W-0            | R/W-0      |  |  |  |

|               | VCFG<2:0>                                                                                            |                                                   |                                        |                  | CSCNA             | CHPS             | <1:0>      |  |  |  |

| bit 15        |                                                                                                      |                                                   |                                        |                  |                   |                  | bit        |  |  |  |

| R-0           | U-0                                                                                                  | R/W-0                                             | R/W-0                                  | R/W-0            | R/W-0             | R/W-0            | R/W-0      |  |  |  |

| BUFS          |                                                                                                      |                                                   | SMP                                    | <3:0>            |                   | BUFM             | ALTS       |  |  |  |

| bit 7         |                                                                                                      |                                                   |                                        |                  |                   |                  | bit        |  |  |  |

| Legend:       |                                                                                                      |                                                   |                                        |                  |                   |                  |            |  |  |  |

| R = Readable  | e bit                                                                                                | W = Writable                                      | bit                                    | U = Unimple      | mented bit, read  | d as '0'         |            |  |  |  |

| -n = Value at | POR                                                                                                  | '1' = Bit is se                                   | t                                      | '0' = Bit is cle | eared             | x = Bit is unkn  | own        |  |  |  |

| bit 15-13     |                                                                                                      | Converter Vol                                     | tage Reference                         | Configuration    | hite              |                  |            |  |  |  |

| 511 15-15     |                                                                                                      | VREF+                                             | VREF-                                  |                  |                   |                  |            |  |  |  |

|               | 000                                                                                                  | AVDD                                              | Avss                                   | =                |                   |                  |            |  |  |  |

|               |                                                                                                      | rnal VREF+                                        | Avss                                   | -                |                   |                  |            |  |  |  |

|               | 010                                                                                                  | AVDD                                              | External VREF-                         | _                |                   |                  |            |  |  |  |

|               | 011 Exte                                                                                             | rnal VREF+                                        | External VREF-                         |                  |                   |                  |            |  |  |  |

|               | 1xx                                                                                                  | Avdd                                              | Avss                                   |                  |                   |                  |            |  |  |  |

| bit 12-11     | Unimplemen                                                                                           | ted: Read as                                      | ʻ0 <b>'</b>                            |                  |                   |                  |            |  |  |  |

| bit 10        | CSCNA: Scar                                                                                          | n Input Select                                    | ions for CH0+ d                        | uring Sample     | A bit             |                  |            |  |  |  |

|               | 1 = Scan inp                                                                                         | uts                                               |                                        | <b>C</b> .       |                   |                  |            |  |  |  |

|               | 0 = Do not so                                                                                        | can inputs                                        |                                        |                  |                   |                  |            |  |  |  |

| bit 9-8       | CHPS<1:0>:                                                                                           | Selects Chani                                     | nels Utilized bits                     | 3                |                   |                  |            |  |  |  |

|               | When AD12B = 1, CHPS<1:0> is: U-0, Unimplemented, Read as '0'<br>1x = Converts CH0, CH1, CH2 and CH3 |                                                   |                                        |                  |                   |                  |            |  |  |  |

|               |                                                                                                      |                                                   |                                        |                  |                   |                  |            |  |  |  |

|               | 01 = Convert                                                                                         |                                                   | 11                                     |                  |                   |                  |            |  |  |  |

| bit 7         |                                                                                                      |                                                   | (only valid whe                        | n BIJEM = 1)     |                   |                  |            |  |  |  |

|               | 1 = ADC is c                                                                                         | urrently filling                                  | second half of b                       | ouffer, user sh  | ould access dat   |                  |            |  |  |  |

|               |                                                                                                      | , ,                                               |                                        | er, user should  | l access data in  | second half      |            |  |  |  |

| bit 6         | Unimplemen                                                                                           | ted: Read as                                      | ʻ0'                                    |                  |                   |                  |            |  |  |  |

| bit 5-2       | SMPI<3:0>: S<br>operations pe                                                                        |                                                   | ent Rate for DN                        | IA Addresses     | bits or number    | of sample/conv   | ersion     |  |  |  |

|               | 1111 = Increi                                                                                        | ments the D                                       | MA address o                           | or generates     | interrupt after   | completion of    | every 16t  |  |  |  |

|               | 1110 = Increi                                                                                        |                                                   | MA address c                           | or generates     | interrupt after   | completion of    | every 15t  |  |  |  |

|               | • samp                                                                                               | le/conversion                                     | operation                              |                  |                   |                  |            |  |  |  |

|               | •                                                                                                    |                                                   |                                        |                  |                   |                  |            |  |  |  |

|               |                                                                                                      |                                                   |                                        | or generates     | interrupt after   | completion o     | f every 2r |  |  |  |

|               | 0000 = Increi                                                                                        | e/conversion of<br>ments the l<br>e/conversion of | DMA address                            | or generate      | es interrupt a    | fter completio   | n of eve   |  |  |  |

| bit 1         | BUFM: Buffer                                                                                         | Fill Mode Sel                                     | ect bit                                |                  |                   |                  |            |  |  |  |

|               |                                                                                                      | -                                                 | buffer on first ir<br>fer from the beg |                  | econd half of the | e buffer on next | interrupt  |  |  |  |

| bit 0         | -                                                                                                    | -                                                 | ple Mode Selec                         | -                |                   |                  |            |  |  |  |

|               |                                                                                                      | -                                                 |                                        |                  | nple and Sample   | e B on next san  | nple       |  |  |  |