Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 69                                                                               |

| Program Memory Size        | 128KB (128K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 24x10/12b                                                                    |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 80-TQFP                                                                          |

| Supplier Device Package    | 80-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp708-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

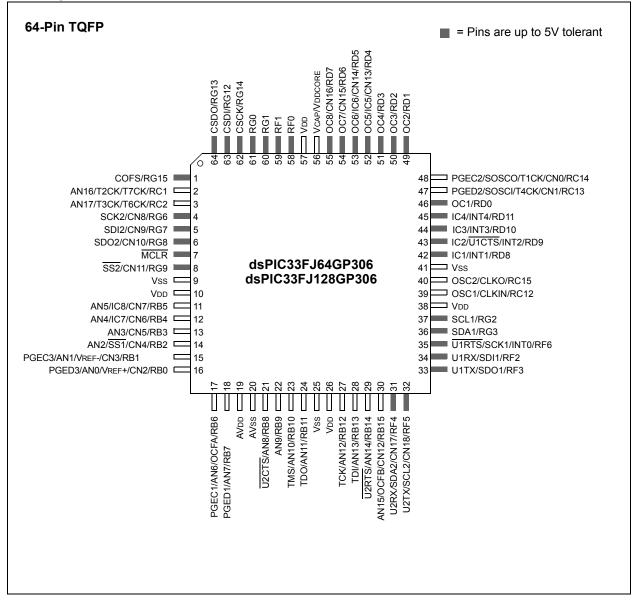

### Pin Diagrams (Continued)

### TABLE 4-9: I2C1 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8 | Bit 7                 | Bit 6 | Bit 5    | Bit 4      | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|---------|--------|---------|--------|--------|--------|--------|-------|-----------------------|-------|----------|------------|------------|-------|-------|-------|---------------|

| I2C1RCV  | 0200        | _       | _      | _       | _      | _      |        | _      | _     | Receive Register      |       |          |            |            |       |       | 0000  |               |

| I2C1TRN  | 0202        | _       | _      | _       | _      | _      | _      | _      | _     |                       |       |          | Transmit   | Register   |       |       |       | OOFF          |

| I2C1BRG  | 0204        | _       | _      | _       | _      | _      | _      | _      |       |                       |       | Baud Rat | e Generato | r Register |       |       |       | 0000          |

| I2C1CON  | 0206        | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW | SMEN  | GCEN                  | STREN | ACKDT    | ACKEN      | RCEN       | PEN   | RSEN  | SEN   | 1000          |

| I2C1STAT | 0208        | ACKSTAT | TRSTAT | _       | _      | _      | BCL    | GCSTAT | ADD10 | IWCOL                 | I2COV | D_A      | Р          | S          | R_W   | RBF   | TBF   | 0000          |

| I2C1ADD  | 020A        | —       | _      | —       | —      | _      |        |        |       |                       |       | Address  | Register   |            |       |       |       | 0000          |

| I2C1MSK  | 020C        | —       | _      | —       | —      | _      |        |        |       | Address Mask Register |       |          |            |            |       |       | 0000  |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-10: I2C2 REGISTER MAP

| SFR Name | SFR<br>Addr | Bit 15  | Bit 14 | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9                 | Bit 8            | Bit 7 | Bit 6 | Bit 5    | Bit 4      | Bit 3      | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|----------|-------------|---------|--------|---------|--------|--------|--------|-----------------------|------------------|-------|-------|----------|------------|------------|-------|-------|-------|---------------|

| I2C2RCV  | 0210        | _       | _      | _       | _      | _      |        | _                     | Receive Register |       |       |          |            |            |       |       |       | 0000          |

| I2C2TRN  | 0212        | _       | _      | _       | —      | _      |        | —                     | —                |       |       |          | Transmit   | Register   |       |       |       | OOFF          |

| I2C2BRG  | 0214        | _       | _      | _       | —      | _      |        | —                     |                  |       |       | Baud Rat | e Generato | r Register |       |       |       | 0000          |

| I2C2CON  | 0216        | I2CEN   | _      | I2CSIDL | SCLREL | IPMIEN | A10M   | DISSLW                | SMEN             | GCEN  | STREN | ACKDT    | ACKEN      | RCEN       | PEN   | RSEN  | SEN   | 1000          |

| I2C2STAT | 0218        | ACKSTAT | TRSTAT | _       | —      | _      | BCL    | GCSTAT                | ADD10            | IWCOL | I2COV | D_A      | Р          | S          | R_W   | RBF   | TBF   | 0000          |

| I2C2ADD  | 021A        |         | _      | _       | —      | _      | I      |                       | Address Register |       |       |          |            |            |       |       | 0000  |               |

| I2C2MSK  | 021C        | _       |        | _       | _      | _      |        | Address Mask Register |                  |       |       |          |            |            |       |       | 0000  |               |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-15: ADC1 REGISTER MAP

| File Name               | Addr | Bit 15 | Bit 14    | Bit 13 | Bit 12  | Bit 11                                                | Bit 10             | Bit 9   | Bit 8   | Bit 7  | Bit 6  | Bit 5  | Bit 4      | Bit 3  | Bit 2  | Bit 1     | Bit 0   | All<br>Resets |

|-------------------------|------|--------|-----------|--------|---------|-------------------------------------------------------|--------------------|---------|---------|--------|--------|--------|------------|--------|--------|-----------|---------|---------------|

| ADC1BUF0                | 0300 |        |           |        |         | ADC Data Buffer 0                                     |                    |         |         |        |        |        |            |        | xxxx   |           |         |               |

| AD1CON1                 | 0320 | ADON   | —         | ADSIDL | ADDMABM | M – AD12B FORM<1:0> SSRC<2:0> – SIMSAM ASAM SAMP DONE |                    |         |         |        |        |        |            | DONE   | 0000   |           |         |               |

| AD1CON2                 | 0322 | ١      | /CFG<2:0> | •      | _       | _                                                     | CSCNA              | CHP     | S<1:0>  | BUFS   | _      |        | SMPI       | <3:0>  |        | BUFM      | ALTS    | 0000          |

| AD1CON3                 | 0324 | ADRC   | _         | _      |         | S                                                     | AMC<4:0> ADCS<7:0> |         |         |        |        |        |            | 0000   |        |           |         |               |

| AD1CHS123               | 0326 | _      | _         | _      | _       | _                                                     | CH123N             | NB<1:0> | CH123SB | _      | _      | _      | _          | _      | CH123N | NA<1:0>   | CH123SA | 0000          |

| AD1CHS0                 | 0328 | CH0NB  | _         |        |         | CI                                                    | H0SB<4:0>          | >       |         | CH0NA  |        | —      | CH0SA<4:0> |        |        | 0000      |         |               |

| AD1PCFGH <sup>(1)</sup> | 032A | PCFG31 | PCFG30    | PCFG29 | PCFG28  | PCFG27                                                | PCFG26             | PCFG25  | PCFG24  | PCFG23 | PCFG22 | PCFG21 | PCFG20     | PCFG19 | PCFG18 | PCFG17    | PCFG16  | 0000          |

| AD1PCFGL                | 032C | PCFG15 | PCFG14    | PCFG13 | PCFG12  | PCFG11                                                | PCFG10             | PCFG9   | PCFG8   | PCFG7  | PCFG6  | PCFG5  | PCFG4      | PCFG3  | PCFG2  | PCFG1     | PCFG0   | 0000          |

| AD1CSSH(1)              | 032E | CSS31  | CSS30     | CSS29  | CSS28   | CSS27                                                 | CSS26              | CSS25   | CSS24   | CSS23  | CSS22  | CSS21  | CSS20      | CSS19  | CSS18  | CSS17     | CSS16   | 0000          |

| AD1CSSL                 | 0330 | CSS15  | CSS14     | CSS13  | CSS12   | CSS11                                                 | CSS10              | CSS9    | CSS8    | CSS7   | CSS6   | CSS5   | CSS4       | CSS3   | CSS2   | CSS1      | CSS0    | 0000          |

| AD1CON4                 | 0332 | _      |           |        | _       |                                                       | _                  | —       | _       |        | _      | _      | _          | _      | [      | DMABL<2:0 | )>      | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: Not all ANx inputs are available on all devices. See the device pin diagrams for available ANx inputs.

### TABLE 4-16: ADC2 REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14    | Bit 13 | Bit 12  | Bit 11            | Bit 10   | Bit 9   | Bit 8   | Bit 7 | Bit 6    | Bit 5 | Bit 4        | Bit 3  | Bit 2  | Bit 1    | Bit 0   | All<br>Resets |

|-----------|------|--------|-----------|--------|---------|-------------------|----------|---------|---------|-------|----------|-------|--------------|--------|--------|----------|---------|---------------|

| ADC2BUF0  | 0340 |        |           |        |         | ADC Data Buffer 0 |          |         |         |       |          |       |              | xxxx   |        |          |         |               |

| AD2CON1   | 0360 | ADON   | —         | ADSIDL | ADDMABM |                   | AD12B    | FOR     | M<1:0>  | ;     | SSRC<2:0 | >     | _            | SIMSAM | ASAM   | SAMP     | DONE    | 0000          |

| AD2CON2   | 0362 | Ņ      | VCFG<2:0> | >      | _       | _                 | CSCNA    | CHP     | S<1:0>  | BUFS  | _        |       | SMPI         | <3:0>  |        | BUFM     | ALTS    | 0000          |

| AD2CON3   | 0364 | ADRC   | —         | _      |         | S                 | AMC<4:0> |         |         |       |          |       | ADC          | S<7:0> |        |          |         | 0000          |

| AD2CHS123 | 0366 | —      | _         | —      | _       |                   | CH123N   | IB<1:0> | CH123SB | _     | _        | _     | _            | —      | CH123N | NA<1:0>  | CH123SA | 0000          |

| AD2CHS0   | 0368 | CH0NB  | _         | —      | _       |                   | CH0S     | B<3:0>  |         | CH0NA | _        | _     | — CH0SA<3:0> |        |        |          | 0000    |               |

| Reserved  | 036A | —      | _         | —      | _       | _                 | _        | _       | _       | _     | _        | _     | _            | —      | —      | _        | _       | 0000          |

| AD2PCFGL  | 036C | PCFG15 | PCFG14    | PCFG13 | PCFG12  | PCFG11            | PCFG10   | PCFG9   | PCFG8   | PCFG7 | PCFG6    | PCFG5 | PCFG4        | PCFG3  | PCFG2  | PCFG1    | PCFG0   | 0000          |

| Reserved  | 036E | —      | _         | —      | _       | _                 | —        | _       | _       | _     | _        | _     | _            | —      | _      | _        | _       | 0000          |

| AD2CSSL   | 0370 | CSS15  | CSS14     | CSS13  | CSS12   | CSS11             | CSS10    | CSS9    | CSS8    | CSS7  | CSS6     | CSS5  | CSS4         | CSS3   | CSS2   | CSS1     | CSS0    | 0000          |

| AD2CON4   | 0372 | _      | _         | —      | _       | _                 | —        | _       | _       | _     | _        | —     | _            | _      | [      | DMABL<2: | 0>      | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| ABLE 7-1:        | INTERRUP                             | T VECTORS   |              |                                 |

|------------------|--------------------------------------|-------------|--------------|---------------------------------|

| Vector<br>Number | Interrupt<br>Request (IRQ)<br>Number | IVT Address | AIVT Address | Interrupt Source                |

| 8                | 0                                    | 0x000014    | 0x000114     | INT0 – External Interrupt 0     |

| 9                | 1                                    | 0x000016    | 0x000116     | IC1 – Input Compare 1           |

| 10               | 2                                    | 0x000018    | 0x000118     | OC1 – Output Compare 1          |

| 11               | 3                                    | 0x00001A    | 0x00011A     | T1 – Timer1                     |

| 12               | 4                                    | 0x00001C    | 0x00011C     | DMA0 – DMA Channel 0            |

| 13               | 5                                    | 0x00001E    | 0x00011E     | IC2 – Input Capture 2           |

| 14               | 6                                    | 0x000020    | 0x000120     | OC2 – Output Compare 2          |

| 15               | 7                                    | 0x000022    | 0x000122     | T2 – Timer2                     |

| 16               | 8                                    | 0x000024    | 0x000124     | T3 – Timer3                     |

| 17               | 9                                    | 0x000026    | 0x000126     | SPI1E – SPI1 Error              |

| 18               | 10                                   | 0x000028    | 0x000128     | SPI1 – SPI1 Transfer Done       |

| 19               | 11                                   | 0x00002A    | 0x00012A     | U1RX – UART1 Receiver           |

| 20               | 12                                   | 0x00002C    | 0x00012C     | U1TX – UART1 Transmitter        |

| 21               | 13                                   | 0x00002E    | 0x00012E     | ADC1 – ADC 1                    |

| 22               | 14                                   | 0x000030    | 0x000130     | DMA1 – DMA Channel 1            |

| 23               | 15                                   | 0x000032    | 0x000132     | Reserved                        |

| 24               | 16                                   | 0x000034    | 0x000134     | SI2C1 – I2C1 Slave Events       |

| 25               | 17                                   | 0x000036    | 0x000136     | MI2C1 – I2C1 Master Events      |

| 26               | 18                                   | 0x000038    | 0x000138     | Reserved                        |

| 27               | 19                                   | 0x00003A    | 0x00013A     | Change Notification Interrupt   |

| 28               | 20                                   | 0x00003C    | 0x00013C     | INT1 – External Interrupt 1     |

| 29               | 21                                   | 0x00003E    | 0x00013E     | ADC2 – ADC 2                    |

| 30               | 22                                   | 0x000040    | 0x000140     | IC7 – Input Capture 7           |

| 31               | 23                                   | 0x000042    | 0x000142     | IC8 – Input Capture 8           |

| 32               | 24                                   | 0x000044    | 0x000144     | DMA2 – DMA Channel 2            |

| 33               | 25                                   | 0x000046    | 0x000146     | OC3 – Output Compare 3          |

| 34               | 26                                   | 0x000048    | 0x000148     | OC4 – Output Compare 4          |

| 35               | 27                                   | 0x00004A    | 0x00014A     | T4 – Timer4                     |

| 36               | 28                                   | 0x00004C    | 0x00014C     | T5 – Timer5                     |

| 37               | 29                                   | 0x00004E    | 0x00014E     | INT2 – External Interrupt 2     |

| 38               | 30                                   | 0x000050    | 0x000150     | U2RX – UART2 Receiver           |

| 39               | 31                                   | 0x000052    | 0x000152     | U2TX – UART2 Transmitter        |

| 40               | 32                                   | 0x000054    | 0x000154     | SPI2E – SPI2 Error              |

| 41               | 33                                   | 0x000056    | 0x000156     | SPI1 – SPI1 Transfer Done       |

| 42               | 34                                   | 0x000058    | 0x000158     | C1RX – ECAN1 Receive Data Ready |

| 43               | 35                                   | 0x00005A    | 0x00015A     | C1 – ECAN1 Event                |

| 44               | 36                                   | 0x00005C    | 0x00015C     | DMA3 – DMA Channel 3            |

| 45               | 37                                   | 0x00005E    | 0x00015E     | IC3 – Input Capture 3           |

| 46               | 38                                   | 0x000060    | 0x000160     | IC4 – Input Capture 4           |

| 47               | 39                                   | 0x000062    | 0x000162     | IC5 – Input Capture 5           |

| 48               | 40                                   | 0x000064    | 0x000164     | IC6 – Input Capture 6           |

| 49               | 41                                   | 0x000066    | 0x000166     | OC5 – Output Compare 5          |

| 50               | 42                                   | 0x000068    | 0x000168     | OC6 – Output Compare 6          |

| 51               | 43                                   | 0x00006A    | 0x00016A     | OC7 – Output Compare 7          |

| 52               | 44                                   | 0x00006C    | 0x00016C     | OC8 – Output Compare 8          |

| 53               | 45                                   | 0x00006E    | 0x00016E     | Reserved                        |

| REGISTER 7           | -1: SR: C            | PU STATUS F          | REGISTER <sup>(1</sup> | )            |                  |          |       |

|----------------------|----------------------|----------------------|------------------------|--------------|------------------|----------|-------|

| R-0                  | R-0                  | R/C-0                | R/C-0                  | R-0          | R/C-0            | R -0     | R/W-0 |

| OA                   | OB                   | SA                   | SB                     | OAB          | SAB              | DA       | DC    |

| bit 15               |                      |                      |                        |              |                  |          | bit 8 |

|                      |                      |                      |                        |              |                  |          |       |

| R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R/W-0 <sup>(3)</sup> | R-0                    | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

| IPL2 <sup>(2)</sup>  | IPL1 <sup>(2)</sup>  | IPL0 <sup>(2)</sup>  | RA                     | N            | OV               | Z        | С     |

| bit 7                |                      |                      |                        |              |                  |          | bit 0 |

|                      |                      |                      |                        |              |                  |          |       |

| Legend:              |                      |                      |                        |              |                  |          |       |

| C = Clear only       | bit                  | R = Readable         | bit                    | U = Unimpler | mented bit, read | 1 as '0' |       |

141

| Legend:            |                      |                                    |  |

|--------------------|----------------------|------------------------------------|--|

| C = Clear only bit | R = Readable bit     | U = Unimplemented bit, read as '0' |  |

| S = Set only bit   | W = Writable bit     | -n = Value at POR                  |  |

| '1' = Bit is set   | '0' = Bit is cleared | x = Bit is unknown                 |  |

bit 7-5

IPL<2:0>: CPU Interrupt Priority Level Status bits<sup>(2)</sup>

- 111 = CPU Interrupt Priority Level is 7 (15), user interrupts disabled

- 110 = CPU Interrupt Priority Level is 6 (14)

- 101 = CPU Interrupt Priority Level is 5 (13)

- 100 = CPU Interrupt Priority Level is 4 (12)

- 011 = CPU Interrupt Priority Level is 3 (11)

- 010 = CPU Interrupt Priority Level is 2 (10)

- 001 = CPU Interrupt Priority Level is 1 (9)

- 000 = CPU Interrupt Priority Level is 0 (8)

### Note 1: For complete register details, see Register 3-1: "SR: CPU STATUS REGISTER".

- 2: The IPL<2:0> bits are concatenated with the IPL<3> bit (CORCON<3>) to form the CPU Interrupt Priority Level. The value in parentheses indicates the IPL if IPL<3> = 1. User interrupts are disabled when IPL<3> = 1.

- 3: The IPL<2:0> Status bits are read-only when NSTDIS (INTCON1<15>) = 1.

### REGISTER 7-2: CORCON: CORE CONTROL REGISTER<sup>(1)</sup>

| U-0          | U-0   | U-0            | R/W-0  | R/W-0               | R-0   | R-0              | R-0   |

|--------------|-------|----------------|--------|---------------------|-------|------------------|-------|

| —            | —     | —              | US     | EDT                 |       | DL<2:0>          |       |

| bit 15       |       |                |        |                     |       |                  | bit 8 |

|              |       |                |        |                     |       |                  |       |

| R/W-0        | R/W-0 | R/W-1          | R/W-0  | R/C-0               | R/W-0 | R/W-0            | R/W-0 |

| SATA         | SATB  | SATDW          | ACCSAT | IPL3 <sup>(2)</sup> | PSV   | RND              | IF    |

| bit 7        |       |                |        |                     |       |                  | bit 0 |

| r            |       |                |        |                     |       |                  |       |

| Legend:      |       | C = Clear only | y bit  |                     |       |                  |       |

| R = Readable | bit   | W = Writable   | bit    | -n = Value at       | POR   | '1' = Bit is set |       |

bit 3

0' = Bit is cleared

IPL3: CPU Interrupt Priority Level Status bit 3(2)

'x = Bit is unknown

1 = CPU interrupt priority level is greater than 7

0 = CPU interrupt priority level is 7 or less

### Note 1: For complete register details, see Register 3-2: "CORCON: CORE CONTROL REGISTER".

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU Interrupt Priority Level.

U = Unimplemented bit, read as '0'

### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

| bit 2 | OC1IF: Output Compare Channel 1 Interrupt Flag Status bit |

|-------|-----------------------------------------------------------|

|       | 1 = Interrupt request has occurred                        |

|       | 0 = Interrupt request has not occurred                    |

| bit 1 | IC1IF: Input Capture Channel 1 Interrupt Flag Status bit  |

|       | 1 = Interrupt request has occurred                        |

|       | 0 = Interrupt request has not occurred                    |

### bit 0 INTOIF: External Interrupt 0 Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

### REGISTER 7-10: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 (CONTINUED)

- bit 2 OC1IE: Output Compare Channel 1 Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

- bit 1 IC1IE: Input Capture Channel 1 Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

- bit 0 INTOIE: External Interrupt 0 Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

| U-0          | R/W-1             | R/W-0                                   | R/W-0          | U-0               | R/W-1            | R/W-0           | R/W-0 |

|--------------|-------------------|-----------------------------------------|----------------|-------------------|------------------|-----------------|-------|

| _            |                   | T4IP<2:0>                               |                |                   |                  | OC4IP<2:0>      |       |

| bit 15       |                   |                                         |                |                   |                  |                 | bit   |

| U-0          | R/W-1             | R/W-0                                   | R/W-0          | U-0               | R/W-1            | R/W-0           | R/W-0 |

| 0-0          | R/W-1             | OC3IP<2:0>                              | R/W-U          | 0-0               | R/W-I            | DMA2IP<2:0>     | R/W-U |

| <br>bit 7    |                   | 00311 \2.02                             |                |                   |                  |                 | bit   |

|              |                   |                                         |                |                   |                  |                 |       |

| Legend:      |                   |                                         |                |                   |                  |                 |       |

| R = Readab   | le bit            | W = Writable b                          | pit            | U = Unimple       | mented bit, rea  | ad as '0'       |       |

| -n = Value a | It POR            | '1' = Bit is set                        |                | '0' = Bit is cle  | eared            | x = Bit is unkn | own   |

|              |                   |                                         |                |                   |                  |                 |       |

| bit 15       | -                 | ented: Read as 'o                       |                |                   |                  |                 |       |

| bit 14-12    |                   | Timer4 Interrupt                        | •              |                   |                  |                 |       |

|              | 111 = Interr      | upt is priority 7 (h                    | nighest priori | ity interrupt)    |                  |                 |       |

|              | •                 |                                         |                |                   |                  |                 |       |

|              | •                 |                                         |                |                   |                  |                 |       |

|              | 001 = Interr      | upt is priority 1                       |                |                   |                  |                 |       |

|              |                   | upt source is disa                      | abled          |                   |                  |                 |       |

| bit 11       | Unimpleme         | nted: Read as 'o                        | )'             |                   |                  |                 |       |

| bit 10-8     | OC4IP<2:0         | Output Compa                            | re Channel     | 4 Interrupt Prior | rity bits        |                 |       |

|              | 111 = Interr      | upt is priority 7 (h                    | nighest priori | ity interrupt)    |                  |                 |       |

|              | •                 |                                         |                |                   |                  |                 |       |

|              | •                 |                                         |                |                   |                  |                 |       |

|              | •<br>001 = Interr | upt is priority 1                       |                |                   |                  |                 |       |

|              |                   | upt is phoney if                        | abled          |                   |                  |                 |       |

| bit 7        |                   | ented: Read as 'o                       |                |                   |                  |                 |       |

| bit 6-4      | -                 | : Output Compa                          |                | 3 Interrunt Prio  | rity bits        |                 |       |

|              |                   | upt is priority 7 (h                    |                | •                 | ity bito         |                 |       |

|              | •                 |                                         | iigheot phon   | ity interrupt)    |                  |                 |       |

|              | •                 |                                         |                |                   |                  |                 |       |

|              | •                 |                                         |                |                   |                  |                 |       |

|              |                   | upt is priority 1<br>upt source is disa | abled          |                   |                  |                 |       |

| hit 2        |                   | ented: Read as '0                       |                |                   |                  |                 |       |

| bit 3        | -                 |                                         |                | mafar Camplet     | Latern at Drie   | with a latita   |       |

| bit 2-0      |                   | 0>: DMA Channe                          |                | -                 | e interrupt Prid | ority dits      |       |

|              |                   | upt is priority 7 (h                    | iignest priori | ity interrupt)    |                  |                 |       |

|              |                   |                                         |                |                   |                  |                 |       |

|              |                   |                                         |                |                   |                  |                 |       |

|              | •                 |                                         |                |                   |                  |                 |       |

|              |                   | upt is priority 1<br>upt source is disa |                |                   |                  |                 |       |

| REGISTER     | R 7-30: IPC15:                 |                                      |                  |                                         | REGISTER 15       |            |       |  |  |  |  |

|--------------|--------------------------------|--------------------------------------|------------------|-----------------------------------------|-------------------|------------|-------|--|--|--|--|

| U-0          | U-0                            | U-0                                  | U-0              | U-0                                     | U-0               | U-0        | U-0   |  |  |  |  |

| _            | _                              | _                                    | _                | _                                       | —                 | —          | —     |  |  |  |  |

| bit 15       |                                |                                      |                  |                                         |                   |            | bit 8 |  |  |  |  |

|              |                                |                                      |                  |                                         |                   |            |       |  |  |  |  |

| U-0          | R/W-1                          | R/W-0                                | R/W-0            | U-0                                     | R/W-1             | R/W-0      | R/W-0 |  |  |  |  |

|              |                                | DMA5IP<2:0>                          |                  |                                         |                   | DCIIP<2:0> |       |  |  |  |  |

| bit 7        |                                |                                      |                  |                                         |                   |            | bit 0 |  |  |  |  |

|              |                                |                                      |                  |                                         |                   |            |       |  |  |  |  |

| Legend:      |                                |                                      |                  |                                         |                   |            |       |  |  |  |  |

| R = Readat   | ole bit                        | W = Writable                         | bit              | U = Unimpler                            | mented bit, read  | as '0'     |       |  |  |  |  |

| -n = Value a | at POR                         | '1' = Bit is set                     |                  | '0' = Bit is cleared x = Bit is unknown |                   |            |       |  |  |  |  |

|              |                                |                                      |                  |                                         |                   |            |       |  |  |  |  |

| bit 15-7     | Unimplemen                     | ted: Read as '                       | 0'               |                                         |                   |            |       |  |  |  |  |

| bit 6-4      | DMA5IP<2:0                     | >: DMA Chann                         | el 5 Data Trar   | nsfer Complete                          | Interrupt Priorit | y bits     |       |  |  |  |  |

|              | 111 = Interru                  | pt is priority 7 (                   | highest priority | y interrupt)                            |                   |            |       |  |  |  |  |

|              | •                              |                                      |                  |                                         |                   |            |       |  |  |  |  |

|              | •                              |                                      |                  |                                         |                   |            |       |  |  |  |  |

|              | •                              |                                      |                  |                                         |                   |            |       |  |  |  |  |

|              | 001 = Interru<br>000 = Interru | pt is priority 1<br>pt source is dis | abled            |                                         |                   |            |       |  |  |  |  |

| bit 3        | Unimplemen                     | ted: Read as '                       | 0'               |                                         |                   |            |       |  |  |  |  |

| bit 2-0      | DCIIP<2:0>:                    | DCI Event Inte                       | rrupt Priority b | oits                                    |                   |            |       |  |  |  |  |

|              |                                |                                      |                  | · · · · · · · · · · · · · · · · · · ·   |                   |            |       |  |  |  |  |

111 = Interrupt is priority 7 (highest priority interrupt)

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

| R/W-0        | R/W-0                       | R/W-1                 | R/W-1         | R/W-0                | R/W-0            | R/W-0              | R/W-0      |

|--------------|-----------------------------|-----------------------|---------------|----------------------|------------------|--------------------|------------|

| ROI          | N/W-0                       | DOZE<2:0>             | D/ VV- I      | DOZEN <sup>(1)</sup> | N/W-0            | FRCDIV<2:0>        | N/W-0      |

| bit 15       |                             | DOZL~2.02             |               | DOZEN                |                  | TRODIV-2.02        | bit        |

|              |                             |                       |               |                      |                  |                    | bit        |

| R/W-0        | R/W-1                       | U-0                   | R/W-0         | R/W-0                | R/W-0            | R/W-0              | R/W-0      |

| PLLP         | OST<1:0>                    |                       |               |                      | PLLPRE<4:0       | >                  |            |

| bit 7        |                             |                       |               |                      |                  |                    | bit        |

|              |                             |                       |               |                      |                  |                    |            |

| Legend:      |                             | -                     | -             | ration bits on Po    | OR               |                    |            |

| R = Readab   |                             | W = Writable          | bit           | •                    | nented bit, read |                    |            |

| -n = Value a | t POR                       | '1' = Bit is set      |               | '0' = Bit is cle     | ared             | x = Bit is unkno   | own        |

| L:1 4 F      |                             |                       | 4             |                      |                  |                    |            |

| bit 15       |                             | er on Interrupt bi    |               | d the process        | r clock/porinho  | ral clock ratio is | sot to 1.1 |

|              |                             | ts have no effect     |               |                      |                  |                    | 361 10 1.1 |

| bit 14-12    | DOZE<2:0>                   | Processor Cloo        | k Reduction   | Select bits          |                  |                    |            |

|              | 000 = Fcy/1                 |                       |               |                      |                  |                    |            |

|              | 001 = FCY/2                 |                       |               |                      |                  |                    |            |

|              | 010 = FCY/4<br>011 = FCY/8  |                       |               |                      |                  |                    |            |

|              | 100 = FCY/1                 | · ,                   |               |                      |                  |                    |            |

|              | 101 = FCY/3                 |                       |               |                      |                  |                    |            |

|              | 110 = FCY/6<br>111 = FCY/1  |                       |               |                      |                  |                    |            |

| bit 11       |                             | ZE Mode Enabl         | o hit(1)      |                      |                  |                    |            |

|              |                             |                       |               | etween the per       | ipheral clocks a | and the processo   | or clocks  |

|              |                             | or clock/periphe      |               |                      |                  |                    |            |

| bit 10-8     | FRCDIV<2:0                  | >: Internal Fast      | RC Oscillato  | or Postscaler bit    | S                |                    |            |

|              |                             | divide by 1 (defa     | ult)          |                      |                  |                    |            |

|              | 001 = FRC 0<br>010 = FRC 0  |                       |               |                      |                  |                    |            |

|              | 010 = FRC (                 |                       |               |                      |                  |                    |            |

|              | 100 <b>= FRC d</b>          | divide by 16          |               |                      |                  |                    |            |

|              | 101 = FRC (                 | -                     |               |                      |                  |                    |            |

|              | 110 = FRC (<br>111 = FRC (  | divide by 256         |               |                      |                  |                    |            |

| bit 7-6      |                             | -                     | Output Divide | er Select bits (al   | so denoted as    | 'N2', PLL postsc   | aler)      |

|              | 00 = Output/                |                       |               | × ×                  |                  | <i>,</i> ,         | ,          |

|              | 01 = Output/                |                       |               |                      |                  |                    |            |

|              | 10 = Reserv<br>11 = Output/ |                       |               |                      |                  |                    |            |

| bit 5        | •                           | o<br>nted: Read as 'o | ı'            |                      |                  |                    |            |

| bit 4-0      | -                           |                       |               | ıt Divider bits (a   | lso denoted as   | 'N1', PLL presca   | aler)      |

|              |                             | ut/2 (default)        |               |                      |                  |                    |            |

|              | 00001 = Inp                 |                       |               |                      |                  |                    |            |

|              | •                           |                       |               |                      |                  |                    |            |

|              | •                           |                       |               |                      |                  |                    |            |

|              |                             |                       |               |                      |                  |                    |            |

**Note 1:** This bit is cleared when the ROI bit is set and an interrupt occurs.

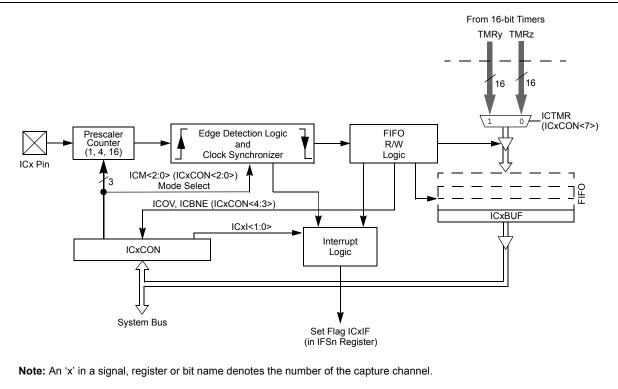

### 14.0 INPUT CAPTURE

Note: This data sheet summarizes the features of the dsPIC33FJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "Input Capture" (DS70198) in the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The input capture module is useful in applications requiring frequency (period) and pulse measurement. The dsPIC33FJXXXGPX06/X08/X10 devices support up to eight input capture channels.

The input capture module captures the 16-bit value of the selected Time Base register when an event occurs at the ICx pin. The events that cause a capture event are listed below in three categories:

Simple Capture Event modes 1. -Capture timer value on every falling edge of input at ICx pin

**FIGURE 14-1:**

-Capture timer value on every rising edge of input at ICx pin

INPUT CAPTURE BLOCK DIAGRAM

- Capture timer value on every edge (rising and 2. falling)

- 3. Prescaler Capture Event modes

- -Capture timer value on every 4th rising edge of input at ICx pin

- -Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base. The selected timer can use either an internal or external clock.

Other operational features include:

- · Device wake-up from capture pin during CPU Sleep and Idle modes

- · Interrupt on input capture event

- 4-word FIFO buffer for capture values

- Interrupt optionally generated after 1, 2, 3 or 4 buffer locations are filled

- · Input capture can also be used to provide additional sources of external interrupts

Note: Only IC1 and IC2 can trigger a DMA data transfer. If DMA data transfers are required, the FIFO buffer size must be set to 1 (ICI < 1:0 > = 0.0).

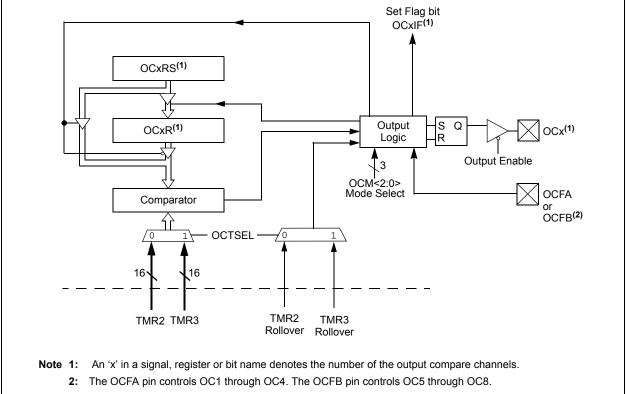

### 15.0 OUTPUT COMPARE

Note: This data sheet summarizes the features of the dsPIC33FJXXXGPX06/X08/X10 families of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 13. "Output Compare" (DS70209) in the "dsPIC33F Family Reference Manual",, which is available on the Microchip web site (www.microchip.com).

The output compare module can select either Timer2 or Timer3 for its time base. The module compares the value of the timer with the value of one or two Compare registers depending on the operating mode selected. The state of the output pin changes when the timer value matches the Compare register value. The output compare module generates either a single output pulse, or a sequence of output pulses, by changing the state of the output pin on the compare match events. The output compare module can also generate interrupts on compare match events.

The output compare module has multiple operating modes:

- Active-Low One-Shot mode

- Active-High One-Shot mode

- Toggle mode

- Delayed One-Shot mode

- Continuous Pulse mode

- PWM mode without Fault Protection

- PWM mode with Fault Protection

| REGISTER 1    | 6-3: SPIxC                                                                                    | ON2: SPIx C                         | ONTROL R       | EGISTER 2         |                  |                  |       |

|---------------|-----------------------------------------------------------------------------------------------|-------------------------------------|----------------|-------------------|------------------|------------------|-------|

| R/W-0         | R/W-0                                                                                         | R/W-0                               | U-0            | U-0               | U-0              | U-0              | U-0   |

| FRMEN         | SPIFSD                                                                                        | FRMPOL                              | _              | _                 | _                | _                |       |

| bit 15        |                                                                                               |                                     |                |                   |                  |                  | bit 8 |

|               |                                                                                               |                                     |                |                   |                  |                  |       |

| U-0           | U-0                                                                                           | U-0                                 | U-0            | U-0               | U-0              | R/W-0            | U-0   |

| —             | —                                                                                             | —                                   |                | —                 |                  | FRMDLY           |       |

| bit 7         |                                                                                               |                                     |                |                   |                  |                  | bit 0 |

| Legend:       |                                                                                               |                                     |                |                   |                  |                  |       |

| R = Readable  | bit                                                                                           | W = Writable                        | bit            | U = Unimplei      | mented bit, read | 1 as '0'         |       |

| -n = Value at |                                                                                               | '1' = Bit is set                    |                | '0' = Bit is cle  |                  | x = Bit is unkno | wn    |

|               |                                                                                               |                                     |                |                   |                  |                  |       |

| bit 15        | FRMEN: Fran                                                                                   | med SPIx Supp                       | ort bit        |                   |                  |                  |       |

|               | 1 = Framed SPIx support enabled ( $\overline{SSx}$ pin used as frame sync pulse input/output) |                                     |                |                   |                  |                  |       |

|               | 0 = Framed S                                                                                  | SPIx support dis                    | sabled         |                   |                  |                  |       |

| bit 14        | SPIFSD: Fran                                                                                  | me Sync Pulse                       | Direction Co   | ntrol bit         |                  |                  |       |

|               |                                                                                               | nc pulse input (<br>nc pulse output | · /            |                   |                  |                  |       |

| bit 13        | FRMPOL: Fra                                                                                   | ame Sync Puls                       | e Polarity bit |                   |                  |                  |       |

|               | 1 = Frame sy                                                                                  | nc pulse is acti                    | ve-high        |                   |                  |                  |       |

|               | 0 = Frame sy                                                                                  | nc pulse is acti                    | ve-low         |                   |                  |                  |       |

| bit 12-2      | Unimplemen                                                                                    | ted: Read as '                      | 0'             |                   |                  |                  |       |

| bit 1         | FRMDLY: Fra                                                                                   | ame Sync Pulse                      | e Edge Selec   | t bit             |                  |                  |       |

|               | 1 = Frame sy                                                                                  | nc pulse coinci                     | des with first | bit clock         |                  |                  |       |

|               |                                                                                               | nc pulse prece                      |                |                   |                  |                  |       |

| bit 0         | Unimplemen                                                                                    | ted: This bit m                     | ust not be se  | t to '1' by the u | ser application  |                  |       |

|               |                                                                                               |                                     |                |                   |                  |                  |       |

### REGISTER 19-1: CICTRL1: ECAN™ CONTROL REGISTER 1

| U-0          | U-0                            | R/W-0                            | R/W-0          | r-0              | R/W-1              | R/W-0            | R/W-0    |  |  |  |

|--------------|--------------------------------|----------------------------------|----------------|------------------|--------------------|------------------|----------|--|--|--|

|              | —                              | CSIDL                            | ABAT           |                  |                    | REQOP<2:0>       |          |  |  |  |

| bit 15       |                                |                                  |                |                  |                    |                  | bit 8    |  |  |  |

| R-1          | R-0                            | R-0                              | U-0            | R/W-0            | U-0                | U-0              | R/W-0    |  |  |  |

|              | OPMODE<2:0>                    |                                  | —              | CANCAP           |                    | _                | WIN      |  |  |  |

| bit 7        |                                |                                  |                |                  |                    |                  | bit 0    |  |  |  |

| Legend:      |                                |                                  |                |                  |                    |                  |          |  |  |  |

| R = Readab   | le bit                         | W = Writable                     | bit            | U = Unimpler     | mented bit, read   | d as '0'         |          |  |  |  |

| -n = Value a | t POR                          | '1' = Bit is set                 |                | '0' = Bit is cle | ared               | r = Bit is Rese  | erved    |  |  |  |

|              |                                |                                  |                |                  |                    |                  |          |  |  |  |

| bit 15-14    | Unimplemen                     | ted: Read as '                   | 0'             |                  |                    |                  |          |  |  |  |

| bit 13       | CSIDL: Stop                    | in Idle Mode b                   | oit            |                  |                    |                  |          |  |  |  |

|              | 1 = Discontinu                 | ue module ope                    | ration when d  | evice enters Id  | lle mode           |                  |          |  |  |  |

|              | 0 = Continue                   | module operat                    | ion in Idle mo | de               |                    |                  |          |  |  |  |

| bit 12       | ABAT: Abort                    | -                                |                |                  |                    |                  |          |  |  |  |

|              | Signal all tran<br>are aborted | smit buffers to                  | abort transmi  | ssion. Module    | will clear this bi | t when all trans | missions |  |  |  |

| oit 11       | Reserved: Do                   | o not use                        |                |                  |                    |                  |          |  |  |  |

| bit 10-8     | REQOP<2:0>                     | Request Op                       | eration Mode   | bits             |                    |                  |          |  |  |  |

|              | 000 <b>= Set No</b>            | rmal Operation                   | n mode         |                  |                    |                  |          |  |  |  |

|              | 001 = Set Dis                  |                                  |                |                  |                    |                  |          |  |  |  |

|              | 010 = Set Loc<br>011 = Set Lis | ten Only Mode                    | 1              |                  |                    |                  |          |  |  |  |

|              |                                | nfiguration mo                   |                |                  |                    |                  |          |  |  |  |

|              |                                | ed - do not us                   |                |                  |                    |                  |          |  |  |  |

|              |                                | ed - do not us                   |                |                  |                    |                  |          |  |  |  |

| 6:4 7 F      |                                | ten All Messag                   |                |                  |                    |                  |          |  |  |  |

| bit 7-5      |                                | is in Normal (                   |                | 10               |                    |                  |          |  |  |  |

|              |                                | is in Disable                    | •              | le               |                    |                  |          |  |  |  |

|              | 010 = Module                   | is in Loopbac                    | k mode         |                  |                    |                  |          |  |  |  |

|              |                                | is in Listen O                   |                |                  |                    |                  |          |  |  |  |

|              |                                | e is in Configur<br>ed           | ation mode     |                  |                    |                  |          |  |  |  |

|              |                                | 101 = Reserved<br>110 = Reserved |                |                  |                    |                  |          |  |  |  |

|              | 111 = Module                   | is in Listen A                   | I Messages m   | ode              |                    |                  |          |  |  |  |

| bit 4        | Unimplemen                     | ted: Read as '                   | 0'             |                  |                    |                  |          |  |  |  |

| bit 3        | CANCAP: C                      | AN Message F                     | Receive Timer  | Capture Event    | t Enable bit       |                  |          |  |  |  |

|              | 1 = Enable in<br>0 = Disable C |                                  | sed on CAN n   | nessage receiv   | /e                 |                  |          |  |  |  |

| bit 2-1      |                                | ted: Read as '                   | 0'             |                  |                    |                  |          |  |  |  |

| bit 0        | WIN: SFR M                     |                                  |                |                  |                    |                  |          |  |  |  |

|              | 1 = Use filter                 | •                                | -              |                  |                    |                  |          |  |  |  |

|              | 0 = Use buffe                  |                                  |                |                  |                    |                  |          |  |  |  |

| R/W-0                  | R/W-0                                                                                              | R/W-0                                                                                                                             | U-0              | U-0               | U-0             | U-0             | U-0   |

|------------------------|----------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------|-------------------|-----------------|-----------------|-------|

|                        | DMABS<2:0>                                                                                         |                                                                                                                                   | —                |                   | —               | —               | _     |

| bit 15                 |                                                                                                    |                                                                                                                                   |                  |                   |                 |                 | bit 8 |

| U-0                    | U-0                                                                                                | U-0                                                                                                                               | R/W-0            | R/W-0             | R/W-0           | R/W-0           | R/W-0 |

| _                      |                                                                                                    | _                                                                                                                                 |                  |                   | FSA<4:0>        |                 |       |

| bit 7                  |                                                                                                    |                                                                                                                                   |                  |                   |                 |                 | bit 0 |

|                        |                                                                                                    |                                                                                                                                   |                  |                   |                 |                 |       |

| Legend:<br>R = Readabl | e bit                                                                                              | W = Writable t                                                                                                                    | oit              | U = Unimplen      | nented bit, rea | d as '0'        |       |

| -n = Value at          | POR                                                                                                | '1' = Bit is set                                                                                                                  |                  | '0' = Bit is clea |                 | x = Bit is unkr | iown  |

|                        | 101 = 24 buff<br>100 = 16 buff<br>011 = 12 buff<br>010 = 8 buffe<br>001 = 6 buffe<br>000 = 4 buffe | fers in DMA RAI<br>fers in DMA RAI<br>fers in DMA RAI<br>fers in DMA RAI<br>fers in DMA RAM<br>fers in DMA RAM<br>fers in DMA RAM | M<br>M<br>M<br>I |                   |                 |                 |       |

| bit 12-5<br>bit 4-0    | -                                                                                                  | 30 buffer                                                                                                                         |                  | its               |                 |                 |       |

|                  | —<br>R/W-0<br>1:0>               | —<br>R/W-0                           |            | R/W-0<br>BRF     |                  | R/W-0           | bit a |

|------------------|----------------------------------|--------------------------------------|------------|------------------|------------------|-----------------|-------|

| R/W-0<br>SJW<    | -                                | R/W-0                                | R/W-0      | -                | -                | R/W-0           |       |

| SJW<             | -                                | R/W-0                                | R/W-0      | -                | -                | R/W-0           | R/W-0 |

|                  | 1:0>                             |                                      |            | BRF              | P<5:0>           |                 |       |

| bit 7            |                                  |                                      |            |                  |                  |                 |       |

|                  |                                  |                                      |            |                  |                  |                 | bit   |

|                  |                                  |                                      |            |                  |                  |                 |       |

| Legend:          |                                  |                                      |            |                  |                  |                 |       |

| R = Readable b   | oit                              | W = Writable I                       | oit        | U = Unimpler     | mented bit, read | d as '0'        |       |

| -n = Value at PO | OR                               | '1' = Bit is set                     |            | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|                  |                                  |                                      |            |                  |                  |                 |       |

| bit 15-8         | Unimplement                      | ted: Read as 'o                      | )'         |                  |                  |                 |       |

| bit 7-6          | SJW<1:0>: S                      | ynchronization                       | Jump Width | bits             |                  |                 |       |

|                  | 11 = Length is                   |                                      |            |                  |                  |                 |       |

|                  | 10 = Length is                   |                                      |            |                  |                  |                 |       |

|                  | 01 = Length is<br>00 = Length is |                                      |            |                  |                  |                 |       |

|                  | •                                | aud Rate Pres                        | color bite |                  |                  |                 |       |

|                  |                                  | $Q = 2 \times 64 \times 1/F$         |            |                  |                  |                 |       |

|                  | •                                | J = Z X 04 X 1/1                     | CAN        |                  |                  |                 |       |

|                  | •                                |                                      |            |                  |                  |                 |       |

|                  | •                                |                                      |            |                  |                  |                 |       |

|                  |                                  | 2 = 2 x 3 x 1/Fo<br>2 = 2 x 2 x 1/Fo |            |                  |                  |                 |       |

00 0000 = TQ = 2 x 1 x 1/FCAN

### REGISTER 19-24: CIRXOVF1: ECAN™ RECEIVE BUFFER OVERFLOW REGISTER 1

| R/C-0   | R/C-0   | R/C-0          | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|----------------|---------|---------|---------|--------|--------|

| RXOVF15 | RXOVF14 | RXOVF13        | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9 | RXOVF8 |

| bit 15  |         |                |         |         |         |        | bit 8  |

|         |         |                |         |         |         |        |        |

| R/C-0   | R/C-0   | R/C-0          | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

| RXOVF7  | RXOVF6  | RXOVF5         | RXOVF4  | RXOVF3  | RXOVF2  | RXOVF1 | RXOVF0 |

| bit 7   |         | •              |         |         |         |        | bit 0  |

|         |         |                |         |         |         |        |        |

| Legend: |         | C = Clear only | v bit   |         |         |        |        |

| Legenu.           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-0

**RXOVF<15:0>:** Receive Buffer n Overflow bits

1 = Module pointed a write to a full buffer (set by module)

0 = Overflow is cleared (clear by application software)

### REGISTER 19-25: CIRXOVF2: ECAN™ RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

|         |         |         |         |         |         |         |         |

| R/C-0   |

| RXOVF23 | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Clear only bit |                             |                    |

|-------------------|--------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit   | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-0

RXOVF<31:16>: Receive Buffer n Overflow bits

1 = Module pointed a write to a full buffer (set by module)

0 = Overflow is cleared (clear by application software)

NOTES:

### **REGISTER 21-9:** AD1PCFGH: ADC1 PORT CONFIGURATION REGISTER HIGH<sup>(1,2,3)</sup>

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| PCFG31 | PCFG30 | PCFG29 | PCFG28 | PCFG27 | PCFG26 | PCFG25 | PCFG24 |

| bit 15 |        |        |        |        |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

| R/W-0  |

| PCFG23 | PCFG22 | PCFG21 | PCFG20 | PCFG19 | PCFG18 | PCFG17 | PCFG16 |

| bit 7  | •      |        |        |        |        |        | bit 0  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0

PCFG<31:16>: ADC Port Configuration Control bits

1 = Port pin in Digital mode, port read input enabled, ADC input multiplexer connected to AVss

0 = Port pin in Analog mode, port read input disabled, ADC samples pin voltage

- **Note 1:** On devices without 32 analog inputs, all PCFG bits are R/W by user. However, PCFG bits are ignored on ports without a corresponding input on device.

- 2: ADC2 only supports analog inputs AN0-AN15; therefore, no ADC2 port Configuration register exists.

- **3:** PCFGx = ANx, where x = 16 through 31.

### **REGISTER 21-10:** ADxPCFGL: ADCx PORT CONFIGURATION REGISTER LOW<sup>(1,2,3)</sup>

| R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

|---------|--------|--------|--------|--------|--------|-------|-------|

| PCFG15  | PCFG14 | PCFG13 | PCFG12 | PCFG11 | PCFG10 | PCFG9 | PCFG8 |

| bit 15  |        |        |        |        |        |       | bit 8 |

|         |        |        |        |        |        |       |       |

| R/W-0   | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

| PCFG7   | PCFG6  | PCFG5  | PCFG4  | PCFG3  | PCFG2  | PCFG1 | PCFG0 |

| bit 7   |        |        | ·      | ·      |        | •     | bit 0 |

|         |        |        |        |        |        |       |       |

| Legend: |        |        |        |        |        |       |       |

| Legend:           |                  |                       |                                    |  |

|-------------------|------------------|-----------------------|------------------------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown                 |  |

bit 15-0

PCFG<15:0>: ADC Port Configuration Control bits

1 = Port pin in Digital mode, port read input enabled, ADC input multiplexer connected to AVss

0 = Port pin in Analog mode, port read input disabled, ADC samples pin voltage

**Note 1:** On devices without 16 analog inputs, all PCFG bits are R/W by user. However, PCFG bits are ignored on ports without a corresponding input on device.

- **2:** On devices with two analog-to-digital modules, both AD1PCFGL and AD2PCFGL will affect the configuration of port pins multiplexed with AN0-AN15.

- **3:** PCFGx = ANx, where x = 0 through 15.

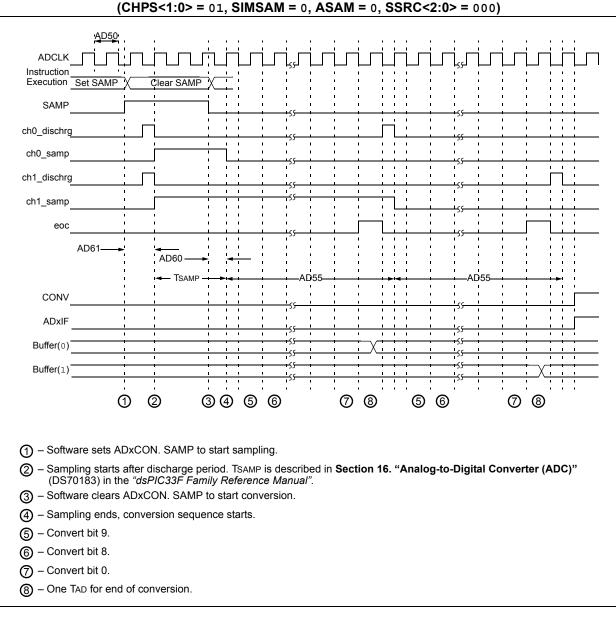

#### FIGURE 25-21: ADC CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (CHPS<1:0> = 01, SIMSAM = 0, ASAM = 0, SSRC<2:0> = 000)