Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 128KB (128K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 16K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 32x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj128gp710t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

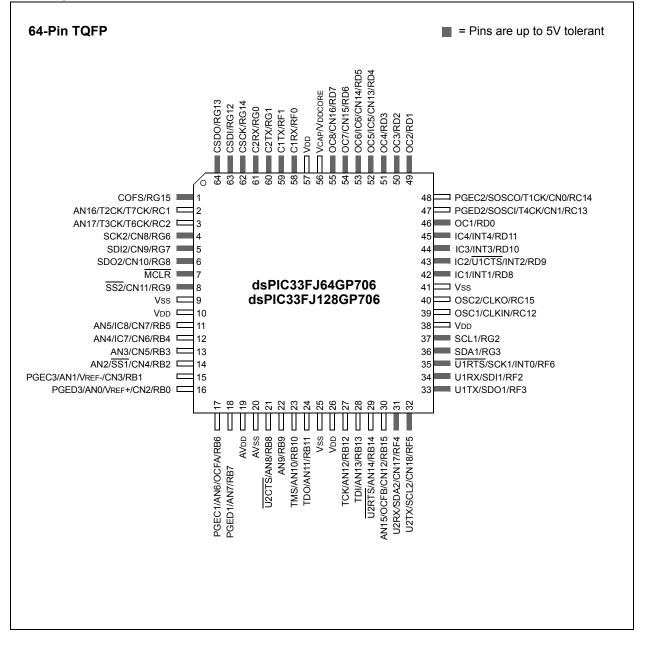

### Pin Diagrams (Continued)

| Reset Type      | Clock Source  | SYSRST Delay           | System Clock<br>Delay | FSCM<br>Delay | Notes            |

|-----------------|---------------|------------------------|-----------------------|---------------|------------------|

| POR             | EC, FRC, LPRC | TPOR + TSTARTUP + TRST | —                     |               | 1, 2, 3          |

|                 | ECPLL, FRCPLL | TPOR + TSTARTUP + TRST | TLOCK                 | TFSCM         | 1, 2, 3, 5, 6    |

|                 | XT, HS, SOSC  | TPOR + TSTARTUP + TRST | Tost                  | TFSCM         | 1, 2, 3, 4, 6    |

|                 | XTPLL, HSPLL  | TPOR + TSTARTUP + TRST | TOST + TLOCK          | TFSCM         | 1, 2, 3, 4, 5, 6 |

| BOR             | EC, FRC, LPRC | TSTARTUP + TRST        | —                     | _             | 3                |

|                 | ECPLL, FRCPLL | TSTARTUP + TRST        | TLOCK                 | TFSCM         | 3, 5, 6          |

|                 | XT, HS, SOSC  | TSTARTUP + TRST        | Tost                  | TFSCM         | 3, 4, 6          |

|                 | XTPLL, HSPLL  | TSTARTUP + TRST        | TOST + TLOCK          | TFSCM         | 3, 4, 5, 6       |

| MCLR            | Any Clock     | Trst                   | —                     | _             | 3                |

| WDT             | Any Clock     | Trst                   | —                     | _             | 3                |

| Software        | Any Clock     | Trst                   | —                     | —             | 3                |

| Illegal Opcode  | Any Clock     | Trst                   | —                     | _             | 3                |

| Uninitialized W | Any Clock     | Trst                   | —                     | —             | 3                |

| Trap Conflict   | Any Clock     | Trst                   | —                     | —             | 3                |

### TABLE 6-3: RESET DELAY TIMES FOR VARIOUS DEVICE RESETS

**Note 1:** TPOR = Power-on Reset delay (10 μs nominal).

- **2:** TSTARTUP = Conditional POR delay of 20 μs nominal (if on-chip regulator is enabled) or 64 ms nominal Power-up Timer delay (if regulator is disabled). TSTARTUP is also applied to all returns from powered-down states, including waking from Sleep mode, only if the regulator is enabled.

- 3: TRST = Internal state Reset time (20 µs nominal).

- **4:** TOST = Oscillator Start-up Timer. A 10-bit counter counts 1024 oscillator periods before releasing the oscillator clock to the system.

- **5**: TLOCK = PLL lock time (20 μs nominal).

- **6**: TFSCM = Fail-Safe Clock Monitor delay (100 μs nominal).

#### 6.2.1 POR AND LONG OSCILLATOR START-UP TIMES

The oscillator start-up circuitry and its associated delay timers are not linked to the device Reset delays that occur at power-up. Some crystal circuits (especially low-frequency crystals) have a relatively long start-up time. Therefore, <u>one or more of the following conditions</u> is possible after SYSRST is released:

- · The oscillator circuit has not begun to oscillate.

- The Oscillator Start-up Timer has not expired (if a crystal oscillator is used).

- The PLL has not achieved a lock (if PLL is used).

The device will not begin to execute code until a valid clock source has been released to the system. Therefore, the oscillator and PLL start-up delays must be considered when the Reset delay time must be known.

#### 6.2.2 FAIL-SAFE CLOCK MONITOR (FSCM) AND DEVICE RESETS

If the FSCM is enabled, it begins to monitor the system clock source when SYSRST is released. If a valid clock source is not available at this time, the device automatically switches to the FRC oscillator and the user can switch to the desired crystal oscillator in the Trap Service Routine.

#### 6.2.2.1 FSCM Delay for Crystal and PLL Clock Sources

When the system clock source is provided by a crystal oscillator and/or the PLL, a small delay, TFSCM, is automatically inserted after the POR and PWRT delay times. The FSCM does not begin to monitor the system clock source until this delay expires. The FSCM delay time is nominally 500  $\mu$ s and provides additional time for the oscillator and/or PLL to stabilize. In most cases, the FSCM delay prevents an oscillator failure trap at a device Reset when the PWRT is disabled.

### 6.3 Special Function Register Reset States

Most of the Special Function Registers (SFRs) associated with the CPU and peripherals are reset to a particular value at a device Reset. The SFRs are grouped by their peripheral or CPU function and their Reset values are specified in each section of this manual.

The Reset value for each SFR does not depend on the type of Reset, with the exception of two registers. The Reset value for the Reset Control register, RCON, depends on the type of device Reset. The Reset value for the Oscillator Control register, OSCCON, depends on the type of Reset and the programmed values of the oscillator Configuration bits in the FOSC Configuration register.

### REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1 (CONTINUED)

- bit 3 CNIF: Input Change Notification Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 2 Unimplemented: Read as '0'

- bit 1 MI2C1IF: I2C1 Master Events Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 SI2C1IF: I2C1 Slave Events Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

### REGISTER 7-12: IEC2: INTERRUPT ENABLE CONTROL REGISTER 2 (CONTINUED)

- bit 2 C1RXIE: ECAN1 Receive Data Ready Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

- bit 1 SPI2IE: SPI2 Event Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

- bit 0 SPI2EIE: SPI2 Error Interrupt Enable bit

- 1 = Interrupt request enabled

- 0 = Interrupt request not enabled

| REGISTER 7-18: IPC3: INTERRUPT PRIORITY CONTROL REGISTER 3 | <b>REGISTER 7-18:</b> |

|------------------------------------------------------------|-----------------------|

|------------------------------------------------------------|-----------------------|

| U-0              | U-0                                                                                                                                  | U-0                                                                                                                                                                                                | U-0                                                                      | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------|-----------------|-----------------|-------|--|--|--|

| _                | _                                                                                                                                    | —                                                                                                                                                                                                  |                                                                          |                  |                 | DMA1IP<2:0>     |       |  |  |  |

| pit 15           |                                                                                                                                      |                                                                                                                                                                                                    |                                                                          |                  |                 |                 | bit 8 |  |  |  |

| U-0              | R/W-1                                                                                                                                | R/W-0                                                                                                                                                                                              | R/W-0                                                                    | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |

| 0-0              | R/W-1                                                                                                                                | AD1IP<2:0>                                                                                                                                                                                         | R/VV-U                                                                   | 0-0              | FV/VV-1         | U1TXIP<2:0>     | R/W-U |  |  |  |

| <br>bit 7        |                                                                                                                                      | AD 11F \2.02                                                                                                                                                                                       |                                                                          | —                |                 | 011XIF<2.02     | bit 0 |  |  |  |

|                  |                                                                                                                                      |                                                                                                                                                                                                    |                                                                          |                  |                 |                 | Dit C |  |  |  |

| _egend:          |                                                                                                                                      |                                                                                                                                                                                                    |                                                                          |                  |                 |                 |       |  |  |  |

| R = Readab       | le bit                                                                                                                               | W = Writable I                                                                                                                                                                                     | oit                                                                      | U = Unimpler     | mented bit, rea | ad as '0'       |       |  |  |  |

| -n = Value a     | It POR                                                                                                                               | '1' = Bit is set                                                                                                                                                                                   |                                                                          | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |  |  |  |

|                  |                                                                                                                                      |                                                                                                                                                                                                    |                                                                          |                  |                 |                 |       |  |  |  |

| oit 15-11        | Unimplemen                                                                                                                           | ted: Read as 'd                                                                                                                                                                                    | )'                                                                       |                  |                 |                 |       |  |  |  |

| oit 10-8         | DMA1IP<2:0                                                                                                                           | >: DMA Channe                                                                                                                                                                                      | el 1 Data Tra                                                            | nsfer Complete   | Interrupt Prior | rity bits       |       |  |  |  |

|                  | 111 = Interru                                                                                                                        | pt is priority 7 (ł                                                                                                                                                                                | nighest priorit                                                          | y interrupt)     |                 |                 |       |  |  |  |

|                  |                                                                                                                                      |                                                                                                                                                                                                    |                                                                          |                  |                 |                 |       |  |  |  |

|                  | •                                                                                                                                    |                                                                                                                                                                                                    |                                                                          |                  |                 |                 |       |  |  |  |

|                  | •                                                                                                                                    |                                                                                                                                                                                                    |                                                                          |                  |                 |                 |       |  |  |  |

|                  | •<br>•<br>•<br>001 = Interru                                                                                                         | pt is priority 1                                                                                                                                                                                   |                                                                          |                  |                 |                 |       |  |  |  |

|                  | •<br>•<br>001 = Interru<br>000 = Interru                                                                                             | pt is priority 1<br>pt source is disa                                                                                                                                                              | abled                                                                    |                  |                 |                 |       |  |  |  |

| oit 7            | 000 = Interru                                                                                                                        |                                                                                                                                                                                                    |                                                                          |                  |                 |                 |       |  |  |  |

| bit 7<br>bit 6-4 | 000 = Interru<br>Unimplemen                                                                                                          | pt source is disa                                                                                                                                                                                  | )'                                                                       | e Interrupt Prio | rity bits       |                 |       |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>AD1IP<2:0>:                                                                                           | pt source is disanted: Read as 'o                                                                                                                                                                  | )'<br>sion Complete                                                      |                  | rity bits       |                 |       |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>AD1IP<2:0>:                                                                                           | pt source is disa<br>ited: Read as 'o<br>ADC1 Convers                                                                                                                                              | )'<br>sion Complete                                                      |                  | rity bits       |                 |       |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>AD1IP<2:0>:                                                                                           | pt source is disa<br>ited: Read as 'o<br>ADC1 Convers                                                                                                                                              | )'<br>sion Complete                                                      |                  | rity bits       |                 |       |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>AD1IP<2:0>:<br>111 = Interru<br>•<br>•                                                                | pt source is disa<br>ited: Read as 'o<br>ADC1 Convers<br>pt is priority 7 (h                                                                                                                       | )'<br>sion Complete                                                      |                  | rity bits       |                 |       |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>AD1IP<2:0>:<br>111 = Interru<br>•<br>•<br>001 = Interru                                               | pt source is disa<br>ited: Read as 'o<br>ADC1 Convers<br>pt is priority 7 (h                                                                                                                       | <sub>)</sub> '<br>sion Completi<br>nighest priorit                       |                  | rity bits       |                 |       |  |  |  |

| bit 6-4          | 000 = Interru<br>Unimplemen<br>AD1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru                                        | pt source is disa<br><b>ited:</b> Read as 'o<br>ADC1 Convers<br>pt is priority 7 (h<br>pt is priority 1                                                                                            | <sub>o</sub> '<br>sion Complete<br>nighest priorit<br>abled              |                  | rity bits       |                 |       |  |  |  |

| bit 6-4<br>bit 3 | 000 = Interru<br>Unimplemen<br>AD1IP<2:0>:<br>111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen                | pt source is disa<br><b>ited:</b> Read as 'o<br>ADC1 Convers<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa                                                                       | <sub>o</sub> '<br>sion Completa<br>nighest priorit<br>abled              | y interrupt)     | rity bits       |                 |       |  |  |  |

| bit 6-4<br>bit 3 | 000 = Interru<br>Unimplemen<br>AD1IP<2:0>:<br>111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>U1TXIP<2:0> | pt source is disa<br><b>ited:</b> Read as 'contraction<br>ADC1 Converse<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>ited:</b> Read as 'contraction                       | )'<br>sion Complete<br>nighest priorit<br>abled<br>5'<br>smitter Interru | ny interrupt)    | rity bits       |                 |       |  |  |  |

| bit 6-4<br>bit 3 | 000 = Interru<br>Unimplemen<br>AD1IP<2:0>:<br>111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>U1TXIP<2:0> | pt source is disa<br><b>ited:</b> Read as 'o<br>ADC1 Convers<br>pt is priority 7 (f<br>pt is priority 1<br>pt source is disa<br><b>ited:</b> Read as 'o<br>•: UART1 Trans                          | )'<br>sion Complete<br>nighest priorit<br>abled<br>5'<br>smitter Interru | ny interrupt)    | rity bits       |                 |       |  |  |  |

|                  | 000 = Interru<br>Unimplemen<br>AD1IP<2:0>:<br>111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>U1TXIP<2:0> | pt source is disa<br><b>ited:</b> Read as 'o<br>ADC1 Convers<br>pt is priority 7 (f<br>pt is priority 1<br>pt source is disa<br><b>ited:</b> Read as 'o<br>•: UART1 Trans                          | )'<br>sion Complete<br>nighest priorit<br>abled<br>5'<br>smitter Interru | ny interrupt)    | rity bits       |                 |       |  |  |  |

| bit 6-4<br>bit 3 | 000 = Interru<br>Unimplemen<br>AD1IP<2:0>:<br>111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>U1TXIP<2:0> | pt source is disa<br><b>ited:</b> Read as 'co<br>ADC1 Convers<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>ited:</b> Read as 'co<br>>: UART1 Trans<br>pt is priority 7 (h | )'<br>sion Complete<br>nighest priorit<br>abled<br>5'<br>smitter Interru | ny interrupt)    | rity bits       |                 |       |  |  |  |

| U-0          | R/W-1           | R/W-0                  | R/W-0          | U-0              | R/W-1           | R/W-0           | R/W-0 |

|--------------|-----------------|------------------------|----------------|------------------|-----------------|-----------------|-------|

| _            |                 | T8IP<2:0>              |                | _                |                 | MI2C2IP<2:0>    |       |

| bit 15       | ·               |                        |                | ·                |                 |                 | bit   |

|              |                 |                        |                |                  |                 |                 |       |

| U-0          | R/W-1           | R/W-0                  | R/W-0          | U-0              | R/W-1           | R/W-0           | R/W-0 |

|              |                 | SI2C2IP<2:0>           |                |                  |                 | T7IP<2:0>       |       |

| bit 7        |                 |                        |                |                  |                 |                 | bit   |

| Legend:      |                 |                        |                |                  |                 |                 |       |

| R = Readab   | le bit          | W = Writable I         | oit            | U = Unimple      | mented bit, rea | ad as '0'       |       |

| -n = Value a | t POR           | '1' = Bit is set       |                | '0' = Bit is cle | eared           | x = Bit is unkn | own   |

|              |                 |                        |                |                  |                 |                 |       |

| bit 15       | Unimplem        | ented: Read as 'o      | )'             |                  |                 |                 |       |

| bit 14-12    |                 | : Timer8 Interrupt     | 5              |                  |                 |                 |       |

|              | 111 = Inte      | rrupt is priority 7 (I | nighest priori | ity interrupt)   |                 |                 |       |

|              | •               |                        |                |                  |                 |                 |       |

|              | •               |                        |                |                  |                 |                 |       |

|              |                 | rrupt is priority 1    |                |                  |                 |                 |       |

|              |                 | rrupt source is disa   |                |                  |                 |                 |       |

| bit 11       | -               | ented: Read as 'o      |                |                  |                 |                 |       |

| bit 10-8     |                 | 2:0>: I2C2 Master      |                |                  | S               |                 |       |

|              | 111 = Inte      | rrupt is priority 7 (I | nighest priori | ity interrupt)   |                 |                 |       |

|              | •               |                        |                |                  |                 |                 |       |

|              | •               |                        |                |                  |                 |                 |       |

|              |                 | rrupt is priority 1    |                |                  |                 |                 |       |

|              |                 | rrupt source is disa   |                |                  |                 |                 |       |

| bit 7        | -               | ented: Read as 'o      |                |                  |                 |                 |       |

| bit 6-4      |                 | 2:0>: I2C2 Slave E     |                |                  |                 |                 |       |

|              | 111 = Inte      | rrupt is priority 7 (I | highest priori | ity interrupt)   |                 |                 |       |

|              | •               |                        |                |                  |                 |                 |       |

|              | •               |                        |                |                  |                 |                 |       |

|              |                 | rrupt is priority 1    |                |                  |                 |                 |       |

| L:1 0        |                 | rrupt source is disa   |                |                  |                 |                 |       |

| bit 3        | -               | ented: Read as 'o      |                |                  |                 |                 |       |

| bit 2-0      |                 | : Timer7 Interrupt     |                | ity interrupt)   |                 |                 |       |

|              | ⊥⊥⊥ = inte<br>• | rrupt is priority 7 (ł | lignest prior  | ity interrupt)   |                 |                 |       |

|              | •               |                        |                |                  |                 |                 |       |

|              | •               |                        |                |                  |                 |                 |       |

|              |                 | rrupt is priority 1    | ablad          |                  |                 |                 |       |

|              | 000 = Inte      | rrupt source is disa   | abled          |                  |                 |                 |       |

| REGISTER 8-9: DSADR: MOST RECENT DMA RAM ADDRESS |     |                  |      |                |              |                    |       |  |  |  |

|--------------------------------------------------|-----|------------------|------|----------------|--------------|--------------------|-------|--|--|--|

| R-0                                              | R-0 | R-0              | R-0  | R-0            | R-0          | R-0                | R-0   |  |  |  |

|                                                  |     |                  | DSAD | )R<15:8>       |              |                    |       |  |  |  |

| bit 15                                           |     |                  |      |                |              |                    | bit 8 |  |  |  |

| R-0                                              | R-0 | R-0              | R-0  | R-0            | R-0          | R-0                | R-0   |  |  |  |

|                                                  |     |                  | DSAI | DR<7:0>        |              |                    |       |  |  |  |

| bit 7                                            |     |                  |      |                |              |                    | bit 0 |  |  |  |

| Legend:                                          |     |                  |      |                |              |                    |       |  |  |  |

| R = Readable bit                                 |     | W = Writable bit |      | U = Unimplemen | ited bit, re | ad as '0'          |       |  |  |  |

| -n = Value at POR                                |     |                  |      |                |              | x = Bit is unknown |       |  |  |  |

bit 15-0 DSADR<15:0>: Most Recent DMA RAM Address Accessed by DMA Controller bits

### 17.0 INTER-INTEGRATED CIRCUIT™ (I<sup>2</sup>C™)

Note: This data sheet summarizes the features of the dsPIC33FJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 19. Circuit™ "Inter-Integrated (l<sup>2</sup>C<sup>™</sup>)" (DS70195) in the "dsPIC33F Family Reference Manual", which is available the Microchip from web site (www.microchip.com).

The Inter-Integrated Circuit ( $I^2C$ ) module provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard, with a 16-bit interface.

The dsPIC33FJXXXGPX06/X08/X10 devices have up to two I<sup>2</sup>C interface modules, denoted as I2C1 and I2C2. Each I<sup>2</sup>C module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each  $I^2C$  module 'x' (x = 1 or 2) offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation.

- I<sup>2</sup>C Slave mode supports 7 and 10-bit address.

- I<sup>2</sup>C Master mode supports 7 and 10-bit address.

- I<sup>2</sup>C Port allows bidirectional transfers between master and slaves.

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control).

- I<sup>2</sup>C supports multi-master operation; detects bus collision and will arbitrate accordingly.

### 17.1 Operating Modes

The hardware fully implements all the master and slave functions of the  $I^2C$  Standard and Fast mode specifications, as well as 7 and 10-bit addressing.

The I<sup>2</sup>C module can operate either as a slave or a master on an I<sup>2</sup>C bus.

The following types of  $I^2C$  operation are supported:

- I<sup>2</sup>C slave operation with 7-bit address

- I<sup>2</sup>C slave operation with 10-bit address

- I<sup>2</sup>C master operation with 7 or 10-bit address

For details about the communication sequence in each of these modes, please refer to the "*dsPIC33F Family Reference Manual*".

### 17.2 I<sup>2</sup>C Registers

I2CxCON and I2CxSTAT are control and status registers, respectively. The I2CxCON register is readable and writable. The lower six bits of I2CxSTAT are read-only. The remaining bits of the I2CSTAT are read/write.

I2CxRSR is the shift register used for shifting data, whereas I2CxRCV is the buffer register to which data bytes are written, or from which data bytes are read. I2CxRCV is the receive buffer. I2CxTRN is the transmit register to which bytes are written during a transmit operation.

The I2CxADD register holds the slave address. A status bit, ADD10, indicates 10-bit Address mode. The I2CxBRG acts as the Baud Rate Generator (BRG) reload value.

In receive operations, I2CxRSR and I2CxRCV together form a double-buffered receiver. When I2CxRSR receives a complete byte, it is transferred to I2CxRCV and an interrupt pulse is generated.

| REGISTER 1                                                                 | 7-3: I2CxN | ISK: I2Cx SL | AVE MODE |              | MASK REGIS       | TER      |       |

|----------------------------------------------------------------------------|------------|--------------|----------|--------------|------------------|----------|-------|

| U-0                                                                        | U-0        | U-0          | U-0      | U-0          | U-0              | R/W-0    | R/W-0 |

|                                                                            |            |              | _        |              | —                | AMSK9    | AMSK8 |

| bit 15                                                                     |            |              |          |              |                  |          | bit 8 |

| R/W-0                                                                      | R/W-0      | R/W-0        | R/W-0    | R/W-0        | R/W-0            | R/W-0    | R/W-0 |

| AMSK7                                                                      | AMSK6      | AMSK5        | AMSK4    | AMSK3        | AMSK2            | AMSK1    | AMSK0 |

| bit 7                                                                      |            |              |          |              |                  |          | bit 0 |

| Legend:                                                                    |            |              |          |              |                  |          |       |

| R = Readable                                                               | bit        | W = Writable | bit      | U = Unimpler | mented bit, read | d as '0' |       |

| -n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |            |              | nown     |              |                  |          |       |

bit 15-10 Unimplemented: Read as '0'

bit 9-0 AMSKx: Mask for Address bit x Select bit

1 = Enable masking for bit x of incoming message address; bit match not required in this position

0 = Disable masking for bit x; bit match required in this position

| REGISTER 1      | 18-2: UxSTA                                                                                                                                  | A: UARTx STA                                                                                                                                         | TUS AND                                                             | CONTROL R                                                     | EGISTER                             |                    |                |

|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------------------------------------------------------------|-------------------------------------|--------------------|----------------|

| R/W-0           | R/W-0                                                                                                                                        | R/W-0                                                                                                                                                | U-0                                                                 | R/W-0 HC                                                      | R/W-0                               | R-0                | R-1            |

| UTXISEL1        | UTXINV                                                                                                                                       | UTXISEL0                                                                                                                                             |                                                                     | UTXBRK                                                        | UTXEN <sup>(1)</sup>                | UTXBF              | TRMT           |

| bit 15          |                                                                                                                                              |                                                                                                                                                      |                                                                     |                                                               |                                     |                    | bit 8          |

| R/W-0           | R/W-0                                                                                                                                        | R/W-0                                                                                                                                                | R-1                                                                 | R-0                                                           | R-0                                 | R/C-0              | R-0            |

|                 | EL<1:0>                                                                                                                                      | ADDEN                                                                                                                                                | RIDLE                                                               | PERR                                                          | FERR                                | OERR               | URXDA          |

| bit 7           |                                                                                                                                              |                                                                                                                                                      |                                                                     |                                                               |                                     |                    | bit C          |

| Logondi         |                                                                                                                                              |                                                                                                                                                      |                                                                     |                                                               |                                     |                    |                |

| Legend:         | . L. 14                                                                                                                                      | HC = Hardwar                                                                                                                                         |                                                                     |                                                               | mented bit mee                      |                    |                |

| R = Readable    |                                                                                                                                              | W = Writable k                                                                                                                                       | DIT                                                                 | -                                                             | mented bit, read                    |                    |                |

| -n = Value at I | POR                                                                                                                                          | '1' = Bit is set                                                                                                                                     |                                                                     | '0' = Bit is cle                                              | ared                                | x = Bit is unkı    | nown           |

| bit 15,13       | <ul> <li>11 = Reserve</li> <li>10 = Interrupt</li> <li>transmit</li> <li>01 = Interrupt</li> <li>operatio</li> <li>00 = Interrupt</li> </ul> | D>: Transmissioned; do not use<br>t when a charact<br>buffer become<br>t when the last of<br>t when a charact<br>t when a charact<br>one character o | ter is transfe<br>s empty<br>character is s<br>ed<br>ter is transfe | erred to the Trais<br>shifted out of th<br>erred to the Trais | nsmit Shift Regi<br>e Transmit Shif | t Register; all tr | ansmit         |

| bit 14          |                                                                                                                                              | nsmit Polarity In                                                                                                                                    |                                                                     | ansmit buller)                                                |                                     |                    |                |

|                 |                                                                                                                                              |                                                                                                                                                      |                                                                     |                                                               |                                     |                    |                |

| bit 12          |                                                                                                                                              | ted: Read as 'o                                                                                                                                      |                                                                     |                                                               |                                     |                    |                |

| bit 11          | -                                                                                                                                            | ansmit Break bit                                                                                                                                     |                                                                     |                                                               |                                     |                    |                |

|                 | 1 = Send Syn<br>cleared b<br>0 = Sync Bre                                                                                                    | nc Break on new<br>by hardware upo<br>eak transmissior                                                                                               | t transmission<br>on completion<br>n disabled or                    | n                                                             | llowed by twelve                    | e '0' bits, follow | ed by Stop bit |

| bit 10          | 1 = Transmit                                                                                                                                 | ismit Enable bit<br>enabled, UxTX<br>disabled, any p                                                                                                 | pin controlle                                                       |                                                               | rted and buffer                     | is reset. UxTX     | pin controlled |

| bit 9           | 1 = Transmit                                                                                                                                 | smit Buffer Full<br>buffer is full<br>buffer is not ful                                                                                              |                                                                     |                                                               | er can be writte                    | n                  |                |

| bit 8           | 1 = Transmit                                                                                                                                 | mit Shift Registe<br>Shift Register is<br>Shift Register i                                                                                           | empty and t                                                         | ransmit buffer is                                             |                                     |                    | as completed   |

| bit 7-6         | 11 = Interrupt<br>10 = Interrupt<br>0x = Interrupt                                                                                           | <b>0&gt;:</b> Receive Intention<br>t is set on UxRS<br>t is set on UxRS<br>t is set when ar<br>Receive buffer h                                      | R transfer m<br>R transfer m<br>y character                         | naking the rece<br>naking the rece<br>is received and         | ive buffer 3/4 fu                   | ll (i.e., has 3 da | ata characters |

# **Note 1:** Refer to **Section 17. "UART"** (DS70188) in the *"dsPIC33F Family Reference Manual"* for information on enabling the UART module for transmit operation.

| R/W-0         | R/W-0                                                                                              | R/W-0                                                                                                                   | U-0         | U-0              | U-0             | U-0             | U-0   |

|---------------|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-------------|------------------|-----------------|-----------------|-------|

| -             | DMABS<2:0>                                                                                         |                                                                                                                         | _           | _                | _               | _               | _     |

| bit 15        |                                                                                                    |                                                                                                                         |             |                  |                 |                 | bit 8 |

|               |                                                                                                    |                                                                                                                         |             |                  |                 |                 |       |

| U-0           | U-0                                                                                                | U-0                                                                                                                     | R/W-0       | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

| _             |                                                                                                    | —                                                                                                                       |             |                  | FSA<4:0>        |                 |       |

| bit 7         |                                                                                                    |                                                                                                                         |             |                  |                 |                 | bit 0 |

| Legend:       |                                                                                                    |                                                                                                                         |             |                  |                 |                 |       |

| R = Readabl   | le bit                                                                                             | W = Writable t                                                                                                          | bit         | U = Unimpler     | nented bit, rea | ad as '0'       |       |

| -n = Value at | t POR                                                                                              | '1' = Bit is set                                                                                                        |             | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

| bit 12-5      | 101 = 24 buff<br>100 = 16 buff<br>011 = 12 buff<br>010 = 8 buffe<br>001 = 6 buffe<br>000 = 4 buffe | ers in DMA RAI<br>ers in DMA RAI<br>ers in DMA RAI<br>ers in DMA RAI<br>rs in DMA RAM<br>rs in DMA RAM<br>rs in DMA RAM | M<br>M<br>M |                  |                 |                 |       |

| bit 4-0       | =                                                                                                  | 30 buffer<br>31 buffer                                                                                                  |             | bits             |                 |                 |       |

|                  | —<br>R/W-0<br>1:0>               | —<br>R/W-0                           |            | R/W-0<br>BRF     |                  | R/W-0           | bit a |

|------------------|----------------------------------|--------------------------------------|------------|------------------|------------------|-----------------|-------|

| R/W-0<br>SJW<    | -                                | R/W-0                                | R/W-0      | -                | -                | R/W-0           |       |

| SJW<             | -                                | R/W-0                                | R/W-0      | -                | -                | R/W-0           | R/W-0 |

|                  | 1:0>                             |                                      |            | BRF              | P<5:0>           |                 |       |

| bit 7            |                                  |                                      |            |                  |                  |                 |       |

|                  |                                  |                                      |            |                  |                  |                 | bit   |

|                  |                                  |                                      |            |                  |                  |                 |       |

| Legend:          |                                  |                                      |            |                  |                  |                 |       |

| R = Readable b   | oit                              | W = Writable I                       | oit        | U = Unimpler     | mented bit, read | d as '0'        |       |

| -n = Value at PO | OR                               | '1' = Bit is set                     |            | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|                  |                                  |                                      |            |                  |                  |                 |       |

| bit 15-8         | Unimplement                      | ted: Read as 'o                      | )'         |                  |                  |                 |       |

| bit 7-6          | SJW<1:0>: S                      | ynchronization                       | Jump Width | bits             |                  |                 |       |

|                  | 11 = Length is                   |                                      |            |                  |                  |                 |       |

|                  | 10 = Length is                   |                                      |            |                  |                  |                 |       |

|                  | 01 = Length is<br>00 = Length is |                                      |            |                  |                  |                 |       |

|                  | •                                | aud Rate Pres                        | color bite |                  |                  |                 |       |

|                  |                                  | $Q = 2 \times 64 \times 1/F$         |            |                  |                  |                 |       |

|                  | •                                | J = Z X 04 X 1/1                     | CAN        |                  |                  |                 |       |

|                  | •                                |                                      |            |                  |                  |                 |       |

|                  | •                                |                                      |            |                  |                  |                 |       |

|                  |                                  | 2 = 2 x 3 x 1/Fo<br>2 = 2 x 2 x 1/Fo |            |                  |                  |                 |       |

00 0000 = TQ = 2 x 1 x 1/FCAN

| R/W-0           | U-0                    | R/W-0                                    | U-0             | R/W-0            | R/W-0              | R/W-0             | R/W-0       |

|-----------------|------------------------|------------------------------------------|-----------------|------------------|--------------------|-------------------|-------------|

| DCIEN           |                        | DCISIDL                                  | _               | DLOOP            | CSCKD              | CSCKE             | COFSD       |

| bit 15          |                        |                                          |                 |                  |                    |                   | bit 8       |

|                 |                        |                                          |                 |                  |                    |                   |             |

| R/W-0           | R/W-0                  | R/W-0                                    | U-0             | U-0              | U-0                | R/W-0             | R/W-0       |

| UNFM            | CSDOM                  | DJST                                     | _               | <u> </u>         |                    | COFS              | V<1:0>      |

| bit 7           |                        |                                          |                 |                  |                    |                   | bit C       |

| Legend:         |                        |                                          |                 |                  |                    |                   |             |

| R = Readable    | bit                    | W = Writable                             | bit             | U = Unimpler     | mented bit, read   | l as '0'          |             |

| -n = Value at F |                        | '1' = Bit is set                         |                 | '0' = Bit is cle |                    | x = Bit is unkr   | iown        |

|                 | -                      |                                          |                 |                  |                    |                   |             |

| bit 15          | DCIEN: DCI             | Module Enable                            | bit             |                  |                    |                   |             |

|                 | 1 = Module is          |                                          |                 |                  |                    |                   |             |

|                 | 0 = Module is          |                                          |                 |                  |                    |                   |             |

| bit 14          | -                      | ted: Read as '                           |                 |                  |                    |                   |             |

| bit 13          |                        | Stop in Idle C                           |                 |                  |                    |                   |             |

|                 |                        | rill halt in CPU I<br>rill continue to c |                 | U Idle mode      |                    |                   |             |

| bit 12          |                        | ted: Read as '                           | -               |                  |                    |                   |             |

| bit 11          | •                      | tal Loopback M                           |                 | bit              |                    |                   |             |

|                 | Ũ                      | •                                        |                 |                  | pins internally of | connected         |             |

|                 | 0 = Digital Lo         | opback mode is                           | s disabled      |                  |                    |                   |             |

| bit 10          |                        | nple Clock Dire                          |                 |                  |                    |                   |             |

|                 |                        | n is an input wh                         |                 |                  |                    |                   |             |

| bit 9           | •                      | n is an output w<br>hple Clock Edge      |                 | ule is enabled   |                    |                   |             |

| DIL 9           |                        |                                          |                 | dae sampled o    | on serial clock ri | sina edae         |             |

|                 |                        |                                          |                 |                  | n serial clock fa  |                   |             |

| bit 8           | COFSD: Frar            | ne Synchroniza                           | ation Direction | n Control bit    |                    |                   |             |

|                 | •                      | n is an input wh                         |                 |                  |                    |                   |             |

|                 | -                      | n is an output w                         | hen DCI moo     | dule is enabled  |                    |                   |             |

| bit 7           |                        | rflow Mode bit                           |                 |                  |                    |                   |             |

|                 |                        | iast value writte                        |                 | smit registers o | n a transmit und   | demow             |             |

| bit 6           |                        | ial Data Output                          |                 |                  |                    |                   |             |

|                 |                        |                                          |                 | abled transmit t | ime slots          |                   |             |

|                 |                        |                                          |                 | transmit time s  |                    |                   |             |

| bit 5           |                        | ata Justification                        |                 |                  |                    |                   |             |

|                 |                        |                                          | otion is begur  | n during the sar | ne serial clock o  | cycle as the frai | me          |

|                 |                        | ization pulse<br>smission/recer          | ntion is begur  | one serial clo   | ck cycle after fra | ame synchroniz    | ation pulse |

| bit 4-2         |                        | ted: Read as '                           | •               |                  |                    |                   |             |

| bit 1-0         | -                      | -: Frame Sync                            |                 |                  |                    |                   |             |

|                 | 11 = 20-bit A          | -                                        |                 |                  |                    |                   |             |

|                 | 10 = 16-bit A          |                                          |                 |                  |                    |                   |             |

|                 | $01 = 1^{\circ}S$ Fran | ne Sync mode                             |                 |                  |                    |                   |             |

### REGISTER 20-1: DCICON1: DCI CONTROL REGISTER 1

### TABLE 23-2: INSTRUCTION SET OVERVIEW

| Base<br>Instr<br># | Assembly<br>Mnemonic |              | Assembly Syntax | Description                              | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|--------------|-----------------|------------------------------------------|---------------|----------------|--------------------------|

| 1                  | ADD                  | ADD          | Acc             | Add Accumulators                         | 1             | 1              | OA,OB,SA,SB              |

|                    |                      | ADD          | f               | f = f + WREG                             | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD          | f,WREG          | WREG = f + WREG                          | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD          | #lit10,Wn       | Wd = lit10 + Wd                          | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD          | Wb,Ws,Wd        | Wd = Wb + Ws                             | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD          | Wb,#lit5,Wd     | Wd = Wb + lit5                           | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD          | Wso,#Slit4,Acc  | 16-bit Signed Add to Accumulator         | 1             | 1              | OA,OB,SA,SB              |

| 2                  | ADDC                 | ADDC         | f               | f = f + WREG + (C)                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADDC         | f,WREG          | WREG = $f + WREG + (C)$                  | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADDC         | #lit10,Wn       | Wd = lit10 + Wd + (C)                    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADDC         | Wb,Ws,Wd        | Wd = Wb + Ws + (C)                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADDC         | Wb,#lit5,Wd     | Wd = Wb + lit5 + (C)                     | 1             | 1              | C,DC,N,OV,Z              |

| 3                  | AND                  | AND          | f               | f = f .AND. WREG                         | 1             | 1              | N,Z                      |

|                    |                      | AND          | f,WREG          | WREG = f .AND. WREG                      | 1             | 1              | N,Z                      |

|                    |                      | AND          | #lit10,Wn       | Wd = lit10 .AND. Wd                      | 1             | 1              | N,Z                      |

|                    |                      | AND          | Wb,Ws,Wd        | Wd = Wb .AND. Ws                         | 1             | 1              | N,Z                      |

|                    |                      | AND          | Wb,#lit5,Wd     | Wd = Wb .AND. lit5                       | 1             | 1              | N,Z                      |

| 4                  | ASR                  | ASR          | f               | f = Arithmetic Right Shift f             | 1             | 1              | C,N,OV,Z                 |

|                    |                      | ASR          | f,WREG          | WREG = Arithmetic Right Shift f          | 1             | 1              | C,N,OV,Z                 |

|                    |                      | ASR          | Ws,Wd           | Wd = Arithmetic Right Shift Ws           | 1             | 1              | C,N,OV,Z                 |

|                    |                      | ASR          | Wb,Wns,Wnd      | Wnd = Arithmetic Right Shift Wb by Wns   | 1             | 1              | N,Z                      |

|                    |                      | ASR          | Wb,#lit5,Wnd    | Wnd = Arithmetic Right Shift Wb by lit5  | 1             | 1              | N,Z                      |

| 5                  | BCLR                 | BCLR         | f,#bit4         | Bit Clear f                              | 1             | 1              | None                     |

| -                  |                      | BCLR         | Ws,#bit4        | Bit Clear Ws                             | 1             | 1              | None                     |

| 6                  | BRA                  | BRA          | C,Expr          | Branch if Carry                          | 1             | 1 (2)          | None                     |

|                    |                      | BRA          | GE, Expr        | Branch if greater than or equal          | 1             | 1 (2)          | None                     |

|                    |                      | BRA          | GEU, Expr       | Branch if unsigned greater than or equal | 1             | 1 (2)          | None                     |

|                    |                      | BRA          | GT, Expr        | Branch if greater than                   | 1             | 1 (2)          | None                     |

|                    |                      | BRA          | GTU, Expr       | Branch if unsigned greater than          | 1             | 1 (2)          | None                     |

|                    |                      | BRA          | LE,Expr         | Branch if less than or equal             | 1             | 1 (2)          | None                     |

|                    |                      | BRA          | LEU,Expr        | Branch if unsigned less than or equal    | 1             | 1 (2)          | None                     |

|                    |                      | BRA          | LT, Expr        | Branch if less than                      | 1             | 1 (2)          | None                     |

|                    |                      | BRA          | LTU, Expr       | Branch if unsigned less than             | 1             | 1 (2)          | None                     |

|                    |                      | BRA          | N,Expr          | Branch if Negative                       | 1             | 1 (2)          | None                     |

|                    |                      | BRA          | NC, Expr        | Branch if Not Carry                      | 1             | 1 (2)          | None                     |

|                    |                      | BRA          | NN, Expr        | Branch if Not Negative                   | 1             | 1 (2)          | None                     |

|                    |                      | BRA          | NOV, Expr       | Branch if Not Overflow                   | 1             | 1 (2)          | None                     |

|                    |                      | BRA          | NZ,Expr         | Branch if Not Zero                       | 1             | 1 (2)          | None                     |

|                    |                      | BRA          | OA, Expr        | Branch if Accumulator A overflow         | 1             | 1 (2)          | None                     |

|                    |                      | BRA          | OB, Expr        | Branch if Accumulator B overflow         | 1             | 1 (2)          | None                     |

|                    |                      | BRA          | OV,Expr         | Branch if Overflow                       | 1             | 1 (2)          | None                     |

|                    |                      | BRA          | SA, Expr        | Branch if Accumulator A saturated        | 1             | 1 (2)          | None                     |

|                    |                      | BRA          | SB, Expr        | Branch if Accumulator B saturated        | 1             | 1 (2)          | None                     |

|                    |                      | BRA          | -               | Branch Unconditionally                   | 1             | 2              | None                     |

|                    |                      |              | Expr<br>Z Expr  | Branch if Zero                           | 1             | 1 (2)          | None                     |

|                    |                      | BRA<br>BRA   | Z,Expr          | Computed Branch                          | 1             | 2              | None                     |

| 7                  | BSET                 |              | Wn<br>f #bit4   | Bit Set f                                | 1             | 1              | None                     |

| '                  | Taca                 | BSET         | f,#bit4         |                                          | 1             | 1              |                          |

| 8                  | DCW                  | BSET         | Ws,#bit4        | Bit Set Ws                               |               |                | None                     |

| 8                  | BSW                  | BSW.C        | Ws,Wb           | Write C bit to Ws <wb></wb>              | 1             | 1              | None                     |

|                    | BTG                  | BSW.Z<br>BTG | Ws,Wb           | Write Z bit to Ws <wb></wb>              | 1             | 1              | None                     |

| 9                  |                      | 0.00         | f,#bit4         | Bit Toggle f                             | 1             | 1              | None                     |

### TABLE 25-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARACT       | ERISTICS                  |     | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |       |      |         |  |

|------------------|---------------------------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|---------|--|

| Parameter<br>No. | Typical <sup>(1)</sup>    | Мах | Units Conditions                                                                                                                                |       |      |         |  |

| Operating Cur    | rent (IDD) <sup>(2)</sup> |     |                                                                                                                                                 | -     |      |         |  |

| DC20d            | 27                        | 30  | mA                                                                                                                                              | -40°C |      |         |  |

| DC20a            | 27                        | 30  | mA                                                                                                                                              | +25°C | 3.3V | 10 MIPS |  |

| DC20b            | 27                        | 30  | mA                                                                                                                                              | +85°C |      |         |  |