Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Detuns                     |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 256КВ (256К х 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 18x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

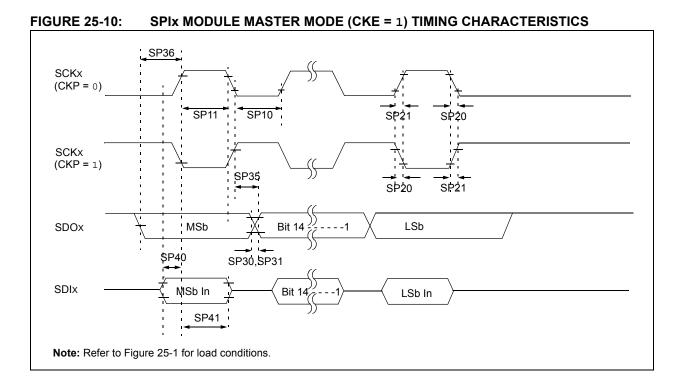

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj256gp506-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

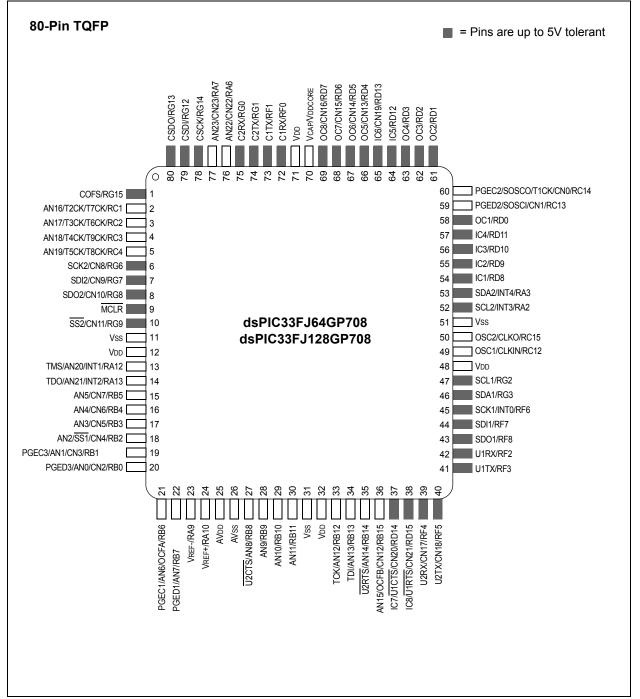

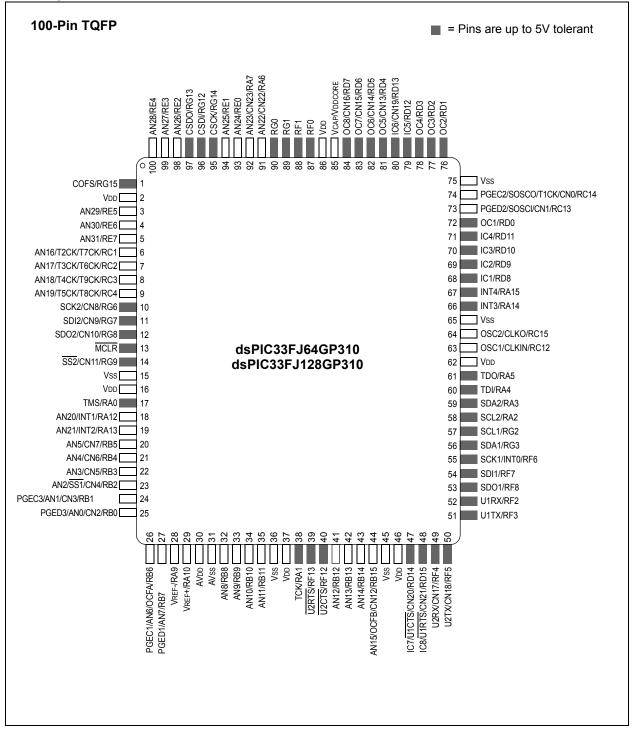

### Pin Diagrams (Continued)

#### Pin Diagrams (Continued)

| TABLE 1-1:   | Pin     | Buffer       | CRIPTIONS (CONTINUED)                                          |  |  |  |  |  |  |

|--------------|---------|--------------|----------------------------------------------------------------|--|--|--|--|--|--|

| Pin Name     | Туре    | Туре         | Description                                                    |  |  |  |  |  |  |

| RG0-RG3      | I/O     | ST           | PORTG is a bidirectional I/O port.                             |  |  |  |  |  |  |

| RG6-RG9      | I/O     | ST           |                                                                |  |  |  |  |  |  |

| RG12-RG15    | I/O     | ST           |                                                                |  |  |  |  |  |  |

| SCK1         | I/O     | ST           | Synchronous serial clock input/output for SPI1.                |  |  |  |  |  |  |

| SDI1         | I       | ST           | SPI1 data in.                                                  |  |  |  |  |  |  |

| SDO1         | 0       |              | SPI1 data out.                                                 |  |  |  |  |  |  |

| SS1          | I/O     | ST           | SPI1 slave synchronization or frame pulse I/O.                 |  |  |  |  |  |  |

| SCK2         | I/O     | ST           | Synchronous serial clock input/output for SPI2.                |  |  |  |  |  |  |

| SDI2         | I       | ST           | SPI2 data in.                                                  |  |  |  |  |  |  |

| SDO2         | 0       |              | SPI2 data out.                                                 |  |  |  |  |  |  |

| SS2          | I/O     | ST           | SPI2 slave synchronization or frame pulse I/O.                 |  |  |  |  |  |  |

| SCL1         | I/O     | ST           | Synchronous serial clock input/output for I2C1.                |  |  |  |  |  |  |

| SDA1         | I/O     | ST           | Synchronous serial data input/output for I2C1.                 |  |  |  |  |  |  |

| SCL2         | I/O     | ST           | Synchronous serial clock input/output for I2C2.                |  |  |  |  |  |  |

| SDA2         | I/O     | ST           | Synchronous serial data input/output for I2C2.                 |  |  |  |  |  |  |

| SOSCI        | I       | ST/CMOS      | 32.768 kHz low-power oscillator crystal input; CMOS otherwise. |  |  |  |  |  |  |

| SOSCO        | 0       | —            | 32.768 kHz low-power oscillator crystal output.                |  |  |  |  |  |  |

| TMS          | I       | ST           | JTAG Test mode select pin.                                     |  |  |  |  |  |  |

| ТСК          | I       | ST           | JTAG test clock input pin.                                     |  |  |  |  |  |  |

| TDI          | I I     | ST           | JTAG test data input pin.                                      |  |  |  |  |  |  |

| TDO          | 0       | —            | JTAG test data output pin.                                     |  |  |  |  |  |  |

| T1CK         | I       | ST           | Timer1 external clock input.                                   |  |  |  |  |  |  |

| T2CK         | I       | ST           | Timer2 external clock input.                                   |  |  |  |  |  |  |

| T3CK         | I       | ST           | Timer3 external clock input.                                   |  |  |  |  |  |  |

| T4CK         | I       | ST           | Timer4 external clock input.                                   |  |  |  |  |  |  |

| T5CK         | I       | ST           | Timer5 external clock input.                                   |  |  |  |  |  |  |

| T6CK         | I       | ST           | Timer6 external clock input.                                   |  |  |  |  |  |  |

| T7CK         | I       | ST           | Timer7 external clock input.                                   |  |  |  |  |  |  |

| T8CK         |         | ST           | Timer8 external clock input.                                   |  |  |  |  |  |  |

| T9CK         |         | ST           | Timer9 external clock input.                                   |  |  |  |  |  |  |

| U1CTS        | I       | ST           | UART1 clear to send.                                           |  |  |  |  |  |  |

| U1RTS        | 0       | _            | UART1 ready to send.                                           |  |  |  |  |  |  |

| U1RX         |         | ST           | UART1 receive.                                                 |  |  |  |  |  |  |

| U1TX         | 0       | -            | UART1 transmit.                                                |  |  |  |  |  |  |

| U2CTS        |         | ST           | UART2 clear to send.                                           |  |  |  |  |  |  |

| U2RTS        | 0       | -            | UART2 ready to send.                                           |  |  |  |  |  |  |

| U2RX         | I       | ST           | UART2 receive.                                                 |  |  |  |  |  |  |

| U2TX         | 0       | _            | UART2 transmit.                                                |  |  |  |  |  |  |

| VDD          | P       | —            | Positive supply for peripheral logic and I/O pins.             |  |  |  |  |  |  |

| VCAP/VDDCORE | Р       | —            | CPU logic filter capacitor connection.                         |  |  |  |  |  |  |

| Vss          | Р       |              | Ground reference for logic and I/O pins.                       |  |  |  |  |  |  |

| VREF+        |         | Analog       | Analog voltage reference (high) input.                         |  |  |  |  |  |  |

| VREF-        |         | Analog       | Analog voltage reference (low) input.                          |  |  |  |  |  |  |

| Legend: CMO  | S = CMO | S compatible | e input or output; Analog = Analog input; P = Power            |  |  |  |  |  |  |

#### **TABLE 1-1:** PINOUT I/O DESCRIPTIONS (CONTINUED)

**Legend:** CMOS = CMOS compatible input or output; ST = Schmitt Trigger input with CMOS levels;

Analog = Analog input; P = Power O = Output;

I = Input

#### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 2, MPLAB ICD 3, or MPLAB REAL ICE<sup>™</sup>.

For more information on ICD 2, ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip website.

- "MPLAB<sup>®</sup> ICD 2 In-Circuit Debugger User's Guide" DS51331

- *"Using MPLAB<sup>®</sup> ICD 2"* (poster) DS51265

- *"MPLAB<sup>®</sup> ICD 2 Design Advisory"* DS51566

- "Using MPLAB<sup>®</sup> ICD 3 In-Circuit Debugger" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- *"MPLAB<sup>®</sup> REAL ICE™ In-Circuit Emulator User's Guide"* DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™" (poster) DS51749

### 2.6 External Oscillator Pins

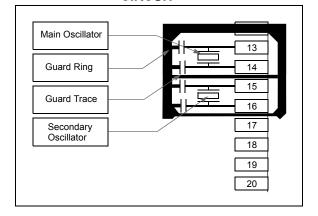

Many DSCs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 9.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

### FIGURE 2-3: S

#### SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

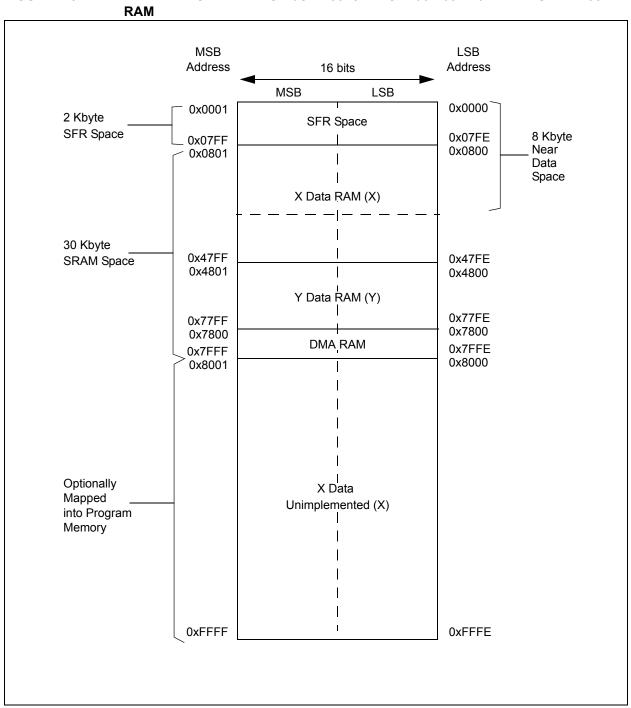

#### FIGURE 4-5: DATA MEMORY MAP FOR dsPIC33FJXXXGPX06/X08/X10 DEVICES WITH 30 KB

### TABLE 4-5: INTERRUPT CONTROLLER REGISTER MAP

| Name         Adar         Bit 1         Bit 1         Bit 1         Bit 7         Bit 7 | IADLE 4 | +-J. |        | INNUF I |            | NOLLLI   | KEGISI  |        |            | -      |          |         | -           | -                    |           |               |            |               |               |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|--------|---------|------------|----------|---------|--------|------------|--------|----------|---------|-------------|----------------------|-----------|---------------|------------|---------------|---------------|

| INTCON2     0082     ALTIVT     DISI     —     —     —     —     —     —     —     —     —     —     —     —     —     —     —     —     —     —     —     —     —     —     —     —     —     —     —     —     Intep                                                                                                                                                                                                                |         |      | Bit 15 | Bit 14  | Bit 13     | Bit 12   | Bit 11  | Bit 10 | Bit 9      | Bit 8  | Bit 7    | Bit 6   | Bit 5       | Bit 4                | Bit 3     | Bit 2         | Bit 1      | Bit 0         | All<br>Resets |

| IFS0       0084       —       DMA1IF       AD1F       UITXJF       UIRXIF       SPI1FF       SPI1FF       T3JF       T2JF       OC2F       IC2JF       DMA0IF       T1JF       OC1IF       IC1IF       INT0FF       0001F         IFS1       0086       UZRXIF       INT2JF       TSF       T4JF       OC4JF       OC3FF       IC0GFF       IC0JFF       INT3JF       INT3JF       INT3JF       INT3JF       CNIFF       -       MA2CIF       SIZCJF       INT3JF       SIZCJF       INT3JF       SIZCJF       INT3JF       SIZCJF       SIZCJF       INT3JF                                                          | INTCON1 | 0080 | NSTDIS | OVAERR  | OVBERR     | COVAERR  | COVBERR | OVATE  | OVBTE      | COVTE  | SFTACERR | DIV0ERR | DMACERR     | MATHERR              | ADDRERR   | STKERR        | OSCFAIL    | _             | 0000          |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | INTCON2 | 0082 | ALTIVT | DISI    | _          | _        | _       | _      | _          | -      |          | _       | -           | INT4EP               | INT3EP    | INT2EP        | INT1EP     | INT0EP        | 0000          |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IFS0    | 0084 | —      | DMA1IF  | AD1IF      | U1TXIF   | U1RXIF  | SPI1IF | SPI1EIF    | T3IF   | T2IF     | OC2IF   | IC2IF       | DMA0IF               | T1IF      | OC1IF         | IC1IF      | <b>INT0IF</b> | 0000          |

| IFS3       008A       —       —       DMASIF       DCIF       DCIF       D       —       C2IF       C2RXIF       INTAIF       INT3F       T9IF       T8IF       MI2C2IF       SIZCIF       T7IF       0000         IFS4       008C       —       —       —       —       —       —       —       —       C2IF       C1TXIF       C1TXIF       DMA7F       DMA0IF       —       UZEF       UIEF       I       0000         IEC0       0094       —       DMA1E       AD11E       UITXIE       SPI1E       SPI1E       T3IE       T2IE       OC2IE       IC2IE       IAMAIE       CAIE       IC3IE       IAMAIE       OMA0IE       —       M2C1E       SIZCIF       T0IE       0000       ICTXE       DMA0IE       T1IE       C1IE       ICTXIE       IAMAIE       IIIE       C1IE       ICTXIE       IAMAIE                                                                                                          | IFS1    | 0086 | U2TXIF | U2RXIF  | INT2IF     | T5IF     | T4IF    | OC4IF  | OC3IF      | DMA2IF | IC8IF    | IC7IF   | AD2IF       | INT1IF               | CNIF      | _             | MI2C1IF    | SI2C1IF       | 0000          |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IFS2    | 0088 | T6IF   | DMA4IF  | _          | OC8IF    | OC7IF   | OC6IF  | OC5IF      | IC6IF  | IC5IF    | IC4IF   | IC3IF       | DMA3IF               | C1IF      | C1RXIF        | SPI2IF     | SPI2EIF       | 0000          |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IFS3    | 008A | —      | —       | DMA5IF     | DCIIF    | DCIEIF  | _      | _          | C2IF   | C2RXIF   | INT4IF  | INT3IF      | T9IF                 | T8IF      | MI2C2IF       | SI2C2IF    | T7IF          | 0000          |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IFS4    | 008C | —      | _       |            | _        | _       | _      | _          |        | C2TXIF   | C1TXIF  | DMA7IF      | DMA6IF               | —         | U2EIF         | U1EIF      | _             | 0000          |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IEC0    | 0094 | _      | DMA1IE  | AD1IE      | U1TXIE   | U1RXIE  | SPI1IE | SPI1EIE    | T3IE   | T2IE     | OC2IE   | IC2IE       | DMA0IE               | T1IE      | OC1IE         | IC1IE      | INT0IE        | 0000          |

| $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IEC1    | 0096 | U2TXIE | U2RXIE  | INT2IE     | T5IE     | T4IE    | OC4IE  | OC3IE      | DMA2IE | IC8IE    | IC7IE   | AD2IE       | INT1IE               | CNIE      |               | MI2C1IE    | SI2C1IE       | 0000          |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IEC2    | 0098 | T6IE   | DMA4IE  | _          | OC8IE    | OC7IE   | OC6IE  | OC5IE      | IC6IE  | IC5IE    | IC4IE   | IC3IE       | DMA3IE               | C1IE      | C1RXIE        | SPI2IE     | SPI2EIE       | 0000          |

| $ \begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IEC3    | 009A | _      | _       | DMA5IE     | DCIIE    | DCIEIE  | _      | _          | C2IE   | C2RXIE   | INT4IE  | INT3IE      | T9IE                 | T8IE      | MI2C2IE       | SI2C2IE    | T7IE          | 0000          |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IEC4    | 009C | —      | _       |            | _        | _       | _      | _          |        | C2TXIE   | C1TXIE  | DMA7IE      | DMA6IE               | —         | U2EIE         | U1EIE      | _             | 0000          |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IPC0    | 00A4 | —      |         | T1IP<2:0>  | >        | _       | ļ      | OC1IP<2:0  | )>     |          |         | IC1IP<2:0>  | P<2:0> — INT0IP<2:0> |           | •             | 4444       |               |               |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IPC1    | 00A6 | —      |         | T2IP<2:0>  | >        | _       | ٦      | OC2IP<2:0  | )>     |          |         | IC2IP<2:0>  |                      | —         | DMA0IP<2:0>   |            | 4444          |               |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IPC2    | 00A8 | —      | ι       | J1RXIP<2:( | 0>       | _       | :      | SPI1IP<2:0 | )>     |          | :       | SPI1EIP<2:0 | >                    | —         |               | T3IP<2:0>  |               | 4444          |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IPC3    | 00AA | —      |         |            | —        | _       | Ľ      | MA1IP<2:   | 0>     |          |         | AD1IP<2:0>  | •                    | —         | U1TXIP<2:0>   |            | >             | 0444          |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IPC4    | 00AC | —      |         | CNIP<2:0   | >        | _       |        | —          |        |          |         | MI2C1IP<2:0 | )>                   | —         | S             | 2C1IP<2:0  | >             | 4044          |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IPC5    | 00AE | —      |         | IC8IP<2:03 | >        | _       |        | IC7IP<2:0  | >      |          |         | AD2IP<2:0>  | •                    | —         | – INT1IP<2:0> |            | >             | 4444          |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IPC6    | 00B0 | —      |         | T4IP<2:0>  | >        | —       |        | OC4IP<2:0  | )>     | —        |         | OC3IP<2:0>  | >                    | —         | D             | MA2IP<2:0  | >             | 4444          |

| $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IPC7    | 00B2 | —      | ι       | J2TXIP<2:( | )>       | _       | L      | J2RXIP<2:  | 0>     |          |         | INT2IP<2:0  | >                    | —         |               | T5IP<2:0>  |               | 4444          |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IPC8    | 00B4 | —      |         | C1IP<2:0>  | >        | —       | C      | C1RXIP<2:  | 0>     | —        |         | SPI2IP<2:0  | >                    | —         | SI            | PI2EIP<2:0 | >             | 4444          |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IPC9    | 00B6 | —      |         | IC5IP<2:0  | >        | —       |        | IC4IP<2:0  | >      | —        |         | IC3IP<2:0>  |                      | —         | D             | MA3IP<2:0  | >             | 4444          |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IPC10   | 00B8 | —      |         | OC7IP<2:0  | >        | —       |        | OC6IP<2:0  | )>     | _        |         | OC5IP<2:0>  | >                    | —         |               | C6IP<2:0>  |               | 4444          |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IPC11   | 00BA | —      |         | T6IP<2:0>  | <b>`</b> | —       | C      | MA4IP<2:   | 0>     | _        | _       | _           | —                    | —         | C             | )C8IP<2:0> | •             | 4404          |

| $\begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | IPC12   | 00BC | —      |         | T8IP<2:0>  | <b>`</b> | —       | N      | 112C2IP<2: | 0>     | _        |         | SI2C2IP<2:0 | >                    | —         |               | T7IP<2:0>  |               | 4444          |

| IPC15       00C2       -       -       -       -       -       DMA5IP<2:0>       -       DCIIP<2:0>       004         IPC16       00C4       -       -       -       -       -       014       044         IPC16       00C4       -       -       -       U2EIP<2:0>       -       U1EIP<2:0>       -       044         IPC17       00C6       -       C2TXIP<2:0>       -       C1TXIP<2:0>       -       DMA7IP<2:0>       -       DMA6IP<2:0>       444                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | IPC13   | 00BE | _      | C       | 2RXIP<2:   | 0>       | _       | I      | NT4IP<2:(  | )>     | —        |         | INT3IP<2:0> | >                    | _         |               | T9IP<2:0>  |               | 4444          |

| IPC16       00C4       -       -       -       U2EIP<2:0>       -       U1EIP<2:0>       -       -       -       044         IPC17       00C6       -       C2TXIP<2:0>       -       C1TXIP<2:0>       -       DMA7IP<2:0>       -       DMA6IP<2:0>       444                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | IPC14   | 00C0 | —      | [       | DCIEIP<2:0 | )>       | _       | _      | —          | _      | _        | _       | _           | _                    | _         |               | C2IP<2:0>  |               | 4004          |

| IPC17         00C6         —         C2TXIP<2:0>         —         C1TXIP<2:0>         —         DMA6IP<2:0>         444                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | IPC15   | 00C2 | —      | —       | —          | —        | _       | _      | —          | _      | _        |         | DMA5IP<2:0  | >                    | _         | [             | OCIIP<2:0> |               | 0044          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | IPC16   | 00C4 |        | _       | —          |          | _       |        | U2EIP<2:0  | )>     | _        |         | U1EIP<2:0>  | •                    | _         | —             | —          | _             | 0440          |

| INTTREG 00E0 ILR<3:0> - VECNUM<6:0> 0000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | IPC17   | 00C6 |        | (       | C2TXIP<2:0 | )>       | _       | (      | C1TXIP<2:  | 0>     | _        |         | DMA7IP<2:0  | >                    | _         | D             | MA6IP<2:0  | >             | 4444          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | INTTREG | 00E0 |        | _       | —          |          |         | ILR<   | 3:0>       |        | _        |         |             | VE                   | CNUM<6:0> |               |            |               | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Flag Bit          | Setting Event                                        | Clearing Event               |  |  |  |  |  |  |  |  |

|-------------------|------------------------------------------------------|------------------------------|--|--|--|--|--|--|--|--|

| TRAPR (RCON<15>)  | Trap conflict event                                  | POR, BOR                     |  |  |  |  |  |  |  |  |

| IOPUWR (RCON<14>) | Illegal opcode or uninitialized<br>W register access | POR, BOR                     |  |  |  |  |  |  |  |  |

| EXTR (RCON<7>)    | MCLR Reset                                           | POR                          |  |  |  |  |  |  |  |  |

| SWR (RCON<6>)     | RESET instruction                                    | POR, BOR                     |  |  |  |  |  |  |  |  |

| WDTO (RCON<4>)    | WDT time-out                                         | PWRSAV instruction, POR, BOR |  |  |  |  |  |  |  |  |

| SLEEP (RCON<3>)   | PWRSAV #SLEEP instruction                            | POR, BOR                     |  |  |  |  |  |  |  |  |

| IDLE (RCON<2>)    | PWRSAV #IDLE instruction                             | POR, BOR                     |  |  |  |  |  |  |  |  |

| BOR (RCON<1>)     | BOR, POR                                             | —                            |  |  |  |  |  |  |  |  |

| POR (RCON<0>)     | POR                                                  | -                            |  |  |  |  |  |  |  |  |

#### TABLE 6-1:RESET FLAG BIT OPERATION

Note: All Reset flag bits may be set or cleared by the user software.

#### 6.1 Clock Source Selection at Reset

If clock switching is enabled, the system clock source at device Reset is chosen, as shown in Table 6-2. If clock switching is disabled, the system clock source is always selected according to the oscillator Configuration bits. Refer to **Section 9.0 "Oscillator Configuration"** for further details.

# TABLE 6-2:OSCILLATOR SELECTION VSTYPE OF RESET (CLOCK<br/>SWITCHING ENABLED)

| Reset Type | Clock Source Determinant      |

|------------|-------------------------------|

| POR        | Oscillator Configuration bits |

| BOR        | (FNOSC<2:0>)                  |

| MCLR       | COSC Control bits             |

| WDTR       | (OSCCON<14:12>)               |

| SWR        |                               |

#### 6.2 Device Reset Times

The Reset times for various types of device Reset are <u>summarized</u> in Table 6-3. The system Reset signal, SYSRST, is released after the POR and PWRT delay times expire.

The time at which the device actually begins to execute code also depends on the system oscillator delays, which include the Oscillator Start-up Timer (OST) and the PLL lock time. The OST and PLL lock times occur in parallel with the applicable SYSRST delay times.

The FSCM delay determines the time at which the FSCM begins to monitor the system clock source after the SYSRST signal is released.

| REGISTER 7      | '-7: IFS2:                                                                                     | INTERRUPT                                                 | FLAG STAT         | US REGIS       | TER   | 2               |      |               |         |  |  |  |

|-----------------|------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-------------------|----------------|-------|-----------------|------|---------------|---------|--|--|--|

| R/W-0           | R/W-0                                                                                          | U-0                                                       | R/W-0             | R/W-0          |       | R/W-0           |      | R/W-0         | R/W-0   |  |  |  |

| T6IF            | DMA4IF                                                                                         |                                                           | OC8IF             | OC7IF          |       | OC6IF           |      | OC5IF         | IC6IF   |  |  |  |

| bit 15          |                                                                                                |                                                           |                   |                |       |                 |      |               | bit 8   |  |  |  |

| R/W-0           | R/W-0                                                                                          | R/W-0                                                     | R/W-0             | R/W-0          |       | R/W-0           |      | R/W-0         | R/W-0   |  |  |  |

| IC5IF           | IC4IF                                                                                          | IC3IF                                                     | DMA3IF            | C1IF           |       | C1RXIF          |      | SPI2IF        | SPI2EIF |  |  |  |

| bit 7           |                                                                                                | 1                                                         | 1                 |                |       |                 |      |               | bit 0   |  |  |  |

| Legend:         |                                                                                                |                                                           |                   |                |       |                 |      |               |         |  |  |  |

| R = Readable    | bit                                                                                            | W = Writable                                              | bit               | U = Unimpl     | eme   | ented bit, read | d as | · 'O'         |         |  |  |  |

| -n = Value at I | POR                                                                                            | '1' = Bit is se                                           | t                 | '0' = Bit is c | lear  | ed              | Х    | = Bit is unkr | nown    |  |  |  |

| bit 15          | TCIE: Timore                                                                                   | Interrupt Flog                                            | Statua hit        |                |       |                 |      |               |         |  |  |  |

| bit 15          |                                                                                                | Interrupt Flag<br>request has or                          |                   |                |       |                 |      |               |         |  |  |  |

|                 |                                                                                                | request has no                                            |                   |                |       |                 |      |               |         |  |  |  |

| bit 14          | DMA4IF: DM                                                                                     | IA Channel 4 E                                            | Data Transfer C   | complete Inte  | errup | t Flag Status   | bit  |               |         |  |  |  |

|                 | •                                                                                              | request has or<br>request has no                          |                   |                |       |                 |      |               |         |  |  |  |

| bit 13          |                                                                                                | ited: Read as                                             |                   |                |       |                 |      |               |         |  |  |  |

| bit 12          | •                                                                                              |                                                           | hannel 8 Interri  | int Flag Stat  | us h  | it              |      |               |         |  |  |  |

|                 |                                                                                                | request has or                                            |                   | apt i lag otat | u3 b  |                 |      |               |         |  |  |  |

|                 |                                                                                                | request has no                                            |                   |                |       |                 |      |               |         |  |  |  |

| bit 11          | OC7IF: Outp                                                                                    | ut Compare C                                              | hannel 7 Interri  | upt Flag Stat  | us b  | it              |      |               |         |  |  |  |

|                 | •                                                                                              | request has or                                            |                   |                |       |                 |      |               |         |  |  |  |

| bit 10          | •                                                                                              | request has no                                            | hannel 6 Interri  | int Flag Stat  | us h  | it              |      |               |         |  |  |  |

|                 | -                                                                                              | request has or                                            |                   | apt i lag Otat | u3 D  |                 |      |               |         |  |  |  |

|                 |                                                                                                | request has no                                            |                   |                |       |                 |      |               |         |  |  |  |

| bit 9           | OC5IF: Outp                                                                                    | OC5IF: Output Compare Channel 5 Interrupt Flag Status bit |                   |                |       |                 |      |               |         |  |  |  |

|                 |                                                                                                | request has or                                            |                   |                |       |                 |      |               |         |  |  |  |

| hit Q           | •                                                                                              | request has no                                            |                   | Tag Status b   | :4    |                 |      |               |         |  |  |  |

| bit 8           | IC6IF: Input Capture Channel 6 Interrupt Flag Status bit<br>1 = Interrupt request has occurred |                                                           |                   |                |       |                 |      |               |         |  |  |  |

|                 |                                                                                                | request has no                                            |                   |                |       |                 |      |               |         |  |  |  |

| bit 7           | IC5IF: Input (                                                                                 | Capture Chanr                                             | nel 5 Interrupt F | lag Status b   | it    |                 |      |               |         |  |  |  |

|                 |                                                                                                | request has or                                            |                   |                |       |                 |      |               |         |  |  |  |

| hit 6           | •                                                                                              | request has no                                            |                   | lag Statua b   | ;+    |                 |      |               |         |  |  |  |

| bit 6           | -                                                                                              | request has or                                            | nel 4 Interrupt F | -lag Status D  | IL    |                 |      |               |         |  |  |  |

|                 | •                                                                                              | request has no                                            |                   |                |       |                 |      |               |         |  |  |  |

| bit 5           | IC3IF: Input (                                                                                 | Capture Chanr                                             | nel 3 Interrupt F | -lag Status b  | it    |                 |      |               |         |  |  |  |

|                 | •                                                                                              | request has or                                            |                   |                |       |                 |      |               |         |  |  |  |

| 1.11.4          | -                                                                                              | request has no                                            |                   |                |       |                 |      |               |         |  |  |  |

| bit 4           |                                                                                                |                                                           | Data Transfer C   | complete inte  | errup | t Flag Status   | DI   |               |         |  |  |  |

|                 |                                                                                                | request has or<br>request has no                          |                   |                |       |                 |      |               |         |  |  |  |

| bit 3           |                                                                                                | •                                                         | pt Flag Status    | bit            |       |                 |      |               |         |  |  |  |

|                 | 1 = Interrupt                                                                                  | request has or                                            | curred            |                |       |                 |      |               |         |  |  |  |

|                 | 0 = Interrupt                                                                                  | request has no                                            | ot occurred       |                |       |                 |      |               |         |  |  |  |

|                 |                                                                                                |                                                           |                   |                |       |                 |      |               |         |  |  |  |

### REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

NOTES:

### REGISTER 8-5: DMAxPAD: DMA CHANNEL x PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0                               | R/W-0 | R/W-0            | R/W-0          | R/W-0        | R/W-0            | R/W-0              | R/W-0 |  |

|-------------------------------------|-------|------------------|----------------|--------------|------------------|--------------------|-------|--|

|                                     |       |                  | PAD            | <15:8>       |                  |                    |       |  |

| bit 15                              |       |                  |                |              |                  |                    | bit 8 |  |

|                                     |       |                  |                |              |                  |                    |       |  |

| R/W-0                               | R/W-0 | R/W-0            | R/W-0          | R/W-0        | R/W-0            | R/W-0              | R/W-0 |  |

|                                     |       |                  | PAD            | )<7:0>       |                  |                    |       |  |

| bit 7                               |       |                  |                |              |                  |                    | bit 0 |  |

|                                     |       |                  |                |              |                  |                    |       |  |

| Legend:                             |       |                  |                |              |                  |                    |       |  |

| R = Readable bit W = Writable bit U |       |                  |                | U = Unimplen | nented bit, read | d as '0'           |       |  |

| -n = Value at POR '1' =             |       | '1' = Bit is set | ' = Bit is set |              | ared             | x = Bit is unknown |       |  |

bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

#### REGISTER 8-6: DMAxCNT: DMA CHANNEL x TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0                                                                  | U-0                                                            | U-0   | U-0   | U-0                  | U-0   | R/W-0 | R/W-0           |

|----------------------------------------------------------------------|----------------------------------------------------------------|-------|-------|----------------------|-------|-------|-----------------|

| —                                                                    | —                                                              | —     | _     | _                    | —     | CNT<  | 9:8> <b>(2)</b> |

| bit 15                                                               |                                                                |       |       |                      |       |       | bit 8           |

|                                                                      |                                                                |       |       |                      |       |       |                 |

| R/W-0                                                                | R/W-0                                                          | R/W-0 | R/W-0 | R/W-0                | R/W-0 | R/W-0 | R/W-0           |

|                                                                      |                                                                |       | CNT<  | :7:0> <sup>(2)</sup> |       |       |                 |

| bit 7                                                                |                                                                |       |       |                      |       |       | bit 0           |

|                                                                      |                                                                |       |       |                      |       |       |                 |