Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 30K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 32x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj256gp710-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### Note the following details of the code protection feature on Microchip devices:

- Microchip products meet the specification contained in their particular Microchip Data Sheet.

- Microchip believes that its family of products is one of the most secure families of its kind on the market today, when used in the intended manner and under normal conditions.

- There are dishonest and possibly illegal methods used to breach the code protection feature. All of these methods, to our knowledge, require using the Microchip products in a manner outside the operating specifications contained in Microchip's Data Sheets. Most likely, the person doing so is engaged in theft of intellectual property.

- Microchip is willing to work with the customer who is concerned about the integrity of their code.

- Neither Microchip nor any other semiconductor manufacturer can guarantee the security of their code. Code protection does not mean that we are guaranteeing the product as "unbreakable."

Code protection is constantly evolving. We at Microchip are committed to continuously improving the code protection features of our products. Attempts to break Microchip's code protection feature may be a violation of the Digital Millennium Copyright Act. If such acts allow unauthorized access to your software or other copyrighted work, you may have a right to sue for relief under that Act.

Information contained in this publication regarding device applications and the like is provided only for your convenience and may be superseded by updates. It is your responsibility to ensure that your application meets with your specifications. MICROCHIP MAKES NO REPRESENTATIONS OR WARRANTIES OF ANY KIND WHETHER EXPRESS OR IMPLIED, WRITTEN OR ORAL, STATUTORY OR OTHERWISE, RELATED TO THE INFORMATION, INCLUDING BUT NOT LIMITED TO ITS CONDITION. QUALITY, PERFORMANCE, MERCHANTABILITY OR FITNESS FOR PURPOSE. Microchip disclaims all liability arising from this information and its use. Use of Microchip devices in life support and/or safety applications is entirely at the buyer's risk, and the buyer agrees to defend, indemnify and hold harmless Microchip from any and all damages, claims, suits, or expenses resulting from such use. No licenses are conveyed, implicitly or otherwise, under any Microchip intellectual property rights.

### QUALITY MANAGEMENT SYSTEM CERTIFIED BY DNV ISO/TS 16949:2002

#### Trademarks

The Microchip name and logo, the Microchip logo, Accuron, dsPIC, KEELOQ, KEELOQ logo, MPLAB, PIC, PICmicro, PICSTART, rfPIC, SmartShunt and UNI/O are registered trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

FilterLab, Linear Active Thermistor, MXDEV, MXLAB, SEEVAL, SmartSensor and The Embedded Control Solutions Company are registered trademarks of Microchip Technology Incorporated in the U.S.A.

Analog-for-the-Digital Age, Application Maestro, CodeGuard, dsPICDEM, dsPICDEM.net, dsPICworks, dsSPEAK, ECAN, ECONOMONITOR, FanSense, In-Circuit Serial Programming, ICSP, ICEPIC, Mindi, MiWi, MPASM, MPLAB Certified logo, MPLIB, MPLINK, mTouch, nanoWatt XLP, PICkit, PICDEM, PICDEM.net, PICtail, PIC<sup>32</sup> logo, PowerCal, PowerInfo, PowerMate, PowerTool, REAL ICE, rfLAB, Select Mode, Total Endurance, TSHARC, WiperLock and ZENA are trademarks of Microchip Technology Incorporated in the U.S.A. and other countries.

$\ensuremath{\mathsf{SQTP}}$  is a service mark of Microchip Technology Incorporated in the U.S.A.

All other trademarks mentioned herein are property of their respective companies.

© 2009, Microchip Technology Incorporated, Printed in the U.S.A., All Rights Reserved.

Microchip received ISO/TS-16949:2002 certification for its worldwide headquarters, design and wafer fabrication facilities in Chandler and Tempe, Arizona; Gresham, Oregon and design centers in California and India. The Company's quality system processes and procedures are for its PIC<sup>®</sup> MCUs and dsPIC<sup>®</sup> DSCs, KEELOQ<sup>®</sup> code hopping devices, Serial EEPROMs, microperipherals, nonvolatile memory and analog products. In addition, Microchip's quality system for the design and manufacture of development systems is ISO 9001:2000 certified.

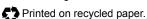

#### Pin Diagrams (Continued)

### 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT DIGITAL SIGNAL CONTROLLERS

Note: This data sheet summarizes the features of the dsPIC33FJXXXGPX06/X08/X10 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "*dsPIC33F Family Reference Manual*", which is available from the Microchip website (www.microchip.com).

### 2.1 Basic Connection Requirements

Getting started with the dsPIC33FJXXXGPX06/X08/X10 family of 16-bit Digital Signal Controllers (DSCs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used)

(see Section 2.2 "Decoupling Capacitors")

- VCAP/VDDCORE (see Section 2.3 "Capacitor on Internal Voltage Regulator (VCAP/VDDCORE)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins used when external voltage reference for ADC module is implemented

| Note: | The   | AVdd    | and   | AVss    | pins | mus | st be |

|-------|-------|---------|-------|---------|------|-----|-------|

|       | conn  | ected   | indep | endent  | of   | the | ADC   |

|       | volta | ge refe | rence | source. |      |     |       |

### 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

### TABLE 4-1: CPU CORE REGISTERS MAP (CONTINUED)

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13                | Bit 12                              | Bit 11 | Bit 10 | Bit 9                 | Bit 8            | Bit 7    | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|----------|-------------|--------|--------|-----------------------|-------------------------------------|--------|--------|-----------------------|------------------|----------|-------|-------|-------|-------|--------|--------|--------|---------------|

| XBREV    | 0050        | BREN   |        |                       |                                     |        |        |                       | 2                | XB<14:0> |       |       |       |       |        |        |        | xxxx          |

| DISICNT  | 0052        | _      | _      |                       | Disable Interrupts Counter Register |        |        |                       |                  |          |       | xxxx  |       |       |        |        |        |               |

| BSRAM    | 0750        | _      | _      | _                     | _                                   | _      | _      | —                     | _                | —        | _     | _     | _     | _     | IW_BSR | IR_BSR | RL_BSR | 0000          |

| SSRAM    | 0752        | _      | _      | —                     | _                                   | _      | _      | —                     | —                | —        | _     | _     | -     | _     | IW_SSR | IR_SSR | RL_SSR | 0000          |

| 1        |             |        | Divisi | and the second second | and a stand                         |        |        | and the second second | a tea se da a te |          |       |       |       |       |        |        |        |               |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

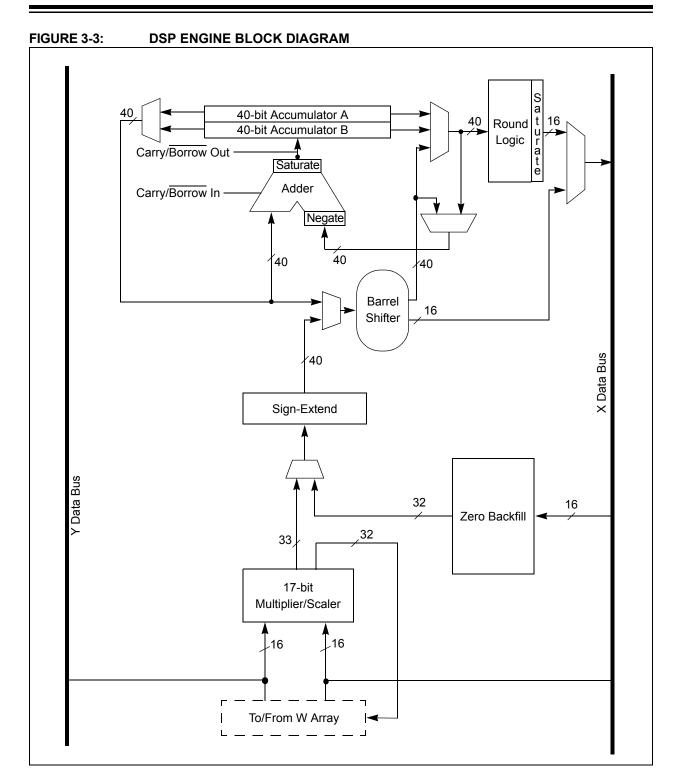

### 6.0 RESET

Note: This data sheet summarizes the features of the dsPIC33FJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Reset" (DS70192) in the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The Reset module combines all Reset sources and controls the device Master Reset Signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- · BOR: Brown-out Reset

- MCLR: Master Clear Pin Reset

- SWR: RESET Instruction

- WDT: Watchdog Timer Reset

- TRAPR: Trap Conflict Reset

- IOPUWR: Illegal Opcode and Uninitialized W Register Reset

A simplified block diagram of the Reset module is shown in Figure 6-1.

Any active source of Reset will make the SYSRST signal active. Many registers associated with the CPU and peripherals are forced to a known Reset state. Most registers are unaffected by a Reset; their status is unknown on POR and unchanged by all other Resets.

**Note:** Refer to the specific peripheral or CPU section of this manual for register Reset states.

All types of device Reset will set a corresponding status bit in the RCON register to indicate the type of Reset (see Register 6-1). A POR will clear all bits, except for the POR bit (RCON<0>), that are set. The user can set or clear any bit at any time during code execution. The RCON bits only serve as status bits. Setting a particular Reset status bit in software does not cause a device Reset to occur.

The RCON register also has other bits associated with the Watchdog Timer and device power-saving states. The function of these bits is discussed in other sections of this manual.

Note: The status bits in the RCON register should be cleared after they are read so that the next RCON register value after a device Reset will be meaningful.

#### FIGURE 6-1: RESET SYSTEM BLOCK DIAGRAM

### REGISTER 7-14: IEC4: INTERRUPT ENABLE CONTROL REGISTER 4

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| —      | —   |     |     | _   |     |     | —     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| R/W-0  | R/W-0  | R/W-0  | R/W-0  | U-0 | R/W-0 | R/W-0 | U-0   |

|--------|--------|--------|--------|-----|-------|-------|-------|

| C2TXIE | C1TXIE | DMA7IE | DMA6IE | —   | U2EIE | U1EIE | —     |

| bit 7  |        |        |        |     |       |       | bit 0 |

| Legend:      |           |                                                    |                               |                    |

|--------------|-----------|----------------------------------------------------|-------------------------------|--------------------|

| R = Readal   | ole bit   | W = Writable bit                                   | U = Unimplemented bit,        | read as '0'        |

| -n = Value a | at POR    | '1' = Bit is set                                   | '0' = Bit is cleared          | x = Bit is unknown |

|              |           |                                                    |                               |                    |

| bit 15-8     | Unimple   | emented: Read as '0'                               |                               |                    |

| bit 7        | C2TXIE    | : ECAN2 Transmit Data Requ                         | est Interrupt Enable bit      |                    |

|              |           | rrupt request enabled<br>rrupt request not enabled |                               |                    |

| bit 6        | C1TXIE    | : ECAN1 Transmit Data Requ                         | est Interrupt Enable bit      |                    |

|              |           | rrupt request enabled<br>rrupt request not enabled |                               |                    |

| bit 5        | DMA7IE    | : DMA Channel 7 Data Trans                         | fer Complete Enable Status bi | it                 |

|              |           | rrupt request enabled<br>rrupt request not enabled |                               |                    |

| bit 4        |           |                                                    | fer Complete Enable Status bi | it                 |

|              |           | rrupt request enabled<br>rrupt request not enabled |                               |                    |

| bit 3        | Unimple   | emented: Read as '0'                               |                               |                    |

| bit 2        | U2EIE:    | UART2 Error Interrupt Enable                       | bit                           |                    |

|              |           | rrupt request enabled<br>rrupt request not enabled |                               |                    |

| bit 1        | U1EIE:    | UART1 Error Interrupt Enable                       | bit                           |                    |

|              | 1 = Inter | rrupt request enabled                              |                               |                    |

|              | 0 = Inter | rrupt request not enabled                          |                               |                    |

| bit 0        | Unimple   | emented: Read as '0'                               |                               |                    |

|              |           |                                                    |                               |                    |

### REGISTER 7-16: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

| —<br>bit 15     |               |                                         |                  |                  |                 |                 |       |

|-----------------|---------------|-----------------------------------------|------------------|------------------|-----------------|-----------------|-------|

| bit 15          |               | T2IP<2:0>                               |                  | —                |                 | OC2IP<2:0>      |       |

|                 |               |                                         |                  |                  |                 |                 | bit   |

|                 |               |                                         |                  |                  |                 |                 |       |

| U-0             | R/W-1         | R/W-0                                   | R/W-0            | U-0              | R/W-1           | R/W-0           | R/W-0 |

|                 |               | IC2IP<2:0>                              |                  | —                |                 | DMA0IP<2:0>     |       |

| bit 7           |               |                                         |                  |                  |                 |                 | bit   |

| Legend:         |               |                                         |                  |                  |                 |                 |       |

| R = Readable    | bit           | W = Writable I                          | oit              | U = Unimple      | mented bit, rea | ad as '0'       |       |

| -n = Value at F | POR           | '1' = Bit is set                        |                  | '0' = Bit is cle | ared            | x = Bit is unkn | own   |

| bit 15          | Unimpleme     | nted: Read as 'o                        | )'               |                  |                 |                 |       |

| bit 14-12       | T2IP<2:0>:    | Timer2 Interrupt                        | Priority bits    |                  |                 |                 |       |

|                 | 111 = Interru | upt is priority 7 (ł                    | nighest priority | y interrupt)     |                 |                 |       |

|                 | •             |                                         |                  |                  |                 |                 |       |

|                 | •             |                                         |                  |                  |                 |                 |       |

|                 | 001 = Interru | upt is priority 1                       |                  |                  |                 |                 |       |

|                 |               | upt source is disa                      |                  |                  |                 |                 |       |

| bit 11          | Unimpleme     | nted: Read as 'o                        | )'               |                  |                 |                 |       |

| bit 10-8        |               | ·: Output Compa                         |                  | •                | ity bits        |                 |       |

|                 | 111 = Interru | upt is priority 7 (h                    | nighest priority | y interrupt)     |                 |                 |       |

|                 | •             |                                         |                  |                  |                 |                 |       |

|                 | •             |                                         |                  |                  |                 |                 |       |

|                 |               | upt is priority 1<br>upt source is disa | abled            |                  |                 |                 |       |

| bit 7           |               | nted: Read as 'o                        |                  |                  |                 |                 |       |

| bit 6-4         | IC2IP<2:0>:   | Input Capture C                         | hannel 2 Inte    | rrupt Priority b | its             |                 |       |

|                 |               | upt is priority 7 (ł                    |                  |                  |                 |                 |       |

|                 | •             |                                         |                  |                  |                 |                 |       |

|                 | •             |                                         |                  |                  |                 |                 |       |

|                 |               | upt is priority 1<br>upt source is disa | abled            |                  |                 |                 |       |

| bit 3           |               | nted: Read as '0                        |                  |                  |                 |                 |       |

| bit 2-0         | -             | D>: DMA Channe                          |                  | sfer Complete    | Interrunt Prio  | rity hite       |       |

| 511 2-0         |               | upt is priority 7 (h                    |                  | -                |                 | They bits       |       |

|                 | •             |                                         |                  | ,                |                 |                 |       |

|                 | •             |                                         |                  |                  |                 |                 |       |

|                 | •             | upt in priority 4                       |                  |                  |                 |                 |       |

|                 |               | upt is priority 1<br>upt source is disa | abled            |                  |                 |                 |       |

| REGISTER 9-     | -3: PLLF | BD: PLL FEE      | DBACK DI | VISOR REGIS      | TER             |                |                      |

|-----------------|----------|------------------|----------|------------------|-----------------|----------------|----------------------|

| U-0             | U-0      | U-0              | U-0      | U-0              | U-0             | U-0            | R/W-0 <sup>(1)</sup> |

|                 | _        | —                | _        | —                | _               | —              | PLLDIV<8>            |

| bit 15          |          |                  |          |                  |                 |                | bit 8                |

| R/W-0           | R/W-0    | R/W-1            | R/W-1    | R/W-0            | R/W-0           | R/W-0          | R/W-0                |

|                 |          |                  | PLLE     | )IV<7:0>         |                 |                |                      |

| bit 7           |          |                  |          |                  |                 |                | bit 0                |

| Legend:         |          |                  |          |                  |                 |                |                      |

| R = Readable    | bit      | W = Writable     | bit      | U = Unimpler     | mented bit, rea | ad as '0'      |                      |

| -n = Value at P | OR       | '1' = Bit is set |          | '0' = Bit is cle | ared            | x = Bit is unl | known                |

bit 15-9 Unimplemented: Read as '0'

bit 8-0 PLLDIV<8:0>: PLL Feedback Divisor bits (also denoted as 'M', PLL multiplier)

```

000000000 = 2

00000001 = 3

000000010 = 4

.

.

000110000 = 50 (default)

.

.

11111111 = 513

```

| REGISTER 1    | 6-3: SPIxC   | ON2: SPIx C                         | ONTROL R                 | EGISTER 2         |                  |                  |       |

|---------------|--------------|-------------------------------------|--------------------------|-------------------|------------------|------------------|-------|

| R/W-0         | R/W-0        | R/W-0                               | U-0                      | U-0               | U-0              | U-0              | U-0   |

| FRMEN         | SPIFSD       | FRMPOL                              | _                        | —                 | _                | _                | _     |

| bit 15        |              |                                     |                          |                   |                  |                  | bit 8 |

|               |              |                                     |                          |                   |                  |                  |       |

| U-0           | U-0          | U-0                                 | U-0                      | U-0               | U-0              | R/W-0            | U-0   |

| —             | —            | —                                   |                          | —                 |                  | FRMDLY           |       |

| bit 7         |              |                                     |                          |                   |                  |                  | bit 0 |

| Legend:       |              |                                     |                          |                   |                  |                  |       |

| R = Readable  | bit          | W = Writable                        | bit                      | U = Unimplei      | mented bit, read | 1 as '0'         |       |

| -n = Value at |              | '1' = Bit is set                    |                          | '0' = Bit is cle  |                  | x = Bit is unkno | wn    |

|               |              |                                     |                          |                   |                  |                  |       |

| bit 15        | FRMEN: Fran  | med SPIx Supp                       | ort bit                  |                   |                  |                  |       |

|               | 1 = Framed S | SPIx support en                     | abled ( <del>SSx</del> p | oin used as fran  | ne sync pulse ir | nput/output)     |       |

|               | 0 = Framed S | SPIx support dis                    | sabled                   |                   |                  |                  |       |

| bit 14        | SPIFSD: Fran | me Sync Pulse                       | Direction Co             | ntrol bit         |                  |                  |       |

|               |              | nc pulse input (<br>nc pulse output | · /                      |                   |                  |                  |       |

| bit 13        | FRMPOL: Fra  | ame Sync Puls                       | e Polarity bit           |                   |                  |                  |       |

|               | 1 = Frame sy | nc pulse is acti                    | ve-high                  |                   |                  |                  |       |

|               | 0 = Frame sy | nc pulse is acti                    | ve-low                   |                   |                  |                  |       |

| bit 12-2      | Unimplemen   | ted: Read as '                      | 0'                       |                   |                  |                  |       |

| bit 1         | FRMDLY: Fra  | ame Sync Pulse                      | e Edge Selec             | t bit             |                  |                  |       |

|               | 1 = Frame sy | nc pulse coinci                     | des with first           | bit clock         |                  |                  |       |

|               |              | nc pulse prece                      |                          |                   |                  |                  |       |

| bit 0         | Unimplemen   | ted: This bit m                     | ust not be se            | t to '1' by the u | ser application  |                  |       |

|               |              |                                     |                          |                   |                  |                  |       |

| REGISTER 1      | 7-3: I2CxN | ISK: I2Cx SL     | AVE MODE |                  | MASK REGIS       | TER             |       |

|-----------------|------------|------------------|----------|------------------|------------------|-----------------|-------|

| U-0             | U-0        | U-0              | U-0      | U-0              | U-0              | R/W-0           | R/W-0 |

|                 |            |                  | _        |                  | —                | AMSK9           | AMSK8 |

| bit 15          |            |                  |          |                  |                  |                 | bit 8 |

| R/W-0           | R/W-0      | R/W-0            | R/W-0    | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| AMSK7           | AMSK6      | AMSK5            | AMSK4    | AMSK3            | AMSK2            | AMSK1           | AMSK0 |

| bit 7           |            |                  |          |                  |                  |                 | bit 0 |

| Legend:         |            |                  |          |                  |                  |                 |       |

| R = Readable    | bit        | W = Writable     | bit      | U = Unimpler     | mented bit, read | d as '0'        |       |

| -n = Value at P | POR        | '1' = Bit is set | t        | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

bit 15-10 Unimplemented: Read as '0'

bit 9-0 AMSKx: Mask for Address bit x Select bit

1 = Enable masking for bit x of incoming message address; bit match not required in this position

0 = Disable masking for bit x; bit match required in this position

|                  | —<br>R/W-0<br>1:0>               | —<br>R/W-0                           |            | R/W-0<br>BRF     |                  | R/W-0           | bit a |

|------------------|----------------------------------|--------------------------------------|------------|------------------|------------------|-----------------|-------|

| R/W-0<br>SJW<    | -                                | R/W-0                                | R/W-0      | -                | -                | R/W-0           |       |

| SJW<             | -                                | R/W-0                                | R/W-0      | -                | -                | R/W-0           | R/W-0 |

|                  | 1:0>                             |                                      |            | BRF              | P<5:0>           |                 |       |

| bit 7            |                                  |                                      |            |                  |                  |                 |       |

|                  |                                  |                                      |            |                  |                  |                 | bit   |

|                  |                                  |                                      |            |                  |                  |                 |       |

| Legend:          |                                  |                                      |            |                  |                  |                 |       |

| R = Readable b   | oit                              | W = Writable I                       | oit        | U = Unimpler     | mented bit, read | d as '0'        |       |

| -n = Value at PO | OR                               | '1' = Bit is set                     |            | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |

|                  |                                  |                                      |            |                  |                  |                 |       |

| bit 15-8         | Unimplement                      | ted: Read as 'o                      | )'         |                  |                  |                 |       |

| bit 7-6          | SJW<1:0>: S                      | ynchronization                       | Jump Width | bits             |                  |                 |       |

|                  | 11 = Length is                   |                                      |            |                  |                  |                 |       |

|                  | 10 = Length is                   |                                      |            |                  |                  |                 |       |

|                  | 01 = Length is<br>00 = Length is |                                      |            |                  |                  |                 |       |

|                  | •                                | aud Rate Pres                        | color bite |                  |                  |                 |       |

|                  |                                  | $Q = 2 \times 64 \times 1/F$         |            |                  |                  |                 |       |

|                  | •                                | J = Z X 04 X 1/1                     | CAN        |                  |                  |                 |       |

|                  | •                                |                                      |            |                  |                  |                 |       |

|                  | •                                |                                      |            |                  |                  |                 |       |

|                  |                                  | 2 = 2 x 3 x 1/Fo<br>2 = 2 x 2 x 1/Fo |            |                  |                  |                 |       |

00 0000 = TQ = 2 x 1 x 1/FCAN

### REGISTER 19-22: CIRXFUL1: ECAN™ RECEIVE BUFFER FULL REGISTER 1

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXFUL15 | RXFUL14 | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9 | RXFUL8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RXFUL7 | RXFUL6 | RXFUL5 | RXFUL4 | RXFUL3 | RXFUL2 | RXFUL1 | RXFUL0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           | C = Clear only bit |                                    |                    |  |  |

|-------------------|--------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit   | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 15-0

RXFUL<15:0>: Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (clear by application software)

#### REGISTER 19-23: CiRXFUL2: ECAN™ RECEIVE BUFFER FULL REGISTER 2

| R/C-0        | R/C-0                        | R/C-0 | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0 |  |  |

|--------------|------------------------------|-------|---------|---------|---------|---------|-------|--|--|

| RXFUL31      | JL31 RXFUL30 RXFUL29 RXFUL28 |       | RXFUL27 | RXFUL26 | RXFUL25 | RXFUL24 |       |  |  |

| bit 15 bit t |                              |       |         |         |         |         |       |  |  |

| R/C-0   | R/C-0                        | R/C-0 | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0 |

|---------|------------------------------|-------|---------|---------|---------|---------|-------|

| RXFUL23 | JL23 RXFUL22 RXFUL21 RXFUL20 |       | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 |       |

| bit 7   |                              |       |         |         |         |         | bit 0 |

| Legend:           | C = Clear only bit |                            |                    |

|-------------------|--------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit   | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-0

RXFUL<31:16>: Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (clear by application software)

| R/W-0         | R-0                                        | R-0                                                                      | R-0                                             | R/W-0                                      | R/W-0              | R/W-0           | R/W-0      |  |  |  |  |

|---------------|--------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------|--------------------------------------------|--------------------|-----------------|------------|--|--|--|--|

| TXENn         | TXABTn                                     | TXLARBn                                                                  | TXERRn                                          | TXREQn                                     | RTRENn             | TXnPR           | 21<1:0>    |  |  |  |  |

| bit 15        |                                            |                                                                          |                                                 |                                            |                    |                 | bit        |  |  |  |  |

| R/W-0         | R-0                                        | R-0                                                                      | R-0                                             | R/W-0                                      | R/W-0              | R/W-0           | R/W-0      |  |  |  |  |

| TXENm         | TXABTm <sup>(1)</sup>                      | TXLARBm <sup>(1)</sup>                                                   | TXERRm <sup>(1)</sup>                           | TXREQm                                     | RTRENm             | TXmPF           | RI<1:0>    |  |  |  |  |

| bit 7         |                                            |                                                                          |                                                 |                                            |                    |                 | bit        |  |  |  |  |

| Legend:       |                                            |                                                                          |                                                 |                                            |                    |                 |            |  |  |  |  |

| R = Readable  | e bit                                      | W = Writable                                                             | bit                                             | U = Unimpler                               | mented bit, read   | as '0'          |            |  |  |  |  |

| -n = Value at | POR                                        | '1' = Bit is set                                                         |                                                 | '0' = Bit is cle                           | ared               | x = Bit is unkn | iown       |  |  |  |  |

| bit 6         | 0 = Buffer TR<br>TXABTm: Me<br>1 = Message |                                                                          | buffer<br>I bit <sup>(1)</sup>                  |                                            |                    |                 |            |  |  |  |  |

| bit 5         | <b>TXLARBm:</b><br>1 = Message             | completed tran<br>Message Lost A<br>lost arbitration<br>did not lose and | Arbitration bit <sup>(*</sup><br>while being se | i)<br>ent                                  |                    |                 |            |  |  |  |  |

| bit 4         | <b>TXERRm:</b> End 1 = A bus error         | rror Detected D<br>or occurred wh<br>or did not occu                     | ouring Transmi<br>ile the messag                | ssion bit <sup>(1)</sup><br>Je was being s |                    |                 |            |  |  |  |  |

| bit 3         | TXREQm: M<br>Setting this bi               | lessage Send F<br>it to '1' request                                      | Request bit<br>s sending a m                    | essage. The b                              | it will automatica |                 | the messag |  |  |  |  |

| bit 2         |                                            | uto-Remote Tra                                                           | -                                               |                                            |                    |                 |            |  |  |  |  |

|               |                                            | emote transmit<br>emote transmit                                         |                                                 |                                            |                    |                 |            |  |  |  |  |

| bit 1-0       | TXmPRI<1:0                                 | TXmPRI<1:0>: Message Transmission Priority bits                          |                                                 |                                            |                    |                 |            |  |  |  |  |

|               |                                            | message priori<br>ermediate mes                                          |                                                 |                                            |                    |                 |            |  |  |  |  |

Note 1: This bit is cleared when TXREQ is set.

| REGISTER 2                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | IS123: ADCx                                                                                                                                                  |                                                                                                                |                                                                                                        | 3 SEL ECT P                                                               | FGISTEP          |         |  |

|------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------|---------|--|

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                              |                                                                                                                |                                                                                                        |                                                                           |                  |         |  |

| U-0                                | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | U-0                                                                                                                                                          | U-0                                                                                                            | U-0                                                                                                    | R/W-0                                                                     | R/W-0            | R/W-0   |  |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                              | – – – CH123I                                                                                                   |                                                                                                        |                                                                           | NB<1:0>          | CH123SB |  |

| bit 15                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                              |                                                                                                                |                                                                                                        |                                                                           |                  | bit 8   |  |

| U-0                                | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | U-0                                                                                                                                                          | U-0                                                                                                            | U-0                                                                                                    | R/W-0                                                                     | R/W-0            | R/W-0   |  |

|                                    | CH123NA<1:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                              |                                                                                                                |                                                                                                        |                                                                           |                  | CH123SA |  |

| bit 7                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                              |                                                                                                                |                                                                                                        | 011120                                                                    | 10/(*1.0*        | bit C   |  |

|                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                              |                                                                                                                |                                                                                                        |                                                                           |                  |         |  |

| Legend:                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                              |                                                                                                                |                                                                                                        |                                                                           |                  |         |  |

| R = Readable                       | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | W = Writable b                                                                                                                                               | oit                                                                                                            | U = Unimple                                                                                            | mented bit, rea                                                           | ad as '0'        |         |  |

| -n = Value at POR '1' = Bit is set |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                              |                                                                                                                | '0' = Bit is cle                                                                                       | eared                                                                     | x = Bit is unk   | nown    |  |

| bit 8                              | 11 = CH1 neg<br>10 = CH1 neg<br>0x = CH1, CH<br>CH123SB: CH<br>When AD12E<br>1 = CH1 posit                                                                                                                                                                                                                                                                                                                                                                                                    | B = 1, CHxNB is<br>gative input is A<br>gative input is A<br>42, CH3 negative<br>nannel 1, 2, 3 P<br>B = 1, CHxSB is<br>ive input is ANG<br>ive input is ANG | N9, CH2 nega<br>N6, CH2 nega<br>/e input is VRE<br>Positive Input S<br><b>s: U-0, Unimp</b><br>3, CH2 positive | ative input is A<br>ative input is A<br>F-<br>Select for Sam<br>I <b>emented, Re</b><br>e input is AN4 | N10, CH3 neg<br>N7, CH3 nega<br>ple B bit<br>ead as '0'<br>, CH3 positive | tive input is AN |         |  |

| bit 7-3                            | Unimplemen                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | ted: Read as 'o                                                                                                                                              | )'                                                                                                             |                                                                                                        |                                                                           |                  |         |  |

| bit 2-1                            | CH123NA<1:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <b>0&gt;:</b> Channel 1,                                                                                                                                     | 2, 3 Negative                                                                                                  | Input Select f                                                                                         | or Sample A bi                                                            | its              |         |  |

| bit 0                              | <ul> <li>CH123NA&lt;1:0&gt;: Channel 1, 2, 3 Negative Input Select for Sample A bits</li> <li>When AD12B = 1, CHxNA is: U-0, Unimplemented, Read as '0'</li> <li>11 = CH1 negative input is AN9, CH2 negative input is AN10, CH3 negative input is AN11</li> <li>10 = CH1 negative input is AN6, CH2 negative input is AN7, CH3 negative input is AN8</li> <li>0x = CH1, CH2, CH3 negative input is VREF-</li> <li>CH123SA: Channel 1, 2, 3 Positive Input Select for Sample A bit</li> </ul> |                                                                                                                                                              |                                                                                                                |                                                                                                        |                                                                           |                  |         |  |

|                                    | When AD12B = 1, CHxSA is: U-0, Unimplemented, Read as '0'<br>1 = CH1 positive input is AN3, CH2 positive input is AN4, CH3 positive input is AN5<br>0 = CH1 positive input is AN0, CH2 positive input is AN1, CH3 positive input is AN2                                                                                                                                                                                                                                                       |                                                                                                                                                              |                                                                                                                |                                                                                                        |                                                                           |                  |         |  |

### 24.7 MPLAB ICE 2000 High-Performance In-Circuit Emulator

The MPLAB ICE 2000 In-Circuit Emulator is intended to provide the product development engineer with a complete microcontroller design tool set for PIC microcontrollers. Software control of the MPLAB ICE 2000 In-Circuit Emulator is advanced by the MPLAB Integrated Development Environment, which allows editing, building, downloading and source debugging from a single environment.

The MPLAB ICE 2000 is a full-featured emulator system with enhanced trace, trigger and data monitoring features. Interchangeable processor modules allow the system to be easily reconfigured for emulation of different processors. The architecture of the MPLAB ICE 2000 In-Circuit Emulator allows expansion to support new PIC microcontrollers.

The MPLAB ICE 2000 In-Circuit Emulator system has been designed as a real-time emulation system with advanced features that are typically found on more expensive development tools. The PC platform and Microsoft<sup>®</sup> Windows<sup>®</sup> 32-bit operating system were chosen to best make these features available in a simple, unified application.

### 24.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The MPLAB REAL ICE probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with the popular MPLAB ICD 2 system (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

MPLAB REAL ICE is field upgradeable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added, such as software breakpoints and assembly code trace. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, real-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 24.9 MPLAB ICD 2 In-Circuit Debugger

Microchip's In-Circuit Debugger, MPLAB ICD 2, is a powerful, low-cost, run-time development tool, connecting to the host PC via an RS-232 or high-speed USB interface. This tool is based on the Flash PIC MCUs and can be used to develop for these and other PIC MCUs and dsPIC DSCs. The MPLAB ICD 2 utilizes the in-circuit debugging capability built into the Flash devices. This feature, along with Microchip's In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) protocol, offers cost-effective, in-circuit Flash debugging from the graphical user interface of the MPLAB Integrated Development Environment. This enables a designer to develop and debug source code by setting breakpoints, single stepping and watching variables, and CPU status and peripheral registers. Running at full speed enables testing hardware and applications in real time. MPLAB ICD 2 also serves as a development programmer for selected PIC devices.

### 24.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices and incorporates an SD/MMC card for file storage and secure data applications.

#### TABLE 25-21: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER TIMING REQUIREMENTS

| AC CHA       | RACTER | ISTICS                                                         | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |                                      |     |       |                                                                                        |  |  |

|--------------|--------|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|-----|-------|----------------------------------------------------------------------------------------|--|--|

| Param<br>No. | Symbol | Characteristic <sup>(1)</sup>                                  | Min                                                                                                                                             | Тур <sup>(2)</sup>                   | Мах | Units | Conditions                                                                             |  |  |

| SY10         | TMCL   | MCLR Pulse-Width (low)                                         | 2                                                                                                                                               | —                                    | _   | μs    | -40°C to +85°C                                                                         |  |  |

| SY11         | TPWRT  | Power-up Timer Period                                          |                                                                                                                                                 | 2<br>4<br>8<br>16<br>32<br>64<br>128 |     | ms    | -40°C to +85°C<br>User programmable                                                    |  |  |

| SY12         | TPOR   | Power-on Reset Delay                                           | 3                                                                                                                                               | 10                                   | 30  | μs    | -40°C to +85°C                                                                         |  |  |

| SY13         | Tioz   | I/O High-Impedance from<br>MCLR Low or Watchdog<br>Timer Reset | 0.68                                                                                                                                            | 0.72                                 | 1.2 | μs    | _                                                                                      |  |  |

| SY20         | Twdt1  | Watchdog Timer<br>Time-out Period                              | —                                                                                                                                               | _                                    |     | —     | See Section 22.4 "Watchdog<br>Timer (WDT)" and LPRC<br>specification F21 (Table 25-19) |  |  |

| SY30         | Tost   | Oscillator Start-up Timer<br>Period                            | —                                                                                                                                               | 1024 Tosc                            | —   | —     | Tosc = OSC1 period                                                                     |  |  |

| SY35         | TFSCM  | Fail-Safe Clock Monitor<br>Delay                               | —                                                                                                                                               | 500                                  | 900 | μs    | -40°C to +85°C                                                                         |  |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

### TABLE 25-23: TIMER2, TIMER4, TIMER6 AND TIMER8 EXTERNAL CLOCK TIMING REQUIREMENTS

| АС СНА       | RACTERIS       | TICS                                    |                                                                | Standard Operating Conditions: 3.0V to 3.6V<br>(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |                                         |     |         |       |                               |

|--------------|----------------|-----------------------------------------|----------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-----|---------|-------|-------------------------------|

| Param<br>No. | Symbol         | Characteristic                          |                                                                |                                                                                                                                                     | Min                                     | Тур | Max     | Units | Conditions                    |

| TB10         | TtxH           | TxCK High Time                          | Synchronous,<br>no prescaler<br>Synchronous,<br>with prescaler |                                                                                                                                                     | 0.5 Tcy + 20                            |     | _       | ns    | Must also meet parameter TB15 |

|              |                |                                         |                                                                |                                                                                                                                                     | 10                                      | _   | —       | ns    |                               |

| TB11         | TtxL           | TxCK Low Time                           | Synchronous,<br>no prescaler                                   |                                                                                                                                                     | 0.5 TCY + 20                            | _   | —       | ns    | Must also meet parameter TB15 |

|              |                |                                         | Synchron<br>with pres                                          |                                                                                                                                                     | 10                                      | _   | —       | ns    |                               |

| TB15         | TtxP           | TxCK Input<br>Period                    | Synchron<br>no presc                                           |                                                                                                                                                     | TCY + 40                                | _   | —       | ns    | N = prescale<br>value         |

|              |                |                                         | Synchron<br>with pres                                          |                                                                                                                                                     | Greater of:<br>20 ns or<br>(Tcy + 40)/N |     |         |       | (1, 8, 64, 256)               |

| TB20         | TCKEXT-<br>MRL | Delay from Extern<br>Edge to Timer Inci |                                                                | lock                                                                                                                                                | 0.5 TCY                                 | _   | 1.5 TCY |       | —                             |

### TABLE 25-24: TIMER3, TIMER5, TIMER7 AND TIMER9 EXTERNAL CLOCK TIMING REQUIREMENTS

| АС СНА       | RACTERIST | rics                                      | (ui                       | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ |     |            |       |                               |  |

|--------------|-----------|-------------------------------------------|---------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----|------------|-------|-------------------------------|--|

| Param<br>No. | Symbol    | Characte                                  | eristic                   | Min                                                                                                                              | Тур | Max        | Units | Conditions                    |  |

| TC10         | TtxH      | TxCK High Time                            | Synchronou                | us 0.5 TCY + 2                                                                                                                   | 0 — |            | ns    | Must also meet parameter TC15 |  |

| TC11         | TtxL      | TxCK Low Time                             | Synchronou                | us 0.5 Tcy + 2                                                                                                                   | 0 — | -          | ns    | Must also meet parameter TC15 |  |

| TC15         | TtxP      | TxCK Input Period                         | Synchronou<br>no prescale | ,                                                                                                                                | -   | —          | ns    | N = prescale<br>value         |  |

|              |           |                                           | Synchronou with prescal   |                                                                                                                                  |     |            |       | (1, 8, 64, 256)               |  |

| TC20         | TCKEXTMRL | Delay from Externa<br>Edge to Timer Incre |                           | k 0.5 Tcy                                                                                                                        | _   | 1.5<br>Тсү | _     | —                             |  |

#### TABLE 25-32: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

|              | ARACTER     | ISTICS           |                           | (unless otherwise  | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ |       |                        |  |  |

|--------------|-------------|------------------|---------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------|-------|------------------------|--|--|

| Param<br>No. | Symbol      | Charac           | teristic                  | Min <sup>(1)</sup> | Max                                                                                                                              | Units | Conditions             |  |  |