Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                             |

| Core Size                  | 16-Bit                                                                            |

| Speed                      | 40 MIPs                                                                           |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                           |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT               |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 30K × 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                         |

| Data Converters            | A/D 32x10b/12b                                                                    |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj256gp710t-i-pf |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.5 Arithmetic Logic Unit (ALU)

The dsPIC33FJXXXGPX06/X08/X10 ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the <u>SR</u> register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the "*dsPIC30F/33F Programmer's Reference Manual*" (DS70157) for information on the SR bits affected by each instruction.

The dsPIC33FJXXXGPX06/X08/X10 CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit-divisor division.

### 3.5.1 MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier of the DSP engine, the ALU supports unsigned, signed or mixed-sign operation in several MCU multiplication modes:

- 1. 16-bit x 16-bit signed

- 2. 16-bit x 16-bit unsigned

- 3. 16-bit signed x 5-bit (literal) unsigned

- 4. 16-bit unsigned x 16-bit unsigned

- 5. 16-bit unsigned x 5-bit (literal) unsigned

- 6. 16-bit unsigned x 16-bit signed

- 7. 8-bit unsigned x 8-bit unsigned

### 3.5.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

### 3.6 DSP Engine

The DSP engine consists of a high-speed, 17-bit x 17-bit multiplier, a barrel shifter and a 40-bit adder/subtracter (with two target accumulators, round and saturation logic).

The dsPIC33FJXXXGPX06/X08/X10 is a single-cycle, instruction flow architecture; therefore, concurrent operation of the DSP engine with MCU instruction flow is not possible. However, some MCU ALU and DSP engine resources may be used concurrently by the same instruction (e.g., ED, EDAC).

The DSP engine also has the capability to perform inherent accumulator-to-accumulator operations which require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has various options selected through various bits in the CPU Core Control register (CORCON), as listed below:

- 1. Fractional or integer DSP multiply (IF).

- 2. Signed or unsigned DSP multiply (US).

- 3. Conventional or convergent rounding (RND).

- 4. Automatic saturation on/off for AccA (SATA).

- 5. Automatic saturation on/off for AccB (SATB).

- 6. Automatic saturation on/off for writes to data memory (SATDW).

- 7. Accumulator Saturation mode selection (ACCSAT).

Table 3-1 provides a summary of DSP instructions. A block diagram of the DSP engine is shown in Figure 3-3.

|             | SUMMARY                |                   |

|-------------|------------------------|-------------------|

| Instruction | Algebraic<br>Operation | ACC Write<br>Back |

| CLR         | A = 0                  | Yes               |

| ED          | $A = (x - y)^2$        | No                |

| EDAC        | $A = A + (x - y)^2$    | No                |

| MAC         | A = A + (x * y)        | Yes               |

| MAC         | $A = A + x^2$          | No                |

| MOVSAC      | No change in A         | Yes               |

| MPY         | A = x * y              | No                |

| MPY         | $A = x^2$              | No                |

| MPY.N       | A = -x * y             | No                |

| MSC         | A = A - x * y          | Yes               |

### TABLE 3-1: DSP INSTRUCTIONS SUMMARY

### 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the dsPIC33FJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 3. "Data Memory" (DS70202) and Section 4. "Program Memory" (DS70203) in the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33FJXXXGPX06/X08/X10 architecture features separate program and data memory spaces and buses. This architecture also allows the direct access of program memory from the data space during code execution.

### 4.1 Program Address Space

The program address memory space of the dsPIC33FJXXXGPX06/X08/X10 devices is 4M instructions. The space is addressable by a 24-bit value derived from either the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping as described in Section 4.6 "Interfacing Program and Data Memory Spaces".

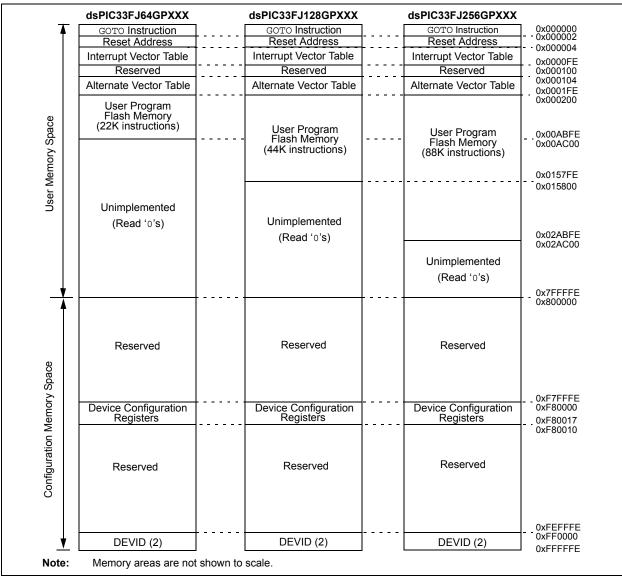

User access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFFF). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space. Memory usage for the dsPIC33FJXXXGPX06/X08/X10 of devices is shown in Figure 4-1.

### FIGURE 4-1: PROGRAM MEMORY FOR dsPIC33FJXXXGPX06/X08/X10 DEVICES

### 4.1.1 PROGRAM MEMORY ORGANIZATION

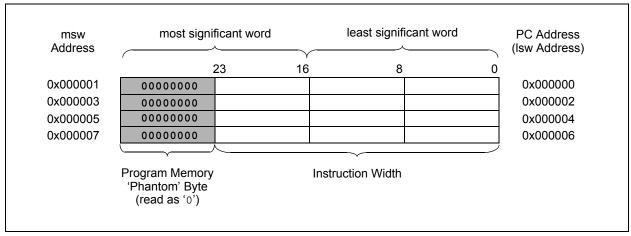

The program memory space is organized in word-addressable blocks. Although it is treated as 24 bits wide, it is more appropriate to think of each address of the program memory as a lower and upper word, with the upper byte of the upper word being unimplemented. The lower word always has an even address, while the upper word has an odd address (Figure 4-2).

Program memory addresses are always word-aligned on the lower word, and addresses are incremented or decremented by two during code execution. This arrangement also provides compatibility with data memory space addressing and makes it possible to access data in the program memory space.

### 4.1.2 INTERRUPT AND TRAP VECTORS

All dsPIC33FJXXXGPX06/X08/X10 devices reserve the addresses between 0x00000 and 0x000200 for hard-coded program execution vectors. A hardware Reset vector is provided to redirect code execution from the default value of the PC on device Reset to the actual start of code. A GOTO instruction is programmed by the user at 0x000000, with the actual address for the start of code at 0x000002.

dsPIC33FJXXXGPX06/X08/X10 devices also have two interrupt vector tables, located from 0x000004 to 0x0000FF and 0x000100 to 0x0001FF. These vector tables allow each of the many device interrupt sources to be handled by separate Interrupt Service Routines (ISRs). A more detailed discussion of the interrupt vector tables is provided in **Section 7.1 "Interrupt Vector Table**".

### FIGURE 4-2: PROGRAM MEMORY ORGANIZATION

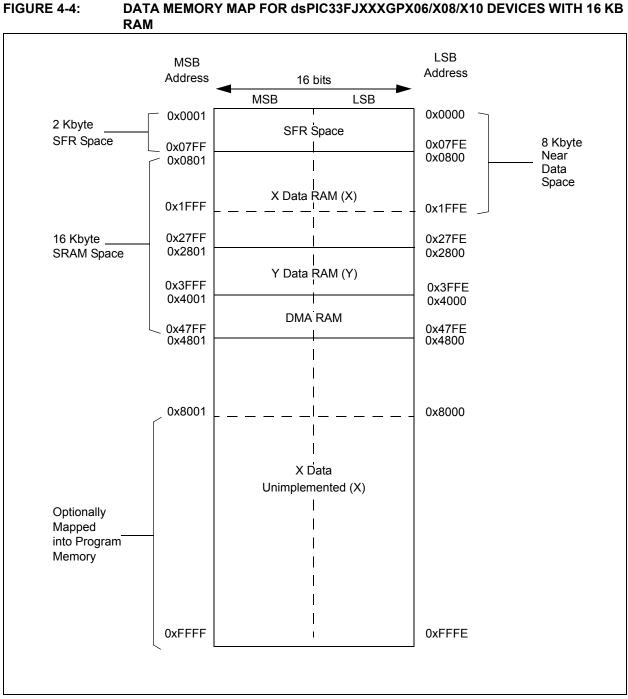

### DATA MEMORY MAP FOR dsPIC33FJXXXGPX06/X08/X10 DEVICES WITH 16 KB

### TABLE 4-2: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJXXXGPX10 DEVICES

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3   | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|---------|---------|---------|---------|---------|---------|---------|---------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | CN7IE   | CN6IE   | CN5IE   | CN4IE   | CN3IE   | CN2IE   | CN1IE   | CN0IE   | 0000          |

| CNEN2       | 0062        | _       |         | _       | _       | _       | _       | _      | _      | CN23IE  | CN22IE  | CN21IE  | CN20IE  | CN19IE  | CN18IE  | CN17IE  | CN16IE  | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | CN7PUE  | CN6PUE  | CN5PUE  | CN4PUE  | CN3PUE  | CN2PUE  | CN1PUE  | CN0PUE  | 0000          |

| CNPU2       | 006A        |         | _       | -       | _       | —       | _       | _      | _      | CN23PUE | CN22PUE | CN21PUE | CN20PUE | CN19PUE | CN18PUE | CN17PUE | CN16PUE | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

#### TABLE 4-3: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJXXXGPX08 DEVICES

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3         | Bit 2   | Bit 1   | Bit 0         | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|---------|---------|---------------|---------|---------|---------------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | CN7IE  | CN6IE  | CN5IE   | CN4IE   | CN3IE         | CN2IE   | CN1IE   | CN0IE         | 0000          |

| CNEN2       | 0062        | —       |         |         | _       |         | —       |        |        | _      | —      | CN21IE  | CN20IE  | CN19IE        | CN18IE  | CN17IE  | CN16IE        | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | CN7PUE | CN6PUE | CN5PUE  | CN4PUE  | <b>CN3PUE</b> | CN2PUE  | CN1PUE  | <b>CN0PUE</b> | 0000          |

| CNPU2       | 006A        | _       |         |         |         |         | —       |        |        | _      | —      | CN21PUE | CN20PUE | CN19PUE       | CN18PUE | CN17PUE | CN16PUE       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-4: CHANGE NOTIFICATION REGISTER MAP FOR dsPIC33FJXXXGPX06 DEVICES

| SFR<br>Name | SFR<br>Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5   | Bit 4   | Bit 3  | Bit 2   | Bit 1   | Bit 0         | All<br>Resets |

|-------------|-------------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|---------|---------|--------|---------|---------|---------------|---------------|

| CNEN1       | 0060        | CN15IE  | CN14IE  | CN13IE  | CN12IE  | CN11IE  | CN10IE  | CN9IE  | CN8IE  | CN7IE  | CN6IE  | CN5IE   | CN4IE   | CN3IE  | CN2IE   | CN1IE   | CN0IE         | 0000          |

| CNEN2       | 0062        | _       | _       | _       | _       | _       | _       | _      | _      | _      | _      | CN21IE  | CN20IE  | -      | CN18IE  | CN17IE  | CN16IE        | 0000          |

| CNPU1       | 0068        | CN15PUE | CN14PUE | CN13PUE | CN12PUE | CN11PUE | CN10PUE | CN9PUE | CN8PUE | CN7PUE | CN6PUE | CN5PUE  | CN4PUE  | CN3PUE | CN2PUE  | CN1PUE  | <b>CN0PUE</b> | 0000          |

| CNPU2       | 006A        | —       | _       | _       | _       | _       | _       | _      | _      | -      |        | CN21PUE | CN20PUE | _      | CN18PUE | CN17PUE | CN16PUE       | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

### TABLE 4-17: DMA REGISTER MAP

|           |      | -      |        | -      | -      | -      | -      | -     |       |           |       | -     |        |           |       |       |       | All    |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-----------|-------|-------|--------|-----------|-------|-------|-------|--------|

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7     | Bit 6 | Bit 5 | Bit 4  | Bit 3     | Bit 2 | Bit 1 | Bit 0 | Resets |

| DMA0CON   | 0380 | CHEN   | SIZE   | DIR    | HALF   | NULLW  |        | _     | _     | _         |       | AMOD  | E<1:0> | —         | _     | MODE  | <1:0> | 0000   |

| DMA0REQ   | 0382 | FORCE  | _      | —      |        | —      | _      | —     |       | —         |       |       | I      | RQSEL<6:0 | >     |       |       | 0000   |

| DMA0STA   | 0384 |        |        |        |        |        |        |       | S     | STA<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA0STB   | 0386 |        |        |        |        |        |        |       | S     | STB<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA0PAD   | 0388 |        |        |        | -      |        |        |       | P     | AD<15:0>  |       |       |        |           |       |       |       | 0000   |

| DMA0CNT   | 038A | —      | —      | _      | —      | —      | _      |       |       |           |       | CN    | <9:0>  |           |       |       |       | 0000   |

| DMA1CON   | 038C | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | —     | —     | —         | —     | AMOD  | E<1:0> | —         | —     | MODE  | <1:0> | 0000   |

| DMA1REQ   | 038E | FORCE  | _      | —      | —      | —      | _      | —     | —     | —         |       |       | I      | RQSEL<6:0 | >     |       |       | 0000   |

| DMA1STA   | 0390 |        |        |        |        |        |        |       | S     | STA<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA1STB   | 0392 |        |        |        |        |        |        |       | S     | TB<15:0>  |       |       |        |           |       |       |       | 0000   |

| DMA1PAD   | 0394 |        |        |        |        |        |        |       | P     | AD<15:0>  |       |       |        |           |       |       |       | 0000   |

| DMA1CNT   | 0396 | _      | _      | _      | —      | _      |        |       |       |           |       | CN    | <9:0>  |           |       |       |       | 0000   |

| DMA2CON   | 0398 | CHEN   | SIZE   | DIR    | HALF   | NULLW  |        | —     | —     | —         | _     | AMOD  | E<1:0> | -         | —     | MODE  | <1:0> | 0000   |

| DMA2REQ   | 039A | FORCE  | -      | _      | _      | _      | _      | _     | _     | _         |       |       | I      | RQSEL<6:0 | >     |       |       | 0000   |

| DMA2STA   | 039C |        |        |        |        |        |        |       | S     | STA<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA2STB   | 039E |        |        |        |        |        |        |       | S     | TB<15:0>  |       |       |        |           |       |       |       | 0000   |

| DMA2PAD   | 03A0 |        |        |        |        |        |        |       | P     | AD<15:0>  |       |       |        |           |       |       |       | 0000   |

| DMA2CNT   | 03A2 | _      | _      | _      | _      | —      | _      |       |       |           |       | CN    | <9:0>  |           |       |       |       | 0000   |

| DMA3CON   | 03A4 | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _     | —         | —     | AMOD  | E<1:0> | _         | _     | MODE  | <1:0> | 0000   |

| DMA3REQ   | 03A6 | FORCE  | _      | _      | _      | —      | _      | _     | _     | —         |       |       | I      | RQSEL<6:0 | >     |       |       | 0000   |

| DMA3STA   | 03A8 |        |        |        |        |        |        |       | S     | STA<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA3STB   | 03AA |        |        |        |        |        |        |       | S     | TB<15:0>  |       |       |        |           |       |       |       | 0000   |

| DMA3PAD   | 03AC |        |        |        |        |        |        |       | P     | AD<15:0>  |       |       |        |           |       |       |       | 0000   |

| DMA3CNT   | 03AE | _      | _      | _      | _      | —      | _      |       |       |           |       | CN    | <9:0>  |           |       |       |       | 0000   |

| DMA4CON   | 03B0 | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _     | _         | _     | AMOD  | E<1:0> | _         | _     | MODE  | <1:0> | 0000   |

| DMA4REQ   | 03B2 | FORCE  | _      | _      | _      | _      | _      | _     | _     | _         |       |       | I      | RQSEL<6:0 | >     |       |       | 0000   |

| DMA4STA   | 03B4 |        |        |        | •      |        |        | •     | S     | TA<15:0>  | •     |       |        |           |       |       |       | 0000   |

| DMA4STB   | 03B6 |        |        |        |        |        |        |       | S     | TB<15:0>  |       |       |        |           |       |       |       | 0000   |

| DMA4PAD   | 03B8 |        |        |        |        |        |        |       | P     | AD<15:0>  |       |       |        |           |       |       |       | 0000   |

| DMA4CNT   | 03BA | _      | _      | _      | —      | —      | —      |       |       |           |       | CN    | <9:0>  |           |       |       |       | 0000   |

| DMA5CON   | 03BC | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | —     | —         | _     | AMOD  | E<1:0> | —         | —     | MODE  | <1:0> | 0000   |

| DMA5REQ   | 03BE | FORCE  | _      | —      | —      | —      | —      | _     | —     | _         |       | •     | I      | RQSEL<6:0 | >     | •     |       | 0000   |

| DMA5STA   | 03C0 |        |        |        |        |        |        |       | S     | TA<15:0>  | •     |       |        |           |       |       |       | 0000   |

| DMA5STB   | 03C2 |        |        |        |        |        |        |       | S     | TB<15:0>  |       |       |        |           |       |       |       | 0000   |

| DMA5PAD   | 03C4 |        |        |        |        |        |        |       | P     | AD<15:0>  |       |       |        |           |       |       |       | 0000   |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

# DS70286C-page 50

| Flag Bit          | Setting Event                                        | Clearing Event               |

|-------------------|------------------------------------------------------|------------------------------|

| TRAPR (RCON<15>)  | Trap conflict event                                  | POR, BOR                     |

| IOPUWR (RCON<14>) | Illegal opcode or uninitialized<br>W register access | POR, BOR                     |

| EXTR (RCON<7>)    | MCLR Reset                                           | POR                          |

| SWR (RCON<6>)     | RESET instruction                                    | POR, BOR                     |

| WDTO (RCON<4>)    | WDT time-out                                         | PWRSAV instruction, POR, BOR |

| SLEEP (RCON<3>)   | PWRSAV #SLEEP instruction                            | POR, BOR                     |

| IDLE (RCON<2>)    | PWRSAV #IDLE instruction                             | POR, BOR                     |

| BOR (RCON<1>)     | BOR, POR                                             | —                            |

| POR (RCON<0>)     | POR                                                  | -                            |

### TABLE 6-1:RESET FLAG BIT OPERATION

Note: All Reset flag bits may be set or cleared by the user software.

### 6.1 Clock Source Selection at Reset

If clock switching is enabled, the system clock source at device Reset is chosen, as shown in Table 6-2. If clock switching is disabled, the system clock source is always selected according to the oscillator Configuration bits. Refer to **Section 9.0 "Oscillator Configuration"** for further details.

## TABLE 6-2:OSCILLATOR SELECTION VSTYPE OF RESET (CLOCK<br/>SWITCHING ENABLED)

| Reset Type | Clock Source Determinant      |

|------------|-------------------------------|

| POR        | Oscillator Configuration bits |

| BOR        | (FNOSC<2:0>)                  |

| MCLR       | COSC Control bits             |

| WDTR       | (OSCCON<14:12>)               |

| SWR        |                               |

### 6.2 Device Reset Times

The Reset times for various types of device Reset are <u>summarized</u> in Table 6-3. The system Reset signal, SYSRST, is released after the POR and PWRT delay times expire.

The time at which the device actually begins to execute code also depends on the system oscillator delays, which include the Oscillator Start-up Timer (OST) and the PLL lock time. The OST and PLL lock times occur in parallel with the applicable SYSRST delay times.

The FSCM delay determines the time at which the FSCM begins to monitor the system clock source after the SYSRST signal is released.

### REGISTER 7-16: IPC1: INTERRUPT PRIORITY CONTROL REGISTER 1

| —<br>bit 15     |               |                                         |                  |                  |                 |                 |       |

|-----------------|---------------|-----------------------------------------|------------------|------------------|-----------------|-----------------|-------|

| bit 15          |               | T2IP<2:0>                               |                  | —                |                 | OC2IP<2:0>      |       |

|                 |               |                                         |                  |                  |                 |                 | bit   |

|                 |               |                                         |                  |                  |                 |                 |       |

| U-0             | R/W-1         | R/W-0                                   | R/W-0            | U-0              | R/W-1           | R/W-0           | R/W-0 |

|                 |               | IC2IP<2:0>                              |                  | —                |                 | DMA0IP<2:0>     |       |

| bit 7           |               |                                         |                  |                  |                 |                 | bit   |

| Legend:         |               |                                         |                  |                  |                 |                 |       |

| R = Readable    | bit           | W = Writable I                          | oit              | U = Unimple      | mented bit, rea | ad as '0'       |       |

| -n = Value at F | POR           | '1' = Bit is set                        |                  | '0' = Bit is cle | ared            | x = Bit is unkn | own   |

| bit 15          | Unimpleme     | nted: Read as 'o                        | )'               |                  |                 |                 |       |

| bit 14-12       | T2IP<2:0>:    | Timer2 Interrupt                        | Priority bits    |                  |                 |                 |       |

|                 | 111 = Interru | upt is priority 7 (ł                    | nighest priority | y interrupt)     |                 |                 |       |

|                 | •             |                                         |                  |                  |                 |                 |       |

|                 | •             |                                         |                  |                  |                 |                 |       |

|                 | 001 = Interru | upt is priority 1                       |                  |                  |                 |                 |       |

|                 |               | upt source is disa                      |                  |                  |                 |                 |       |

| bit 11          | Unimpleme     | nted: Read as 'o                        | )'               |                  |                 |                 |       |

| bit 10-8        |               | ·: Output Compa                         |                  | •                | ity bits        |                 |       |

|                 | 111 = Interru | upt is priority 7 (h                    | nighest priority | y interrupt)     |                 |                 |       |

|                 | •             |                                         |                  |                  |                 |                 |       |

|                 | •             |                                         |                  |                  |                 |                 |       |

|                 |               | upt is priority 1<br>upt source is disa | abled            |                  |                 |                 |       |

| bit 7           |               | nted: Read as 'o                        |                  |                  |                 |                 |       |

| bit 6-4         | IC2IP<2:0>:   | Input Capture C                         | hannel 2 Inte    | rrupt Priority b | its             |                 |       |

|                 |               | upt is priority 7 (ł                    |                  |                  |                 |                 |       |

|                 | •             |                                         |                  |                  |                 |                 |       |

|                 | •             |                                         |                  |                  |                 |                 |       |

|                 |               | upt is priority 1<br>upt source is disa | abled            |                  |                 |                 |       |

| bit 3           |               | nted: Read as 'o                        |                  |                  |                 |                 |       |

| bit 2-0         | -             | D>: DMA Channe                          |                  | sfer Complete    | Interrunt Prio  | rity hite       |       |

| 511 2-0         |               | upt is priority 7 (h                    |                  | -                |                 | They bits       |       |

|                 | •             |                                         |                  | ,                |                 |                 |       |

|                 | •             |                                         |                  |                  |                 |                 |       |

|                 | •             | upt in priority 4                       |                  |                  |                 |                 |       |

|                 |               | upt is priority 1<br>upt source is disa | abled            |                  |                 |                 |       |

| REGISTER 7-18: IPC3: INTERRUPT PRIORITY CONTROL REGISTER 3 | <b>REGISTER 7-18:</b> |

|------------------------------------------------------------|-----------------------|

|------------------------------------------------------------|-----------------------|

| U-0              | U-0                                                                                                                                  | U-0                                                                                                                                                                                                | U-0                                                                      | U-0              | R/W-1           | R/W-0           | R/W-0 |

|------------------|--------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|------------------|-----------------|-----------------|-------|

| _                | _                                                                                                                                    | —                                                                                                                                                                                                  |                                                                          |                  |                 | DMA1IP<2:0>     |       |

| pit 15           |                                                                                                                                      |                                                                                                                                                                                                    |                                                                          |                  |                 |                 | bit 8 |

| U-0              | R/W-1                                                                                                                                | R/W-0                                                                                                                                                                                              | R/W-0                                                                    | U-0              | R/W-1           | R/W-0           | R/W-0 |

| 0-0              | R/W-1                                                                                                                                | AD1IP<2:0>                                                                                                                                                                                         | R/VV-U                                                                   | 0-0              | FV/VV-1         | U1TXIP<2:0>     | R/W-U |

| <br>bit 7        |                                                                                                                                      | AD 11F \2.02                                                                                                                                                                                       |                                                                          | —                |                 | 011XIF<2.02     | bit 0 |

|                  |                                                                                                                                      |                                                                                                                                                                                                    |                                                                          |                  |                 |                 | Dit C |

| _egend:          |                                                                                                                                      |                                                                                                                                                                                                    |                                                                          |                  |                 |                 |       |

| R = Readab       | le bit                                                                                                                               | W = Writable I                                                                                                                                                                                     | oit                                                                      | U = Unimpler     | mented bit, rea | ad as '0'       |       |

| -n = Value a     | It POR                                                                                                                               | '1' = Bit is set                                                                                                                                                                                   |                                                                          | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

|                  |                                                                                                                                      |                                                                                                                                                                                                    |                                                                          |                  |                 |                 |       |

| oit 15-11        | Unimplemen                                                                                                                           | ted: Read as 'd                                                                                                                                                                                    | )'                                                                       |                  |                 |                 |       |

| oit 10-8         | DMA1IP<2:0                                                                                                                           | >: DMA Channe                                                                                                                                                                                      | el 1 Data Tra                                                            | nsfer Complete   | Interrupt Prior | rity bits       |       |

|                  | 111 = Interru                                                                                                                        | pt is priority 7 (ł                                                                                                                                                                                | nighest priorit                                                          | y interrupt)     |                 |                 |       |

|                  |                                                                                                                                      |                                                                                                                                                                                                    |                                                                          |                  |                 |                 |       |

|                  | •                                                                                                                                    |                                                                                                                                                                                                    |                                                                          |                  |                 |                 |       |

|                  | •                                                                                                                                    |                                                                                                                                                                                                    |                                                                          |                  |                 |                 |       |

|                  | •<br>•<br>•<br>001 = Interru                                                                                                         | pt is priority 1                                                                                                                                                                                   |                                                                          |                  |                 |                 |       |

|                  | •<br>•<br>001 = Interru<br>000 = Interru                                                                                             | pt is priority 1<br>pt source is disa                                                                                                                                                              | abled                                                                    |                  |                 |                 |       |

| oit 7            | 000 = Interru                                                                                                                        |                                                                                                                                                                                                    |                                                                          |                  |                 |                 |       |

| bit 7<br>bit 6-4 | 000 = Interru<br>Unimplemen                                                                                                          | pt source is disa                                                                                                                                                                                  | )'                                                                       | e Interrupt Prio | rity bits       |                 |       |

|                  | 000 = Interru<br>Unimplemen<br>AD1IP<2:0>:                                                                                           | pt source is disa<br>ited: Read as 'o                                                                                                                                                              | )'<br>sion Complete                                                      |                  | rity bits       |                 |       |

|                  | 000 = Interru<br>Unimplemen<br>AD1IP<2:0>:                                                                                           | pt source is disa<br>ited: Read as 'o<br>ADC1 Convers                                                                                                                                              | )'<br>sion Complete                                                      |                  | rity bits       |                 |       |

|                  | 000 = Interru<br>Unimplemen<br>AD1IP<2:0>:                                                                                           | pt source is disa<br>ited: Read as 'o<br>ADC1 Convers                                                                                                                                              | )'<br>sion Complete                                                      |                  | rity bits       |                 |       |

|                  | 000 = Interru<br>Unimplemen<br>AD1IP<2:0>:<br>111 = Interru<br>•<br>•                                                                | pt source is disa<br>ited: Read as 'o<br>ADC1 Convers<br>pt is priority 7 (h                                                                                                                       | )'<br>sion Complete                                                      |                  | rity bits       |                 |       |

|                  | 000 = Interru<br>Unimplemen<br>AD1IP<2:0>:<br>111 = Interru<br>•<br>•<br>001 = Interru                                               | pt source is disa<br>ited: Read as 'o<br>ADC1 Convers<br>pt is priority 7 (h                                                                                                                       | <sub>)</sub> '<br>sion Completi<br>nighest priorit                       |                  | rity bits       |                 |       |

| bit 6-4          | 000 = Interru<br>Unimplemen<br>AD1IP<2:0>:<br>111 = Interru<br>001 = Interru<br>000 = Interru                                        | pt source is disa<br><b>ited:</b> Read as 'o<br>ADC1 Convers<br>pt is priority 7 (h<br>pt is priority 1                                                                                            | <sub>o</sub> '<br>sion Complete<br>nighest priorit<br>abled              |                  | rity bits       |                 |       |

| bit 6-4<br>bit 3 | 000 = Interru<br>Unimplemen<br>AD1IP<2:0>:<br>111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen                | pt source is disa<br><b>ited:</b> Read as 'o<br>ADC1 Convers<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa                                                                       | <sub>o</sub> '<br>sion Completa<br>nighest priorit<br>abled              | y interrupt)     | rity bits       |                 |       |

| bit 6-4<br>bit 3 | 000 = Interru<br>Unimplemen<br>AD1IP<2:0>:<br>111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>U1TXIP<2:0> | pt source is disa<br><b>ited:</b> Read as 'contraction<br>ADC1 Converse<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>ited:</b> Read as 'contraction                       | )'<br>sion Complete<br>nighest priorit<br>abled<br>5'<br>smitter Interru | ny interrupt)    | rity bits       |                 |       |

| bit 6-4<br>bit 3 | 000 = Interru<br>Unimplemen<br>AD1IP<2:0>:<br>111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>U1TXIP<2:0> | pt source is disa<br><b>ited:</b> Read as 'o<br>ADC1 Convers<br>pt is priority 7 (f<br>pt is priority 1<br>pt source is disa<br><b>ited:</b> Read as 'o<br>•: UART1 Trans                          | )'<br>sion Complete<br>nighest priorit<br>abled<br>5'<br>smitter Interru | ny interrupt)    | rity bits       |                 |       |

|                  | 000 = Interru<br>Unimplemen<br>AD1IP<2:0>:<br>111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>U1TXIP<2:0> | pt source is disa<br><b>ited:</b> Read as 'o<br>ADC1 Convers<br>pt is priority 7 (f<br>pt is priority 1<br>pt source is disa<br><b>ited:</b> Read as 'o<br>•: UART1 Trans                          | )'<br>sion Complete<br>nighest priorit<br>abled<br>5'<br>smitter Interru | ny interrupt)    | rity bits       |                 |       |

| bit 6-4<br>bit 3 | 000 = Interru<br>Unimplemen<br>AD1IP<2:0>:<br>111 = Interru<br>•<br>•<br>001 = Interru<br>000 = Interru<br>Unimplemen<br>U1TXIP<2:0> | pt source is disa<br><b>ited:</b> Read as 'co<br>ADC1 Convers<br>pt is priority 7 (h<br>pt is priority 1<br>pt source is disa<br><b>ited:</b> Read as 'co<br>>: UART1 Trans<br>pt is priority 7 (h | )'<br>sion Complete<br>nighest priorit<br>abled<br>5'<br>smitter Interru | ny interrupt)    | rity bits       |                 |       |

| REGISTER     | 7-25: IPC1   | 0: INTERRUPT                           | PRIORITY        | CONTROL           | REGISTER 1      | 0               |       |

|--------------|--------------|----------------------------------------|-----------------|-------------------|-----------------|-----------------|-------|

| U-0          | R/W-1        | R/W-0                                  | R/W-0           | U-0               | R/W-1           | R/W-0           | R/W-0 |

| —            |              | OC7IP<2:0>                             |                 | —                 |                 | OC6IP<2:0>      |       |

| bit 15       |              |                                        |                 |                   |                 |                 | bit   |

| U-0          | R/W-1        | R/W-0                                  | R/W-0           | U-0               | R/W-1           | R/W-0           | R/W-0 |

|              |              | OC5IP<2:0>                             |                 |                   |                 | IC6IP<2:0>      |       |

| bit 7        |              |                                        |                 |                   |                 |                 | bit   |

| Legend:      |              |                                        |                 |                   |                 |                 |       |

| R = Readab   | le bit       | W = Writable                           | bit             | U = Unimple       | mented bit, rea | ad as '0'       |       |

| -n = Value a | t POR        | '1' = Bit is set                       |                 | '0' = Bit is cle  | eared           | x = Bit is unkn | own   |

|              |              |                                        |                 |                   |                 |                 |       |

| bit 15       | Unimpleme    | nted: Read as 'o                       | )'              |                   |                 |                 |       |

| bit 14-12    | OC7IP<2:0>   | Output Compa                           | re Channel      | 7 Interrupt Prio  | rity bits       |                 |       |

|              | 111 = Interr | upt is priority 7 (I                   | nighest priori  | ty interrupt)     |                 |                 |       |

|              | •            |                                        |                 |                   |                 |                 |       |

|              | •            |                                        |                 |                   |                 |                 |       |

|              | 001 = Interr | upt is priority 1                      |                 |                   |                 |                 |       |

|              |              | upt source is dis                      | abled           |                   |                 |                 |       |

| bit 11       | Unimpleme    | nted: Read as 'o                       | )'              |                   |                 |                 |       |

| bit 10-8     | OC6IP<2:0>   | Output Compa                           | re Channel      | 6 Interrupt Prio  | rity bits       |                 |       |

|              | 111 = Interr | upt is priority 7 (I                   | nighest priori  | ty interrupt)     |                 |                 |       |

|              | •            |                                        |                 |                   |                 |                 |       |

|              | •            |                                        |                 |                   |                 |                 |       |

|              |              | upt is priority 1<br>upt source is dis | abled           |                   |                 |                 |       |

| bit 7        |              | nted: Read as '                        |                 |                   |                 |                 |       |

| bit 6-4      | -            | Output Compa                           |                 | 5 Interrunt Prio  | rity hits       |                 |       |

|              |              | upt is priority 7 (I                   |                 | -                 | inty bito       |                 |       |

|              | •            |                                        | ing noor priori | ty monapty        |                 |                 |       |

|              | •            |                                        |                 |                   |                 |                 |       |

|              | •            |                                        |                 |                   |                 |                 |       |

|              |              | upt is priority 1<br>upt source is dis | abled           |                   |                 |                 |       |

| bit 3        |              | nted: Read as '                        |                 |                   |                 |                 |       |

| bit 2-0      | -            | Input Capture C                        |                 | errunt Priority h | nite            |                 |       |

| 511 2 0      |              | upt is priority 7 (I                   |                 |                   | 5113            |                 |       |

|              | •            |                                        | gricer priori   |                   |                 |                 |       |

|              | •            |                                        |                 |                   |                 |                 |       |

|              | •            | unt in mul-site of                     |                 |                   |                 |                 |       |

|              |              | upt is priority 1<br>upt source is dis | abled           |                   |                 |                 |       |

|              | uuu – men    |                                        |                 |                   |                 |                 |       |

| R/W-0        | R/W-0                          | R/W-0            | R/W-0          | R/W-0                                  | U-0              | U-0              | U-0     |

|--------------|--------------------------------|------------------|----------------|----------------------------------------|------------------|------------------|---------|

| CHEN         | SIZE                           | DIR              | HALF           | NULLW                                  | _                |                  | _       |

| oit 15       | ·                              |                  |                | •                                      |                  | •                | bit     |

| U-0          | U-0                            | R/W-0            | R/W-0          | U-0                                    | U-0              | R/W-0            | R/W-0   |

| _            | _                              | -                | E<1:0>         | _                                      | _                | MODE             |         |

| bit 7        |                                |                  |                |                                        |                  |                  | bit     |

| Legend:      |                                |                  |                |                                        |                  |                  |         |

| R = Readab   | le bit                         | W = Writable     | bit            | U = Unimplen                           | nented bit, rea  | d as '0'         |         |

| -n = Value a | t POR                          | '1' = Bit is set |                | '0' = Bit is clea                      | ared             | x = Bit is unkn  | own     |

|              |                                |                  |                |                                        |                  |                  |         |

| bit 15       | CHEN: Chan                     |                  |                |                                        |                  |                  |         |

|              | 1 = Channel e<br>0 = Channel e |                  |                |                                        |                  |                  |         |

| bit 14       |                                | ansfer Size bi   | t              |                                        |                  |                  |         |

|              | 1 = Byte                       |                  |                |                                        |                  |                  |         |

|              | 0 = Word                       |                  |                |                                        |                  |                  |         |

| bit 13       |                                |                  |                | ation bus select                       |                  |                  |         |

|              |                                |                  |                | to peripheral ad<br>o DMA RAM ad       |                  |                  |         |

| bit 12       | HALF: Early                    | Block Transfer   | Complete Inte  | errupt Select bit                      | t                |                  |         |

|              |                                |                  |                | ipt when half of<br>ipt when all of th |                  |                  |         |

| bit 11       |                                | Data Peripher    |                |                                        |                  |                  |         |

|              |                                | write to periph  |                |                                        | write (DIR bit ı | must also be cle | ar)     |

| bit 10-6     | -                              | ted: Read as '   | 0'             |                                        |                  |                  |         |

| bit 5-4      | AMODE<1:0                      | >: DMA Chann     | el Operating I | Mode Select bit                        | S                |                  |         |

|              | 11 = Reserve                   | -                |                |                                        |                  |                  |         |

|              |                                | ral Indirect Add | •              |                                        |                  |                  |         |

|              |                                | Indirect witho   |                |                                        |                  |                  |         |

| bit 3-2      |                                | ted: Read as '   |                |                                        |                  |                  |         |

| bit 1-0      | -                              |                  |                | ode Select bits                        |                  |                  |         |

|              |                                |                  |                |                                        | ansfer from/to e | each DMA RAM     | buffer) |

|              | 10 = Continue                  | ous, Ping-Pong   | g modes enab   | led                                    |                  |                  |         |

|              |                                | ot, Ping-Pong    |                |                                        |                  |                  |         |

|              |                                | ous, Ping-Pong   | y modes ulsat  | Jieu                                   |                  |                  |         |

### REGISTER 8-1: DMAxCON: DMA CHANNEL x CONTROL REGISTER

### 10.0 POWER-SAVING FEATURES

Note: This data sheet summarizes the features of the dsPIC33FJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9.

"Watchdog Timer and Power-Saving Modes" (DS70196) in the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The dsPIC33FJXXXGPX06/X08/X10 devices provide the ability to manage power consumption by selectively managing clocking to the CPU and the peripherals. In general, a lower clock frequency and a reduction in the number of circuits being clocked constitutes lower consumed power. dsPIC33FJXXXGPX06/X08/X10 devices can manage power consumption in four different ways:

- Clock frequency

- Instruction-based Sleep and Idle modes

- Software-controlled Doze mode

- · Selective peripheral control in software

Combinations of these methods can be used to selectively tailor an application's power consumption while still maintaining critical application features, such as timing-sensitive communications.

### 10.1 Clock Frequency and Clock Switching

dsPIC33FJXXXGPX06/X08/X10 devices allow a wide range of clock frequencies to be selected under application control. If the system clock configuration is not locked, users can choose low-power or high-precision oscillators by simply changing the NOSC bits (OSCCON<10:8>). The process of changing a system clock during operation, as well as limitations to the process, are discussed in more detail in **Section 9.0 "Oscillator Configuration"**.

### 10.2 Instruction-Based Power-Saving Modes

dsPIC33FJXXXGPX06/X08/X10 devices have two special power-saving modes that are entered through the execution of a special PWRSAV instruction. Sleep mode stops clock operation and halts all code execution. Idle mode halts the CPU and code execution, but allows peripheral modules to continue operation. The assembly syntax of the PWRSAV instruction is shown in Example 10-1.

**Note:** SLEEP\_MODE and IDLE\_MODE are constants defined in the assembler include file for the selected device.

Sleep and Idle modes can be exited as a result of an enabled interrupt, WDT time-out or a device Reset. When the device exits these modes, it is said to "wake-up".

### 10.2.1 SLEEP MODE

Sleep mode has these features:

- The system clock source is shut down. If an on-chip oscillator is used, it is turned off.

- The device current consumption is reduced to a minimum, provided that no I/O pin is sourcing current.

- The Fail-Safe Clock Monitor does not operate during Sleep mode since the system clock source is disabled.

- The LPRC clock continues to run in Sleep mode if the WDT is enabled.

- The WDT, if enabled, is automatically cleared prior to entering Sleep mode.

- Some device features or peripherals may continue to operate in Sleep mode. This includes items such as the input change notification on the I/O ports, or peripherals that use an external clock input. Any peripheral that requires the system clock source for its operation is disabled in Sleep mode.

The device will wake-up from Sleep mode on any of these events:

- Any interrupt source that is individually enabled.

- Any form of device Reset.

- A WDT time-out.

On wake-up from Sleep, the processor restarts with the same clock source that was active when Sleep mode was entered.

### EXAMPLE 10-1: PWRSAV INSTRUCTION SYNTAX

PWRSAV #SLEEP\_MODE PWRSAV #IDLE MODE ; Put the device into SLEEP mode ; Put the device into IDLE mode

| REGISTER     |                  |                                      |          |                   |                 |                | <b>D</b> 447 <b>C</b> |

|--------------|------------------|--------------------------------------|----------|-------------------|-----------------|----------------|-----------------------|

| R/W-0        | R/W-0            | R/W-0                                | R/W-0    | R/W-0             | U-0             | U-0            | R/W-0                 |

| T5MD         | T4MD             | T3MD                                 | T2MD     | T1MD              |                 | —              | DCIMD                 |

| bit 15       |                  |                                      |          |                   |                 |                | bita                  |

| R/W-0        | R/W-0            | R/W-0                                | R/W-0    | R/W-0             | R/W-0           | R/W-0          | R/W-0                 |

| I2C1MD       | U2MD             | U1MD                                 | SPI2MD   | SPI1MD            | C2MD            | C1MD           | AD1MD                 |

| bit 7        |                  | -                                    |          |                   |                 | -              | bit                   |

| Legend:      |                  |                                      |          |                   |                 |                |                       |

| R = Readab   | le bit           | W = Writable                         | bit      | U = Unimplen      | nented bit, rea | d as '0'       |                       |

| -n = Value a | t POR            | '1' = Bit is set                     | t        | '0' = Bit is clea | ared            | x = Bit is unk | nown                  |

| bit 15       | T5MD. Time       | r5 Module Disa                       | ble hit  |                   |                 |                |                       |

| DIL 15       |                  | nodule is disabl                     |          |                   |                 |                |                       |

|              |                  | nodule is enable                     |          |                   |                 |                |                       |

| bit 14       | T4MD: Time       | r4 Module Disa                       | ble bit  |                   |                 |                |                       |

|              | -                | nodule is disabl<br>nodule is enable |          |                   |                 |                |                       |

| bit 13       |                  | r3 Module Disa                       |          |                   |                 |                |                       |

| bit To       | 1 = Timer3 n     | nodule is disabl                     | ed       |                   |                 |                |                       |

| bit 12       |                  | r2 Module Disa                       |          |                   |                 |                |                       |

|              | -                | nodule is disabl                     |          |                   |                 |                |                       |

|              | -                | nodule is enable                     |          |                   |                 |                |                       |

| bit 11       | T1MD: Time       | r1 Module Disa                       | ble bit  |                   |                 |                |                       |

|              | -                | nodule is disabl<br>nodule is enable |          |                   |                 |                |                       |

| bit 10-9     |                  | nted: Read as '                      |          |                   |                 |                |                       |

| bit 8        | -                | Module Disabl                        |          |                   |                 |                |                       |

|              |                  | ule is disabled<br>ule is enabled    |          |                   |                 |                |                       |

| bit 7        |                  | 1 Module Disal                       | ole bit  |                   |                 |                |                       |

|              | $1 = I^2 C1 mod$ | dule is disabled                     |          |                   |                 |                |                       |

| bit 6        |                  | T2 Module Disa                       | able bit |                   |                 |                |                       |

|              |                  | nodule is disab                      |          |                   |                 |                |                       |

|              | 0 = UART2 r      | nodule is enabl                      | ed       |                   |                 |                |                       |

| bit 5        | U1MD: UAR        | T1 Module Disa                       | able bit |                   |                 |                |                       |

|              | -                | nodule is disab<br>nodule is enabl   |          |                   |                 |                |                       |

| bit 4        | SPI2MD: SP       | 12 Module Disa                       | ble bit  |                   |                 |                |                       |

|              |                  | dule is disablec<br>dule is enabled  |          |                   |                 |                |                       |

| bit 3        |                  | 11 Module Disa                       |          |                   |                 |                |                       |

|              | 1 = SPI1 mo      | dule is disabled                     | 1        |                   |                 |                |                       |

| bit 2        |                  | N2 Module Disa                       |          |                   |                 |                |                       |

|              | _                | nodule is disab                      |          |                   |                 |                |                       |

#### DIALDI E AANTDAL DEALATED 4

### REGISTER 18-1: UXMODE: UARTX MODE REGISTER (CONTINUED)

| bit 4   | URXINV: Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                                                                          |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | <ul> <li>BRGH: High Baud Rate Enable bit</li> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul> |

| bit 2-1 | <pre>PDSEL&lt;1:0&gt;: Parity and Data Selection bits 11 = 9-bit data, no parity 10 = 8-bit data, odd parity 01 = 8-bit data, even parity 00 = 8-bit data, no parity</pre>                                                  |

| bit 0   | <b>STSEL:</b> Stop Bit Selection bit<br>1 = Two Stop bits<br>0 = One Stop bit                                                                                                                                               |

- **Note 1:** Refer to **Section 17. "UART"** (DS70188) in the *"dsPIC33F Family Reference Manual"* for information on enabling the UART module for receive or transmit operation.

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

### 22.2 On-Chip Voltage Regulator

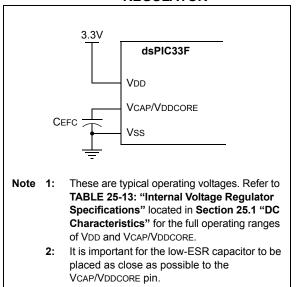

All of the dsPIC33FJXXXGPX06/X08/X10 devices power their core digital logic at a nominal 2.5V. This may create an issue for designs that are required to operate at a higher typical voltage, such as 3.3V. To simplify system design, all devices in the dsPIC33FJXXXGPX06/X08/X10 family incorporate an on-chip regulator that allows the device to run its core logic from VDD.

The regulator provides power to the core from the other VDD pins. The regulator requires that a low-ESR (less than 5 ohms) capacitor (such as tantalum or ceramic) be connected to the VCAP/VDDCORE pin (Figure 22-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in Table 25-13 of Section 25.0 "Electrical Characteristics".

| Note: | It is important for the low-ESR capacitor to |  |  |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|--|--|

|       | be placed as close as possible to the        |  |  |  |  |  |  |  |

|       | VCAP/VDDCORE pin.                            |  |  |  |  |  |  |  |

On a POR, it takes approximately 20  $\mu$ s for the on-chip voltage regulator to generate an output voltage. During this time, designated as TSTARTUP, code execution is disabled. TSTARTUP is applied every time the device resumes operation after any power-down.

#### FIGURE 22-1: CONNECTIONS FOR THE ON-CHIP VOLTAGE REGULATOR<sup>(1)</sup>

### 22.3 BOR: Brown-Out Reset

The BOR (Brown-out Reset) module is based on an internal voltage reference circuit that monitors the regulated voltage VCAP/VDDCORE. The main purpose of the BOR module is to generate a device Reset when a brown-out condition occurs. Brown-out conditions are generally caused by glitches on the AC mains (i.e., missing portions of the AC cycle waveform due to bad power transmission lines or voltage sags due to excessive current draw when a large inductive load is turned on).

A BOR will generate a Reset pulse which will reset the device. The BOR will select the clock source, based on the device Configuration bit values (FNOSC<2:0> and POSCMD<1:0>). Furthermore, if an oscillator mode is selected, the BOR will activate the Oscillator Start-up Timer (OST). The system clock is held until OST expires. If the PLL is used, then the clock will be held until the LOCK bit (OSCCON<5>) is '1'.

Concurrently, the PWRT time-out (TPWRT) will be applied before the internal Reset is released. If TPWRT = 0 and a crystal oscillator is being used, then a nominal delay of TFSCM = 100 is applied. The total delay in this case is TFSCM.

The BOR Status bit (RCON<1>) will be set to indicate that a BOR has occurred. The BOR circuit continues to operate while in Sleep or Idle modes and will reset the device should VDD fall below the BOR threshold voltage.

| Field | Description                                                                                                                                                                                                                                              |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wm*Wm | Multiplicand and Multiplier working register pair for Square instructions ∈ {W4 * W4,W5 * W5,W6 * W6,W7 * W7}                                                                                                                                            |

| Wm*Wn | Multiplicand and Multiplier working register pair for DSP instructions ∈<br>{W4 * W5,W4 * W6,W4 * W7,W5 * W6,W5 * W7,W6 * W7}                                                                                                                            |

| Wn    | One of 16 working registers ∈ {W0W15}                                                                                                                                                                                                                    |

| Wnd   | One of 16 destination working registers ∈ {W0W15}                                                                                                                                                                                                        |

| Wns   | One of 16 source working registers ∈ {W0W15}                                                                                                                                                                                                             |

| WREG  | W0 (working register used in file register instructions)                                                                                                                                                                                                 |

| Ws    | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                                                                                                                                                                                             |

| Wso   | Source W register ∈<br>{ Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }                                                                                                                                                                          |

| Wx    | X data space prefetch address register for DSP instructions<br>∈ {[W8]+ = 6, [W8]+ = 4, [W8]+ = 2, [W8], [W8]- = 6, [W8]- = 4, [W8]- = 2,<br>[W9]+ = 6, [W9]+ = 4, [W9]+ = 2, [W9], [W9]- = 6, [W9]- = 4, [W9]- = 2,<br>[W9 + W12], none}                |

| Wxd   | X data space prefetch destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                 |

| Wy    | Y data space prefetch address register for DSP instructions<br>∈ {[W10]+ = 6, [W10]+ = 4, [W10]+ = 2, [W10], [W10]- = 6, [W10]- = 4, [W10]- = 2,<br>[W11]+ = 6, [W11]+ = 4, [W11]+ = 2, [W11], [W11]- = 6, [W11]- = 4, [W11]- = 2,<br>[W11 + W12], none} |

| Wyd   | Y data space prefetch destination register for DSP instructions ∈ {W4W7}                                                                                                                                                                                 |

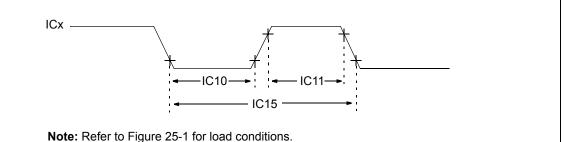

### FIGURE 25-6: INPUT CAPTURE (CAPx) TIMING CHARACTERISTICS

### TABLE 25-25: INPUT CAPTURE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                     | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ |              |     |       |                                  |  |  |