Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT             |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 18x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

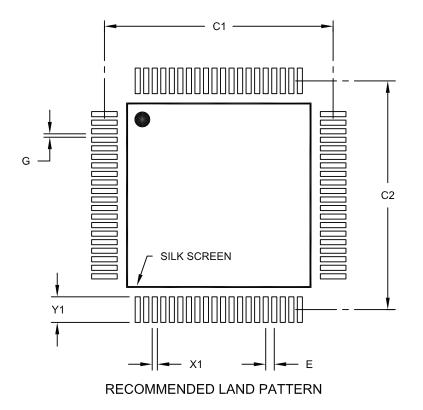

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp206-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the dsPIC33FJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the latest family reference sections of the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

This document contains device specific information for the following devices:

- dsPIC33FJ64GP206

- dsPIC33FJ64GP306

- dsPIC33FJ64GP310

- dsPIC33FJ64GP706

- dsPIC33FJ64GP708

- dsPIC33FJ64GP710

- dsPIC33FJ128GP206

- dsPIC33FJ128GP306

- dsPIC33FJ128GP310

- dsPIC33FJ128GP706

- dsPIC33FJ128GP708

- dsPIC33FJ128GP710

- dsPIC33FJ256GP506

- dsPIC33FJ256GP510

- dsPIC33FJ256GP710

The dsPIC33FJXXXGPX06/X08/X10 General Purpose Family of device includes devices with a wide range of pin counts (64, 80 and 100), different program memory sizes (64 Kbytes, 128 Kbytes and 256 Kbytes) and different RAM sizes (8 Kbytes, 16 Kbytes and 30 Kbytes). This feature makes the family suitable for a wide variety of high-performance digital signal control applications. The device is pin compatible with the PIC24H family of devices, and also share a very high degree of compatibility with the dsPIC30F family devices. This allows for easy migration between device families as may be necessitated by the specific functionality, computational resource and system cost requirements of the application.

The dsPIC33FJXXXGPX06/X08/X10 device family employs a powerful 16-bit architecture that seamlessly integrates the control features of a Microcontroller (MCU) with the computational capabilities of a Digital Signal Processor (DSP). The resulting functionality is ideal for applications that rely on high-speed, repetitive computations, as well as control.

The DSP engine, dual 40-bit accumulators, hardware support for division operations, barrel shifter, 17 x 17 multiplier, a large array of 16-bit working registers and a wide variety of data addressing modes, together provide the dsPIC33FJXXXGPX06/X08/X10 Central Processing Unit (CPU) with extensive mathematical processing capability. Flexible and deterministic interrupt handling, coupled with a powerful array of peripherals, renders the dsPIC33FJXXXGPX06/X08/X10 devices suitable for control applications. Further, Direct Memory Access (DMA) enables overhead-free transfer of data between several peripherals and a dedicated DMA RAM. Reliable, field programmable Flash program memory ensures scalability of applications that use dsPIC33FJXXXGPX06/X08/X10 devices.

Figure 1-1 illustrates a general block diagram of the various core and peripheral modules in the dsPIC33FJXXXGPX06/X08/X10 family of devices. Table 1-1 provides the functions of the various pins illustrated in the pinout diagrams.

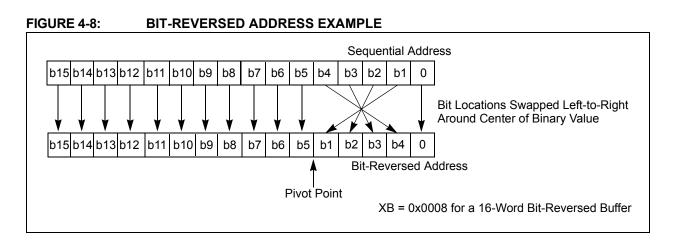

| Normal Address |    |    |    |         |    | Bit-Reversed Address |    |    |         |  |  |

|----------------|----|----|----|---------|----|----------------------|----|----|---------|--|--|

| A3             | A2 | A1 | A0 | Decimal | A3 | A2                   | A1 | A0 | Decimal |  |  |

| 0              | 0  | 0  | 0  | 0       | 0  | 0                    | 0  | 0  | 0       |  |  |

| 0              | 0  | 0  | 1  | 1       | 1  | 0                    | 0  | 0  | 8       |  |  |

| 0              | 0  | 1  | 0  | 2       | 0  | 1                    | 0  | 0  | 4       |  |  |

| 0              | 0  | 1  | 1  | 3       | 1  | 1                    | 0  | 0  | 12      |  |  |

| 0              | 1  | 0  | 0  | 4       | 0  | 0                    | 1  | 0  | 2       |  |  |

| 0              | 1  | 0  | 1  | 5       | 1  | 0                    | 1  | 0  | 10      |  |  |

| 0              | 1  | 1  | 0  | 6       | 0  | 1                    | 1  | 0  | 6       |  |  |

| 0              | 1  | 1  | 1  | 7       | 1  | 1                    | 1  | 0  | 14      |  |  |

| 1              | 0  | 0  | 0  | 8       | 0  | 0                    | 0  | 1  | 1       |  |  |

| 1              | 0  | 0  | 1  | 9       | 1  | 0                    | 0  | 1  | 9       |  |  |

| 1              | 0  | 1  | 0  | 10      | 0  | 1                    | 0  | 1  | 5       |  |  |

| 1              | 0  | 1  | 1  | 11      | 1  | 1                    | 0  | 1  | 13      |  |  |

| 1              | 1  | 0  | 0  | 12      | 0  | 0                    | 1  | 1  | 3       |  |  |

| 1              | 1  | 0  | 1  | 13      | 1  | 0                    | 1  | 1  | 11      |  |  |

| 1              | 1  | 1  | 0  | 14      | 0  | 1                    | 1  | 1  | 7       |  |  |

| 1              | 1  | 1  | 1  | 15      | 1  | 1                    | 1  | 1  | 15      |  |  |

| Flag Bit          | Setting Event                                        | Clearing Event               |  |  |  |  |  |

|-------------------|------------------------------------------------------|------------------------------|--|--|--|--|--|

| TRAPR (RCON<15>)  | Trap conflict event                                  | POR, BOR                     |  |  |  |  |  |

| IOPUWR (RCON<14>) | Illegal opcode or uninitialized<br>W register access | POR, BOR                     |  |  |  |  |  |

| EXTR (RCON<7>)    | MCLR Reset                                           | POR                          |  |  |  |  |  |

| SWR (RCON<6>)     | RESET instruction                                    | POR, BOR                     |  |  |  |  |  |

| WDTO (RCON<4>)    | WDT time-out                                         | PWRSAV instruction, POR, BOR |  |  |  |  |  |

| SLEEP (RCON<3>)   | PWRSAV #SLEEP instruction                            | POR, BOR                     |  |  |  |  |  |

| IDLE (RCON<2>)    | PWRSAV #IDLE instruction                             | POR, BOR                     |  |  |  |  |  |

| BOR (RCON<1>)     | BOR, POR                                             | —                            |  |  |  |  |  |

| POR (RCON<0>)     | POR                                                  | -                            |  |  |  |  |  |

#### TABLE 6-1:RESET FLAG BIT OPERATION

Note: All Reset flag bits may be set or cleared by the user software.

### 6.1 Clock Source Selection at Reset

If clock switching is enabled, the system clock source at device Reset is chosen, as shown in Table 6-2. If clock switching is disabled, the system clock source is always selected according to the oscillator Configuration bits. Refer to **Section 9.0 "Oscillator Configuration"** for further details.

# TABLE 6-2:OSCILLATOR SELECTION VSTYPE OF RESET (CLOCK<br/>SWITCHING ENABLED)

| Reset Type | Clock Source Determinant      |

|------------|-------------------------------|

| POR        | Oscillator Configuration bits |

| BOR        | (FNOSC<2:0>)                  |

| MCLR       | COSC Control bits             |

| WDTR       | (OSCCON<14:12>)               |

| SWR        |                               |

### 6.2 Device Reset Times

The Reset times for various types of device Reset are <u>summarized</u> in Table 6-3. The system Reset signal, SYSRST, is released after the POR and PWRT delay times expire.

The time at which the device actually begins to execute code also depends on the system oscillator delays, which include the Oscillator Start-up Timer (OST) and the PLL lock time. The OST and PLL lock times occur in parallel with the applicable SYSRST delay times.

The FSCM delay determines the time at which the FSCM begins to monitor the system clock source after the SYSRST signal is released.

| REGISTER 7                           | -4: INTCC                                                                                                                                            | N2: INTERF                                           |                                                                                                     | ROL REGIST                         | ER 2             |                 |        |  |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------------------------------|------------------|-----------------|--------|--|

| R/W-0                                | R-0                                                                                                                                                  | U-0                                                  | U-0                                                                                                 | U-0                                | U-0              | U-0             | U-0    |  |

| ALTIVT                               | DISI                                                                                                                                                 | —                                                    | _                                                                                                   | _                                  |                  | _               | —      |  |

| bit 15                               |                                                                                                                                                      |                                                      | ÷                                                                                                   |                                    |                  |                 | bit 8  |  |

| U-0                                  | U-0                                                                                                                                                  | U-0                                                  | R/W-0                                                                                               | R/W-0                              | R/W-0            | R/W-0           | R/W-0  |  |

| _                                    | —                                                                                                                                                    | _                                                    | INT4EP                                                                                              | INT3EP                             | INT2EP           | INT1EP          | INT0EP |  |

| bit 7                                |                                                                                                                                                      |                                                      |                                                                                                     |                                    |                  |                 | bit 0  |  |

| Legend:                              |                                                                                                                                                      |                                                      |                                                                                                     |                                    |                  |                 |        |  |

| R = Readable                         | bit                                                                                                                                                  | W = Writable                                         | bit                                                                                                 | U = Unimpler                       | nented bit, read | as '0'          |        |  |

| -n = Value at I                      | POR                                                                                                                                                  | '1' = Bit is se                                      | t                                                                                                   | '0' = Bit is cle                   | ared             | x = Bit is unkr | nown   |  |

| bit 14<br>bit 13-5<br>bit 4<br>bit 3 | 0 = Use stand<br>DISI: DISI In<br>1 = DISI inst<br>0 = DISI inst<br>Unimplemen<br>INT4EP: Exte<br>1 = Interrupt o<br>INT3EP: Exte<br>1 = Interrupt o | on negative ec<br>on positive ed                     | vector table<br>us bit<br>ve<br>active<br>'0'<br>4 Edge Detect<br>lge<br>ge<br>3 Edge Detect<br>lge | Polarity Select<br>Polarity Select |                  |                 |        |  |

| bit 2                                | 1 = Interrupt of                                                                                                                                     | ernal Interrupt<br>on negative ec<br>on positive edg | lge                                                                                                 | Polarity Select                    | t bit            |                 |        |  |

| bit 1                                | INT1EP: External Interrupt 1 Edge Detect Polarity Select bit<br>1 = Interrupt on negative edge<br>0 = Interrupt on positive edge                     |                                                      |                                                                                                     |                                    |                  |                 |        |  |

| bit 0                                | 1 = Interrupt                                                                                                                                        | ernal Interrupt<br>on negative ec<br>on positive ed  | lge                                                                                                 | Polarity Select                    | t bit            |                 |        |  |

| 11.0          |                                                                                              |             |                |       |               |      |                            |               |  |

|---------------|----------------------------------------------------------------------------------------------|-------------|----------------|-------|---------------|------|----------------------------|---------------|--|

| U-0           | R/W-0 R/W-0                                                                                  | R/W-0       | R/W-0          |       | R/W-0         |      | R/W-0                      | R/W-0         |  |

| <br>bit 15    | DMA1IE AD1IE                                                                                 | U1TXIE      | U1RXIE         |       | SPI1IE        |      | SPI1EIE                    | T3IE<br>bit 8 |  |

|               |                                                                                              |             |                |       |               |      |                            | DILC          |  |

| R/W-0         | R/W-0 R/W-0                                                                                  | R/W-0       | R/W-0          |       | R/W-0         |      | R/W-0                      | R/W-0         |  |

| T2IE          | - 1                                                                                          | DMA0IE      | T1IE           |       | OC1IE         |      | IC1IE                      | INT0IE        |  |

| bit 7         |                                                                                              |             |                |       |               |      |                            | bit (         |  |

| Legend:       |                                                                                              |             |                |       |               |      |                            |               |  |

| R = Readable  | e bit W = Writable bit                                                                       |             | U = Unimple    | emer  | nted bit, rea | ad a | is '0'                     |               |  |

| -n = Value at | POR '1' = Bit is set                                                                         |             | '0' = Bit is c | leare | ed            | >    | <pre>c = Bit is unkn</pre> | own           |  |

| L:4 / F       | Unimplemented: Deed op (o)                                                                   |             |                |       |               |      |                            |               |  |

| bit 15        | Unimplemented: Read as '0'                                                                   | Transform   |                |       | En abla bii   |      |                            |               |  |

| bit 14        | <b>DMA1IE:</b> DMA Channel 1 Data<br>1 = Interrupt request enabled                           | Transfer C  | omplete inte   | rrupt | Enable bit    |      |                            |               |  |

|               | 0 = Interrupt request not enable                                                             | ed          |                |       |               |      |                            |               |  |

| bit 13        | AD1IE: ADC1 Conversion Com                                                                   |             | upt Enable b   | it    |               |      |                            |               |  |

|               | 1 = Interrupt request enabled                                                                |             |                |       |               |      |                            |               |  |

|               | 0 = Interrupt request not enable                                                             |             |                |       |               |      |                            |               |  |

| bit 12        | U1TXIE: UART1 Transmitter In                                                                 | terrupt Ena | ble bit        |       |               |      |                            |               |  |

|               | <ul><li>1 = Interrupt request enabled</li><li>0 = Interrupt request not enable</li></ul>     | )d          |                |       |               |      |                            |               |  |

| bit 11        | <b>U1RXIE:</b> UART1 Receiver Inter                                                          | rupt Enable | e bit          |       |               |      |                            |               |  |

|               | <ol> <li>I = Interrupt request enabled</li> <li>Interrupt request not enabled</li> </ol>     |             |                |       |               |      |                            |               |  |

| bit 10        | SPI1IE: SPI1 Event Interrupt E                                                               |             |                |       |               |      |                            |               |  |

|               | 1 = Interrupt request enabled                                                                |             |                |       |               |      |                            |               |  |

|               | 0 = Interrupt request not enable                                                             | ed          |                |       |               |      |                            |               |  |

| bit 9         | SPI1EIE: SPI1 Error Interrupt E                                                              | nable bit   |                |       |               |      |                            |               |  |

|               | 1 = Interrupt request enabled                                                                |             |                |       |               |      |                            |               |  |

|               | 0 = Interrupt request not enable                                                             |             |                |       |               |      |                            |               |  |

| bit 8         | <b>T3IE:</b> Timer3 Interrupt Enable b                                                       | lit         |                |       |               |      |                            |               |  |

|               | <ol> <li>I = Interrupt request enabled</li> <li>0 = Interrupt request not enabled</li> </ol> |             |                |       |               |      |                            |               |  |

| bit 7         | T2IE: Timer2 Interrupt Enable b                                                              |             |                |       |               |      |                            |               |  |

|               | 1 = Interrupt request enabled                                                                |             |                |       |               |      |                            |               |  |

|               | 0 = Interrupt request not enable                                                             |             |                |       |               |      |                            |               |  |

| bit 6         | OC2IE: Output Compare Channel 2 Interrupt Enable bit                                         |             |                |       |               |      |                            |               |  |

|               | <ul> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enable</li> </ul>  | h           |                |       |               |      |                            |               |  |

| bit 5         | IC2IE: Input Capture Channel 2                                                               |             | nable bit      |       |               |      |                            |               |  |

|               | 1 = Interrupt request enabled                                                                |             |                |       |               |      |                            |               |  |

|               | 0 = Interrupt request not enable                                                             | ed .        |                |       |               |      |                            |               |  |

| bit 4         | DMA0IE: DMA Channel 0 Data                                                                   | Transfer C  | omplete Inte   | rrupt | Enable bit    |      |                            |               |  |

|               | <ul> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enable</li> </ul>  | ed          |                |       |               |      |                            |               |  |

|               |                                                                                              |             |                |       |               |      |                            |               |  |

| bit 3         | T1IE: Timer1 Interrupt Enable b                                                              |             |                |       |               |      |                            |               |  |

| U-0          | R/W-1                                                                                                                                                | R/W-0                                                                                                                                   | R/W-0          | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------|------------------|-----------------|-----------------|-------|--|--|--|--|

| _            |                                                                                                                                                      | T6IP<2:0>                                                                                                                               |                | _                |                 | DMA4IP<2:0>     |       |  |  |  |  |

| bit 15       |                                                                                                                                                      |                                                                                                                                         |                |                  |                 |                 | bit 8 |  |  |  |  |

|              |                                                                                                                                                      |                                                                                                                                         |                |                  |                 |                 |       |  |  |  |  |

| U-0          | U-0                                                                                                                                                  | U-0                                                                                                                                     | U-0            | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |

| —            | —                                                                                                                                                    | _                                                                                                                                       | —              | —                |                 | OC8IP<2:0>      |       |  |  |  |  |

| bit 7        |                                                                                                                                                      |                                                                                                                                         |                |                  |                 |                 | bit ( |  |  |  |  |

| Legend:      |                                                                                                                                                      |                                                                                                                                         |                |                  |                 |                 |       |  |  |  |  |

| R = Readab   | le bit                                                                                                                                               | W = Writable                                                                                                                            | bit            | U = Unimpler     | nented bit, rea | d as '0'        |       |  |  |  |  |

| -n = Value a | t POR                                                                                                                                                | '1' = Bit is set                                                                                                                        |                | '0' = Bit is cle |                 | x = Bit is unkr | nown  |  |  |  |  |

|              |                                                                                                                                                      |                                                                                                                                         |                |                  |                 |                 |       |  |  |  |  |

| bit 15       | Unimplemen                                                                                                                                           | ited: Read as 'o                                                                                                                        | )'             |                  |                 |                 |       |  |  |  |  |

| bit 14-12    | T6IP<2:0>: ⊺                                                                                                                                         | ïmer6 Interrupt                                                                                                                         | Priority bits  |                  |                 |                 |       |  |  |  |  |

|              | <pre>111 = Interrupt is priority 7 (highest priority interrupt)</pre>                                                                                |                                                                                                                                         |                |                  |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                                    |                                                                                                                                         |                |                  |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                                    |                                                                                                                                         |                |                  |                 |                 |       |  |  |  |  |

|              |                                                                                                                                                      | pt is priority 1<br>pt source is dis                                                                                                    | abled          |                  |                 |                 |       |  |  |  |  |

| bit 11       | Unimplemen                                                                                                                                           | ited: Read as 'o                                                                                                                        | )'             |                  |                 |                 |       |  |  |  |  |

| bit 10-8     | DMA4IP<2:0                                                                                                                                           | >: DMA Chann                                                                                                                            | el 4 Data Trar | nsfer Complete   | Interrupt Prior | ity bits        |       |  |  |  |  |

|              | <b>DMA4IP&lt;2:0&gt;:</b> DMA Channel 4 Data Transfer Complete Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                                                                                                                                         |                |                  |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                                    |                                                                                                                                         |                |                  |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                                    |                                                                                                                                         |                |                  |                 |                 |       |  |  |  |  |

|              | •<br>001 = Interrupt is priority 1                                                                                                                   |                                                                                                                                         |                |                  |                 |                 |       |  |  |  |  |

|              |                                                                                                                                                      | pt source is dis                                                                                                                        | abled          |                  |                 |                 |       |  |  |  |  |

| bit 7-3      | Unimplemen                                                                                                                                           | ted: Read as '                                                                                                                          | )'             |                  |                 |                 |       |  |  |  |  |

| bit 2-0      | OC8IP<2:0>:                                                                                                                                          | : Output Compa                                                                                                                          | re Channel 8   | Interrupt Prior  | ity bits        |                 |       |  |  |  |  |

|              | 111 = Interru                                                                                                                                        | <b>OC8IP&lt;2:0&gt;:</b> Output Compare Channel 8 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                |                  |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                                    |                                                                                                                                         |                |                  |                 |                 |       |  |  |  |  |

|              | •                                                                                                                                                    |                                                                                                                                         |                |                  |                 |                 |       |  |  |  |  |

|              | 001 = Interru                                                                                                                                        | pt is priority 1                                                                                                                        |                |                  |                 |                 |       |  |  |  |  |

|              |                                                                                                                                                      |                                                                                                                                         |                |                  |                 |                 |       |  |  |  |  |

| U-0 R/W-1 R/W-0 R/W-0 U-0 U-0 U-0 U-0 U-0<br>U1EIP<2:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | REGISTER      | 7-31: IPC16                              | : INTERRUP1                             |                | CONTROL          | REGISTER 1      | 6               |       |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------------------------------|-----------------------------------------|----------------|------------------|-----------------|-----------------|-------|--|--|

| bit 15 bit 15 bit 15 bit 15 bit 15 bit 15 bit 7 bit 15 bit 10-8 U2EIP<2:0> 0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 U-0 bit 7 bit 10-8 U2EIP<2:0>: UART2 Error Interrupt Priority bits 111 = Interrupt is priority 1 000 = Interrupt is priority 7 (highest priority interrupt) i f 6-4 U1EIP<2:0>: UART1 Error Interrupt Priority bits 111 = Interrupt is priority 7 (highest priority interrupt) i c c c c c c c c c c c c c c c c c c c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | U-0           | U-0                                      | U-0                                     | U-0            | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |

| U-0 R/W-1 R/W-0 R/W-0 U-0 U-0 U-0 U-0 U-0<br>U1EIP<2:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |               | —                                        | —                                       | _              | _                |                 | U2EIP<2:0>      |       |  |  |

| ulter       ulter         bit 7       bit 7         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-11       Unimplemented: Read as '0'       bit 15-11       Unimplemented: Read as '0'         bit 10-8       U2EIP<2:0>: UART2 Error Interrupt Priority bits       111 = Interrupt is priority 7 (highest priority interrupt)         .       .       .         .001 = Interrupt is priority 1       .         .001 = Interrupt source is disabled       .         bit 6-4       U1EIP<2:0>: UART1 Error Interrupt Priority bits         .111 = Interrupt is priority 7 (highest priority interrupt)       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .       .         .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | bit 15        |                                          |                                         |                |                  |                 |                 | bit 8 |  |  |

| ulter       ulter         bit 7       ulter         Legend:       R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-11       Unimplemented: Read as '0'       bit 15-11       Unimplemented: Read as '0'         bit 10-8       U2EIP<2:0>: UART2 Error Interrupt Priority bits       111 = Interrupt is priority 7 (highest priority interrupt)         .       .       .       .         .001 = Interrupt is priority 1       .       .         .001 = Interrupt source is disabled       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .         .       .       .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | U-0           | R/W-1                                    | R/W-0                                   | R/W-0          | U-0              | U-0             | U-0             | U-0   |  |  |

| Legend:<br>R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'<br>-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown<br>bit 15-11 Unimplemented: Read as '0'<br>bit 10-8 U2EIP<2:0>: UART2 Error Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | _             |                                          | U1EIP<2:0>                              |                | _                | _               | _               | _     |  |  |

| R = Readable bit       W = Writable bit       U = Unimplemented bit, read as '0'         -n = Value at POR       '1' = Bit is set       '0' = Bit is cleared       x = Bit is unknown         bit 15-11       Unimplemented: Read as '0'       test is unknown       x = Bit is unknown         bit 15-11       Unimplemented: Read as '0'       test is unknown       x = Bit is unknown         bit 10-8       U2EIP<2:0>: UART2 Error Interrupt Priority bits       111 = Interrupt is priority 7 (highest priority interrupt)       .         .       001 = Interrupt is priority 1       000 = Interrupt source is disabled       .       .         bit 7       Unimplemented: Read as '0'       .       .       .         bit 6-4       U1EIP<2:0>: UART1 Error Interrupt Priority bits       .       .         111 = Interrupt is priority 7 (highest priority interrupt)       .       .         .       .       .       .         .       .       .       .         .       .       .       .         .       .       .       .         .       .       .       .         .       .       .       .         .       .       .       .         .       .       .       . <td>bit 7</td> <td></td> <td></td> <td></td> <td></td> <td></td> <td></td> <td>bit (</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | bit 7         |                                          |                                         |                |                  |                 |                 | bit ( |  |  |

| In a Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown x = Bit is | Legend:       |                                          |                                         |                |                  |                 |                 |       |  |  |

| bit 15-11 Unimplemented: Read as '0'<br>bit 10-8 U2EIP<2:0>: UART2 Error Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | R = Readabl   | le bit                                   | W = Writable                            | bit            | U = Unimple      | mented bit, rea | d as '0'        |       |  |  |

| bit 10-8 U2EIP<2:0>: UART2 Error Interrupt Priority bits 111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -n = Value at | t POR                                    | '1' = Bit is set                        |                | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |  |  |

| <pre>000 = Interrupt source is disabled<br/>bit 7 Unimplemented: Read as '0'<br/>bit 6-4 U1EIP&lt;2:0&gt;: UART1 Error Interrupt Priority bits<br/>111 = Interrupt is priority 7 (highest priority interrupt)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | bit 10-8      | 111 = Interru<br>•<br>•                  | pt is priority 7 (l                     | •              | •                |                 |                 |       |  |  |

| bit 6-4 U1EIP<2:0>: UART1 Error Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |               |                                          |                                         |                |                  |                 |                 |       |  |  |

| <pre>111 = Interrupt is priority 7 (highest priority interrupt)</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | bit 7         | Unimplemen                               | ited: Read as 'o                        | 0'             |                  |                 |                 |       |  |  |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | bit 6-4       | 111 = Interru<br>•<br>•<br>001 = Interru | pt is priority 7 (I<br>pt is priority 1 | highest priori | •                |                 |                 |       |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 3-0       |                                          |                                         |                |                  |                 |                 |       |  |  |

### REGISTER 7-31: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

### 8.0 DIRECT MEMORY ACCESS (DMA)

Note: This data sheet summarizes the features of the dsPIC33FJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 22. "Direct Memory Access (DMA)" (DS70182) in the "dsPIC33F Family Reference Manual", which is available the Microchip from web site (www.microchip.com).

Direct Memory Access (DMA) is a very efficient mechanism of copying data between peripheral SFRs (e.g., UART Receive register, Input Capture 1 buffer), and buffers or variables stored in RAM, with minimal CPU intervention. The DMA controller can automatically copy entire blocks of data without requiring the user software to read or write the peripheral Special Function Registers (SFRs) every time a peripheral interrupt occurs. The DMA controller uses a dedicated bus for data transfers and therefore, does not steal cycles from the code execution flow of the CPU. To exploit the DMA capability, the corresponding user buffers or variables must be located in DMA RAM.

The dsPIC33FJXXXGPX06/X08/X10 peripherals that can utilize DMA are listed in Table 8-1 along with their associated Interrupt Request (IRQ) numbers.

#### TABLE 8-1: PERIPHERALS WITH DMA SUPPORT

| Peripheral         | IRQ Number |

|--------------------|------------|

| INTO               | 0          |

| Input Capture 1    | 1          |

| Input Capture 2    | 5          |

| Output Compare 1   | 2          |

| Output Compare 2   | 6          |

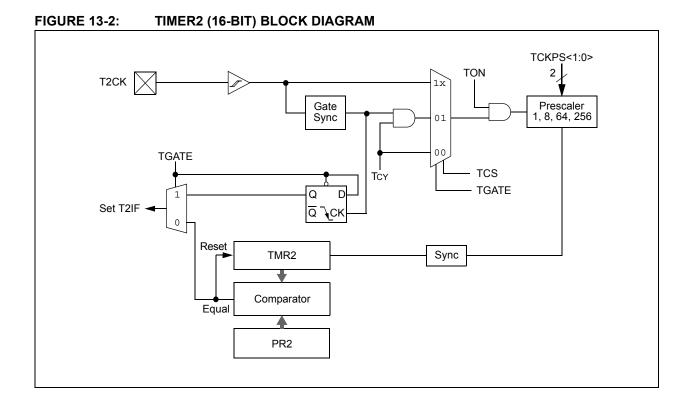

| Timer2             | 7          |

| Timer3             | 8          |

| SPI1               | 10         |

| SPI2               | 33         |

| UART1 Reception    | 11         |

| UART1 Transmission | 12         |

| UART2 Reception    | 30         |

| UART2 Transmission | 31         |

| ADC1               | 13         |

| ADC2               | 21         |

| DCI                | 60         |

| ECAN1 Reception    | 34         |

| ECAN1 Transmission | 70         |

| ECAN2 Reception    | 55         |

| ECAN2 Transmission | 71         |

The DMA controller features eight identical data transfer channels.

Each channel has its own set of control and status registers. Each DMA channel can be configured to copy data either from buffers stored in dual port DMA RAM to peripheral SFRs, or from peripheral SFRs to buffers in DMA RAM.

The DMA controller supports the following features:

- · Word or byte sized data transfers.

- Transfers from peripheral to DMA RAM or DMA RAM to peripheral.

- Indirect Addressing of DMA RAM locations with or without automatic post-increment.

- Peripheral Indirect Addressing In some peripherals, the DMA RAM read/write addresses may be partially derived from the peripheral.

- One-Shot Block Transfers Terminating DMA transfer after one block transfer.

- Continuous Block Transfers Reloading DMA RAM buffer start address after every block transfer is complete.

- Ping-Pong Mode Switching between two DMA RAM start addresses between successive block transfers, thereby filling two buffers alternately.

- Automatic or manual initiation of block transfers

- Each channel can select from 20 possible sources of data sources or destinations.

For each DMA channel, a DMA interrupt request is generated when a block transfer is complete. Alternatively, an interrupt can be generated when half of the block has been filled.

<sup>© 2009</sup> Microchip Technology Inc.

**XT WITH PLL MODE**

**EXAMPLE**

$F_{CY} = \frac{F_{OSC}}{2} = \frac{1}{2} \left( \frac{1000000 \cdot 32}{2 \cdot 2} \right) = 40 \text{ MIPS}$

**EQUATION 9-3:**

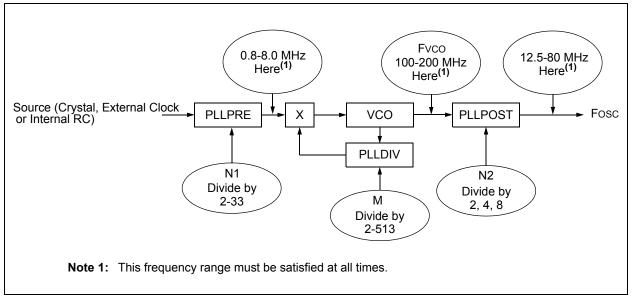

For example, suppose a 10 MHz crystal is being used, with "XT with PLL" being the selected oscillator mode. If PLLPRE<4:0> = 0, then N1 = 2. This yields a VCO input of 10/2 = 5 MHz, which is within the acceptable range of 0.8-8 MHz. If PLLDIV<8:0> = 0x1E, then M = 32. This yields a VCO output of 5 x 32 = 160 MHz, which is within the 100-200 MHz range needed.

If PLLPOST<1:0> = 0, then N2 = 2. This provides a Fosc of 160/2 = 80 MHz. The resultant device operating speed is 80/2 = 40 MIPS.

#### FIGURE 9-2: dsPIC33FJXXXGPX06/X08/X10 PLL BLOCK DIAGRAM

#### TABLE 9-1: CONFIGURATION BIT VALUES FOR CLOCK SELECTION

| Oscillator Mode                                  | Oscillator Source | POSCMD<1:0> | FNOSC<2:0> | Note |

|--------------------------------------------------|-------------------|-------------|------------|------|

| Fast RC Oscillator with Divide-by-N<br>(FRCDIVN) | Internal          | xx          | 111        | 1, 2 |

| Fast RC Oscillator with Divide-by-16 (FRCDIV16)  | Internal          | xx          | 110        | 1    |

| Low-Power RC Oscillator (LPRC)                   | Internal          | xx          | 101        | 1    |

| Secondary (Timer1) Oscillator (SOSC)             | Secondary         | xx          | 100        | 1    |

| Primary Oscillator (HS) with PLL<br>(HSPLL)      | Primary           | 10          | 011        | -    |

| Primary Oscillator (XT) with PLL<br>(XTPLL)      | Primary           | 01          | 011        | -    |

| Primary Oscillator (EC) with PLL<br>(ECPLL)      | Primary           | 00          | 011        | 1    |