Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT             |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 32x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp310-i-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

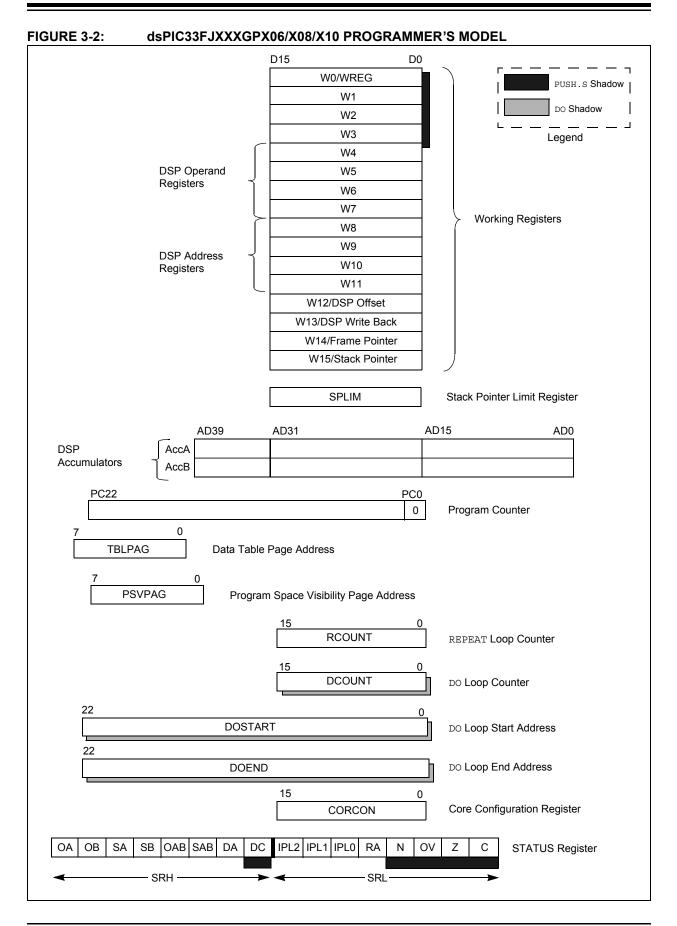

# 3.5 Arithmetic Logic Unit (ALU)

The dsPIC33FJXXXGPX06/X08/X10 ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the <u>SR</u> register. The C and DC Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the "*dsPIC30F/33F Programmer's Reference Manual*" (DS70157) for information on the SR bits affected by each instruction.

The dsPIC33FJXXXGPX06/X08/X10 CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit-divisor division.

### 3.5.1 MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier of the DSP engine, the ALU supports unsigned, signed or mixed-sign operation in several MCU multiplication modes:

- 1. 16-bit x 16-bit signed

- 2. 16-bit x 16-bit unsigned

- 3. 16-bit signed x 5-bit (literal) unsigned

- 4. 16-bit unsigned x 16-bit unsigned

- 5. 16-bit unsigned x 5-bit (literal) unsigned

- 6. 16-bit unsigned x 16-bit signed

- 7. 8-bit unsigned x 8-bit unsigned

### 3.5.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 1. 32-bit signed/16-bit signed divide

- 2. 32-bit unsigned/16-bit unsigned divide

- 3. 16-bit signed/16-bit signed divide

- 4. 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. 16-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

### 3.6 DSP Engine

The DSP engine consists of a high-speed, 17-bit x 17-bit multiplier, a barrel shifter and a 40-bit adder/subtracter (with two target accumulators, round and saturation logic).

The dsPIC33FJXXXGPX06/X08/X10 is a single-cycle, instruction flow architecture; therefore, concurrent operation of the DSP engine with MCU instruction flow is not possible. However, some MCU ALU and DSP engine resources may be used concurrently by the same instruction (e.g., ED, EDAC).

The DSP engine also has the capability to perform inherent accumulator-to-accumulator operations which require no additional data. These instructions are ADD, SUB and NEG.

The DSP engine has various options selected through various bits in the CPU Core Control register (CORCON), as listed below:

- 1. Fractional or integer DSP multiply (IF).

- 2. Signed or unsigned DSP multiply (US).

- 3. Conventional or convergent rounding (RND).

- 4. Automatic saturation on/off for AccA (SATA).

- 5. Automatic saturation on/off for AccB (SATB).

- 6. Automatic saturation on/off for writes to data memory (SATDW).

- 7. Accumulator Saturation mode selection (ACCSAT).

Table 3-1 provides a summary of DSP instructions. A block diagram of the DSP engine is shown in Figure 3-3.

| SUMMARY     |                        |                   |  |  |  |  |

|-------------|------------------------|-------------------|--|--|--|--|

| Instruction | Algebraic<br>Operation | ACC Write<br>Back |  |  |  |  |

| CLR         | A = 0                  | Yes               |  |  |  |  |

| ED          | $A = (x - y)^2$        | No                |  |  |  |  |

| EDAC        | $A = A + (x - y)^2$    | No                |  |  |  |  |

| MAC         | A = A + (x * y)        | Yes               |  |  |  |  |

| MAC         | $A = A + x^2$          | No                |  |  |  |  |

| MOVSAC      | No change in A         | Yes               |  |  |  |  |

| MPY         | A = x * y              | No                |  |  |  |  |

| MPY         | $A = x^2$              | No                |  |  |  |  |

| MPY.N       | A = -x * y             | No                |  |  |  |  |

| MSC         | A = A - x * y          | Yes               |  |  |  |  |

#### TABLE 3-1: DSP INSTRUCTIONS SUMMARY

NOTES:

# 4.2 Data Address Space

The dsPIC33FJXXXGPX06/X08/X10 CPU has a separate 16-bit wide data memory space. The data space is accessed using separate Address Generation Units (AGUs) for read and write operations. Data memory maps of devices with different RAM sizes are shown in Figure 4-3 through Figure 4-5.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the data space. This arrangement gives a data space address range of 64 Kbytes or 32K words. The lower half of the data memory space (that is, when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility area (see Section 4.6.3 "Reading Data from Program Memory Using Program Space Visibility").

dsPIC33FJXXXGPX06/X08/X10 devices implement a total of up to 30 Kbytes of data memory. Should an EA point to a location outside of this area, an all-zero word or byte will be returned.

#### 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byte addressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all data space EAs resolve to bytes. The Least Significant Bytes (LSBs) of each word have even addresses, while the Most Significant Bytes (MSBs) have odd addresses.

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve data space memory usage efficiency, the dsPIC33FJXXXGPX06/X08/X10 instruction set supports both word and byte operations. As a consequence of byte accessibility, all effective address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] will result in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

Data byte reads will read the complete word that contains the byte, using the LSb of any EA to determine which byte to select. The selected byte is placed onto the LSb of the data path. That is, data memory and registers are organized as two parallel byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register which matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed; if it occurred on a write, the instruction will be executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the Least Significant Byte. The Most Significant Byte is not modified.

A sign-extend instruction (SE) is provided to allow users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users can clear the MSb of any W register by executing a zero-extend (ZE) instruction on the appropriate address.

### 4.2.3 SFR SPACE

The first 2 Kbytes of the Near Data Space, from 0x0000 to 0x07FF, is primarily occupied by Special Function Registers (SFRs). These are used by the dsPIC33FJXXXGPX06/X08/X10 core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control, and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'. A complete listing of implemented SFRs, including their addresses, is shown in Table 4-1 through Table 4-34.

**Note:** The actual set of peripheral features and interrupts varies by the device. Please refer to the corresponding device tables and pinout diagrams for device-specific information.

### 4.2.4 NEAR DATA SPACE

The 8-Kbyte area between 0x0000 and 0x1FFF is referred to as the Near Data Space. Locations in this space are directly addressable via a 13-bit absolute address field within all memory direct instructions. Additionally, the whole data space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an Address Pointer.

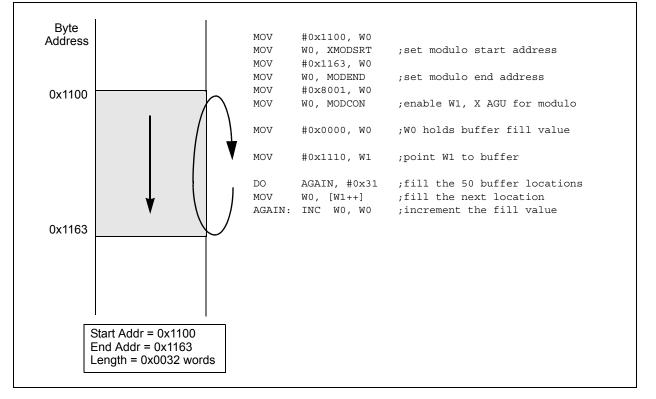

can operate on any W register pointer. However, it is not advisable to use W14 or W15 for Modulo Addressing since these two registers are used as the Stack Frame Pointer and Stack Pointer, respectively.

In general, any particular circular buffer can only be configured to operate in one direction as there are certain restrictions on the buffer start address (for incrementing buffers), or end address (for decrementing buffers), based upon the direction of the buffer.

The only exception to the usage restrictions is for buffers which have a power-of-2 length. As these buffers satisfy the start and end address criteria, they may operate in a bidirectional mode (i.e., address boundary checks will be performed on both the lower and upper address boundaries).

#### 4.4.1 START AND END ADDRESS

The Modulo Addressing scheme requires that a starting and ending address be specified and loaded into the 16-bit Modulo Buffer Address registers: XMODSRT, XMODEND, YMODSRT and YMODEND (see Table 4-1).

Note: Y space Modulo Addressing EA calculations assume word sized data (LSb of every EA is always clear).

The length of a circular buffer is not directly specified. It is determined by the difference between the corresponding start and end addresses. The maximum possible length of the circular buffer is 32K words (64 Kbytes).

#### 4.4.2 W ADDRESS REGISTER SELECTION

The Modulo and Bit-Reversed Addressing Control register, MODCON<15:0>, contains enable flags as well as a W register field to specify the W Address registers. The XWM and YWM fields select which registers will operate with Modulo Addressing. If XWM = 15, X RAGU and X WAGU Modulo Addressing is disabled. Similarly, if YWM = 15, Y AGU Modulo Addressing is disabled.

The X Address Space Pointer W register (XWM), to which Modulo Addressing is to be applied, is stored in MODCON<3:0> (see Table 4-1). Modulo Addressing is enabled for X data space when XWM is set to any value other than '15' and the XMODEN bit is set at MODCON<15>.

The Y Address Space Pointer W register (YWM) to which Modulo Addressing is to be applied is stored in MODCON<7:4>. Modulo Addressing is enabled for Y data space when YWM is set to any value other than '15' and the YMODEN bit is set at MODCON<14>.

#### FIGURE 4-7: MODULO ADDRESSING OPERATION EXAMPLE

| TABLE 7-1:       |                                      | PT VECTORS (CO        | NTINUED)              |                                    |

|------------------|--------------------------------------|-----------------------|-----------------------|------------------------------------|

| Vector<br>Number | Interrupt<br>Request (IRQ)<br>Number | IVT Address           | AIVT Address          | Interrupt Source                   |

| 54               | 46                                   | 0x000070              | 0x000170              | DMA4 – DMA Channel 4               |

| 55               | 47                                   | 0x000072              | 0x000172              | T6 – Timer6                        |

| 56               | 48                                   | 0x000074              | 0x000174              | T7 – Timer7                        |

| 57               | 49                                   | 0x000076              | 0x000176              | SI2C2 – I2C2 Slave Events          |

| 58               | 50                                   | 0x000078              | 0x000178              | MI2C2 – I2C2 Master Events         |

| 59               | 51                                   | 0x00007A              | 0x00017A              | T8 – Timer8                        |

| 60               | 52                                   | 0x00007C              | 0x00017C              | T9 – Timer9                        |

| 61               | 53                                   | 0x00007E              | 0x00017E              | INT3 – External Interrupt 3        |

| 62               | 54                                   | 0x000080              | 0x000180              | INT4 – External Interrupt 4        |

| 63               | 55                                   | 0x000082              | 0x000182              | C2RX – ECAN2 Receive Data Ready    |

| 64               | 56                                   | 0x000084              | 0x000184              | C2 – ECAN2 Event                   |

| 65               | 57                                   | 0x000086              | 0x000186              | Reserved                           |

| 66               | 58                                   | 0x000088              | 0x000188              | Reserved                           |

| 67               | 59                                   | 0x00008A              | 0x00018A              | DCIE – DCI Error                   |

| 68               | 60                                   | 0x00008C              | 0x00018C              | DCID – DCI Transfer Done           |

| 69               | 61                                   | 0x00008E              | 0x00018E              | DMA5 – DMA Channel 5               |

| 70               | 62                                   | 0x000090              | 0x000190              | Reserved                           |

| 71               | 63                                   | 0x000092              | 0x000192              | Reserved                           |

| 72               | 64                                   | 0x000094              | 0x000194              | Reserved                           |

| 73               | 65                                   | 0x000096              | 0x000196              | U1E – UART1 Error                  |

| 74               | 66                                   | 0x000098              | 0x000198              | U2E – UART2 Error                  |

| 75               | 67                                   | 0x00009A              | 0x00019A              | Reserved                           |

| 76               | 68                                   | 0x00009C              | 0x00019C              | DMA6 – DMA Channel 6               |

| 77               | 69                                   | 0x00009E              | 0x00019E              | DMA7 – DMA Channel 7               |

| 78               | 70                                   | 0x0000A0              | 0x0001A0              | C1TX – ECAN1 Transmit Data Request |

| 79               | 71                                   | 0x0000A2              | 0x0001A2              | C2TX – ECAN2 Transmit Data Request |

| 80-125           | 72-117                               | 0x0000A4-0x0000<br>FE | 0x0001A4-0x0001<br>FE | Reserved                           |

# TABLE 7-1: INTERRUPT VECTORS (CONTINUED)

### TABLE 7-2: TRAP VECTORS

| Vector Number | IVT Address       | AIVT Address | Trap Source        |

|---------------|-------------------|--------------|--------------------|

| 0             | 0x000004          | 0x000104     | Reserved           |

| 1             | 0x00006           | 0x000106     | Oscillator Failure |

| 2             | 0x00008           | 0x000108     | Address Error      |

| 3             | 0x00000A          | 0x00010A     | Stack Error        |

| 4             | 0x00000C 0x00010C |              | Math Error         |

| 5             | 0x00000E          | 0x00010E     | DMA Error Trap     |

| 6             | 0x000010          | 0x000110     | Reserved           |

| 7             | 7 0x000012        |              | Reserved           |

| REGISTER      | 7-12: IEC2:    | INTERRUPT                                                                                                                  | ENABLE CO        | ONTROL RE        | GISTER 2         |                 |         |  |  |  |

|---------------|----------------|----------------------------------------------------------------------------------------------------------------------------|------------------|------------------|------------------|-----------------|---------|--|--|--|

| R/W-0         | R/W-0          | U-0                                                                                                                        | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |

| T6IE          | DMA4IE         | —                                                                                                                          | OC8IE            | OC7IE            | OC6IE            | OC5IE           | IC6IE   |  |  |  |

| bit 15        |                |                                                                                                                            |                  |                  |                  |                 | bit     |  |  |  |

| R/W-0         | R/W-0          | R/W-0                                                                                                                      | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |

| IC5IE         | IC4IE          | IC3IE                                                                                                                      | DMA3IE           | C1IE             | C1RXIE           | SPI2IE          | SPI2EIE |  |  |  |

| bit 7         |                |                                                                                                                            |                  |                  |                  |                 | bit     |  |  |  |

| Legend:       |                |                                                                                                                            |                  |                  |                  |                 |         |  |  |  |

| R = Readabl   | e hit          | W = Writable                                                                                                               | bit              | U = Unimpler     | mented bit, read | l as '0'        |         |  |  |  |

| -n = Value at |                | '1' = Bit is se                                                                                                            |                  | '0' = Bit is cle |                  | x = Bit is unki | าดพท    |  |  |  |

|               |                |                                                                                                                            | •                | o Dicio die      |                  |                 |         |  |  |  |

| bit 15        | T6IE: Timer6   | Interrupt Enat                                                                                                             | ole bit          |                  |                  |                 |         |  |  |  |

|               |                | request enable                                                                                                             |                  |                  |                  |                 |         |  |  |  |

|               | 0 = Interrupt  | request not en                                                                                                             | abled            |                  |                  |                 |         |  |  |  |

| bit 14        | DMA4IE: DM     | IA Channel 4 E                                                                                                             | ata Transfer C   | complete Interr  | rupt Enable bit  |                 |         |  |  |  |

|               |                | request enable                                                                                                             |                  |                  |                  |                 |         |  |  |  |

|               | -              | request not en                                                                                                             |                  |                  |                  |                 |         |  |  |  |

| bit 13        | -              | ted: Read as                                                                                                               |                  |                  |                  |                 |         |  |  |  |

| bit 12        | •              | ut Compare Cl                                                                                                              |                  | upt Enable bit   |                  |                 |         |  |  |  |

|               |                | request enable<br>request not en                                                                                           |                  |                  |                  |                 |         |  |  |  |

| bit 11        | •              | •                                                                                                                          |                  | upt Enable bit   |                  |                 |         |  |  |  |

|               | 1 = Interrupt  | OC7IE: Output Compare Channel 7 Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled |                  |                  |                  |                 |         |  |  |  |

| bit 10        | OC6IE: Outp    | OC6IE: Output Compare Channel 6 Interrupt Enable bit                                                                       |                  |                  |                  |                 |         |  |  |  |

|               |                | request enable<br>request not en                                                                                           |                  |                  |                  |                 |         |  |  |  |

| bit 9         | OC5IE: Outp    | ut Compare Cl                                                                                                              | nannel 5 Interro | upt Enable bit   |                  |                 |         |  |  |  |

|               |                | 1 = Interrupt request enabled<br>0 = Interrupt request not enabled                                                         |                  |                  |                  |                 |         |  |  |  |

| bit 8         | IC6IE: Input ( | Capture Chanr                                                                                                              | el 6 Interrupt E | Enable bit       |                  |                 |         |  |  |  |

|               |                | request enable<br>request not en                                                                                           |                  |                  |                  |                 |         |  |  |  |

| bit 7         | IC5IE: Input ( | Capture Chanr                                                                                                              | el 5 Interrupt E | Enable bit       |                  |                 |         |  |  |  |

|               |                | 1 = Interrupt request enabled                                                                                              |                  |                  |                  |                 |         |  |  |  |

|               |                | request not en                                                                                                             |                  |                  |                  |                 |         |  |  |  |

| bit 6         | •              | Capture Chanr                                                                                                              | •                | nable bit        |                  |                 |         |  |  |  |

|               |                | request enable<br>request not en                                                                                           |                  |                  |                  |                 |         |  |  |  |

| bit 5         | •              | Capture Chanr                                                                                                              |                  | Enable bit       |                  |                 |         |  |  |  |

|               |                | request enable                                                                                                             |                  |                  |                  |                 |         |  |  |  |

|               |                | request not en                                                                                                             |                  |                  |                  |                 |         |  |  |  |

| bit 4         | DMA3IE: DM     | IA Channel 3 E                                                                                                             | ata Transfer C   | complete Interr  | rupt Enable bit  |                 |         |  |  |  |

|               |                | request enable                                                                                                             |                  |                  |                  |                 |         |  |  |  |

|               | -              | request not en                                                                                                             |                  |                  |                  |                 |         |  |  |  |

| bit 3         |                | 1 Event Interru                                                                                                            | -                |                  |                  |                 |         |  |  |  |

|               |                | request enable<br>request not en                                                                                           |                  |                  |                  |                 |         |  |  |  |

|               |                |                                                                                                                            |                  |                  |                  |                 |         |  |  |  |

# \_ \_

| U-0          | R/W-1                                                               | R/W-0                                   | R/W-0          | U-0               | R/W-1            | R/W-0           | R/W-0 |  |  |  |

|--------------|---------------------------------------------------------------------|-----------------------------------------|----------------|-------------------|------------------|-----------------|-------|--|--|--|

| _            |                                                                     | T4IP<2:0>                               |                |                   |                  | OC4IP<2:0>      |       |  |  |  |

| bit 15       |                                                                     |                                         |                |                   |                  |                 | bit   |  |  |  |

| U-0          | R/W-1                                                               | R/W-0                                   | R/W-0          | U-0               | R/W-1            | R/W-0           | R/W-0 |  |  |  |

| 0-0          | R/W-1                                                               | OC3IP<2:0>                              | R/W-U          | 0-0               | R/W-I            | DMA2IP<2:0>     | R/W-U |  |  |  |

| <br>bit 7    |                                                                     | 00311 \2.02                             |                |                   |                  |                 | bit   |  |  |  |

|              |                                                                     |                                         |                |                   |                  |                 |       |  |  |  |

| Legend:      |                                                                     |                                         |                |                   |                  |                 |       |  |  |  |

| R = Readab   | le bit                                                              | W = Writable b                          | bit            | U = Unimple       | mented bit, rea  | ad as '0'       |       |  |  |  |

| -n = Value a | It POR                                                              | '1' = Bit is set                        |                | '0' = Bit is cle  | eared            | x = Bit is unkn | own   |  |  |  |

|              |                                                                     |                                         |                |                   |                  |                 |       |  |  |  |

| bit 15       | -                                                                   | ented: Read as 'o                       |                |                   |                  |                 |       |  |  |  |

| bit 14-12    |                                                                     | Timer4 Interrupt                        | •              |                   |                  |                 |       |  |  |  |

|              | 111 = Interr                                                        | upt is priority 7 (h                    | nighest priori | ity interrupt)    |                  |                 |       |  |  |  |

|              | •                                                                   |                                         |                |                   |                  |                 |       |  |  |  |

|              | •                                                                   |                                         |                |                   |                  |                 |       |  |  |  |

|              | 001 = Interrupt is priority 1                                       |                                         |                |                   |                  |                 |       |  |  |  |

|              |                                                                     | upt source is disa                      | abled          |                   |                  |                 |       |  |  |  |

| bit 11       | Unimplemented: Read as '0'                                          |                                         |                |                   |                  |                 |       |  |  |  |

| bit 10-8     | OC4IP<2:0                                                           | Output Compa                            | re Channel     | 4 Interrupt Prior | rity bits        |                 |       |  |  |  |

|              | 111 = Interr                                                        | upt is priority 7 (h                    | nighest priori | ity interrupt)    |                  |                 |       |  |  |  |

|              | •                                                                   |                                         |                |                   |                  |                 |       |  |  |  |

|              | •                                                                   |                                         |                |                   |                  |                 |       |  |  |  |

|              | •<br>001 = Interr                                                   | upt is priority 1                       |                |                   |                  |                 |       |  |  |  |

|              |                                                                     | upt is phoney if                        | abled          |                   |                  |                 |       |  |  |  |

| bit 7        |                                                                     | ented: Read as 'o                       |                |                   |                  |                 |       |  |  |  |

| bit 6-4      | -                                                                   | : Output Compa                          |                | 3 Interrunt Prio  | rity bits        |                 |       |  |  |  |

|              |                                                                     | upt is priority 7 (h                    |                | •                 | ity bito         |                 |       |  |  |  |

|              | •                                                                   |                                         | iigheot phon   | ity interrupt)    |                  |                 |       |  |  |  |

|              | •                                                                   |                                         |                |                   |                  |                 |       |  |  |  |

|              | •                                                                   |                                         |                |                   |                  |                 |       |  |  |  |

|              | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled |                                         |                |                   |                  |                 |       |  |  |  |

| hit 2        |                                                                     | ented: Read as '0                       |                |                   |                  |                 |       |  |  |  |

| bit 3        | -                                                                   |                                         |                | mafar Camplet     | Latern at Drie   | with a latita   |       |  |  |  |

| bit 2-0      |                                                                     | 0>: DMA Channe                          |                | -                 | e interrupt Prid | ority dits      |       |  |  |  |

|              |                                                                     | upt is priority 7 (h                    | iignest priori | ity interrupt)    |                  |                 |       |  |  |  |

|              |                                                                     |                                         |                |                   |                  |                 |       |  |  |  |

|              |                                                                     |                                         |                |                   |                  |                 |       |  |  |  |

|              | •                                                                   |                                         |                |                   |                  |                 |       |  |  |  |

|              |                                                                     | upt is priority 1<br>upt source is disa |                |                   |                  |                 |       |  |  |  |

| U-0          | R/W-1                                                                                                                     | R/W-0                                                                 | R/W-0           | U-0               | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |  |

|--------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|-----------------|-------------------|-----------------|-----------------|-------|--|--|--|--|--|

|              |                                                                                                                           | IC5IP<2:0>                                                            |                 | —                 |                 | IC4IP<2:0>      |       |  |  |  |  |  |

| oit 15       |                                                                                                                           |                                                                       |                 |                   |                 |                 | bit   |  |  |  |  |  |

| U-0          | R/W-1                                                                                                                     | R/W-0                                                                 | R/W-0           | U-0               | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |  |

| _            |                                                                                                                           | IC3IP<2:0>                                                            |                 | _                 |                 | DMA3IP<2:0>     |       |  |  |  |  |  |

| bit 7        |                                                                                                                           |                                                                       |                 |                   |                 |                 | bit   |  |  |  |  |  |

| Legend:      |                                                                                                                           |                                                                       |                 |                   |                 |                 |       |  |  |  |  |  |

| R = Readab   | le bit                                                                                                                    | W = Writable b                                                        | pit             | U = Unimpler      | mented bit, rea | ad as '0'       |       |  |  |  |  |  |

| -n = Value a | t POR                                                                                                                     | '1' = Bit is set                                                      |                 | '0' = Bit is cle  | ared            | x = Bit is unkn | own   |  |  |  |  |  |

| bit 15       | Unimpleme                                                                                                                 | nted: Read as '0                                                      | )'              |                   |                 |                 |       |  |  |  |  |  |

| bit 14-12    |                                                                                                                           | Input Capture C                                                       |                 |                   | its             |                 |       |  |  |  |  |  |

|              | •                                                                                                                         | <pre>111 = Interrupt is priority 7 (highest priority interrupt)</pre> |                 |                   |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                                         | •                                                                     |                 |                   |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                                         | •                                                                     |                 |                   |                 |                 |       |  |  |  |  |  |

|              |                                                                                                                           | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled   |                 |                   |                 |                 |       |  |  |  |  |  |

| bit 11       |                                                                                                                           | nted: Read as '0                                                      |                 |                   |                 |                 |       |  |  |  |  |  |

| oit 10-8     | -                                                                                                                         |                                                                       |                 | errupt Prioritv b | its             |                 |       |  |  |  |  |  |

|              | IC4IP<2:0>: Input Capture Channel 4 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                                                                       |                 |                   |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                                         |                                                                       |                 |                   |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                                         |                                                                       |                 |                   |                 |                 |       |  |  |  |  |  |

|              | •<br>001 = Interrupt is priority 1                                                                                        |                                                                       |                 |                   |                 |                 |       |  |  |  |  |  |

|              |                                                                                                                           | upt source is disa                                                    | abled           |                   |                 |                 |       |  |  |  |  |  |

| bit 7        | Unimpleme                                                                                                                 | nted: Read as '0                                                      | )'              |                   |                 |                 |       |  |  |  |  |  |

| bit 6-4      |                                                                                                                           | Input Capture C                                                       |                 |                   | its             |                 |       |  |  |  |  |  |

|              | 111 = Interr                                                                                                              | upt is priority 7 (h                                                  | nighest priorit | ty interrupt)     |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                                         |                                                                       |                 |                   |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                                         |                                                                       |                 |                   |                 |                 |       |  |  |  |  |  |

|              |                                                                                                                           | upt is priority 1<br>upt source is disa                               | abled           |                   |                 |                 |       |  |  |  |  |  |

| bit 3        | Unimpleme                                                                                                                 | nted: Read as 'o                                                      | )'              |                   |                 |                 |       |  |  |  |  |  |

| bit 2-0      | DMA3IP<2:                                                                                                                 | 0>: DMA Channe                                                        | el 3 Data Tra   | nsfer Complete    | Interrupt Price | rity bits       |       |  |  |  |  |  |

|              | 111 = Interr                                                                                                              | upt is priority 7 (h                                                  | nighest priorit | ty interrupt)     |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                                         |                                                                       |                 |                   |                 |                 |       |  |  |  |  |  |

|              | •                                                                                                                         |                                                                       |                 |                   |                 |                 |       |  |  |  |  |  |

|              |                                                                                                                           | upt is priority 1                                                     |                 |                   |                 |                 |       |  |  |  |  |  |

|              | 000 = Interr                                                                                                              |                                                                       |                 |                   |                 |                 |       |  |  |  |  |  |

| R/W-0        | R/W-0                      | R/W-1                                            | R/W-1         | R/W-0                | R/W-0            | R/W-0              | R/W-0      |  |  |  |

|--------------|----------------------------|--------------------------------------------------|---------------|----------------------|------------------|--------------------|------------|--|--|--|

| ROI          | N/W-0                      | DOZE<2:0>                                        | D/ VV- I      | DOZEN <sup>(1)</sup> | N/W-0            | FRCDIV<2:0>        | N/W-0      |  |  |  |

| bit 15       |                            | DOZL~2.02                                        |               | DOZEN                |                  |                    | bit        |  |  |  |

|              |                            |                                                  |               |                      |                  |                    | bit        |  |  |  |

| R/W-0        | R/W-1                      | U-0                                              | R/W-0         | R/W-0                | R/W-0            | R/W-0              | R/W-0      |  |  |  |

| PLLP         | OST<1:0>                   |                                                  |               |                      | PLLPRE<4:0       | >                  |            |  |  |  |

| bit 7        |                            |                                                  |               |                      |                  |                    | bit        |  |  |  |

|              |                            |                                                  |               |                      |                  |                    |            |  |  |  |

| Legend:      |                            | -                                                | -             | ration bits on Po    | OR               |                    |            |  |  |  |

| R = Readab   |                            | W = Writable                                     | bit           | •                    | nented bit, read |                    |            |  |  |  |

| -n = Value a | t POR                      | '1' = Bit is set                                 |               | '0' = Bit is cle     | ared             | x = Bit is unkno   | own        |  |  |  |

| L:1 4 F      |                            |                                                  | 4             |                      |                  |                    |            |  |  |  |

| bit 15       |                            | er on Interrupt bi                               |               | d the process        | r clock/porinho  | ral clock ratio is | sot to 1.1 |  |  |  |

|              |                            | ts have no effect                                |               |                      |                  |                    | 361 10 1.1 |  |  |  |

| bit 14-12    | DOZE<2:0>                  | Processor Cloo                                   | k Reduction   | Select bits          |                  |                    |            |  |  |  |

|              | 000 = Fcy/1                |                                                  |               |                      |                  |                    |            |  |  |  |

|              | 001 = FCY/2                |                                                  |               |                      |                  |                    |            |  |  |  |

|              | 010 = FCY/4<br>011 = FCY/8 |                                                  |               |                      |                  |                    |            |  |  |  |

|              |                            | 100 = FCY/16                                     |               |                      |                  |                    |            |  |  |  |

|              |                            | 101 = FCY/32                                     |               |                      |                  |                    |            |  |  |  |

|              | 110 = FCY/6<br>111 = FCY/1 |                                                  |               |                      |                  |                    |            |  |  |  |

| bit 11       |                            | ZE Mode Enabl                                    | o hit(1)      |                      |                  |                    |            |  |  |  |

|              |                            |                                                  |               | etween the per       | ipheral clocks a | and the processo   | or clocks  |  |  |  |

|              |                            | or clock/periphe                                 |               |                      |                  |                    |            |  |  |  |

| bit 10-8     | FRCDIV<2:0                 | >: Internal Fast                                 | RC Oscillato  | or Postscaler bit    | S                |                    |            |  |  |  |

|              |                            | divide by 1 (defa                                | ult)          |                      |                  |                    |            |  |  |  |

|              | 001 = FRC 0<br>010 = FRC 0 |                                                  |               |                      |                  |                    |            |  |  |  |

|              | 010 = FRC (                |                                                  |               |                      |                  |                    |            |  |  |  |

|              | 100 <b>= FRC d</b>         | divide by 16                                     |               |                      |                  |                    |            |  |  |  |

|              |                            | 101 = FRC divide by 32<br>110 = FRC divide by 64 |               |                      |                  |                    |            |  |  |  |

|              |                            | divide by 256                                    |               |                      |                  |                    |            |  |  |  |

| bit 7-6      |                            | -                                                | Output Divide | er Select bits (al   | so denoted as    | 'N2', PLL postsc   | aler)      |  |  |  |

|              | 00 = Output/               |                                                  |               | × ×                  |                  | <i>,</i> ,         | ,          |  |  |  |

|              |                            | 01 = Output/4 (default)                          |               |                      |                  |                    |            |  |  |  |

|              |                            | 10 = Reserved<br>11 = Output/8                   |               |                      |                  |                    |            |  |  |  |

| bit 5        | •                          | o<br>nted: Read as 'o                            | ı'            |                      |                  |                    |            |  |  |  |

| bit 4-0      | -                          |                                                  |               | ıt Divider bits (a   | lso denoted as   | 'N1', PLL presca   | aler)      |  |  |  |

|              |                            | ut/2 (default)                                   |               |                      |                  |                    |            |  |  |  |

|              | 00001 = Inp                |                                                  |               |                      |                  |                    |            |  |  |  |

|              | •                          |                                                  |               |                      |                  |                    |            |  |  |  |

|              | •                          |                                                  |               |                      |                  |                    |            |  |  |  |

|              |                            |                                                  |               |                      |                  |                    |            |  |  |  |

**Note 1:** This bit is cleared when the ROI bit is set and an interrupt occurs.

| REGISTER 9-                        | -3: PLLF | BD: PLL FEE                          | DBACK DI | VISOR REGIS                        | TER   |       |                      |

|------------------------------------|----------|--------------------------------------|----------|------------------------------------|-------|-------|----------------------|

| U-0                                | U-0      | U-0                                  | U-0      | U-0                                | U-0   | U-0   | R/W-0 <sup>(1)</sup> |

|                                    | _        | —                                    | _        | —                                  | _     | —     | PLLDIV<8>            |

| bit 15                             |          |                                      |          |                                    |       |       | bit 8                |

| R/W-0                              | R/W-0    | R/W-1                                | R/W-1    | R/W-0                              | R/W-0 | R/W-0 | R/W-0                |

|                                    |          |                                      | PLLE     | )IV<7:0>                           |       |       |                      |

| bit 7                              |          |                                      |          |                                    |       |       | bit 0                |

| Legend:                            |          |                                      |          |                                    |       |       |                      |

| R = Readable bit W = Writable bit  |          |                                      | bit      | U = Unimplemented bit, read as '0' |       |       |                      |

| -n = Value at POR '1' = Bit is set |          | '0' = Bit is cleared x = Bit is unkn |          | known                              |       |       |                      |

bit 15-9 Unimplemented: Read as '0'

bit 8-0 PLLDIV<8:0>: PLL Feedback Divisor bits (also denoted as 'M', PLL multiplier)

```

000000000 = 2

00000001 = 3

000000010 = 4

.

.

000110000 = 50 (default)

.

.

11111111 = 513

```

| REGISTER      | 10-2: PMD2    | 2: PERIPHER                      | AL MODULE        | DISABLE C         | ONTROL RE        | GISTER 2        |       |

|---------------|---------------|----------------------------------|------------------|-------------------|------------------|-----------------|-------|

| R/W-0         | R/W-0         | R/W-0                            | R/W-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

| IC8MD         | IC7MD         | IC6MD                            | IC5MD            | IC4MD             | IC3MD            | IC2MD           | IC1MD |

| bit 15        |               |                                  |                  |                   |                  |                 | bit 8 |

| R/W-0         | R/W-0         | R/W-0                            | R/W-0            | R/W-0             | R/W-0            | R/W-0           | R/W-0 |

| OC8MD         | OC7MD         | OC6MD                            | OC5MD            | OC4MD             | OC3MD            | OC2MD           | OC1MD |

| bit 7         | OCTIND        | OCOMD                            | OCOMD            | 0041110           | OCSIND           | OCZIVID         | bit 0 |

| Legend:       |               |                                  |                  |                   |                  |                 |       |

| R = Readable  | e bit         | W = Writable                     | bit              | U = Unimplem      | nented bit, read | l as '0'        |       |

| -n = Value at | POR           | '1' = Bit is set                 |                  | '0' = Bit is clea | ared             | x = Bit is unkr | nown  |

| bit 15        | IC8MD: Input  | Capture 8 Mod                    | lule Disable bit |                   |                  |                 |       |

|               |               | oture 8 module<br>oture 8 module |                  |                   |                  |                 |       |

| bit 14        | IC7MD: Input  | Capture 7 Mod                    | dule Disable bit |                   |                  |                 |       |

|               |               | oture 7 module<br>oture 7 module |                  |                   |                  |                 |       |

| bit 13        | IC6MD: Input  | Capture 6 Mod                    | dule Disable bit |                   |                  |                 |       |

|               |               | oture 6 module<br>oture 6 module |                  |                   |                  |                 |       |

| bit 12        | IC5MD: Input  | Capture 5 Mod                    | dule Disable bit |                   |                  |                 |       |

|               |               | oture 5 module<br>oture 5 module |                  |                   |                  |                 |       |

| bit 11        | IC4MD: Input  | Capture 4 Mod                    | dule Disable bit |                   |                  |                 |       |

|               |               | oture 4 module<br>oture 4 module |                  |                   |                  |                 |       |

| bit 10        | IC3MD: Input  | Capture 3 Mod                    | dule Disable bit |                   |                  |                 |       |

|               |               | oture 3 module<br>oture 3 module |                  |                   |                  |                 |       |

| bit 9         | IC2MD: Input  | Capture 2 Mod                    | dule Disable bit |                   |                  |                 |       |

|               |               | oture 2 module<br>oture 2 module |                  |                   |                  |                 |       |

| bit 8         |               |                                  | dule Disable bit |                   |                  |                 |       |

|               |               | oture 1 module<br>oture 1 module |                  |                   |                  |                 |       |

| bit 7         | OC8MD: Out    | put Compare 8                    | Module Disable   | e bit             |                  |                 |       |

|               | 1 = Output Co | ompare 8 modu<br>ompare 8 modu   | lle is disabled  |                   |                  |                 |       |

| bit 6         | OC7MD: Out    | put Compare 4                    | Module Disable   | e bit             |                  |                 |       |

|               |               | ompare 7 modu<br>ompare 7 modu   |                  |                   |                  |                 |       |

| bit 5         | OC6MD: Out    | put Compare 6                    | Module Disable   | e bit             |                  |                 |       |

|               |               | ompare 6 modu<br>ompare 6 modu   |                  |                   |                  |                 |       |

| bit 4         | -             | -                                | Module Disable   | e bit             |                  |                 |       |

|               | 1 = Output Co | ompare 5 modu<br>ompare 5 modu   | lle is disabled  |                   |                  |                 |       |

# REGISTER 10-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2

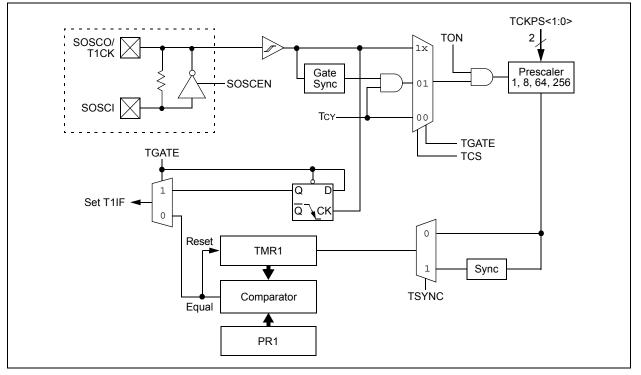

# 12.0 TIMER1

Note: This data sheet summarizes the features of the dsPIC33FJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 11.** "**Timers**" (DS70205) in the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The Timer1 module is a 16-bit timer, which can serve as the time counter for the real-time clock, or operate as a free-running interval timer/counter. Timer1 can operate in three modes:

- 16-bit Timer

- 16-bit Synchronous Counter

- 16-bit Asynchronous Counter

Timer1 also supports these features:

- Timer gate operation

- · Selectable prescaler settings

- Timer operation during CPU Idle and Sleep modes

- Interrupt on 16-bit Period register match or falling edge of external gate signal

Figure 12-1 presents a block diagram of the 16-bit timer module.

To configure Timer1 for operation:

- 1. Set the TON bit (= 1) in the T1CON register.

- 2. Select the timer prescaler ratio using the TCKPS<1:0> bits in the T1CON register.

- 3. Set the Clock and Gating modes using the TCS and TGATE bits in the T1CON register.

- 4. Set or clear the TSYNC bit in T1CON to select synchronous or asynchronous operation.

- 5. Load the timer period value into the PR1 register.

- 6. If interrupts are required, set the interrupt enable bit, T1IE. Use the priority bits, T1IP<2:0>, to set the interrupt priority.

#### FIGURE 12-1: 16-BIT TIMER1 MODULE BLOCK DIAGRAM

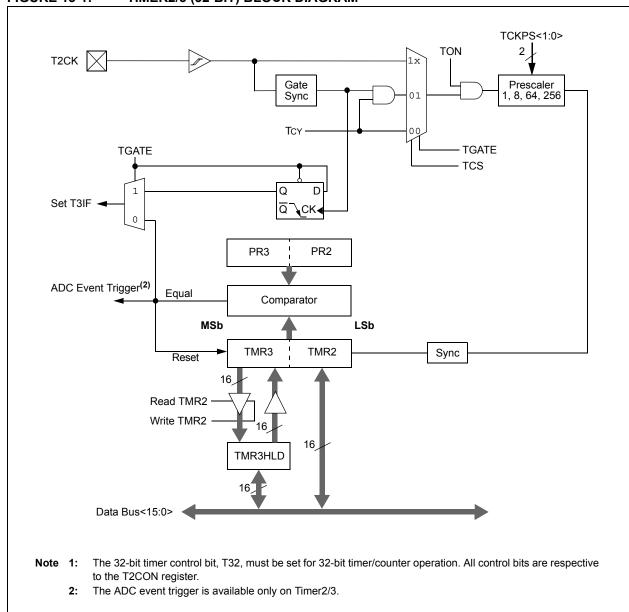

# FIGURE 13-1: TIMER2/3 (32-BIT) BLOCK DIAGRAM<sup>(1)</sup>

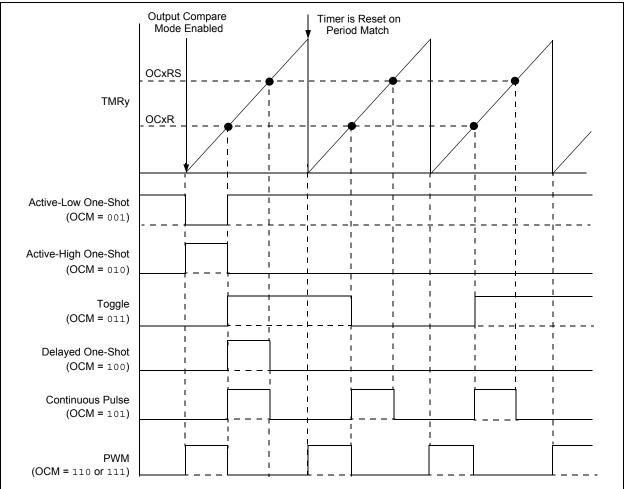

### 15.1 Output Compare Modes

Configure the Output Compare modes by setting the appropriate Output Compare Mode (OCM<2:0>) bits in the Output Compare Control (OCxCON<2:0>) register. Table 15-1 lists the different bit settings for the Output Compare modes. Figure 15-2 illustrates the output compare operation for various modes. The user

TABLE 15-1: OUTPUT COMPARE MODES

application must disable the associated timer when writing to the Output Compare Control registers to avoid malfunctions.

| Note: | See Section 13. "Output Compare"       |

|-------|----------------------------------------|

|       | (DS70209) in the "dsPIC33F Family Ref- |

|       | erence Manual" for OCxR and OCxRS      |

|       | register restrictions.                 |

| OCM<2:0> Mode |                              | OCx Pin Initial State                                                   | OCx Interrupt Generation         |  |  |

|---------------|------------------------------|-------------------------------------------------------------------------|----------------------------------|--|--|

| 000           | Module Disabled              | Controlled by GPIO register                                             | _                                |  |  |

| 001           | Active-Low One-Shot          | 0                                                                       | OCx rising edge                  |  |  |

| 010           | Active-High One-Shot         | 1                                                                       | OCx falling edge                 |  |  |

| 011           | Toggle                       | Current output is maintained                                            | OCx rising and falling edge      |  |  |

| 100           | Delayed One-Shot             | 0                                                                       | OCx falling edge                 |  |  |

| 101           | Continuous Pulse             | 0                                                                       | OCx falling edge                 |  |  |

| 110           | PWM without Fault Protection | '0', if OCxR is zero<br>'1', if OCxR is non-zero                        | No interrupt                     |  |  |

| 111           | PWM with Fault Protection    | <ul><li>'0', if OCxR is zero</li><li>'1', if OCxR is non-zero</li></ul> | OCFA falling edge for OC1 to OC4 |  |  |

#### FIGURE 15-2: OUTPUT COMPARE OPERATION

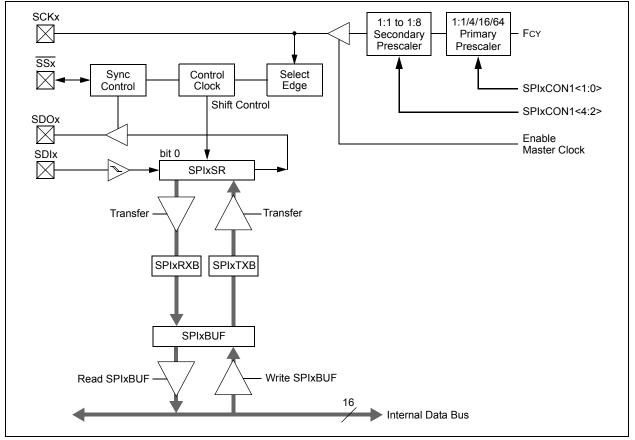

# 16.0 SERIAL PERIPHERAL INTERFACE (SPI)

This data sheet summarizes the features Note: of the dsPIC33FJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 18. "Serial Peripheral Interface (SPI)" (DS70206) in the "dsPIC33F Family Reference Manual", which is available the Microchip from web site (www.microchip.com).

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, ADC, etc. The SPI module is compatible with SPI and SIOP from Motorola<sup>®</sup>.

**Note:** In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers will follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 or SPI2 module. Each SPI module consists of a 16-bit shift register, SPIxSR (where x = 1 or 2), used for shifting data in and out, and a buffer register, SPIxBUF. A control register, SPIxCON, configures the module. Additionally, a status register, SPIxSTAT, indicates various status conditions.

The serial interface consists of 4 pins: SDIx (serial data input), SDOx (serial data output), SCKx (shift clock input or output), and SSx (active-low slave select).

In Master mode operation, SCK is a clock output but in Slave mode, it is a clock input.

### FIGURE 16-1: SPI MODULE BLOCK DIAGRAM

| F15MSK<br>bit 15<br>R/W-0<br>F11MSK<br>bit 7 | R/W-0                                        | F14MS                                                                         |                                    | F13MS                              | SK<1:0> | F12MS              | K<1:0> |  |

|----------------------------------------------|----------------------------------------------|-------------------------------------------------------------------------------|------------------------------------|------------------------------------|---------|--------------------|--------|--|

| R/W-0<br>F11MSk                              |                                              | R/W-0                                                                         |                                    |                                    |         |                    |        |  |

| F11MSk                                       |                                              | R/W-0                                                                         |                                    |                                    |         |                    | bit 8  |  |

|                                              | <<1:0>                                       |                                                                               | R/W-0                              | R/W-0                              | R/W-0   | R/W-0              | R/W-0  |  |

| bit 7                                        |                                              | F10MSK<1:0>                                                                   |                                    | F9MSK<1:0>                         |         | F8MSK<1:0>         |        |  |

|                                              |                                              | <u>.</u>                                                                      |                                    | •                                  |         |                    | bit C  |  |

| Legend:                                      |                                              |                                                                               |                                    |                                    |         |                    |        |  |

| R = Readable bit                             |                                              | W = Writable bit                                                              |                                    | U = Unimplemented bit, read as '0' |         |                    |        |  |

| -n = Value at POR                            |                                              | '1' = Bit is set                                                              |                                    | '0' = Bit is cleared               |         | x = Bit is unknown |        |  |

| bit 15-14                                    | 11 = Reserve<br>10 = Accepta<br>01 = Accepta | D>: Mask Sourc<br>ed<br>ance Mask 2 reg<br>ance Mask 1 reg<br>ance Mask 0 reg | gisters contail<br>gisters contail | n mask<br>n mask                   |         |                    |        |  |

bit 13-12 F14MSK<1:0>: Mask Source for Filter 14 bit (same values as bit 15-14)

bit 11-10 **F13MSK<1:0>:** Mask Source for Filter 13 bit (same values as bit 15-14)

bit 9-8 F12MSK<1:0>: Mask Source for Filter 12 bit (same values as bit 15-14)

bit 7-6 F11MSK<1:0>: Mask Source for Filter 11 bit (same values as bit 15-14)

bit 5-4 F10MSK<1:0>: Mask Source for Filter 10 bit (same values as bit 15-14)

bit 3-2 **F9MSK<1:0>:** Mask Source for Filter 9 bit (same values as bit 15-14)

bit 1-0 F8MSK<1:0>: Mask Source for Filter 8 bit (same values as bit 15-14)

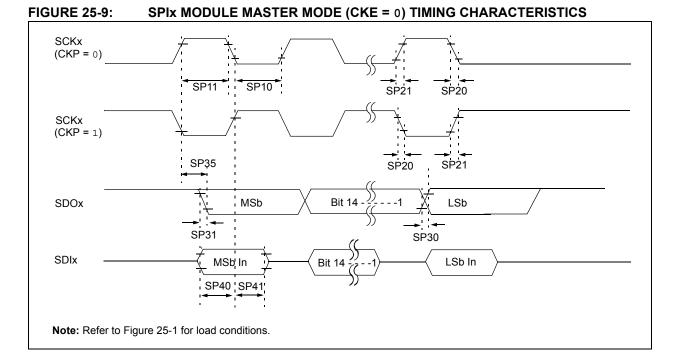

### TABLE 25-28: SPIx MASTER MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                            | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ |                    |     |       |                                         |

|--------------------|-----------------------|--------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|-----------------------------------------|

| Param<br>No.       | Symbol                | Characteristic <sup>(1)</sup>              | Min                                                                                                                              | Тур <sup>(2)</sup> | Max | Units | Conditions                              |