Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | dsPIC                                                                            |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                  |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT              |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 64KB (64K x 8)                                                                   |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 32x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp310t-i-pf |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Communication Modules:**

- · 3-wire SPI (up to two modules):

- Framing supports I/O interface to simple codecs

- Supports 8-bit and 16-bit data

- Supports all serial clock formats and sampling modes

- I<sup>2</sup>C<sup>™</sup> (up to two modules):

- Full Multi-Master Slave mode support

- 7-bit and 10-bit addressing

- Bus collision detection and arbitration

- Integrated signal conditioning

- Slave address masking

- UART (up to two modules):

- Interrupt on address bit detect

- Interrupt on UART error

- Wake-up on Start bit from Sleep mode

- 4-character TX and RX FIFO buffers

- LIN bus support

- IrDA® encoding and decoding in hardware

- High-Speed Baud mode

- Hardware Flow Control with CTS and RTS

- Data Converter Interface (DCI) module:

- Codec interface

- Supports I<sup>2</sup>S and AC'97 protocols

- Up to 16-bit data words, up to 16 words per frame

- 4-word deep TX and RX buffers

- Enhanced CAN (ECAN<sup>™</sup> module) 2.0B active (up to 2 modules):

- Up to eight transmit and up to 32 receive buffers

- 16 receive filters and three masks

- Loopback, Listen Only and Listen All Messages modes for diagnostics and bus monitoring

- Wake-up on CAN message

- Automatic processing of Remote Transmission Requests

- FIFO mode using DMA

- DeviceNet™ addressing support

### Analog-to-Digital Converters (ADCs):

- · Up to two ADC modules in a device

- 10-bit, 1.1 Msps or 12-bit, 500 ksps conversion:

- Two, four or eight simultaneous samples

- Up to 32 input channels with auto-scanning

- Conversion start can be manual or synchronized with one of four trigger sources

- Conversion possible in Sleep mode

- ±1 LSb max integral nonlinearity

- ±1 LSb max differential nonlinearity

### **CMOS Flash Technology:**

- · Low-power, high-speed Flash technology

- · Fully static design

- 3.3V (±10%) operating voltage

- Industrial temperature

- · Low-power consumption

### Packaging:

- 100-pin TQFP (14x14x1 mm and 12x12x1 mm)

- 80-pin TQFP (12x12x1 mm)

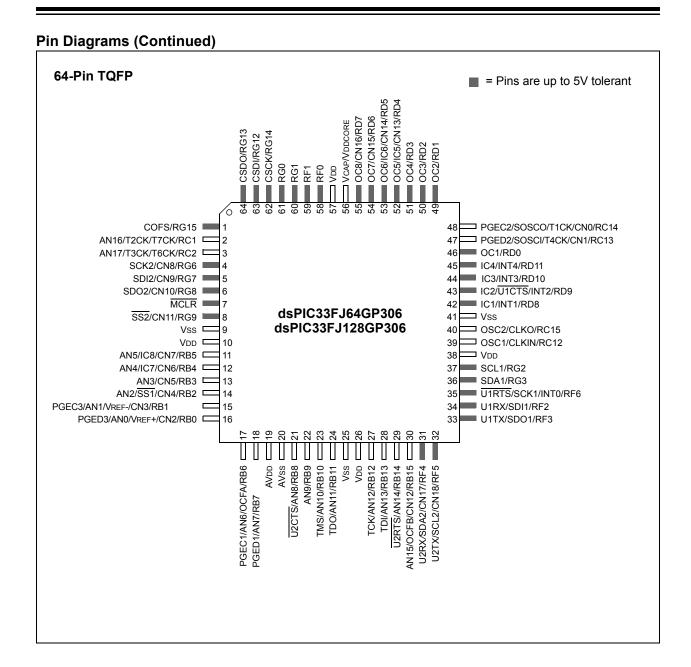

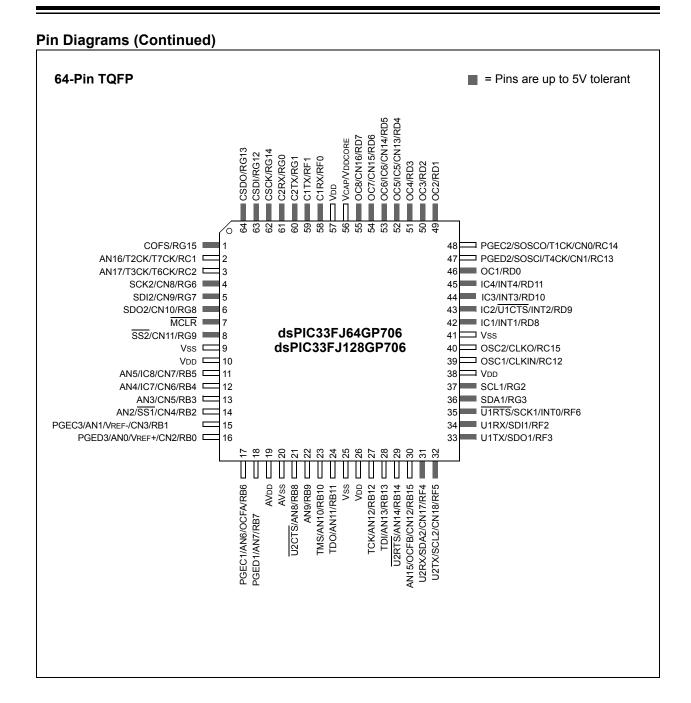

- 64-pin TQFP (10x10x1 mm)

**Note:** See the device variant tables for exact peripheral features per device.

### 1.0 DEVICE OVERVIEW

Note:

This data sheet summarizes the features of the dsPIC33FJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the latest family reference sections of the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

This document contains device specific information for the following devices:

- dsPIC33FJ64GP206

- dsPIC33FJ64GP306

- dsPIC33FJ64GP310

- dsPIC33FJ64GP706

- dsPIC33FJ64GP708

- dsPIC33FJ64GP710

- dsPIC33FJ128GP206

- dsPIC33FJ128GP306

- dsPIC33FJ128GP310

- dsPIC33FJ128GP706

- dsPIC33FJ128GP708

- dsPIC33FJ128GP710

- dsPIC33FJ256GP506

- dsPIC33FJ256GP510

- dsPIC33FJ256GP710

The dsPIC33FJXXXGPX06/X08/X10 General Purpose Family of device includes devices with a wide range of pin counts (64, 80 and 100), different program memory sizes (64 Kbytes, 128 Kbytes and 256 Kbytes) and different RAM sizes (8 Kbytes, 16 Kbytes and 30 Kbytes).

This feature makes the family suitable for a wide variety of high-performance digital signal control applications. The device is pin compatible with the PIC24H family of devices, and also share a very high degree of compatibility with the dsPIC30F family devices. This allows for easy migration between device families as may be necessitated by the specific functionality, computational resource and system cost requirements of the application.

The dsPIC33FJXXXGPX06/X08/X10 device family employs a powerful 16-bit architecture that seamlessly integrates the control features of a Microcontroller (MCU) with the computational capabilities of a Digital Signal Processor (DSP). The resulting functionality is ideal for applications that rely on high-speed, repetitive computations, as well as control.

The DSP engine, dual 40-bit accumulators, hardware support for division operations, barrel shifter, 17 x 17 multiplier, a large array of 16-bit working registers and a wide variety of data addressing modes, together provide the dsPIC33FJXXXGPX06/X08/X10 Central Processing Unit (CPU) with extensive mathematical processing capability. Flexible and deterministic interrupt handling, coupled with a powerful array of peripherals, renders dsPIC33FJXXXGPX06/X08/X10 devices suitable for control applications. Further, Direct Memory Access (DMA) enables overhead-free transfer of data between several peripherals and a dedicated DMA RAM. Reliable, field programmable Flash program memory ensures scalability of applications that use dsPIC33FJXXXGPX06/X08/X10 devices.

Figure 1-1 illustrates a general block diagram of the various core and peripheral modules in the dsPIC33FJXXXGPX06/X08/X10 family of devices. Table 1-1 provides the functions of the various pins illustrated in the pinout diagrams.

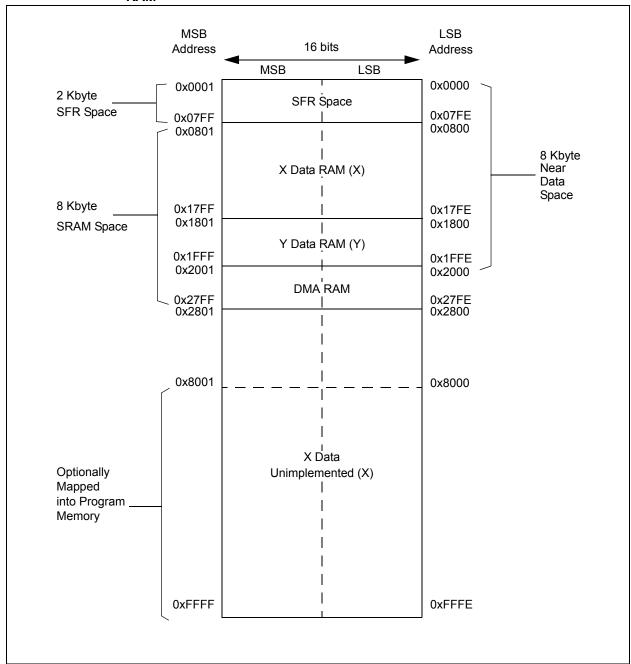

FIGURE 4-3: DATA MEMORY MAP FOR dsPIC33FJXXXGPX06/X08/X10 DEVICES WITH 8 KBS RAM

| TABLE 4-6: TIMER REGISTER M | IΔF | ? N | (FR | HRI | ?FG | TIMER | 4-6. | TARI F |  |

|-----------------------------|-----|-----|-----|-----|-----|-------|------|--------|--|

|-----------------------------|-----|-----|-----|-----|-----|-------|------|--------|--|

| SFR<br>Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9        | Bit 8        | Bit 7          | Bit 6          | Bit 5      | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-------------|-------------|--------|--------|--------|--------|--------|--------|--------------|--------------|----------------|----------------|------------|--------|-------|-------|-------|-------|---------------|

| TMR1        | 0100        |        |        |        |        |        |        |              | Timer1       | Register       |                |            |        |       |       |       |       | xxxx          |

| PR1         | 0102        |        |        |        |        |        |        |              | Period F     | Register 1     |                |            |        |       |       |       |       | FFFF          |

| T1CON       | 0104        | TON    | _      | TSIDL  | _      | _      | _      | _            | _            | _              | TGATE          | TCKP       | S<1:0> | _     | TSYNC | TCS   | _     | 0000          |

| TMR2        | 0106        |        |        |        |        |        |        |              | Timer2       | Register       |                |            |        |       |       |       |       | xxxx          |

| TMR3HLD     | 0108        |        |        |        |        |        | Tim    | ner3 Holding | Register (fo | r 32-bit time  | operations o   | only)      |        |       |       |       |       | xxxx          |

| TMR3        | 010A        |        |        |        |        |        |        |              | Timer3       | Register       |                |            |        |       |       |       |       | xxxx          |

| PR2         | 010C        |        |        |        |        |        |        |              | Period F     | Register 2     |                |            |        |       |       |       |       | FFFF          |

| PR3         | 010E        |        |        |        |        |        |        |              | Period F     | Register 3     |                |            |        |       |       |       |       | FFFF          |

| T2CON       | 0110        | TON    | -      | TSIDL  | -      | _      | -      | -            | _            | _              | TGATE          | TCKP       | S<1:0> | T32   | _     | TCS   | 1     | 0000          |

| T3CON       | 0112        | TON    | -      | TSIDL  | -      | _      | -      | -            | _            | _              | TGATE          | TCKP       | S<1:0> | _     | _     | TCS   | 1     | 0000          |

| TMR4        | 0114        |        |        |        |        |        |        |              | Timer4       | Register       |                |            |        |       |       |       |       | xxxx          |

| TMR5HLD     | 0116        |        |        |        |        |        | -      | Timer5 Hold  | ing Register | (for 32-bit or | erations only  | <b>y</b> ) |        |       |       |       |       | xxxx          |

| TMR5        | 0118        |        |        |        |        |        |        |              | Timer5       | Register       |                |            |        |       |       |       |       | xxxx          |

| PR4         | 011A        |        |        |        |        |        |        |              | Period F     | Register 4     |                |            |        |       |       |       |       | FFFF          |

| PR5         | 011C        |        |        |        |        |        |        |              | Period F     | Register 5     |                |            |        |       |       |       |       | FFFF          |

| T4CON       | 011E        | TON    | _      | TSIDL  | _      | _      | _      | _            | _            | _              | TGATE          | TCKP       | S<1:0> | T32   | _     | TCS   | _     | 0000          |

| T5CON       | 0120        | TON    | _      | TSIDL  | _      | _      | _      | _            | _            | _              | TGATE          | TCKP       | S<1:0> | _     | _     | TCS   | _     | 0000          |

| TMR6        | 0122        |        |        |        |        |        |        |              | Timer6       | Register       |                |            |        |       |       |       |       | xxxx          |

| TMR7HLD     | 0124        |        |        |        |        |        |        | Timer7 Hold  | ing Register | (for 32-bit or | perations only | <b>/</b> ) |        |       |       |       |       | xxxx          |

| TMR7        | 0126        |        |        |        |        |        |        |              | Timer7       | Register       |                |            |        |       |       |       |       | xxxx          |

| PR6         | 0128        |        |        |        |        |        |        |              | Period F     | Register 6     |                |            |        |       |       |       |       | FFFF          |

| PR7         | 012A        |        |        |        |        |        |        |              | Period F     | Register 7     |                |            |        |       |       |       |       | FFFF          |

| T6CON       | 012C        | TON    | _      | TSIDL  | _      | _      | _      | _            | _            | _              | TGATE          | TCKP       | S<1:0> | T32   | _     | TCS   | _     | 0000          |

| T7CON       | 012E        | TON    | _      | TSIDL  | _      | _      | _      | _            | _            | _              | TGATE          | TCKP       | S<1:0> | _     | _     | TCS   | _     | 0000          |

| TMR8        | 0130        |        |        |        |        |        |        |              | Timer8       | Register       |                |            |        |       |       |       |       | xxxx          |

| TMR9HLD     | 0132        |        |        |        |        |        | -      | Timer9 Hold  | ing Register | (for 32-bit or | perations only | <b>y</b> ) |        |       |       |       |       | xxxx          |

| TMR9        | 0134        |        |        |        |        |        |        |              | Timer9       | Register       |                |            |        |       |       |       |       | xxxx          |

| PR8         | 0136        |        |        |        |        |        |        |              | Period F     | Register 8     |                |            |        |       |       |       |       | FFFF          |

| PR9         | 0138        |        |        |        |        |        |        |              | Period F     | Register 9     |                |            |        |       |       |       |       | FFFF          |

| T8CON       | 013A        | TON    |        | TSIDL  |        |        |        |              |              |                | TGATE          | TCKP       | S<1:0> | T32   |       | TCS   |       | 0000          |

| T9CON       | 013C        | TON    | _      | TSIDL  |        |        |        |              | _            | _              | TGATE          | TCKP       | S<1:0> |       |       | TCS   | _     | 0000          |

**Legend:** x = unknown value on Reset, --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| <b>TABLE 4-7</b> : | INPUT CAPTURE REGISTER MAP |  |

|--------------------|----------------------------|--|

|                    |                            |  |

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8      | Bit 7        | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

|----------|-------------|--------|--------|--------|--------|--------|--------|-------|------------|--------------|-------|-------|-------|-------|-------|----------|-------|---------------|

| IC1BUF   | 0140        |        |        |        |        |        |        |       | Input 1 Ca | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC1CON   | 0142        | _      | _      | ICSIDL |        | ı      | -      | _     | -          | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC2BUF   | 0144        |        |        |        |        |        |        |       | Input 2 Ca | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC2CON   | 0146        | _      | _      | ICSIDL | -      | _      | _      | _     | _          | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC3BUF   | 0148        |        |        |        |        |        |        |       | Input 3 Ca | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC3CON   | 014A        | _      | -      | ICSIDL | 1      | _      | _      | _     | _          | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC4BUF   | 014C        |        |        |        |        |        |        |       | Input 4 Ca | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC4CON   | 014E        | _      | _      | ICSIDL | -      | _      | _      | _     | _          | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC5BUF   | 0150        |        |        |        |        |        |        |       | Input 5 Ca | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC5CON   | 0152        | _      | _      | ICSIDL | -      | _      | _      | _     | _          | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC6BUF   | 0154        |        |        |        |        |        |        |       | Input 6 Ca | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC6CON   | 0156        | _      | _      | ICSIDL | -      | _      | _      | _     | _          | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC7BUF   | 0158        |        |        |        |        |        |        |       | Input 7 Ca | pture Regist | er    |       |       |       |       |          |       | xxxx          |

| IC7CON   | 015A        | _      | _      | ICSIDL | -      | -      | _      | _     | _          | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

| IC8BUF   | 015C        |        |        | •      |        |        | •      | •     | Input 8 Ca | pture Regist | er    |       |       |       | •     | •        | •     | xxxx          |

| IC8CON   | 015E        | _      | _      | ICSIDL | _      | _      | _      | _     | _          | ICTMR        | ICI<  | 1:0>  | ICOV  | ICBNE |       | ICM<2:0> |       | 0000          |

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

© 2009 Microchip Technology Inc.

TABLE 4-23: ECAN2 REGISTER MAP WHEN C2CTRL1.WIN = 1 FOR dsPIC33FJXXXGP706/708/710 DEVICES ONLY

| File Name  | Addr      | Bit 15    | Bit 14                | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9  | Bit 8                         | Bit 7               | Bit 6    | Bit 5  | Bit 4 | Bit 3      | Bit 2 | Bit 1  | Bit 0  | AII<br>Resets |

|------------|-----------|-----------|-----------------------|--------|--------|--------|--------|--------|-------------------------------|---------------------|----------|--------|-------|------------|-------|--------|--------|---------------|

|            | 0500      |           |                       | ·•     |        |        |        | Se     | e definition                  | when WIN            | I = x    | •      |       | · <u>·</u> | •     |        |        |               |

|            | -<br>051E |           |                       |        |        |        |        |        |                               |                     |          |        |       |            |       |        |        |               |

| C2BUFPNT1  | 0520      |           | F3BF                  | P<3:0> |        |        | F2BP   | <3:0>  |                               |                     | F1BF     | 2<3:0> |       |            | F0BF  | P<3:0> |        | 0000          |

| C2BUFPNT2  | 0522      |           | F7BF                  | P<3:0> |        |        | F6BP   | <3:0>  |                               |                     | F5BP     | 2<3:0> |       |            | F4BF  | P<3:0> |        | 0000          |

| C2BUFPNT3  | 0524      |           | F11Bl                 | P<3:0> |        |        | F10BF  | P<3:0> |                               |                     | F9BF     | >3:0>  |       |            | F8BF  | P<3:0> |        | 0000          |

| C2BUFPNT4  | 0526      |           | F15BP<3:0> F14BP<3:0> |        |        |        |        |        |                               |                     | F13BF    | P<3:0> |       |            | F12B  | P<3:0> |        | 0000          |

| C2RXM0SID  | 0530      |           | SID<10:3>             |        |        |        |        |        |                               | SID<2:0> — MIDE — E |          |        | EID<  | 17:16>     | xxxx  |        |        |               |

| C2RXM0EID  | 0532      | EID<15:8> |                       |        |        |        |        |        |                               |                     |          |        | EID   | <7:0>      |       |        |        | xxxx          |

| C2RXM1SID  | 0534      |           |                       |        | SID<   | 10:3>  |        |        |                               |                     | SID<2:0> |        | _     | MIDE       | _     | EID<   | 17:16> | xxxx          |

| C2RXM1EID  | 0536      | EID<15:8> |                       |        |        |        |        |        | EID<7:0>                      |                     |          |        |       |            |       | xxxx   |        |               |

| C2RXM2SID  | 0538      | SID<10:3> |                       |        |        |        |        |        |                               | SID<2:0>            |          | _      | MIDE  | _          | EID<  | 17:16> | xxxx   |               |

| C2RXM2EID  | 053A      |           | EID<15:8> EID<7:0>    |        |        |        |        |        |                               |                     |          |        |       |            | xxxx  |        |        |               |

| C2RXF0SID  | 0540      |           |                       |        |        |        |        | EID<   | 17:16>                        | xxxx                |          |        |       |            |       |        |        |               |

| C2RXF0EID  | 0542      | EID<15:8> |                       |        |        |        |        |        |                               |                     |          | EID    | <7:0> |            |       |        | xxxx   |               |

| C2RXF1SID  | 0544      |           |                       |        | SID<   | 10:3>  |        |        |                               |                     | SID<2:0> |        | _     | EXIDE      | _     | EID<   | 17:16> | xxxx          |

| C2RXF1EID  | 0546      |           |                       |        | EID<   | 15:8>  |        |        |                               |                     |          |        | EID   | <7:0>      |       |        |        | xxxx          |

| C2RXF2SID  | 0548      |           |                       |        | SID<   | 10:3>  |        |        |                               |                     | SID<2:0> |        | _     | EXIDE      | _     | EID<   | 17:16> | xxxx          |

| C2RXF2EID  | 054A      |           |                       |        | EID<   | 15:8>  |        |        |                               | EID<7:0>            |          |        |       |            |       |        | xxxx   |               |

| C2RXF3SID  | 054C      |           |                       |        | SID<   | 10:3>  |        |        |                               |                     | SID<2:0> |        | _     | EXIDE      | _     | EID<   | 17:16> | xxxx          |

| C2RXF3EID  | 054E      |           |                       |        | EID<   | 15:8>  |        |        |                               |                     |          |        | EID   | <7:0>      |       |        |        | xxxx          |

| C2RXF4SID  | 0550      |           |                       |        | SID<   | 10:3>  |        |        |                               |                     | SID<2:0> |        | _     | EXIDE      | _     | EID<   | 17:16> | xxxx          |

| C2RXF4EID  | 0552      |           |                       |        | EID<   | 15:8>  |        |        |                               |                     |          |        | EID   | <7:0>      |       |        |        | xxxx          |

| C2RXF5SID  | 0554      |           |                       |        | SID<   | 10:3>  |        |        |                               |                     | SID<2:0> |        | _     | EXIDE      | _     | EID<   | 17:16> | xxxx          |

| C2RXF5EID  | 0556      |           |                       |        | EID<   | 15:8>  |        |        |                               |                     |          |        | EID   | <7:0>      |       |        |        | xxxx          |

| C2RXF6SID  | 0558      |           |                       |        | SID<   | 10:3>  |        |        |                               |                     | SID<2:0> |        | _     | EXIDE      | _     | EID<   | 17:16> | xxxx          |

| C2RXF6EID  | 055A      |           |                       |        | EID<   | 15:8>  |        |        |                               |                     |          |        | EID   | <7:0>      |       |        |        | xxxx          |

| C2RXF7SID  | 055C      |           |                       |        | SID<   | 10:3>  |        |        |                               |                     | SID<2:0> |        | _     | EXIDE      | _     | EID<   | 17:16> | xxxx          |

| C2RXF7EID  | 055E      |           |                       |        |        |        |        |        | EID<7:0>                      |                     |          |        |       |            | xxxx  |        |        |               |

| C2RXF8SID  | 0560      | SID<10:3> |                       |        |        |        |        |        | SID<2:0> — EXIDE — EID<17:16> |                     |          |        |       | 17:16>     | xxxx  |        |        |               |

| C2RXF8EID  | 0562      |           |                       |        |        |        |        |        | EID<7:0>                      |                     |          |        |       |            | xxxx  |        |        |               |

| C2RXF9SID  | 0564      |           |                       |        |        |        |        |        | SID<2:0>                      |                     |          |        |       | 17:16>     | xxxx  |        |        |               |

| C2RXF9EID  | 0566      |           |                       |        |        |        |        |        |                               |                     |          | xxxx   |       |            |       |        |        |               |

| C2RXF10SID | 0568      |           |                       |        | SID<   | 10:3>  |        |        |                               |                     | SID<2:0> |        | _     | EXIDE      | _     | EID<   | 17:16> | xxxx          |

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

# 4.6 Interfacing Program and Data Memory Spaces

The dsPIC33FJXXXGPX06/X08/X10 architecture uses a 24-bit wide program space and a 16-bit wide data space. The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the dsPIC33FJXXXGPX06/X08/X10 architecture provides two methods by which program space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the program space

- Remapping a portion of the program space into the data space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated from time to time. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look ups from a large table of static data. It can only access the least significant word of the program word.

#### 4.6.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Page register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the Most Significant bit of TBLPAG is used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

For remapping operations, the 8-bit Program Space Visibility register (PSVPAG) is used to define a 16K word page in the program space. When the Most Significant bit of the EA is '1', PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space address. Unlike table operations, this limits remapping operations strictly to the user memory area.

Table 4-37 and Figure 4-9 show how the program EA is created for table operations and remapping accesses from the data EA. Here, P<23:0> refers to a program space word, whereas D<15:0> refers to a data space word.

TABLE 4-37: PROGRAM SPACE ADDRESS CONSTRUCTION

| Access Time                                             | Access        | Program Space Address |            |               |               |       |  |  |  |

|---------------------------------------------------------|---------------|-----------------------|------------|---------------|---------------|-------|--|--|--|

| Access Type                                             | Space         | <23>                  | <22:16>    | <15>          | <14:1>        | <0>   |  |  |  |

| Instruction Access                                      | User          | 0                     |            | PC<22:1>      | •             | 0     |  |  |  |

| (Code Execution)                                        |               |                       | 0xx xxxx x | xxx xxx       | xx xxxx xxx0  |       |  |  |  |

| TBLRD/TBLWT                                             | User          | ТВ                    | LPAG<7:0>  | Data EA<15:0> |               |       |  |  |  |

| (Byte/Word Read/Write)                                  |               | 0                     | xxx xxxx   | xxxx xx       | xx xxxx xxxx  |       |  |  |  |

|                                                         | Configuration | ТВ                    | LPAG<7:0>  |               | Data EA<15:0> |       |  |  |  |

| 1xxx xxxx                                               |               |                       |            |               |               |       |  |  |  |

| Program Space Visibility                                | User          | 0                     | PSVPAG<7   | <b>'</b> :0>  | Data EA<14:   | 0>(1) |  |  |  |

| (Block Remap/Read) 0 xxxx xxxx xxxx xxxx xxxx xxxx xxxx |               |                       |            |               |               | xxxx  |  |  |  |

Note 1: Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

#### REGISTER 7-11: IEC1: INTERRUPT ENABLE CONTROL REGISTER 1

| R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  |

|--------|--------|--------|-------|-------|-------|-------|--------|

| U2TXIE | U2RXIE | INT2IE | T5IE  | T4IE  | OC4IE | OC3IE | DMA2IE |

| bit 15 |        |        |       |       |       |       | bit 8  |

| R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 | U-0 | R/W-0   | R/W-0   |

|-------|-------|-------|--------|-------|-----|---------|---------|

| IC8IE | IC7IE | AD2IE | INT1IE | CNIE  | _   | MI2C1IE | SI2C1IE |

| bit 7 |       |       |        |       |     |         | bit 0   |

Legend:

bit 11

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15 **U2TXIE:** UART2 Transmitter Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 14 **U2RXIE:** UART2 Receiver Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 13 INT2IE: External Interrupt 2 Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 12 **T5IE:** Timer5 Interrupt Enable bit

1 = Interrupt request enabled

0 = Interrupt request not enabledT4IE: Timer4 Interrupt Enable bit

1 = Interrupt request enabled

0 = Interrupt request not enabled

bit 10 OC4IE: Output Compare Channel 4 Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 9 OC3IE: Output Compare Channel 3 Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 8 DMA2IE: DMA Channel 2 Data Transfer Complete Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 7 IC8IE: Input Capture Channel 8 Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 6 IC7IE: Input Capture Channel 7 Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 5 AD2IE: ADC2 Conversion Complete Interrupt Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

bit 4 INT1IE: External Interrupt 1 Enable bit

1 = Interrupt request enabled0 = Interrupt request not enabled

#### REGISTER 7-31: IPC16: INTERRUPT PRIORITY CONTROL REGISTER 16

| U-0    | U-0 | U-0 | U-0 | U-0 | R/W-1 | R/W-0      | R/W-0 |

|--------|-----|-----|-----|-----|-------|------------|-------|

| _      | _   | _   | _   | _   |       | U2EIP<2:0> |       |

| bit 15 |     |     |     |     |       |            | bit 8 |

| U-0   | R/W-1 | R/W-0      | R/W-0 | U-0 | U-0 | U-0 | U-0   |

|-------|-------|------------|-------|-----|-----|-----|-------|

| _     |       | U1EIP<2:0> |       | _   | _   | _   | _     |

| bit 7 |       |            |       |     |     |     | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-11 **Unimplemented:** Read as '0'

bit 10-8 **U2EIP<2:0>:** UART2 Error Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

.

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 7 **Unimplemented:** Read as '0'

bit 6-4 **U1EIP<2:0>:** UART1 Error Interrupt Priority bits

111 = Interrupt is priority 7 (highest priority interrupt)

•

•

•

001 = Interrupt is priority 1

000 = Interrupt source is disabled

bit 3-0 **Unimplemented:** Read as '0'

NOTES:

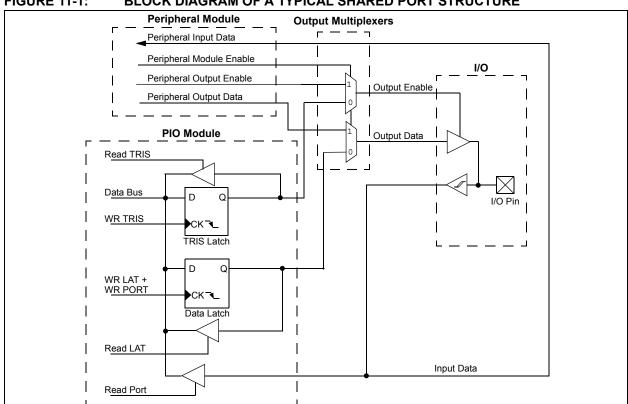

### 11.0 I/O PORTS

Note: This data sheet summarizes the features of the dsPIC33FJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 10. "I/O Ports" (DS70193) in the "dsPIC33F Family Reference Manual", which is avail-

able from the Microchip web site

All of the device pins (except VDD, VSS, MCLR and OSC1/CLKIN) are shared between the peripherals and the parallel I/O ports. All I/O input ports feature Schmitt Trigger inputs for improved noise immunity.

(www.microchip.com).

### 11.1 Parallel I/O (PIO) Ports

A parallel I/O port that shares a pin with a peripheral is, in general, subservient to the peripheral. The peripheral's output buffer data and control signals are provided to a pair of multiplexers. The multiplexers select whether the peripheral or the associated port has ownership of the output data and control signals of the I/O pin. The logic also prevents "loop through", in which a port's digital output can drive the input of a peripheral that shares the same pin. Figure 11-1 illustrates how ports are shared with other peripherals and the associated I/O pin to which they are connected.

When a peripheral is enabled and actively driving an associated pin, the use of the pin as a general purpose output pin is disabled. The I/O pin may be read, but the output driver for the parallel port bit will be disabled. If a peripheral is enabled, but the peripheral is not actively driving a pin, that pin may be driven by a port.

All port pins have three registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx), read the latch. Writes to the latch, write the latch. Reads from the port (PORTx), read the port pins, while writes to the port pins, write the latch.

Any bit and its associated data and control registers that are not valid for a particular device will be disabled. That means the corresponding LATx and TRISx registers and the port pins will read as zeros.

When a pin is shared with another peripheral or function that is defined as an input only, it is nevertheless regarded as a dedicated port because there is no other competing source of outputs. An example is the INT4 pin.

**Note:** The voltage on a digital input pin can be between -0.3V to 5.6V.

FIGURE 11-1: BLOCK DIAGRAM OF A TYPICAL SHARED PORT STRUCTURE

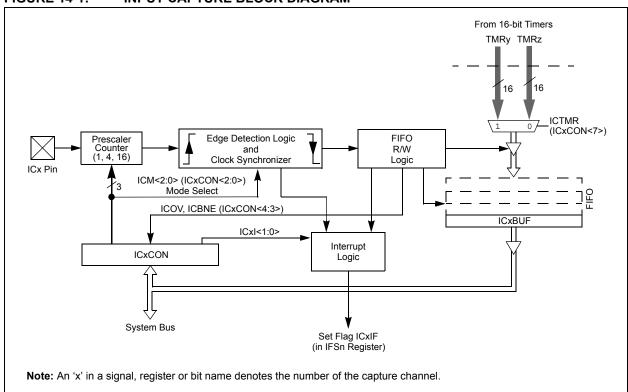

### 14.0 INPUT CAPTURE

Note:

This data sheet summarizes the features of the dsPIC33FJXXXGPX06/X08/X10 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 12**. **"Input Capture"** (DS70198) in the "dsPIC33F Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The input capture module is useful in applications requiring frequency (period) and pulse measurement. The dsPIC33FJXXXGPX06/X08/X10 devices support up to eight input capture channels.

The input capture module captures the 16-bit value of the selected Time Base register when an event occurs at the ICx pin. The events that cause a capture event are listed below in three categories:

- 1. Simple Capture Event modes

- -Capture timer value on every falling edge of input at ICx pin

- Capture timer value on every rising edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- 3. Prescaler Capture Event modes

- -Capture timer value on every 4th rising edge of input at ICx pin

- -Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during CPU Sleep and Idle modes

- · Interrupt on input capture event

- · 4-word FIFO buffer for capture values

- Interrupt optionally generated after 1, 2, 3 or 4 buffer locations are filled

- Input capture can also be used to provide additional sources of external interrupts

Note: Only IC1 and IC2 can trigger a DMA data transfer. If DMA data transfers are required, the FIFO buffer size must be set to 1 (ICI<1:0> = 00).

FIGURE 14-1: INPUT CAPTURE BLOCK DIAGRAM

NOTES:

### REGISTER 19-15: CiBUFPNT4: ECAN™ FILTER 12-15 BUFFER POINTER REGISTER

| R/W-0  | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0  | R/W-0 |

|--------|-------|-------|-------|-------|-------|--------|-------|

|        | F15BP | <3:0> |       |       | F14BF | P<3:0> |       |

| bit 15 |       |       |       |       |       |        | bit 8 |

| R/W-0 | R/W-0 | R/W-0 | R/W-0 | R/W-0      | R/W-0 | R/W-0 | R/W-0 |  |

|-------|-------|-------|-------|------------|-------|-------|-------|--|

|       | F13BP | <3:0> |       | F12BP<3:0> |       |       |       |  |

| bit 7 |       |       |       |            |       |       | bit 0 |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-12 F15BP<3:0>: RX Buffer Written when Filter 15 Hits bits bit 11-8 F14BP<3:0>: RX Buffer Written when Filter 14 Hits bits bit 7-4 F13BP<3:0>: RX Buffer Written when Filter 13 Hits bits bit 3-0 F12BP<3:0>: RX Buffer Written when Filter 12 Hits bits

TABLE 22-2: dsPIC33FJXXXGPX06/X08/X10 CONFIGURATION BITS DESCRIPTION (CONTINUED)

| Bit Field   | Register | Description                                                                                                                                                                                                                                                                                                                                                                         |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IESO        | FOSCSEL  | Two-speed Oscillator Start-up Enable bit  1 = Start-up device with FRC, then automatically switch to the user-selected oscillator source when ready  0 = Start-up device with user-selected oscillator source                                                                                                                                                                       |

| FNOSC<2:0>  | FOSCSEL  | Initial Oscillator Source Selection bits  111 = Internal Fast RC (FRC) oscillator with postscaler  110 = Internal Fast RC (FRC) oscillator with divide-by-16  101 = LPRC oscillator  100 = Secondary (LP) oscillator  011 = Primary (XT, HS, EC) oscillator with PLL  010 = Primary (XT, HS, EC) oscillator  001 = Internal Fast RC (FRC) oscillator with PLL  000 = FRC oscillator |

| FCKSM<1:0>  | FOSC     | Clock Switching Mode bits  1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled  01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled  00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                                                                                                         |

| OSCIOFNC    | FOSC     | OSC2 Pin Function bit (except in XT and HS modes)  1 = OSC2 is clock output  0 = OSC2 is general purpose digital I/O pin                                                                                                                                                                                                                                                            |

| POSCMD<1:0> | FOSC     | Primary Oscillator Mode Select bits  11 = Primary oscillator disabled  10 = HS Crystal Oscillator mode  01 = XT Crystal Oscillator mode  00 = EC (External Clock) mode                                                                                                                                                                                                              |

| FWDTEN      | FWDT     | Watchdog Timer Enable bit  1 = Watchdog Timer always enabled (LPRC oscillator cannot be disabled. Clearing the SWDTEN bit in the RCON register will have no effect.)  0 = Watchdog Timer enabled/disabled by user software (LPRC can be disabled by clearing the SWDTEN bit in the RCON register)                                                                                   |

| WINDIS      | FWDT     | Watchdog Timer Window Enable bit  1 = Watchdog Timer in Non-Window mode  0 = Watchdog Timer in Window mode                                                                                                                                                                                                                                                                          |

| WDTPRE      | FWDT     | Watchdog Timer Prescaler bit 1 = 1:128 0 = 1:32                                                                                                                                                                                                                                                                                                                                     |

| WDTPOST     | FWDT     | Watchdog Timer Postscaler bits  1111 = 1:32,768  1110 = 1:16,384                                                                                                                                                                                                                                                                                                                    |

| JTAGEN      | FICD     | JTAG Enable bits 1 = JTAG enabled 0 = JTAG disabled                                                                                                                                                                                                                                                                                                                                 |

| ICS<1:0>    | FICD     | ICD Communication Channel Select bits  11 = Communicate on PGEC1 and PGED1  10 = Communicate on PGEC2 and PGED2  01 = Communicate on PGEC3 and PGED3  00 = Reserved                                                                                                                                                                                                                 |

**TABLE 23-2: INSTRUCTION SET OVERVIEW**

| Base<br>Instr<br># | Assembly<br>Mnemonic |          | Assembly Syntax Description |                                          | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|----------|-----------------------------|------------------------------------------|---------------|----------------|--------------------------|

| 1                  | ADD                  | ADD      | Acc                         | Add Accumulators                         | 1             | 1              | OA,OB,SA,SB              |

|                    |                      | ADD      | f                           | f = f + WREG                             | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD      | f,WREG                      | WREG = f + WREG                          | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD      | #lit10,Wn                   | Wd = lit10 + Wd                          | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD      | Wb,Ws,Wd                    | Wd = Wb + Ws                             | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD      | Wb,#lit5,Wd                 | Wd = Wb + lit5                           | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADD      | Wso,#Slit4,Acc              | 16-bit Signed Add to Accumulator         | 1             | 1              | OA,OB,SA,SB              |

| 2                  | ADDC                 | ADDC     | f                           | f = f + WREG + (C)                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADDC     | f,WREG                      | WREG = f + WREG + (C)                    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADDC     | #lit10,Wn                   | Wd = lit10 + Wd + (C)                    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADDC     | Wb,Ws,Wd                    | Wd = Wb + Ws + (C)                       | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | ADDC     | Wb,#lit5,Wd                 | Wd = Wb + lit5 + (C)                     | 1             | 1              | C,DC,N,OV,Z              |

| 3                  | AND                  | AND      | f                           | f = f .AND. WREG                         | 1             | 1              | N,Z                      |

|                    |                      | AND      | f,WREG                      | WREG = f .AND. WREG                      | 1             | 1              | N,Z                      |

|                    |                      | AND      | #lit10,Wn                   | Wd = lit10 .AND. Wd                      | 1             | 1              | N,Z                      |

|                    |                      | AND      | Wb,Ws,Wd                    | Wd = Wb .AND. Ws                         | 1             | 1              | N,Z                      |

|                    |                      | AND      | Wb,#lit5,Wd                 | Wd = Wb .AND. lit5                       | 1             | 1              | N,Z                      |

| 4                  | ASR                  | ASR      | f                           | f = Arithmetic Right Shift f             | 1             | 1              | C,N,OV,Z                 |

|                    |                      | ASR      | f,WREG                      | WREG = Arithmetic Right Shift f          | 1             | 1              | C,N,OV,Z                 |

|                    |                      | ASR      | Ws,Wd                       | Wd = Arithmetic Right Shift Ws           | 1             | 1              | C,N,OV,Z                 |

|                    |                      | ASR      | Wb, Wns, Wnd                | Wnd = Arithmetic Right Shift Wb by Wns   | 1             | 1              | N,Z                      |

|                    |                      | ASR      | Wb,#lit5,Wnd                | Wnd = Arithmetic Right Shift Wb by lit5  | 1             | 1              | N,Z                      |

| 5                  | BCLR                 | BCLR     | f,#bit4                     | Bit Clear f                              | 1             | 1              | None                     |

|                    |                      | BCLR     | Ws,#bit4                    | Bit Clear Ws                             | 1             | 1              | None                     |

| 6                  | BRA                  | BRA      | C,Expr                      | Branch if Carry                          | 1             | 1 (2)          | None                     |

|                    |                      | BRA      | GE, Expr                    | Branch if greater than or equal          | 1             | 1 (2)          | None                     |

|                    |                      | BRA      | GEU, Expr                   | Branch if unsigned greater than or equal | 1             | 1 (2)          | None                     |

|                    |                      | BRA      | GT, Expr                    | Branch if greater than                   | 1             | 1 (2)          | None                     |

|                    |                      | BRA      | GTU, Expr                   | Branch if unsigned greater than          | 1             | 1 (2)          | None                     |

|                    |                      | BRA      | LE, Expr                    | Branch if less than or equal             | 1             | 1 (2)          | None                     |

|                    |                      | BRA      | LEU, Expr                   | Branch if unsigned less than or equal    | 1             | 1 (2)          | None                     |

|                    |                      | BRA      | LT, Expr                    | Branch if less than                      | 1             | 1 (2)          | None                     |

|                    |                      | BRA      | LTU, Expr                   | Branch if unsigned less than             | 1             | 1 (2)          | None                     |

|                    |                      | BRA      | N, Expr                     | Branch if Negative                       | 1             | 1 (2)          | None                     |

|                    |                      | BRA      | NC, Expr                    | Branch if Not Carry                      | 1             | 1 (2)          | None                     |

|                    |                      | BRA      | NN, Expr                    | Branch if Not Negative                   | 1             | 1 (2)          | None                     |

|                    |                      | BRA      | NOV, Expr                   | Branch if Not Overflow                   | 1             | 1 (2)          | None                     |

|                    |                      | BRA      | NZ,Expr                     | Branch if Not Zero                       | 1             | 1 (2)          | None                     |

|                    |                      | BRA      | OA, Expr                    | Branch if Accumulator A overflow         | 1             | 1 (2)          | None                     |

|                    |                      | BRA      | OB, Expr                    | Branch if Accumulator B overflow         | 1             | 1 (2)          | None                     |

|                    |                      | BRA      | OV, Expr                    | Branch if Overflow                       | 1             | 1 (2)          | None                     |

|                    |                      | BRA      | SA, Expr                    | Branch if Accumulator A saturated        | 1             | 1 (2)          | None                     |

|                    |                      | BRA      | SB, Expr                    | Branch if Accumulator B saturated        | 1             | 1 (2)          | None                     |

|                    |                      | BRA      | Expr                        | Branch Unconditionally                   | 1             | 2              | None                     |

|                    |                      | BRA      | Z,Expr                      | Branch if Zero                           | 1             | 1 (2)          | None                     |

|                    |                      | BRA      | Wn                          | Computed Branch                          | 1             | 2              | None                     |

| 7                  | BSET                 | BSET     | f,#bit4                     | Bit Set f                                | 1             | 1              | None                     |

| •                  | 2021                 | BSET     | Ws,#bit4                    | Bit Set Ws                               | 1             | 1              | None                     |

| 8                  | BSW                  | BSW.C    | Ws, Wb                      | Write C bit to Ws <wb></wb>              | 1             | 1              | None                     |

| J                  | MOG                  | BSW.Z    | Ws,Wb                       | Write Z bit to Ws <wb></wb>              | 1             | 1              | None                     |

|                    | BTG                  | BTG      | f,#bit4                     | Bit Toggle f                             | 1             | 1              | None                     |

| 9                  |                      | I D I CT | 1, #D1L4                    | I DIL IUQQIE I                           | 1 1           | 1 1            | INUITE                   |

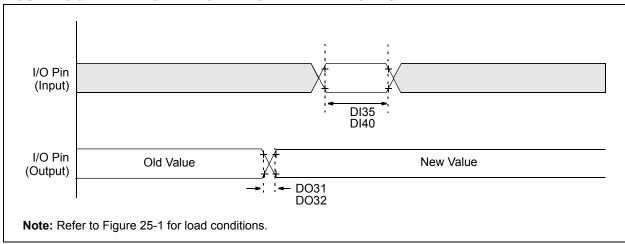

### FIGURE 25-3: CLKO AND I/O TIMING CHARACTERISTICS

#### **TABLE 25-20: I/O TIMING REQUIREMENTS**

| TABLE 20 20: I/O TIMINO NEGOTIEMENTO |        |                       |                                                                                                                                |                    |     |       |            |  |  |

|--------------------------------------|--------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|------------|--|--|

| AC CHARACTERISTICS                   |        |                       | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)  Operating temperature -40°C ≤ TA ≤ +85°C for Industrial |                    |     |       |            |  |  |

| Param<br>No.                         | Symbol | Character             | Min                                                                                                                            | Typ <sup>(1)</sup> | Max | Units | Conditions |  |  |

| DO31                                 | TioR   | Port Output Rise Time | _                                                                                                                              | 10                 | 25  | ns    | _          |  |  |

| DO32                                 | TioF   | Port Output Fall Time | _                                                                                                                              | 10                 | 25  | ns    | _          |  |  |

| DI35                                 | TINP   | INTx Pin High or Low  | 20                                                                                                                             | _                  | _   | ns    | _          |  |  |

| DI40                                 | TRBP   | CNx High or Low Tim   | 2                                                                                                                              | _                  | _   | Tcy   | _          |  |  |

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

TABLE 25-34: DCI MODULE (MULTI-CHANNEL, I<sup>2</sup>S MODES) TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                                                          | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated) Operating temperature $-40^{\circ}\text{C} \le \text{Ta} \le +85^{\circ}\text{C}$ for Industrial |                    |     |       |            |  |

|--------------------|--------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|-----|-------|------------|--|

| Param<br>No.       | Symbol | mbol Characteristic <sup>(1)</sup>                                       |                                                                                                                                                                        | Typ <sup>(2)</sup> | Max | Units | Conditions |  |

| CS10               | TCSCKL | CSCK Input Low Time<br>(CSCK pin is an input)                            | Tcy/2 + 20                                                                                                                                                             | _                  | _   | ns    | _          |  |

|                    |        | CSCK Output Low Time <sup>(3)</sup> (CSCK pin is an output)              | 30                                                                                                                                                                     | _                  | _   | ns    | _          |  |

| CS11               | Тсѕскн | CSCK Input High Time (CSCK pin is an input)                              | Tcy/2 + 20                                                                                                                                                             |                    | _   | ns    | _          |  |

|                    |        | CSCK Output High Time <sup>(3)</sup> (CSCK pin is an output)             | 30                                                                                                                                                                     | _                  | _   | ns    | _          |  |

| CS20               | TCSCKF | CSCK Output Fall Time <sup>(4)</sup><br>(CSCK pin is an output)          | _                                                                                                                                                                      | 10                 | 25  | ns    | _          |  |

| CS21               | TCSCKR | CSCK Output Rise Time <sup>(4)</sup> (CSCK pin is an output)             | _                                                                                                                                                                      | 10                 | 25  | ns    | _          |  |

| CS30               | TCSDOF | CSDO Data Output Fall Time(4)                                            | _                                                                                                                                                                      | 10                 | 25  | ns    | _          |  |

| CS31               | TCSDOR | CSDO Data Output Rise Time(4)                                            | _                                                                                                                                                                      | 10                 | 25  | ns    | _          |  |

| CS35               | TDV    | Clock Edge to CSDO Data Valid                                            | _                                                                                                                                                                      | _                  | 10  | ns    | _          |  |

| CS36               | TDIV   | Clock Edge to CSDO Tri-Stated                                            | 10                                                                                                                                                                     | _                  | 20  | ns    | _          |  |

| CS40               | TCSDI  | Setup Time of CSDI Data Input to CSCK Edge (CSCK pin is input or output) | 20                                                                                                                                                                     | _                  | _   | ns    | _          |  |

| CS41               | THCSDI | Hold Time of CSDI Data Input to CSCK Edge (CSCK pin is input or output)  | 20                                                                                                                                                                     | _                  | _   | ns    | _          |  |

| CS50               | TCOFSF | COFS Fall Time<br>(COFS pin is output)                                   | _                                                                                                                                                                      | 10                 | 25  | ns    | See Note 1 |  |

| CS51               | TCOFSR | COFS Rise Time<br>(COFS pin is output)                                   | _                                                                                                                                                                      | 10                 | 25  | ns    | See Note 1 |  |

| CS55               | TSCOFS | Setup Time of COFS Data Input to CSCK Edge (COFS pin is input)           | 20                                                                                                                                                                     | _                  |     | ns    | _          |  |

| CS56               | THCOFS | Hold Time of COFS Data Input to CSCK Edge (COFS pin is input)            | 20                                                                                                                                                                     | _                  | _   | ns    | _          |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

**<sup>2:</sup>** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**<sup>3:</sup>** The minimum clock period for CSCK is 100 ns. Therefore, the clock generated in Master mode must not violate this specification.

<sup>4:</sup> Assumes 50 pF load on all DCI pins.