Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | dsPIC                                                                           |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | AC'97, Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT             |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

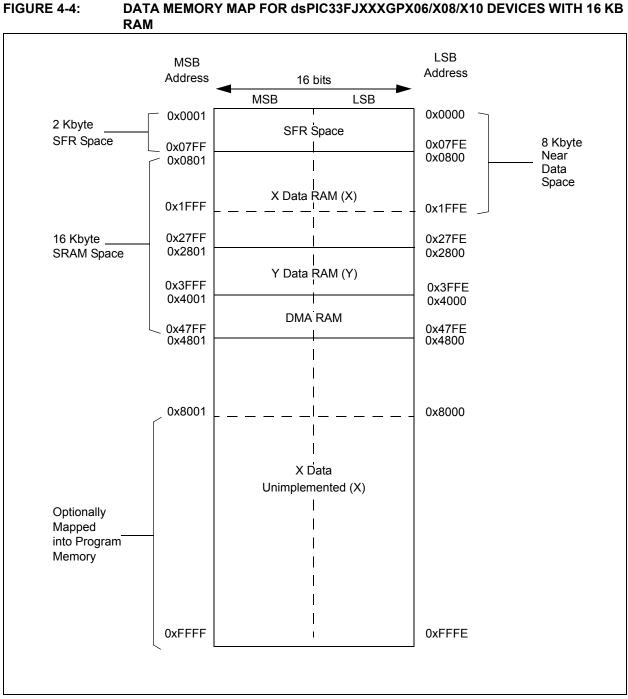

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 32x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/dspic33fj64gp710-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| U-0             | U-0                                                                                                                           | U-0                                     | R/W-0          | R/W-0               | R-0             | R-0              | R-0   |  |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|----------------|---------------------|-----------------|------------------|-------|--|--|--|--|

|                 |                                                                                                                               |                                         | US             | EDT <sup>(1)</sup>  |                 | DL<2:0>          |       |  |  |  |  |

| bit 15          |                                                                                                                               |                                         |                |                     |                 |                  | bit   |  |  |  |  |

| R/W-0           | R/W-0                                                                                                                         | R/W-1                                   | R/W-0          | R/C-0               | R/W-0           | R/W-0            | R/W-0 |  |  |  |  |

| SATA            | SATB                                                                                                                          | SATDW                                   | ACCSAT         | IPL3 <sup>(2)</sup> | PSV             | RND              | IF    |  |  |  |  |

| bit 7           |                                                                                                                               |                                         |                |                     | •               |                  | bit   |  |  |  |  |

| Legend:         |                                                                                                                               | C = Clear on                            | y bit          |                     |                 |                  |       |  |  |  |  |

| R = Readabl     | le bit                                                                                                                        | W = Writable                            | bit            | -n = Value at       | POR             | '1' = Bit is set |       |  |  |  |  |

| 0' = Bit is cle | eared                                                                                                                         | 'x = Bit is unk                         | nown           | U = Unimple         | mented bit, rea | d as '0'         |       |  |  |  |  |

| bit 15-13       | Unimplemen                                                                                                                    | ted: Read as '                          | 0'             |                     |                 |                  |       |  |  |  |  |

| bit 12          | US: DSP Mul                                                                                                                   | tiply Unsigned                          | /Signed Contro | ol bit              |                 |                  |       |  |  |  |  |

|                 | Ų                                                                                                                             | ne multiplies a                         | Ų              |                     |                 |                  |       |  |  |  |  |

| bit 11          | -                                                                                                                             | ne multiplies a                         | -              | .;+(1)              |                 |                  |       |  |  |  |  |

|                 | •                                                                                                                             |                                         |                | current loop it     | eration         |                  |       |  |  |  |  |

|                 | 0 = No effect                                                                                                                 | 0                                       | •              | ·                   |                 |                  |       |  |  |  |  |

| bit 10-8        |                                                                                                                               | Loop Nesting                            | Level Status b | its                 |                 |                  |       |  |  |  |  |

|                 | <pre>111 = 7 DO loops active .</pre>                                                                                          |                                         |                |                     |                 |                  |       |  |  |  |  |

|                 | •                                                                                                                             |                                         |                |                     |                 |                  |       |  |  |  |  |

|                 | 001 = 1 DO loop active                                                                                                        |                                         |                |                     |                 |                  |       |  |  |  |  |

| L:1 7           | 000 = 0  DO IO                                                                                                                | -                                       | hl- h:4        |                     |                 |                  |       |  |  |  |  |

| bit 7           | SATA: AccA Saturation Enable bit<br>1 = Accumulator A saturation enabled                                                      |                                         |                |                     |                 |                  |       |  |  |  |  |

|                 |                                                                                                                               | ator A saturatio                        |                |                     |                 |                  |       |  |  |  |  |

| bit 6           | SATB: AccB Saturation Enable bit                                                                                              |                                         |                |                     |                 |                  |       |  |  |  |  |

|                 | 1 = Accumulator B saturation enabled                                                                                          |                                         |                |                     |                 |                  |       |  |  |  |  |

| bit 5           | 0 = Accumulator B saturation disabled                                                                                         |                                         |                |                     |                 |                  |       |  |  |  |  |

| DIL D           | <b>SATDW:</b> Data Space Write from DSP Engine Saturation Enable bit<br>1 = Data space write saturation enabled               |                                         |                |                     |                 |                  |       |  |  |  |  |

|                 | <ul> <li>a Data space write saturation disabled</li> <li>b = Data space write saturation disabled</li> </ul>                  |                                         |                |                     |                 |                  |       |  |  |  |  |

| bit 4           | ACCSAT: Accumulator Saturation Mode Select bit                                                                                |                                         |                |                     |                 |                  |       |  |  |  |  |

|                 | 1 = 9.31 saturation (super saturation)                                                                                        |                                         |                |                     |                 |                  |       |  |  |  |  |

| 1.11.0          |                                                                                                                               | ration (normal                          |                |                     |                 |                  |       |  |  |  |  |

| bit 3           | <b>IPL3:</b> CPU Interrupt Priority Level Status bit 3 <sup>(2)</sup>                                                         |                                         |                |                     |                 |                  |       |  |  |  |  |

|                 | <ul> <li>1 = CPU interrupt priority level is greater than 7</li> <li>0 = CPU interrupt priority level is 7 or less</li> </ul> |                                         |                |                     |                 |                  |       |  |  |  |  |

| bit 2           |                                                                                                                               | n Space Visibil                         |                |                     |                 |                  |       |  |  |  |  |

|                 |                                                                                                                               | 1 = Program space visible in data space |                |                     |                 |                  |       |  |  |  |  |

|                 |                                                                                                                               | space not visib                         |                | ce                  |                 |                  |       |  |  |  |  |

| bit 1           |                                                                                                                               | ng Mode Sele                            |                | 1                   |                 |                  |       |  |  |  |  |

|                 | ,                                                                                                                             | onventional) ro<br>(convergent)         | U U            |                     |                 |                  |       |  |  |  |  |

| bit 0           |                                                                                                                               | Fractional Mul                          | -              |                     |                 |                  |       |  |  |  |  |

|                 |                                                                                                                               | ode enabled fo                          |                |                     |                 |                  |       |  |  |  |  |

|                 | 0 = Fractiona                                                                                                                 | l mode enable                           | d for DSP mul  | tinly one           |                 |                  |       |  |  |  |  |

### REGISTER 3-2: CORCON: CORE CONTROL REGISTER

**Note 1:** This bit will always read as '0'.

2: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU interrupt priority level.

### DATA MEMORY MAP FOR dsPIC33FJXXXGPX06/X08/X10 DEVICES WITH 16 KB

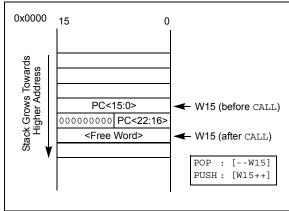

### 4.2.7 SOFTWARE STACK

In addition to its use as a working register, the W15 register in the dsPIC33FJXXXGPX06/X08/X10 devices is also used as a software Stack Pointer. The Stack Pointer always points to the first available free word and grows from lower to higher addresses. It pre-decrements for stack pops and post-increments for stack pushes, as shown in Figure 4-6. For a PC push during any CALL instruction, the MSb of the PC is zero-extended before the push, ensuring that the MSb is always clear.

| Note: | A PC push during exception processing    |  |  |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|--|--|

|       | concatenates the SRL register to the MSb |  |  |  |  |  |  |  |

|       | of the PC prior to the push.             |  |  |  |  |  |  |  |

The Stack Pointer Limit register (SPLIM) associated with the Stack Pointer sets an upper address boundary for the stack. SPLIM is uninitialized at Reset. As is the case for the Stack Pointer, SPLIM<0> is forced to '0' because all stack operations must be word-aligned. Whenever an EA is generated using W15 as a source or destination pointer, the resulting address is compared with the value in SPLIM. If the contents of the Stack Pointer (W15) and the SPLIM register are equal and a push operation is performed, a stack error trap will not occur. The stack error trap will occur on a subsequent push operation. Thus, for example, if it is desirable to cause a stack error trap when the stack grows beyond address 0x2000 in RAM, initialize the SPLIM with the value 0x1FFE.

Similarly, a Stack Pointer underflow (stack error) trap is generated when the Stack Pointer address is found to be less than 0x0800. This prevents the stack from interfering with the Special Function Register (SFR) space.

A write to the SPLIM register should not be immediately followed by an indirect read operation using W15.

#### FIGURE 4-6: CALL STACK FRAME

### 4.2.8 DATA RAM PROTECTION FEATURE

The dsPIC33F product family supports Data RAM protection features which enable segments of RAM to be protected when used in conjunction with Boot and Secure Code Segment Security. BSRAM (Secure RAM segment for BS) is accessible only from the Boot Segment Flash code when enabled. SSRAM (Secure RAM segment for RAM) is accessible only from the Secure Segment Flash code when enabled. See Table 4-1 for an overview of the BSRAM and SSRAM SFRs.

### 4.3 Instruction Addressing Modes

The addressing modes in Table 4-35 form the basis of the addressing modes optimized to support the specific features of individual instructions. The addressing modes provided in the MAC class of instructions are somewhat different from those in the other instruction types.

#### 4.3.1 FILE REGISTER INSTRUCTIONS

Most file register instructions use a 13-bit address field (f) to directly address data present in the first 8192 bytes of data memory (Near Data Space). Most file register instructions employ a working register, W0, which is denoted as WREG in these instructions. The destination is typically either the same file register or WREG (with the exception of the MUL instruction), which writes the result to a register or register pair. The MOV instruction allows additional flexibility and can access the entire data space.

### 4.3.2 MCU INSTRUCTIONS

The 3-operand MCU instructions are of the form:

Operand 3 = Operand 1 < function> Operand 2

where Operand 1 is always a working register (i.e., the addressing mode can only be register direct) which is referred to as Wb. Operand 2 can be a W register, fetched from data memory, or a 5-bit literal. The result location can be either a W register or a data memory location. The following addressing modes are supported by MCU instructions:

- Register Direct

- · Register Indirect

- · Register Indirect Post-Modified

- · Register Indirect Pre-Modified

- 5-bit or 10-bit Literal

Note: Not all instructions support all the addressing modes given above. Individual instructions may support different subsets of these addressing modes.

#### 4.4.3 MODULO ADDRESSING APPLICABILITY

Modulo Addressing can be applied to the Effective Address (EA) calculation associated with any W register. It is important to realize that the address boundaries check for addresses less than, or greater than, the upper (for incrementing buffers) and lower (for decrementing buffers) boundary addresses (not just equal to). Address changes may, therefore, jump beyond boundaries and still be adjusted correctly.

Note: The modulo corrected effective address is written back to the register only when Pre-Modify or Post-Modify Addressing mode is used to compute the effective address. When an address offset (e.g., [W7+W2]) is used, Modulo Address correction is performed but the contents of the register remain unchanged.

### 4.5 Bit-Reversed Addressing

Bit-Reversed Addressing mode is intended to simplify data re-ordering for radix-2 FFT algorithms. It is supported by the X AGU for data writes only.

The modifier, which may be a constant value or register contents, is regarded as having its bit order reversed. The address source and destination are kept in normal order. Thus, the only operand requiring reversal is the modifier.

### 4.5.1 BIT-REVERSED ADDRESSING IMPLEMENTATION

Bit-Reversed Addressing mode is enabled when:

- BWM bits (W register selection) in the MODCON register are any value other than '15' (the stack cannot be accessed using Bit-Reversed Addressing).

- 2. The BREN bit is set in the XBREV register.

- 3. The addressing mode used is Register Indirect with Pre-Increment or Post-Increment.

If the length of a bit-reversed buffer is  $M = 2^N$  bytes, the last 'N' bits of the data buffer start address must be zeros.

XB<14:0> is the Bit-Reversed Address modifier, or 'pivot point', which is typically a constant. In the case of an FFT computation, its value is equal to half of the FFT data buffer size.

| Note: | All bit-reversed EA calculations assume   |

|-------|-------------------------------------------|

|       | word sized data (LSb of every EA is       |

|       | always clear). The XB value is scaled     |

|       | accordingly to generate compatible (byte) |

|       | addresses.                                |

When enabled, Bit-Reversed Addressing is only executed for Register Indirect with Pre-Increment or Post-Increment Addressing and word sized data writes. It will not function for any other addressing mode or for byte sized data and normal addresses are generated instead. When Bit-Reversed Addressing is active, the W Address Pointer is always added to the address modifier (XB) and the offset associated with the Register Indirect Addressing mode is ignored. In addition, as word sized data is a requirement, the LSb of the EA is ignored (and always clear).

| Note: | Modulo Addressing and Bit-Reversed            |  |  |  |  |  |  |  |  |

|-------|-----------------------------------------------|--|--|--|--|--|--|--|--|

|       | Addressing should not be enabled              |  |  |  |  |  |  |  |  |

|       | together. In the event that the user attempts |  |  |  |  |  |  |  |  |

|       | to do so, Bit-Reversed Addressing will        |  |  |  |  |  |  |  |  |

|       | assume priority when active for the X         |  |  |  |  |  |  |  |  |

|       | WAGU and X WAGU Modulo Addressing             |  |  |  |  |  |  |  |  |

|       | will be disabled. However, Modulo             |  |  |  |  |  |  |  |  |

|       | Addressing will continue to function in the X |  |  |  |  |  |  |  |  |

|       | RAGU.                                         |  |  |  |  |  |  |  |  |

If Bit-Reversed Addressing has already been enabled by setting the BREN (XBREV<15>) bit, then a write to the XBREV register should not be immediately followed by an indirect read operation using the W register that has been designated as the bit-reversed pointer.

### REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1 (CONTINUED)

- bit 3 CNIF: Input Change Notification Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 2 Unimplemented: Read as '0'

- bit 1 MI2C1IF: I2C1 Master Events Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 SI2C1IF: I2C1 Slave Events Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

| 11.0          |                                                                                                                    |             |                |       |               |      |                            |               |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------------|-------------|----------------|-------|---------------|------|----------------------------|---------------|--|--|

| U-0           | R/W-0 R/W-0                                                                                                        | R/W-0       | R/W-0          |       | R/W-0         |      | R/W-0                      | R/W-0         |  |  |

| <br>bit 15    | DMA1IE AD1IE                                                                                                       | U1TXIE      | U1RXIE         |       | SPI1IE        |      | SPI1EIE                    | T3IE<br>bit 8 |  |  |

|               |                                                                                                                    |             |                |       |               |      |                            | DILC          |  |  |

| R/W-0         | R/W-0 R/W-0                                                                                                        | R/W-0       | R/W-0          |       | R/W-0         |      | R/W-0                      | R/W-0         |  |  |

| T2IE          | - 1                                                                                                                | DMA0IE      | T1IE           |       | OC1IE         |      | IC1IE                      | INT0IE        |  |  |

| bit 7         |                                                                                                                    |             |                |       |               |      |                            | bit (         |  |  |

| Legend:       |                                                                                                                    |             |                |       |               |      |                            |               |  |  |

| R = Readable  | e bit W = Writable bit                                                                                             |             | U = Unimple    | emer  | nted bit, rea | ad a | is '0'                     |               |  |  |

| -n = Value at | POR '1' = Bit is set                                                                                               |             | '0' = Bit is c | leare | ed            | >    | <pre>c = Bit is unkn</pre> | own           |  |  |

| L:4 / F       | Unimplemented: Deed op (o)                                                                                         |             |                |       |               |      |                            |               |  |  |

| bit 15        | Unimplemented: Read as '0'                                                                                         | Transform   |                |       | En abla bii   |      |                            |               |  |  |

| bit 14        | <b>DMA1IE:</b> DMA Channel 1 Data<br>1 = Interrupt request enabled                                                 | Transfer C  | omplete inte   | rrupt | Enable bit    |      |                            |               |  |  |

|               | 0 = Interrupt request not enable                                                                                   | ed          |                |       |               |      |                            |               |  |  |

| bit 13        | AD1IE: ADC1 Conversion Com                                                                                         |             | upt Enable b   | it    |               |      |                            |               |  |  |

|               | 1 = Interrupt request enabled                                                                                      |             |                |       |               |      |                            |               |  |  |

|               | 0 = Interrupt request not enabled                                                                                  |             |                |       |               |      |                            |               |  |  |

| bit 12        | U1TXIE: UART1 Transmitter In                                                                                       | terrupt Ena | ble bit        |       |               |      |                            |               |  |  |

|               | <ul><li>1 = Interrupt request enabled</li><li>0 = Interrupt request not enable</li></ul>                           | )d          |                |       |               |      |                            |               |  |  |

| bit 11        | <b>U1RXIE:</b> UART1 Receiver Inter                                                                                | rupt Enable | e bit          |       |               |      |                            |               |  |  |

|               | <ol> <li>Interrupt request enabled</li> <li>Interrupt request not enabled</li> </ol>                               |             |                |       |               |      |                            |               |  |  |

| bit 10        | SPI1IE: SPI1 Event Interrupt E                                                                                     |             |                |       |               |      |                            |               |  |  |

|               | 1 = Interrupt request enabled                                                                                      |             |                |       |               |      |                            |               |  |  |

|               | 0 = Interrupt request not enable                                                                                   | ed          |                |       |               |      |                            |               |  |  |

| bit 9         | SPI1EIE: SPI1 Error Interrupt Enable bit                                                                           |             |                |       |               |      |                            |               |  |  |

|               | 1 = Interrupt request enabled                                                                                      |             |                |       |               |      |                            |               |  |  |

|               | 0 = Interrupt request not enable                                                                                   |             |                |       |               |      |                            |               |  |  |

| bit 8         | T3IE: Timer3 Interrupt Enable bit                                                                                  |             |                |       |               |      |                            |               |  |  |

|               | <ol> <li>I = Interrupt request enabled</li> <li>Interrupt request not enabled</li> </ol>                           |             |                |       |               |      |                            |               |  |  |

| bit 7         | T2IE: Timer2 Interrupt Enable bit                                                                                  |             |                |       |               |      |                            |               |  |  |

|               | 1 = Interrupt request enabled                                                                                      |             |                |       |               |      |                            |               |  |  |

|               | 0 = Interrupt request not enable                                                                                   |             |                |       |               |      |                            |               |  |  |

| bit 6         | OC2IE: Output Compare Channel 2 Interrupt Enable bit                                                               |             |                |       |               |      |                            |               |  |  |

|               | 1 = Interrupt request enabled                                                                                      |             |                |       |               |      |                            |               |  |  |

| bit 5         | <ul> <li>o = Interrupt request not enabled</li> <li>IC2IE: Input Capture Channel 2 Interrupt Enable bit</li> </ul> |             |                |       |               |      |                            |               |  |  |

|               | 1 = Interrupt request enabled                                                                                      |             |                |       |               |      |                            |               |  |  |

|               | 0 = Interrupt request not enable                                                                                   | ed .        |                |       |               |      |                            |               |  |  |

| bit 4         | DMA0IE: DMA Channel 0 Data                                                                                         | Transfer C  | omplete Inte   | rrupt | Enable bit    |      |                            |               |  |  |

|               | <ul> <li>1 = Interrupt request enabled</li> <li>0 = Interrupt request not enable</li> </ul>                        | ed          |                |       |               |      |                            |               |  |  |

|               |                                                                                                                    |             |                |       |               |      |                            |               |  |  |

| bit 3         | T1IE: Timer1 Interrupt Enable b                                                                                    |             |                |       |               |      |                            |               |  |  |

| U-0          | R/W-1                                                                          | R/W-0                                                                 | R/W-0          | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |

|--------------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------|----------------|------------------|-----------------|-----------------|-------|--|--|--|--|

| _            |                                                                                | T8IP<2:0>                                                             |                | _                |                 | MI2C2IP<2:0>    |       |  |  |  |  |

| bit 15       | ·                                                                              |                                                                       |                | ·                |                 |                 | bit   |  |  |  |  |

|              |                                                                                |                                                                       |                |                  |                 |                 |       |  |  |  |  |

| U-0          | R/W-1                                                                          | R/W-0                                                                 | R/W-0          | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |

|              |                                                                                | SI2C2IP<2:0>                                                          |                |                  |                 | T7IP<2:0>       |       |  |  |  |  |

| bit 7        |                                                                                |                                                                       |                |                  |                 |                 | bit   |  |  |  |  |

| Legend:      |                                                                                |                                                                       |                |                  |                 |                 |       |  |  |  |  |

| R = Readab   | le bit                                                                         | W = Writable I                                                        | oit            | U = Unimple      | mented bit, rea | ad as '0'       |       |  |  |  |  |

| -n = Value a | t POR                                                                          | '1' = Bit is set                                                      |                | '0' = Bit is cle | eared           | x = Bit is unkn | own   |  |  |  |  |

|              |                                                                                |                                                                       |                |                  |                 |                 |       |  |  |  |  |

| bit 15       | Unimplem                                                                       | ented: Read as 'o                                                     | )'             |                  |                 |                 |       |  |  |  |  |

| bit 14-12    |                                                                                | : Timer8 Interrupt                                                    | 5              |                  |                 |                 |       |  |  |  |  |

|              | 111 = Inte                                                                     | <pre>111 = Interrupt is priority 7 (highest priority interrupt)</pre> |                |                  |                 |                 |       |  |  |  |  |

|              | •                                                                              |                                                                       |                |                  |                 |                 |       |  |  |  |  |

|              | •                                                                              |                                                                       |                |                  |                 |                 |       |  |  |  |  |

|              |                                                                                | 001 = Interrupt is priority 1                                         |                |                  |                 |                 |       |  |  |  |  |

|              |                                                                                | rrupt source is disa                                                  |                |                  |                 |                 |       |  |  |  |  |

| bit 11       | -                                                                              | Unimplemented: Read as '0'                                            |                |                  |                 |                 |       |  |  |  |  |

| bit 10-8     | MI2C2IP<2:0>: I2C2 Master Events Interrupt Priority bits                       |                                                                       |                |                  |                 |                 |       |  |  |  |  |

|              | 111 = Inte                                                                     | rrupt is priority 7 (I                                                | nighest priori | ity interrupt)   |                 |                 |       |  |  |  |  |

|              | •                                                                              |                                                                       |                |                  |                 |                 |       |  |  |  |  |

|              | •                                                                              |                                                                       |                |                  |                 |                 |       |  |  |  |  |

|              |                                                                                | rrupt is priority 1                                                   |                |                  |                 |                 |       |  |  |  |  |

|              |                                                                                | rrupt source is disa                                                  |                |                  |                 |                 |       |  |  |  |  |

| bit 7        | -                                                                              | ented: Read as 'o                                                     |                |                  |                 |                 |       |  |  |  |  |

| bit 6-4      | SI2C2IP<2:0>: I2C2 Slave Events Interrupt Priority bits                        |                                                                       |                |                  |                 |                 |       |  |  |  |  |

|              | <ul> <li>111 = Interrupt is priority 7 (highest priority interrupt)</li> </ul> |                                                                       |                |                  |                 |                 |       |  |  |  |  |

|              | •                                                                              |                                                                       |                |                  |                 |                 |       |  |  |  |  |

|              | •                                                                              |                                                                       |                |                  |                 |                 |       |  |  |  |  |

|              |                                                                                | rrupt is priority 1                                                   |                |                  |                 |                 |       |  |  |  |  |

| L:1 0        |                                                                                | rrupt source is disa                                                  |                |                  |                 |                 |       |  |  |  |  |

| bit 3        | -                                                                              | ented: Read as 'o                                                     |                |                  |                 |                 |       |  |  |  |  |

| bit 2-0      |                                                                                | : Timer7 Interrupt                                                    |                | ity interrent)   |                 |                 |       |  |  |  |  |

|              | ⊥⊥⊥ = inte<br>•                                                                | rrupt is priority 7 (ł                                                | lignest prior  | ity interrupt)   |                 |                 |       |  |  |  |  |

|              | •                                                                              |                                                                       |                |                  |                 |                 |       |  |  |  |  |

|              | •                                                                              |                                                                       |                |                  |                 |                 |       |  |  |  |  |

|              |                                                                                | rrupt is priority 1                                                   | ablad          |                  |                 |                 |       |  |  |  |  |

|              | 000 = Inte                                                                     | rrupt source is disa                                                  | abled          |                  |                 |                 |       |  |  |  |  |

| REGISTER 9-                       | -3: PLLF                                          | BD: PLL FEE | DBACK DI           | VISOR REGIS                        | TER   |       |                      |  |

|-----------------------------------|---------------------------------------------------|-------------|--------------------|------------------------------------|-------|-------|----------------------|--|

| U-0                               | U-0                                               | U-0         | U-0                | U-0                                | U-0   | U-0   | R/W-0 <sup>(1)</sup> |  |

|                                   | _                                                 | —           | _                  | —                                  | _     | —     | PLLDIV<8>            |  |

| bit 15                            |                                                   |             |                    |                                    |       |       | bit 8                |  |

| R/W-0                             | R/W-0                                             | R/W-1       | R/W-1              | R/W-0                              | R/W-0 | R/W-0 | R/W-0                |  |

|                                   |                                                   |             | PLLE               | )IV<7:0>                           |       |       |                      |  |

| bit 7                             |                                                   |             |                    |                                    |       |       | bit 0                |  |

| Legend:                           |                                                   |             |                    |                                    |       |       |                      |  |

| R = Readable bit W = Writable bit |                                                   |             | bit                | U = Unimplemented bit, read as '0' |       |       |                      |  |

| -n = Value at P                   | alue at POR '1' = Bit is set '0' = Bit is cleared |             | x = Bit is unknown |                                    |       |       |                      |  |

bit 15-9 Unimplemented: Read as '0'

bit 8-0 PLLDIV<8:0>: PLL Feedback Divisor bits (also denoted as 'M', PLL multiplier)

```

000000000 = 2

00000001 = 3

000000010 = 4

.

.

000110000 = 50 (default)

.

.

11111111 = 513

```

NOTES:

| REGISTER 1                                                           | 6-3: SPIxC                                                                                    | ON2: SPIx C                         | ONTROL R       | EGISTER 2         |                 |                  |       |  |  |  |

|----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|-------------------------------------|----------------|-------------------|-----------------|------------------|-------|--|--|--|

| R/W-0                                                                | R/W-0                                                                                         | R/W-0                               | U-0            | U-0               | U-0             | U-0              | U-0   |  |  |  |

| FRMEN                                                                | SPIFSD                                                                                        | FRMPOL                              | _              | —                 | _               | _                | _     |  |  |  |

| bit 15                                                               |                                                                                               |                                     |                |                   |                 |                  | bit 8 |  |  |  |

|                                                                      |                                                                                               |                                     |                |                   |                 |                  |       |  |  |  |

| U-0                                                                  | U-0                                                                                           | U-0                                 | U-0            | U-0               | U-0             | R/W-0            | U-0   |  |  |  |

| —                                                                    | —                                                                                             | —                                   |                | —                 |                 | FRMDLY           |       |  |  |  |

| bit 7                                                                |                                                                                               |                                     |                |                   |                 |                  | bit 0 |  |  |  |

| Legend:                                                              |                                                                                               |                                     |                |                   |                 |                  |       |  |  |  |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |                                                                                               |                                     |                |                   |                 |                  |       |  |  |  |

| -n = Value at                                                        |                                                                                               | '1' = Bit is set                    |                | '0' = Bit is cle  |                 | x = Bit is unkno | wn    |  |  |  |

|                                                                      |                                                                                               |                                     |                |                   |                 |                  |       |  |  |  |

| bit 15                                                               | FRMEN: Framed SPIx Support bit                                                                |                                     |                |                   |                 |                  |       |  |  |  |

|                                                                      | 1 = Framed SPIx support enabled ( $\overline{SSx}$ pin used as frame sync pulse input/output) |                                     |                |                   |                 |                  |       |  |  |  |

|                                                                      | 0 = Framed S                                                                                  | SPIx support dis                    | sabled         |                   |                 |                  |       |  |  |  |

| bit 14                                                               | SPIFSD: Fran                                                                                  | me Sync Pulse                       | Direction Co   | ntrol bit         |                 |                  |       |  |  |  |

|                                                                      |                                                                                               | nc pulse input (<br>nc pulse output | · /            |                   |                 |                  |       |  |  |  |

| bit 13                                                               | FRMPOL: Fra                                                                                   | ame Sync Puls                       | e Polarity bit |                   |                 |                  |       |  |  |  |

|                                                                      | 1 = Frame sync pulse is active-high                                                           |                                     |                |                   |                 |                  |       |  |  |  |

|                                                                      | 0 = Frame sync pulse is active-low                                                            |                                     |                |                   |                 |                  |       |  |  |  |

| bit 12-2                                                             | Unimplemen                                                                                    | ted: Read as '                      | 0'             |                   |                 |                  |       |  |  |  |

| bit 1                                                                | FRMDLY: Fra                                                                                   | ame Sync Pulse                      | e Edge Selec   | t bit             |                 |                  |       |  |  |  |

|                                                                      | 1 = Frame sy                                                                                  | nc pulse coinci                     | des with first | bit clock         |                 |                  |       |  |  |  |

|                                                                      |                                                                                               | nc pulse prece                      |                |                   |                 |                  |       |  |  |  |

| bit 0                                                                | Unimplemen                                                                                    | ted: This bit m                     | ust not be se  | t to '1' by the u | ser application |                  |       |  |  |  |

|                                                                      |                                                                                               |                                     |                |                   |                 |                  |       |  |  |  |

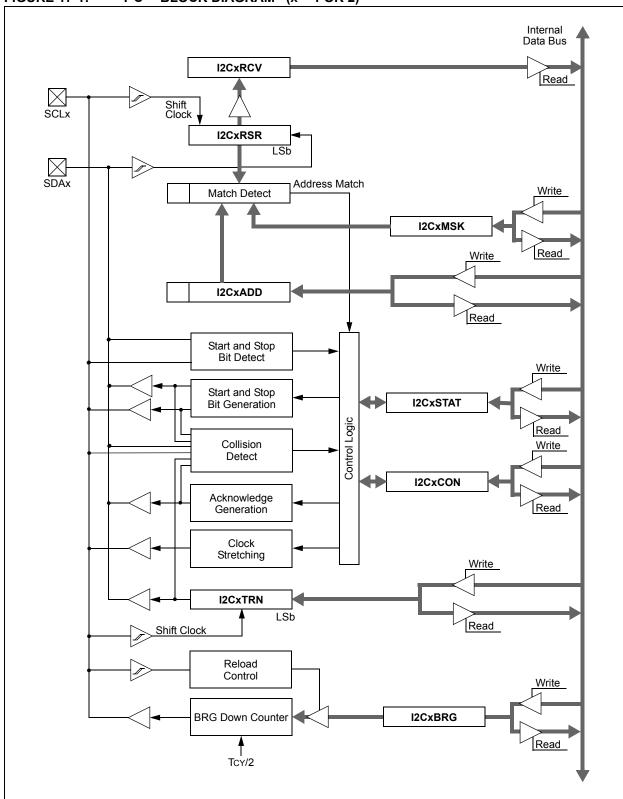

FIGURE 17-1:  $I^2C^{TM}$  BLOCK DIAGRAM (x = 1 OR 2)

REGISTER 18-1: UXMODE: UARTX MODE REGISTER

| W = Writ<br>'1' = Bit i<br><b>TEN:</b> UARTx Enal<br>ARTx is enabled;<br>ARTx is disabled<br>inimal<br><b>plemented:</b> Read<br>L: Stop in Idle Mo<br>iscontinue module of<br>intimue module of<br>IrDA <sup>®</sup> Encoder and<br>DA <sup>®</sup> encoder and<br>DA <sup>®</sup> encoder and | HC R/W-0<br>JD URXINV<br>ardware cleared<br>table bit<br>is set<br>ble bit <sup>(1)</sup><br>; all UARTx pins a<br>; all UARTx pins a<br>d as '0'<br>de bit<br>le operation when<br>operation in Idle m<br>and Decoder Enated<br>d decoder enabled | '0' = Bit is cl<br>are controlled b<br>are controlled b<br>device enters<br>hode<br>ble bit <sup>(2)</sup>                                                                                                                                              | y UARTx as defi<br>y port latches; U                                                                                                                                                                                                | R/W-0<br>L<1:0><br>I as '0'<br>x = Bit is unkr<br>ned by UEN<1:                                                                                                                                                                                                                                                | :0>                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| HC = Ha<br>W = Writ<br>'1' = Bit i<br>'EN: UARTx Enal<br>ARTx is enabled;<br>ARTx is disabled<br>inimal<br>plemented: Read<br>.: Stop in Idle Mo<br>iscontinue modul<br>continue module o<br>IrDA <sup>®</sup> Encoder and<br>DA <sup>®</sup> encoder and                                       | JD URXINV<br>ardware cleared<br>table bit<br>is set<br>ble bit <sup>(1)</sup><br>; all UARTx pins a<br>; all UARTx pins a<br>d as '0'<br>de bit<br>le operation when<br>operation in Idle m<br>and Decoder Enat                                    | BRGH<br>U = Unimple<br>'0' = Bit is cl<br>are controlled b<br>are controlled b<br>device enters<br>tode<br>ble bit <sup>(2)</sup>                                                                                                                       | PDSEI<br>emented bit, reac<br>eared<br>y UARTx as defi<br>y port latches; U                                                                                                                                                         | L<1:0><br>I as '0'<br>x = Bit is unkr<br>ned by UEN<1:                                                                                                                                                                                                                                                         | R/W-0<br>STSEL<br>bit (                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| HC = Ha<br>W = Writ<br>'1' = Bit i<br>'EN: UARTx Enal<br>ARTx is enabled;<br>ARTx is disabled<br>inimal<br>plemented: Read<br>.: Stop in Idle Mo<br>iscontinue modul<br>continue module o<br>IrDA <sup>®</sup> Encoder and<br>DA <sup>®</sup> encoder and                                       | JD URXINV<br>ardware cleared<br>table bit<br>is set<br>ble bit <sup>(1)</sup><br>; all UARTx pins a<br>; all UARTx pins a<br>d as '0'<br>de bit<br>le operation when<br>operation in Idle m<br>and Decoder Enat                                    | BRGH<br>U = Unimple<br>'0' = Bit is cl<br>are controlled b<br>are controlled b<br>device enters<br>tode<br>ble bit <sup>(2)</sup>                                                                                                                       | PDSEI<br>emented bit, reac<br>eared<br>y UARTx as defi<br>y port latches; U                                                                                                                                                         | L<1:0><br>I as '0'<br>x = Bit is unkr<br>ned by UEN<1:                                                                                                                                                                                                                                                         | STSEL<br>bit (<br>nown                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| HC = Ha<br>W = Writ<br>'1' = Bit i<br>'EN: UARTx Enal<br>ARTx is enabled;<br>ARTx is disabled<br>inimal<br>plemented: Read<br>.: Stop in Idle Mo<br>iscontinue modul<br>continue module o<br>IrDA <sup>®</sup> Encoder and<br>DA <sup>®</sup> encoder and                                       | JD URXINV<br>ardware cleared<br>table bit<br>is set<br>ble bit <sup>(1)</sup><br>; all UARTx pins a<br>; all UARTx pins a<br>d as '0'<br>de bit<br>le operation when<br>operation in Idle m<br>and Decoder Enat                                    | BRGH<br>U = Unimple<br>'0' = Bit is cl<br>are controlled b<br>are controlled b<br>device enters<br>tode<br>ble bit <sup>(2)</sup>                                                                                                                       | PDSEI<br>emented bit, reac<br>eared<br>y UARTx as defi<br>y port latches; U                                                                                                                                                         | L<1:0><br>I as '0'<br>x = Bit is unkr<br>ned by UEN<1:                                                                                                                                                                                                                                                         | STSEL<br>bit (<br>nown                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| HC = Ha<br>W = Writ<br>'1' = Bit i<br>'EN: UARTx Enat<br>ARTx is enabled;<br>ARTx is disabled<br>inimal<br>plemented: Read<br>L: Stop in Idle Mo<br>iscontinue module o<br>iscontinue module o<br>IrDA <sup>®</sup> Encoder an<br>DA <sup>®</sup> encoder and                                   | ardware cleared<br>table bit<br>is set<br>ble bit <sup>(1)</sup><br>; all UARTx pins a<br>; all UARTx pins a<br>d as '0'<br>de bit<br>le operation when<br>operation in Idle m<br>and Decoder Enat                                                 | U = Unimple<br>'0' = Bit is cl<br>are controlled b<br>are controlled b<br>device enters<br>tode<br>ble bit <sup>(2)</sup>                                                                                                                               | emented bit, reac<br>eared<br>y UARTx as defi<br>y port latches; U                                                                                                                                                                  | l as '0'<br>x = Bit is unkr<br>ned by UEN<1:                                                                                                                                                                                                                                                                   | bit (<br>nown<br>:0>                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| W = Writ<br>'1' = Bit i<br><b>TEN:</b> UARTx Enal<br>ARTx is enabled;<br>ARTx is disabled<br>inimal<br><b>plemented:</b> Read<br>L: Stop in Idle Mo<br>iscontinue module of<br>intimue module of<br>IrDA <sup>®</sup> Encoder and<br>DA <sup>®</sup> encoder and<br>DA <sup>®</sup> encoder and | table bit<br>is set<br>ble bit <sup>(1)</sup><br>; all UARTx pins a<br>; all UARTx pins a<br>d as '0'<br>de bit<br>le operation when<br>operation in Idle m<br>and Decoder Enat                                                                    | '0' = Bit is cl<br>are controlled b<br>are controlled b<br>device enters<br>hode<br>ble bit <sup>(2)</sup>                                                                                                                                              | eared<br>y UARTx as defi<br>y port latches; U                                                                                                                                                                                       | x = Bit is unkr<br>ned by UEN<1:                                                                                                                                                                                                                                                                               | nown<br>:0>                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| W = Writ<br>'1' = Bit i<br><b>TEN:</b> UARTx Enal<br>ARTx is enabled;<br>ARTx is disabled<br>inimal<br><b>plemented:</b> Read<br>L: Stop in Idle Mo<br>iscontinue module of<br>intimue module of<br>IrDA <sup>®</sup> Encoder and<br>DA <sup>®</sup> encoder and<br>DA <sup>®</sup> encoder and | table bit<br>is set<br>ble bit <sup>(1)</sup><br>; all UARTx pins a<br>; all UARTx pins a<br>d as '0'<br>de bit<br>le operation when<br>operation in Idle m<br>and Decoder Enat                                                                    | '0' = Bit is cl<br>are controlled b<br>are controlled b<br>device enters<br>hode<br>ble bit <sup>(2)</sup>                                                                                                                                              | eared<br>y UARTx as defi<br>y port latches; U                                                                                                                                                                                       | x = Bit is unkr<br>ned by UEN<1:                                                                                                                                                                                                                                                                               | :0>                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| W = Writ<br>'1' = Bit i<br><b>TEN:</b> UARTx Enal<br>ARTx is enabled;<br>ARTx is disabled<br>inimal<br><b>plemented:</b> Read<br>L: Stop in Idle Mo<br>iscontinue module of<br>intimue module of<br>IrDA <sup>®</sup> Encoder and<br>DA <sup>®</sup> encoder and<br>DA <sup>®</sup> encoder and | table bit<br>is set<br>ble bit <sup>(1)</sup><br>; all UARTx pins a<br>; all UARTx pins a<br>d as '0'<br>de bit<br>le operation when<br>operation in Idle m<br>and Decoder Enat                                                                    | '0' = Bit is cl<br>are controlled b<br>are controlled b<br>device enters<br>hode<br>ble bit <sup>(2)</sup>                                                                                                                                              | eared<br>y UARTx as defi<br>y port latches; U                                                                                                                                                                                       | x = Bit is unkr<br>ned by UEN<1:                                                                                                                                                                                                                                                                               | :0>                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| '1' = Bit i<br><b>TEN:</b> UARTx Enal<br>ARTx is enabled;<br>ARTx is disabled<br>inimal<br><b>plemented:</b> Read<br><b>.:</b> Stop in Idle Mo<br>iscontinue module of<br>iscontinue module of<br>IrDA <sup>®</sup> Encoder and<br>DA <sup>®</sup> encoder and<br>DA <sup>®</sup> encoder and   | is set<br>ble bit <sup>(1)</sup><br>; all UARTx pins a<br>; all UARTx pins a<br>d as '0'<br>de bit<br>le operation when<br>operation in Idle m<br>and Decoder Enate<br>d decoder enabled                                                           | '0' = Bit is cl<br>are controlled b<br>are controlled b<br>device enters<br>hode<br>ble bit <sup>(2)</sup>                                                                                                                                              | eared<br>y UARTx as defi<br>y port latches; U                                                                                                                                                                                       | x = Bit is unkr<br>ned by UEN<1:                                                                                                                                                                                                                                                                               | :0>                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| <b>EN:</b> UARTx Enal<br>ARTx is enabled;<br>ARTx is disabled<br>inimal<br><b>plemented:</b> Read<br>.: Stop in Idle Mo<br>iscontinue module o<br>fontinue module o<br>IrDA <sup>®</sup> Encoder and<br>DA <sup>®</sup> encoder and                                                             | ble bit <sup>(1)</sup><br>; all UARTx pins a<br>; all UARTx pins a<br>d as '0'<br>de bit<br>e operation when<br>operation in Idle m<br>and Decoder Enat                                                                                            | are controlled b<br>are controlled b<br>device enters<br>lode<br>ble bit <sup>(2)</sup>                                                                                                                                                                 | y UARTx as defi<br>y port latches; U                                                                                                                                                                                                | ned by UEN<1:                                                                                                                                                                                                                                                                                                  | :0>                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| ARTx is enabled;<br>ARTx is disabled<br>inimal<br>plemented: Read<br>L: Stop in Idle Mo<br>iscontinue module of<br>ontinue module of<br>IrDA <sup>®</sup> Encoder and<br>DA <sup>®</sup> encoder and                                                                                            | ; all UARTx pins a<br>; all UARTx pins a<br>d as '0'<br>de bit<br>le operation when<br>operation in Idle m<br>and Decoder Enat<br>d decoder enabled                                                                                                | are controlled b<br>device enters<br>lode<br>ole bit <sup>(2)</sup>                                                                                                                                                                                     | y port latches; U                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| ARTx is enabled;<br>ARTx is disabled<br>inimal<br>plemented: Read<br>L: Stop in Idle Mo<br>iscontinue module of<br>ontinue module of<br>IrDA <sup>®</sup> Encoder and<br>DA <sup>®</sup> encoder and                                                                                            | ; all UARTx pins a<br>; all UARTx pins a<br>d as '0'<br>de bit<br>le operation when<br>operation in Idle m<br>and Decoder Enat<br>d decoder enabled                                                                                                | are controlled b<br>device enters<br>lode<br>ole bit <sup>(2)</sup>                                                                                                                                                                                     | y port latches; U                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| ARTx is disabled<br>ninimal<br>plemented: Read<br>.: Stop in Idle Mo<br>iscontinue modul<br>continue module o<br>IrDA <sup>®</sup> Encoder and<br>DA <sup>®</sup> encoder and                                                                                                                   | ; all UARTx pins a<br>d as '0'<br>de bit<br>e operation when<br>operation in Idle m<br>and Decoder Enat                                                                                                                                            | are controlled b<br>device enters<br>lode<br>ole bit <sup>(2)</sup>                                                                                                                                                                                     | y port latches; U                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                           |  |  |  |  |