#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Betuns                             |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Active                                                                                                              |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 1 Core, 32-Bit                                                                                                      |

| Speed                              | 800MHz                                                                                                              |

| Co-Processors/DSP                  | Multimedia; NEON™ SIMD                                                                                              |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | -                                                                                                                   |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | -40°C ~ 125°C (TJ)                                                                                                  |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-LFBGA                                                                                                           |

| Supplier Device Package            | 624-MAPBGA (21x21)                                                                                                  |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6s4avm08adr                                            |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Architectural Overview

# 2 Architectural Overview

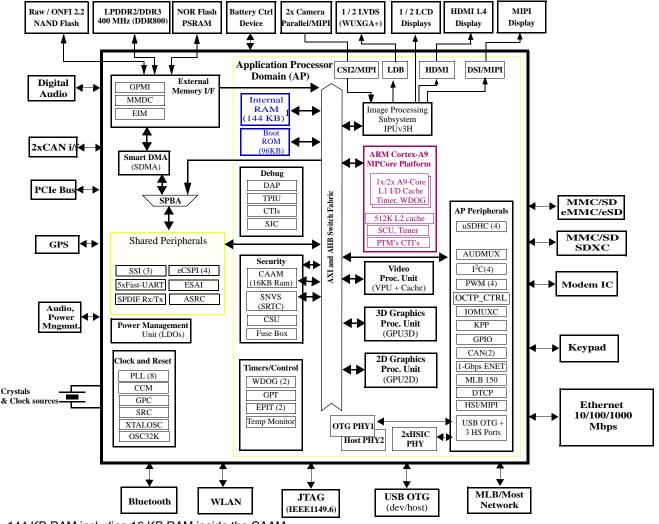

The following subsections provide an architectural overview of the i.MX 6Solo/6DualLite processor system.

### 2.1 Block Diagram

Figure 3 shows the functional modules in the i.MX 6Solo/6DualLite processor system.

<sup>1</sup> 144 KB RAM including 16 KB RAM inside the CAAM.

<sup>2</sup> For i.MX 6Solo, there is only one A9-core platform in the chip; for i.MX 6DualLite, there are two A9-core platforms.

#### Figure 3. i.MX 6Solo/6DualLite System Block Diagram

#### NOTE

The numbers in brackets indicate number of module instances. For example, PWM (4) indicates four separate PWM peripherals.

#### **Modules List**

| Block Mnemonic                            | Block Name                           | Subsystem                     | Brief Description                                                                                                                                                                                                                                                                                                                                                                 |

|-------------------------------------------|--------------------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CSU                                       | Central Security Unit                | Security                      | The Central Security Unit (CSU) is responsible for setting comprehensive security policy within the i.MX 6Solo/6DualLite platform.                                                                                                                                                                                                                                                |

| CTI-0<br>CTI-1<br>CTI-2<br>CTI-3<br>CTI-4 | Cross Trigger Interfaces             | Debug / Trace                 | Cross Trigger Interfaces allows cross-triggering based<br>on inputs from masters attached to CTIs. The CTI<br>module is internal to the Cortex-A9 Core Platform.                                                                                                                                                                                                                  |

| СТМ                                       | Cross Trigger Matrix                 | Debug / Trace                 | Cross Trigger Matrix IP is used to route triggering events<br>between CTIs. The CTM module is internal to the<br>Cortex-A9 Core Platform.                                                                                                                                                                                                                                         |

| DAP                                       | Debug Access Port                    | System Control<br>Peripherals | <ul> <li>The DAP provides real-time access for the debugger without halting the core to:</li> <li>System memory and peripheral registers</li> <li>All debug configuration registers</li> <li>The DAP also provides debugger access to JTAG scan chains. The DAP module is internal to the Cortex-A9 Core Platform.</li> </ul>                                                     |

| DCIC-0<br>DCIC-1                          | Display Content Integrity<br>Checker | Automotive IP                 | The DCIC provides integrity check on portion(s) of the display. Each i.MX 6Solo/6DualLite processor has two such modules.                                                                                                                                                                                                                                                         |

| DSI                                       | MIPI DSI i/f                         | Multimedia<br>Peripherals     | The MIPI DSI IP provides DSI standard display port<br>interface. The DSI interface support 80 Mbps to 1 Gbps<br>speed per data lane.                                                                                                                                                                                                                                              |

| DTCP                                      | DTCP                                 | Multimedia<br>Peripherals     | Provides encryption function according to Digital<br>Transmission Content Protection standard for traffic<br>over MLB150.                                                                                                                                                                                                                                                         |

| eCSPI1-4                                  | Configurable SPI                     | Connectivity<br>Peripherals   | Full-duplex enhanced Synchronous Serial Interface. It is configurable to support Master/Slave modes, four chip selects to support multiple peripherals.                                                                                                                                                                                                                           |

| ENET                                      | Ethernet Controller                  | Connectivity<br>Peripherals   | The Ethernet Media Access Controller (MAC) is<br>designed to support 10/100/1000 Mbps Ethernet/IEEE<br>802.3 networks. An external transceiver interface and<br>transceiver function are required to complete the<br>interface to the media. The module has dedicated<br>hardware to support the IEEE 1588 standard. See the<br>ENET chapter of the reference manual for details. |

|                                           |                                      |                               | <b>Note:</b> The theoretical maximum performance of 1 Gbps<br>ENET is limited to 470 Mbps (total for Tx and Rx) due to<br>internal bus throughput limitations. The actual<br>measured performance in optimized environment is up<br>to 400 Mbps. For details, see the ERR004512 erratum<br>in the i.MX 6Solo/6DualLite errata document<br>(IMX6SDLCE).                            |

#### Table 2. i.MX 6Solo/6DualLite Modules List (continued)

| Block Mnemonic                                                     | Block Name                           | Subsystem                     | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------|--------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| EPIT-1<br>EPIT-2                                                   | Enhanced Periodic<br>Interrupt Timer | Timer Peripherals             | Each EPIT is a 32-bit "set and forget" timer that starts<br>counting after the EPIT is enabled by software. It is<br>capable of providing precise interrupts at regular<br>intervals with minimal processor intervention. It has a<br>12-bit prescaler for division of input clock frequency to<br>get the required time setting for the interrupts to occur,<br>and counter value can be programmed on the fly.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| ESAI                                                               | Enhanced Serial Audio<br>Interface   | Connectivity<br>Peripherals   | The Enhanced Serial Audio Interface (ESAI) provides a<br>full-duplex serial port for serial communication with a<br>variety of serial devices, including industry-standard<br>codecs, SPDIF transceivers, and other processors.<br>The ESAI consists of independent transmitter and<br>receiver sections, each section with its own clock<br>generator. All serial transfers are synchronized to a<br>clock. Additional synchronization signals are used to<br>delineate the word frames. The normal mode of<br>operation is used to transfer data at a periodic rate, one<br>word per period. The network mode is also intended for<br>periodic transfers; however, it supports up to 32 words<br>(time slots) per period. This mode can be used to build<br>time division multiplexed (TDM) networks. In contrast,<br>the on-demand mode is intended for non-periodic<br>transfers of data and to transfer data serially at high<br>speed when the data becomes available.<br>The ESAI has 12 pins for data and clocking connection<br>to external devices. |

| FlexCAN-1<br>FlexCAN-2                                             | Flexible Controller Area<br>Network  | Connectivity<br>Peripherals   | The CAN protocol was primarily, but not only, designed<br>to be used as a vehicle serial data bus, meeting the<br>specific requirements of this field: real-time processing,<br>reliable operation in the Electromagnetic interference<br>(EMI) environment of a vehicle, cost-effectiveness and<br>required bandwidth. The FlexCAN module is a full<br>implementation of the CAN protocol specification,<br>Version 2.0 B, which supports both standard and<br>extended message frames.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 512x8 Fuse Box                                                     | Electrical Fuse Array                | Security                      | Electrical Fuse Array. Enables to setup Boot Modes,<br>Security Levels, Security Keys, and many other system<br>parameters.<br>The i.MX 6Solo/6DualLite processors consist of<br>512x8-bit fuse fox accessible through OCOTP_CTRL<br>interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| GPIO-1<br>GPIO-2<br>GPIO-3<br>GPIO-4<br>GPIO-5<br>GPIO-6<br>GPIO-7 | General Purpose I/O<br>Modules       | System Control<br>Peripherals | Used for general purpose input/output to external ICs.<br>Each GPIO module supports 32 bits of I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

#### **Modules List**

| Block Mnemonic | Block Name                    | Subsystem                            | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|----------------|-------------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| WDOG-1         | Watch Dog                     | Timer Peripherals                    | The Watch Dog Timer supports two comparison points<br>during each counting period. Each of the comparison<br>points is configurable to evoke an interrupt to the ARM<br>core, and a second point evokes an external event on<br>the WDOG line.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| WDOG-2<br>(TZ) | Watch Dog (TrustZone)         | Timer Peripherals                    | The TrustZone Watchdog (TZ WDOG) timer module<br>protects against TrustZone starvation by providing a<br>method of escaping normal mode and forcing a switch<br>to the TZ mode. TZ starvation is a situation where the<br>normal OS prevents switching to the TZ mode. Such<br>situation is undesirable as it can compromise the<br>system's security. Once the TZ WDOG module is<br>activated, it must be serviced by TZ software on a<br>periodic basis. If servicing does not take place, the timer<br>times out. Upon a time-out, the TZ WDOG asserts a TZ<br>mapped interrupt that forces switching to the TZ mode.<br>If it is still not served, the TZ WDOG asserts a security<br>violation signal to the CSU. The TZ WDOG module<br>cannot be programmed or deactivated by a normal<br>mode SW. |

| WEIM           | NOR-Flash /PSRAM<br>interface | Connectivity<br>Peripherals          | <ul> <li>The WEIM NOR-FLASH / PSRAM provides:</li> <li>Support 16-bit (in muxed IO mode only) PSRAM memories (sync and async operating modes), at slow frequency</li> <li>Support 16-bit (in muxed IO mode only) NOR-Flash memories, at slow frequency</li> <li>Multiple chip selects</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| XTALOSC        | Crystal Oscillator I/F        | Clocks, Resets, and<br>Power Control | The XTALOSC module enables connectivity to external crystal oscillator device. In a typical application use-case, it is used for 24 MHz oscillator to provide USB required frequency.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

Table 2. i.MX 6Solo/6DualLite Modules List (continued)

#### Table 10. Maximum Supply Currents (continued)

| Power Line                | Conditions | Conditions Max Current                                                                                                                                                                         |    |  |  |  |

|---------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|--|

| NVCC_LVDS2P5 <sup>6</sup> | _          | <ul> <li>NVCC_LVDS2P5 is connected to</li> <li>VDD_HIGH_CAP at the board level.</li> <li>VDD_HIGH_CAP is capable of</li> <li>handing the current required by</li> <li>NVCC_LVDS2P5.</li> </ul> |    |  |  |  |

| MISC                      |            |                                                                                                                                                                                                |    |  |  |  |

| DDR_VREF                  |            | 1                                                                                                                                                                                              | mA |  |  |  |

The actual maximum current drawn from VDD\_HIGH\_IN will be as shown plus any additional current drawn from the VDD\_HIGH\_CAP outputs, depending upon actual application configuration (for example, NVCC\_LVDS\_2P5, NVCC\_MIPI, or HDMI and PCIe VPH supplies).

- <sup>2</sup> Under normal operating conditions, the maximum current on VDD\_SNVS\_IN is shown in Table 10. The maximum VDD\_SNVS\_IN current may be higher depending on specific operating configurations, such as BOOT\_MODE[1:0] not equal to 00, or use of the Tamper feature. During initial power on, VDD\_SNVS\_IN can draw up to 1 mA if the supply is capable of sourcing that current. If less than 1 mA is available, the VDD\_SNVS\_CAP charge time will increase.

- <sup>3</sup> This is the maximum current per active USB physical interface.

- <sup>4</sup> The DRAM power consumption is dependent on several factors, such as external signal termination. DRAM power calculators are typically available from the memory vendors. They take in account factors, such as signal termination. See the i.MX 6Solo/DualLite Power Consumption Measurement Application Note (AN4576) for examples of DRAM power consumption during specific use case scenarios.

- <sup>5</sup> General equation for estimated, maximum power consumption of an IO power supply:

- $Imax = N \times C \times V \times (0.5 \times F)$

Where:

1

- N—Number of IO pins supplied by the power line

- C—Equivalent external capacitive load

- V—IO voltage

- (0.5 xF)—Data change rate. Up to 0.5 of the clock rate (F)

- In this equation, Imax is in Amps, C in Farads, V in Volts, and F in Hertz.

- <sup>6</sup> NVCC\_LVDS2P5 is supplied by VDD\_HIGH\_CAP (by external connection) so the maximum supply current is included in the current shown for VDD\_HIGH\_IN. The maximum supply current for NVCC\_LVDS2P5 has not been characterized separately.

### 4.1.6 Low Power Mode Supply Currents

Table 11 shows the current core consumption (not including I/O) of i.MX 6Solo/6DualLite processors in selected low power modes.

| Mode                      | Test Conditions                                                                        | Supply             | Typical <sup>1</sup> | Units |

|---------------------------|----------------------------------------------------------------------------------------|--------------------|----------------------|-------|

| WAIT                      | • ARM, SoC, and PU LDOs are set to 1.225                                               | VDD_ARM_IN (1.4V)  | 4.5                  |       |

|                           | <ul> <li>HIGH LDO set to 2.5 V</li> <li>Clocks are gated.</li> </ul>                   | VDD_SOC_IN (1.4V)  | 23                   | mA    |

|                           | <ul> <li>DDR is in self refresh.</li> <li>PLLs are active in bypass (24MHz)</li> </ul> | VDD_HIGH_IN (3.0V) | 13.5                 |       |

| Supply Voltages remain ON | Total                                                                                  | 79                 | mW                   |       |

| Mode       | Test Conditions | Supply            | Max Current | Unit |

|------------|-----------------|-------------------|-------------|------|

| Power Down | _               | PCIE_VP (1.1 V)   | 1.3         | mA   |

|            |                 | PCIE_VPTX (1.1 V) | 0.18        |      |

|            |                 | PCIE_VPH (2.5 V)  | 0.36        |      |

#### Table 13. PCIe PHY Current Drain (continued)

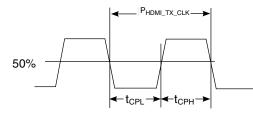

### 4.1.9 HDMI Power Consumption

Table 14 provides HDMI PHY currents for both Active 3D Tx with LFSR15 data and power-down modes.

| Mode       | Test Conditions      | Supply   | Max Current | Unit |

|------------|----------------------|----------|-------------|------|

| Active     | Bit rate 251.75 Mbps | HDMI_VPH | 14          | mA   |

|            |                      | HDMI_VP  | 4.1         | mA   |

|            | Bit rate 279.27 Mbps | HDMI_VPH | 14          | mA   |

|            |                      | HDMI_VP  | 4.2         | mA   |

|            | Bit rate 742.5 Mbps  | HDMI_VPH | 17          | mA   |

|            |                      | HDMI_VP  | 7.5         | mA   |

|            | Bit rate 1.485 Gbps  | HDMI_VPH | 17          | mA   |

|            |                      | HDMI_VP  | 12          | mA   |

|            | Bit rate 2.275 Gbps  | HDMI_VPH | 16          | mA   |

|            |                      | HDMI_VP  | 17          | mA   |

|            | Bit rate 2.97 Gbps   | HDMI_VPH | 19          | mA   |

|            |                      | HDMI_VP  | 22          | mA   |

| Power-down | —                    | HDMI_VPH | 49          | μA   |

|            |                      | HDMI_VP  | 1100        | μA   |

#### Table 14. HDMI PHY Current Drain

## 4.2 **Power Supplies Requirements and Restrictions**

The system design must comply with power-up sequence, power-down sequence, and steady state guidelines as described in this section to guarantee the reliable operation of the device. Any deviation from these sequences may result in the following situations:

- Excessive current during power-up phase

- Prevention of the device from booting

- Irreversible damage to the processor (worst-case scenario)

### 4.3.2.2 LDO\_2P5

The LDO\_2P5 module implements a programmable linear-regulator function from VDD\_HIGH\_IN (see Table 8 for minimum and maximum input requirements). Typical Programming Operating Range is 2.25 V to 2.75 V with the nominal default setting as 2.5 V. LDO\_2P5 supplies the USB Phy, LVDS Phy, HDMI Phy, MIPI Phy, E-fuse module, and PLLs. A programmable brown-out detector is included in the regulator that can be used by the system to determine when the load capability of the regulator is being exceeded, to take the necessary steps. Current-limiting can be enabled to allow for in-rush current requirements during start-up, if needed. Active-pull-down can also be enabled for systems requiring this feature. An alternate self-biased low-precision weak-regulator is included that can be enabled for applications needing to keep the output voltage alive during low-power modes where the main regulator driver and its associated global bandgap reference module are disabled. The output of the weak-regulator is not programmable and is a function of the input supply as well as the load current. Typically, with a 3 V input supply the weak-regulator output is 2.525 V and its output impedance is approximately  $40 \,\Omega$

For information on external capacitor requirements for this regulator, see the Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors (IMX6DQ6SDLHDG).

For additional information, see the i.MX 6Solo/6DualLite reference manual.

### 4.3.2.3 LDO\_USB

The LDO\_USB module implements a programmable linear-regulator function from the USB\_OTG\_VBUS and USB\_H1\_VBUS voltages (4.4 V–5.25 V) to produce a nominal 3.0 V output voltage. A programmable brown-out detector is included in the regulator that can be used by the system to determine when the load capability of the regulator is being exceeded, to take the necessary steps. This regulator has a built in power-mux that allows the user to select to run the regulator from either USB\_VBUS supply, when both are present. If only one of the USB\_VBUS voltages is present, then, the regulator automatically selects this supply. Current limit is also included to help the system meet in-rush current targets.

For information on external capacitor requirements for this regulator, see the Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors (IMX6DQ6SDLHDG).

For additional information, see the i.MX 6Solo/6DualLite reference manual.

| Parameters                               | Symbol   | Test Conditions   | Min                       | Мах                       | Unit |

|------------------------------------------|----------|-------------------|---------------------------|---------------------------|------|

| Input Reference Voltage                  | Vref     | _                 | $0.49 \times \text{OVDD}$ | $0.51 \times \text{OVDD}$ | V    |

| DC High-Level input voltage              | Vih_DC   | _                 | Vref+0.13                 | OVDD                      | V    |

| DC Low-Level input voltage               | Vil_DC   | _                 | OVSS                      | Vref-0.13                 | V    |

| Differential Input Logic High            | Vih_diff | —                 | 0.26                      | Note <sup>2</sup>         |      |

| Differential Input Logic Low             | Vil_diff | —                 | Note <sup>3</sup>         | -0.26                     |      |

| Pull-up/Pull-down Impedance Mismatch     | Mmpupd   | —                 | -15                       | 15                        | %    |

| 240 $\Omega$ unit calibration resolution | Rres     | —                 | _                         | 10                        | Ω    |

| Keeper Circuit Resistance                | Rkeep    | —                 | 110                       | 175                       | kΩ   |

| Input current (no pull-up/down)          | lin      | VI = 0, VI = OVDD | -2.5                      | 2.5                       | μA   |

Table 24. LPDDR2 I/O DC Electrical Parameters<sup>1</sup> (continued)

<sup>1</sup> Note that the JEDEC LPDDR2 specification (JESD209\_2B) supersedes any specification in this document.

<sup>2</sup> The single-ended signals need to be within the respective limits (Vih(dc) max, Vil(dc) min) for single-ended signals as well as the limitations for overshoot and undershoot.

<sup>3</sup> The single-ended signals need to be within the respective limits (Vih(dc) max, Vil(dc) min) for single-ended signals as well as the limitations for overshoot and undershoot.

### 4.6.3.2 DDR3/DDR3L Mode I/O DC Parameters

The parameters in Table 25 are guaranteed per the operating ranges in Table 8, unless otherwise noted. For details on supported DDR memory configurations, see Section 4.9.4, "Multi-Mode DDR Controller (MMDC).

| Parameters                           | Symbol   | Test Conditions                           | Min                        | Мах                       | Unit |

|--------------------------------------|----------|-------------------------------------------|----------------------------|---------------------------|------|

| High-level output voltage            | VOH      | loh= -0.1mA<br>Voh (for DSE=001)          | $0.8 \times \text{OVDD}^2$ | —                         | V    |

| Low-level output voltage             | VOL      | lol= 0.1mA<br>Vol (for DSE=001)           | _                          | $0.2 \times \text{OVDD}$  | V    |

| High-level output voltage            | VOH      | loh= -1mA<br>Voh (for all except DSE=001) | $0.8 \times \text{OVDD}$   | —                         | V    |

| Low-level output voltage             | VOL      | Iol= 1mA<br>Vol (for all except DSE=001)  | _                          | $0.2 \times \text{OVDD}$  | V    |

| Input Reference Voltage              | Vref     | _                                         | $0.49 \times \text{OVDD}$  | $0.51 \times \text{OVDD}$ | V    |

| DC High-Level input voltage          | Vih_DC   | _                                         | Vref <sup>3</sup> +0.1     | OVDD                      | V    |

| DC Low-Level input voltage           | Vil_DC   | _                                         | OVSS                       | Vref-0.1                  | V    |

| Differential Input Logic High        | Vih_diff | _                                         | 0.2                        | See Note <sup>4</sup>     | V    |

| Differential Input Logic Low         | Vil_diff | _                                         | See Note <sup>3</sup>      | -0.2                      | V    |

| Termination Voltage                  | Vtt      | Vtt tracking OVDD/2                       | $0.49 \times \text{OVDD}$  | $0.51 \times \text{OVDD}$ | V    |

| Pull-up/Pull-down Impedance Mismatch | Mmpupd   |                                           | -10                        | 10                        | %    |

Table 25. DDR3/DDR3L I/O DC Electrical Characteristics<sup>1</sup>

| Parameter                                         | Symbol | Test Conditions        | Min  | Мах  | Unit |

|---------------------------------------------------|--------|------------------------|------|------|------|

| Output Differential Voltage                       | VOD    | Rload-50Ω Diff         | 300  | 500  | mV   |

| Output High Voltage                               | VOH    | Rload-50Ω Diff         | 1.25 | 1.75 | V    |

| Output Low Voltage                                | VOL    | Rload-50 $\Omega$ Diff | 0.75 | 1.25 | V    |

| Common-mode output voltage<br>((Vpadp*+Vpadn*)/2) | Vocm   | Rload-50 $\Omega$ Diff | 1    | 1.5  | V    |

| Differential output impedance                     | Zo     | _                      | 1.6  | —    | kΩ   |

#### Table 28. MLB I/O DC Characteristics

### 4.7 I/O AC Parameters

This section includes the AC parameters of the following I/O types:

- General Purpose I/O (GPIO)

- Double Data Rate I/O (DDR) for LPDDR2 and DDR3/DDR3L modes

- LVDS I/O

- MLB I/O

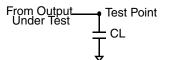

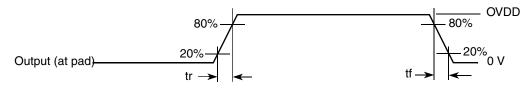

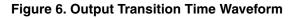

The GPIO and DDR I/O load circuit and output transition time waveforms are shown in Figure 5 and Figure 6.

CL includes package, probe and fixture capacitance

#### Figure 5. Load Circuit for Output

### 4.7.1 General Purpose I/O AC Parameters

The I/O AC parameters for GPIO in slow and fast modes are presented in the Table 29 and Table 30, respectively. Note that the fast or slow I/O behavior is determined by the appropriate control bits in the IOMUXC control registers.

### 4.10.2 Source Synchronous Mode AC Timing (ONFI 2.x Compatible)

NF19 NF18 NAND\_CE\_B ┥╺┝ NF23 NAND\_CLE ┥┥┝┥ NF25 NF26 NF24 NAND\_ALE NF25 NF26 NAND\_WE/RE\_B NF22 NAND\_CLK NAND\_DQS NAND\_DQS Output enable NF20 NF20 NF21 NF21 **.** CMD ADD NAND\_DATA[7:0] NAND\_DATA[7:0] Output enable

Figure 30 to Figure 32 show the write and read timing of Source Synchronous Mode.

Figure 30. Source Synchronous Mode Command and Address Timing Diagram

| ID   | Parameter                        | Parameter Symbol   |                   | Cycle | Unit |

|------|----------------------------------|--------------------|-------------------|-------|------|

|      |                                  |                    | Min               | Мах   |      |

| NF28 | Data write setup                 | tDS <sup>6</sup>   | 0.25 × tCK - 0.32 | —     | ns   |

| NF29 | Data write hold                  | tDH <sup>6</sup>   | 0.25 × tCK - 0.79 | —     | ns   |

| NF30 | NAND_DQS/NAND_DQ read setup skew | tDQSQ <sup>7</sup> | —                 | 3.18  |      |

| NF31 | NAND_DQS/NAND_DQ read hold skew  | tQHS <sup>7</sup>  | —                 | 3.27  |      |

#### Table 48. Samsung Toggle Mode Timing Parameters<sup>1</sup> (continued)

<sup>1</sup> The GPMI toggle mode output timing can be controlled by the module's internal registers HW\_GPMI\_TIMING0\_ADDRESS\_SETUP, HW\_GPMI\_TIMING0\_DATA\_SETUP, and HW\_GPMI\_TIMING0\_DATA\_HOLD. This AC timing depends on these registers settings. In the table, AS/DS/DH represents each of these settings.

<sup>2</sup> AS minimum value can be 0, while DS/DH minimum value is 1.

<sup>3</sup> T = tCK (GPMI clock period) -0.075ns (half of maximum p-p jitter).

<sup>4</sup> CE\_DELAY represents HW\_GPMI\_TIMING2[CE\_DELAY]. NF18 is guaranteed by the design. Read/Write operation is started with enough time of ALE/CLE assertion to low level.

<sup>5</sup> PRE\_DELAY+1)  $\geq$  (AS+DS).

<sup>6</sup> Shown in Figure 34, Samsung Toggle Mode Data Write Timing diagram.

<sup>7</sup> Shown in Figure 33, NAND\_DQS/NAND\_DQ Read Valid Window.

For DDR Toggle mode, Figure 33 shows the timing diagram of NAND\_DQS/NAND\_DATAxx read valid window. The typical value of tDQSQ is 1.4 ns (max) and 1.4 ns (max) for tQHS at 133 MB/s. GPMI will sample NAND\_DATA[7:0] at both rising and falling edge of an delayed NAND\_DQS signal, which is provided by an internal DPLL. The delay value of this register can be controlled by GPMI register GPMI\_READ\_DDR\_DLL\_CTRL.SLV\_DLY\_TARGET (see the GPMI chapter of the i.MX 6Solo/6DualLite reference manual). Generally, the typical delay value is equal to 0x7 which means 1/4 clock cycle delay expected. But if the board delay is big enough and cannot be ignored, the delay value should be made larger to compensate the board delay.

### 4.11 External Peripheral Interface Parameters

The following subsections provide information on external peripheral interfaces.

### 4.11.1 AUDMUX Timing Parameters

The AUDMUX provides a programmable interconnect logic for voice, audio, and data routing between internal serial interfaces (SSIs) and external serial interfaces (audio and voice codecs). The AC timing of AUDMUX external pins is governed by the SSI module. For more information, see the respective SSI electrical specifications found within this document.

### 4.11.2 ECSPI Timing Parameters

This section describes the timing parameters of the ECSPI blocks. The ECSPI have separate timing parameters for master and slave modes.

| Characteristics <sup>1,2</sup>                                                       | Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Expression <sup>2</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Min                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Max                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Condition <sup>3</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

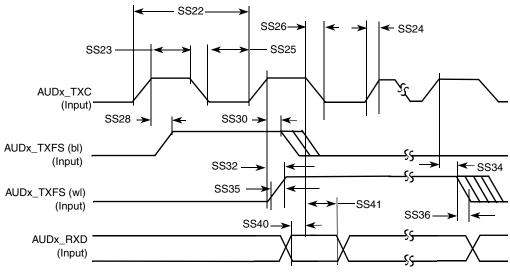

| ESAI_TX_CLK rising edge to ESAI_TX_FS out (wr) low <sup>5</sup>                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22.0<br>12.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | x ck<br>i ck                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ESAI_TX_CLK rising edge to ESAI_TX_FS out (wI) high                                  | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 19.0<br>9.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | x ck<br>i ck                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ESAI_TX_CLK rising edge to ESAI_TX_FS out (wI) low                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 20.0<br>10.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | x ck<br>i ck                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |