#### Welcome to E-XFL.COM

#### **Understanding Embedded - Microprocessors**

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Details                            |                                                                                                                     |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Product Status                     | Active                                                                                                              |

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 2 Core, 32-Bit                                                                                                      |

| Speed                              | 1GHz                                                                                                                |

| Co-Processors/DSP                  | Multimedia; NEON™ SIMD                                                                                              |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | -                                                                                                                   |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | -40°C ~ 125°C (TJ)                                                                                                  |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-LFBGA                                                                                                           |

| Supplier Device Package            | 624-MAPBGA (21x21)                                                                                                  |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6u4avm10ac                                             |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

• The *i.MX 6Solo/6DualLite Applications Processors for Industrial Products* data sheet (IMX6SDLIEC) covers parts listed with "C (Industrial temp)"

For more information go to <u>nxp.com/imx6series</u> or contact a NXP representative for details.

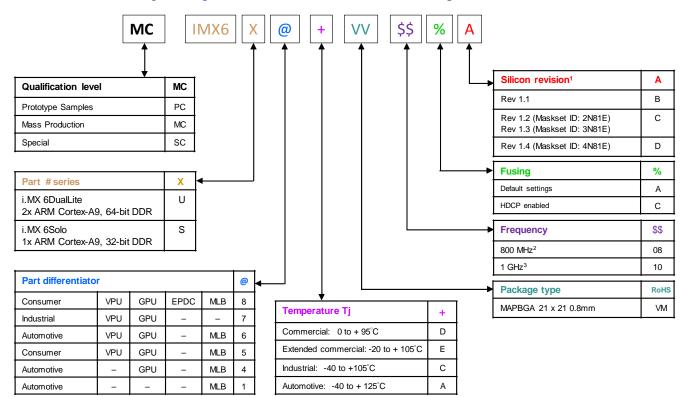

1. See the nxp.com\imx6series Web page for latest information on the available silicon revision.

2. If a 24 MHz input clock is used (required for USB), the maximum SoC speed is limited to 792 MHz. 3. If a 24 MHz input clock is used (required for USB), the maximum SoC speed is limited to 996 MHz.

## Figure 1. Part Number Nomenclature—i.MX 6Solo and 6DualLite

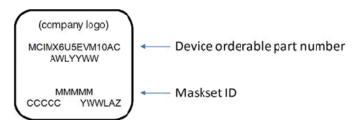

Figure 2. Example Part Marking

# 1.2 Features

The i.MX 6Solo/6DualLite processors are based on ARM Cortex-A9 MPCore Platform, which has the following features:

- The i.MX 6Solo supports single ARM Cortex-A9 MPCore (with TrustZone)

- The i.MX 6DualLite supports dual ARM Cortex-A9 MPCore (with TrustZone)

- The core configuration is symmetric, where each core includes:

- LVDS serial ports—One port up to 165 Mpixels/sec or two ports up to 85 MP/sec (for example, WUXGA at 60 Hz) each

- HDMI 1.4 port

- MIPI/DSI, two lanes at 1 Gbps

- Camera sensors:

- Two parallel Camera ports (up to 20 bit and up to 240 MHz peak)

- MIPI CSI-2 Serial port, supporting from 80 Mbps to 1 Gbps speed per data lane. The CSI-2 Receiver core can manage one clock lane and up to two data lanes. Each i.MX 6Solo/6DualLite processor has two lanes.

- Expansion cards:

- Four MMC/SD/SDIO card ports all supporting:

- 1-bit or 4-bit transfer mode specifications for SD and SDIO cards up to UHS-I SDR-104 mode (104 MB/s max)

- 1-bit, 4-bit, or 8-bit transfer mode specifications for MMC cards up to 52 MHz in both SDR and DDR modes (104 MB/s max)

- USB:

- One high speed (HS) USB 2.0 OTG (Up to 480 Mbps), with integrated HS USB Phy

- Three USB 2.0 (480 Mbps) hosts:

- One HS host with integrated High Speed Phy

- Two HS hosts with integrated HS-IC USB (High Speed Inter-Chip USB) Phy

- Expansion PCI Express port (PCIe) v2.0 one lane

- PCI Express (Gen 2.0) dual mode complex, supporting Root complex operations and Endpoint operations. Uses x1 PHY configuration.

- Miscellaneous IPs and interfaces:

- SSI block is capable of supporting audio sample frequencies up to 192 kHz stereo inputs and outputs with I<sup>2</sup>S mode

- ESAI is capable of supporting audio sample frequencies up to 260 kHz in I<sup>2</sup>S mode with 7.1 multi channel outputs

- Five UARTs, up to 5.0 Mbps each:

- Providing RS232 interface

- Supporting 9-bit RS485 multidrop mode

- One of the five UARTs (UART1) supports 8-wire while others four supports 4-wire. This is due to the SoC IOMUX limitation, since all UART IPs are identical.

- Four eCSPI (Enhanced CSPI)

- Four  $I^2C$ , supporting 400 kbps

- Gigabit Ethernet Controller (IEEE1588 compliant), 10/100/1000<sup>1</sup> Mbps

- Four Pulse Width Modulators (PWM)

1. The theoretical maximum performance of 1 Gbps ENET is limited to 470 Mbps (total for Tx and Rx) due to internal bus throughput limitations. The actual measured performance in optimized environment is up to 400 Mbps. For details, see the ERR004512 erratum in the i.MX 6Solo/6DualLite errata document (IMX6SDLCE).

## NOTE

The actual feature set depends on the part numbers as described in Table 1, "Example Orderable Part Numbers," on page 3. Functions, such as video hardware acceleration, and 2D and 3D hardware graphics acceleration may not be enabled for specific part numbers.

# **1.3 Updated Signal Naming Convention**

The signal names of the i.MX6 series of products have been standardized to better align the signal names within the family and across the documentation. Some of the benefits of these changes are as follows:

- The names are unique within the scope of an SoC and within the series of products

- Searches will return all occurrences of the named signal

- The names are consistent between i.MX 6 series products implementing the same modules

- The module instance is incorporated into the signal name

This change applies only to signal names. The original ball names have been preserved to prevent the need to change schematics, BSDL models, IBIS models, etc.

Throughout this document, the updated signal names are used except where referenced as a ball name (such as the Functional Contact Assignments table, Ball Map table, and so on). A master list of the signal name changes is in the document, *IMX 6 Series Signal Name Mapping* (EB792). This list can be used to map the signal names used in older documentation to the new standardized naming conventions.

# 3 Modules List

The i.MX 6Solo/6DualLite processors contain a variety of digital and analog modules. Table 2 describes these modules in alphabetical order.

| Block Mnemonic | Block Name                                           | Subsystem                     | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------|------------------------------------------------------|-------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APBH-DMA       | NAND Flash and BCH<br>ECC DMA controller             | System Control<br>Peripherals | DMA controller used for GPMI2 operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ARM            | ARM Platform                                         | ARM                           | The ARM Core Platform includes 1x (Solo) Cortex-A9 core for i.MX 6Solo and 2x (Dual) Cortex-A9 cores for i.MX 6DualLite. It also includes associated sub-blocks, such as the Level 2 Cache Controller, SCU (Snoop Control Unit), GIC (General Interrupt Controller), private timers, watchdog, and CoreSight debug modules.                                                                                                                                                                                                                                                                       |

| ASRC           | Asynchronous Sample<br>Rate Converter                | Multimedia<br>Peripherals     | The Asynchronous Sample Rate Converter (ASRC)<br>converts the sampling rate of a signal associated to an<br>input clock into a signal associated to a different output<br>clock. The ASRC supports concurrent sample rate<br>conversion of up to 10 channels of about -120dB<br>THD+N. The sample rate conversion of each channel is<br>associated to a pair of incoming and outgoing sampling<br>rates. The ASRC supports up to three sampling rate<br>pairs.                                                                                                                                    |

| AUDMUX         | Digital Audio Mux                                    | Multimedia<br>Peripherals     | The AUDMUX is a programmable interconnect for voice,<br>audio, and synchronous data routing between host<br>serial interfaces (for example, SSI1, SSI2, and SSI3)<br>and peripheral serial interfaces (audio and voice<br>codecs). The AUDMUX has seven ports with identical<br>functionality and programming models. A desired<br>connectivity is achieved by configuring two or more<br>AUDMUX ports.                                                                                                                                                                                           |

| BCH40          | Binary-BCH ECC<br>Processor                          | System Control<br>Peripherals | The BCH40 module provides up to 40-bit ECC for NAND Flash controller (GPMI)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| CAAM           | Cryptographic<br>accelerator and<br>assurance module | Security                      | CAAM is a cryptographic accelerator and assurance<br>module. CAAM implements several encryption and<br>hashing functions, a run-time integrity checker, and a<br>Pseudo Random Number Generator (PRNG). The<br>pseudo random number generator is certified by<br>Cryptographic Algorithm Validation Program (CAVP) of<br>National Institute of Standards and Technology (NIST).<br>Its DRBG validation number is 94 and its SHS validation<br>number is 1455.<br>CAAM also implements a Secure Memory mechanism.<br>In i.MX 6Solo/6DualLite processors, the security<br>memory provided is 16 KB. |

| CCM            | Clock Control Module,                                | Clocks, Resets, and           | These modules are responsible for clock and reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| GPC<br>SRC     | General Power Controller,<br>System Reset Controller | Power Control                 | distribution in the system, and also for the system power management.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| CSI            | MIPI CSI-2 i/f                                       | Multimedia<br>Peripherals     | The CSI IP provides MIPI CSI-2 standard camera<br>interface port. The CSI-2 interface supports from 80<br>Mbps to 1 Gbps speed per data lane.                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

Table 2. i.MX 6Solo/6DualLite Modules List

# 4.1.5 Maximum Supply Currents

The Power Virus numbers shown in Table 10 represent a use case designed specifically to show the maximum current consumption possible. All cores are running at the defined maximum frequency and are limited to L1 cache accesses only to ensure no pipeline stalls. Although a valid condition, it would have a very limited practical use case, if at all, and be limited to an extremely low duty cycle unless the intention was to specifically show the worst case power consumption.

The NXP power management IC, MMPF0100xxxx, which is targeted for the i.MX 6 series processor family, supports the power consumption shown in Table 10, however a robust thermal design is required for the increased system power dissipation.

See the i.MX 6Solo/6DualLite Power Consumption Measurement Application Note (AN4576) for more details on typical power consumption under various use case definitions.

| Power Line                             | Conditions                                                          | Max Current                          | Unit     |

|----------------------------------------|---------------------------------------------------------------------|--------------------------------------|----------|

| VDD_ARM_IN                             | i.MX 6DualLite: 996 MHz ARM clock based on<br>Power Virus operation | 2200                                 | mA       |

|                                        | i.MX 6Solo: 996 MHz ARM clock based on Power<br>Virus operation     | 1320                                 | mA       |

| VDD_SOC_IN                             | 996 MHz ARM clock                                                   | 1260                                 | mA       |

| VDD_HIGH_IN                            | -                                                                   | 125 <sup>1</sup>                     | mA       |

| VDD_SNVS_IN                            |                                                                     | 275 <sup>2</sup>                     | μA       |

| USB_OTG_VBUS/<br>USB_H1_VBUS (LDO 3P0) | -                                                                   | 25 <sup>3</sup>                      | mA       |

|                                        | Primary Interface (IO) Supplies                                     |                                      |          |

| NVCC_DRAM                              | -                                                                   | 4                                    | —        |

| NVCC_ENET                              | N=10                                                                | Use maximum IO equation <sup>5</sup> | —        |

| NVCC_LCD                               | N=29                                                                | Use maximum IO equation <sup>5</sup> | —        |

| NVCC_GPIO                              | N=24                                                                | Use maximum IO equation <sup>5</sup> | —        |

| NVCC_CSI                               | N=20                                                                | Use maximum IO equation <sup>5</sup> | —        |

| NVCC_EIM                               | N=53                                                                | Use maximum IO equation <sup>5</sup> | —        |

| NVCC_JTAG                              | N=6                                                                 | Use maximum IO equation <sup>5</sup> | _        |

| NVCC_RGMII                             | N=6                                                                 | Use maximum IO equation <sup>5</sup> | —        |

| NVCC_SD1                               | N=6                                                                 | Use maximum IO equation <sup>5</sup> | <u> </u> |

| NVCC_SD2                               | N=6                                                                 | Use maximum IO equation <sup>5</sup> | -        |

| NVCC_SD3                               | N=11                                                                | Use maximum IO equation <sup>5</sup> | —        |

| NVCC_NANDF                             | N=26                                                                | Use maximum IO equation <sup>5</sup> | —        |

Table 10. Maximum Supply Currents

# 4.1.7 USB PHY Current Consumption

## 4.1.7.1 Power Down Mode

In power down mode, everything is powered down, including the USB\_VBUS valid detectors in typical condition. Table 12 shows the USB interface current consumption in power down mode.

## Table 12. USB PHY Current Consumption in Power Down Mode

|         | VDD_USB_CAP (3.0 V) | VDD_HIGH_CAP (2.5 V) | NVCC_PLL_OUT (1.1 V) |

|---------|---------------------|----------------------|----------------------|

| Current | 5.1 μΑ              | 1.7 μΑ               | <0.5 µA              |

## NOTE

The currents on the VDD\_HIGH\_CAP and VDD\_USB\_CAP were identified to be the voltage divider circuits in the USB-specific level shifters.

## 4.1.8 PCIe 2.0 Power Consumption

Table 13 provides PCIe PHY currents under certain Tx operating modes.

| Table 1 | 3. PCle | PHY | Current | Drain |

|---------|---------|-----|---------|-------|

|---------|---------|-----|---------|-------|

| Mode                        | Test Conditions | Supply            | Max Current | Unit |

|-----------------------------|-----------------|-------------------|-------------|------|

| P0: Normal Operation        | 5G Operations   | PCIE_VP (1.1 V)   | 40          | mA   |

|                             |                 | PCIE_VPTX (1.1 V) | 20          | 1    |

|                             |                 | PCIE_VPH (2.5 V)  | 21          | 1    |

|                             | 2.5G Operations | PCIE_VP (1.1 V)   | 27          |      |

|                             |                 | PCIE_VPTX (1.1 V) | 20          | 1    |

|                             |                 | PCIE_VPH (2.5 V)  | 20          | 1    |

| P0s: Low Recovery Time      | 5G Operations   | PCIE_VP (1.1 V)   | 30          | mA   |

| Latency, Power Saving State |                 | PCIE_VPTX (1.1 V) | 2.4         | 1    |

|                             |                 | PCIE_VPH (2.5 V)  | 18          | 1    |

| -                           | 2.5G Operations | PCIE_VP (1.1 V)   | 20          |      |

|                             |                 | PCIE_VPTX (1.1 V) | 2.4         | 1    |

|                             |                 | PCIE_VPH (2.5 V)  | 18          | 1    |

| P1: Longer Recovery Time    | _               | PCIE_VP (1.1 V)   | 12          | mA   |

| Latency, Lower Power State  |                 | PCIE_VPTX (1.1 V) | 2.4         | 1    |

|                             |                 | PCIE_VPH (2.5 V)  | 12          | 1    |

| Mode       | Test Conditions | Supply            | Max Current | Unit |

|------------|-----------------|-------------------|-------------|------|

| Power Down | _               | PCIE_VP (1.1 V)   | 1.3         | mA   |

|            |                 | PCIE_VPTX (1.1 V) | 0.18        |      |

|            |                 | PCIE_VPH (2.5 V)  | 0.36        |      |

## Table 13. PCIe PHY Current Drain (continued)

# 4.1.9 HDMI Power Consumption

Table 14 provides HDMI PHY currents for both Active 3D Tx with LFSR15 data and power-down modes.

| Mode       | Test Conditions      | Supply   | Max Current | Unit |

|------------|----------------------|----------|-------------|------|

| Active     | Bit rate 251.75 Mbps | HDMI_VPH | 14          | mA   |

|            |                      | HDMI_VP  | 4.1         | mA   |

|            | Bit rate 279.27 Mbps | HDMI_VPH | 14          | mA   |

|            |                      | HDMI_VP  | 4.2         | mA   |

|            | Bit rate 742.5 Mbps  | HDMI_VPH | 17          | mA   |

|            |                      | HDMI_VP  | 7.5         | mA   |

|            | Bit rate 1.485 Gbps  | HDMI_VPH | 17          | mA   |

|            |                      | HDMI_VP  | 12          | mA   |

|            | Bit rate 2.275 Gbps  | HDMI_VPH | 16          | mA   |

|            |                      | HDMI_VP  | 17          | mA   |

|            | Bit rate 2.97 Gbps   | HDMI_VPH | 19          | mA   |

|            |                      | HDMI_VP  | 22          | mA   |

| Power-down | —                    | HDMI_VPH | 49          | μA   |

|            |                      | HDMI_VP  | 1100        | μA   |

## Table 14. HDMI PHY Current Drain

# 4.2 **Power Supplies Requirements and Restrictions**

The system design must comply with power-up sequence, power-down sequence, and steady state guidelines as described in this section to guarantee the reliable operation of the device. Any deviation from these sequences may result in the following situations:

- Excessive current during power-up phase

- Prevention of the device from booting

- Irreversible damage to the processor (worst-case scenario)

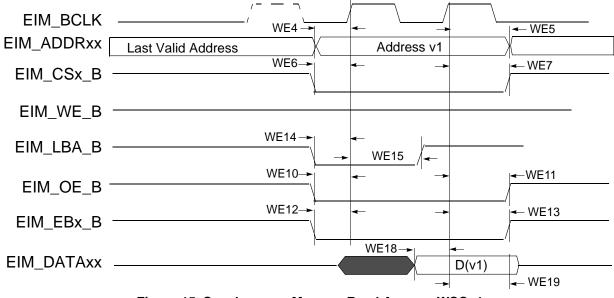

- <sup>1</sup> t is the maximum EIM logic (ACLK\_EXSC) cycle time. The maximum allowed axi\_clk frequency depends on the fixed/non-fixed latency configuration, whereas the maximum allowed EIM\_BCLK frequency is:

- -Fixed latency for both read and write is 104 MHz.

- -Variable latency for read only is 104 MHz.

- -Variable latency for write only is 52 MHz.

- In variable latency configuration for write, if BCD = 0 & WBCDD = 1 or BCD = 1, axi\_clk must be 104 MHz.Write BCD = 1 and 104 MHz ACLK\_EXSC, will result in a EIM\_BCLK of 52 MHz. When the clock branch to EIM is decreased to 104 MHz, other buses are impacted which are clocked from this source. See the CCM chapter of the *i.MX* 6Solo/6DualLite Reference Manual (*IMX*6SDLRM) for a detailed clock tree description.

- <sup>2</sup> EIM\_BCLK parameters are being measured from the 50% point, that is, high is defined as 50% of signal value and low is defined as 50% as signal value.

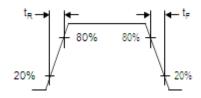

- <sup>3</sup> For signal measurements, "High" is defined as 80% of signal value and "Low" is defined as 20% of signal value.

Figure 15 to Figure 18 provide few examples of basic EIM accesses to external memory devices with the timing parameters mentioned previously for specific control parameters settings.

Figure 15. Synchronous Memory Read Access, WSC=1

## 4.11.2.2 ECSPI Slave Mode Timing

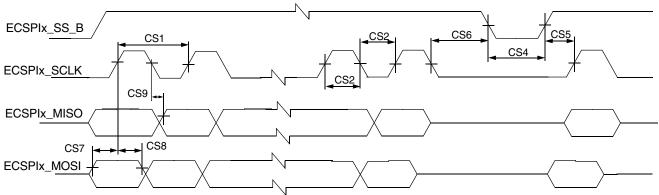

Figure 37 depicts the timing of ECSPI in slave mode. Table 50 lists the ECSPI slave mode timing characteristics.

Note: ECSPIx\_MISO is always driven (not tri-stated) between actual data transmissions. This limits the ECSPI to be connected between a single master and a single slave.

Figure 37. ECSPI Slave Mode Timing Diagram

| ID  | Parameter                                                               | Symbol              | Min                     | Max | Unit |

|-----|-------------------------------------------------------------------------|---------------------|-------------------------|-----|------|

| CS1 | ECSPIx_SCLK Cycle Time-Read<br>ECSPIx_SCLK Cycle Time-Write             | t <sub>clk</sub>    | 43<br>15                | —   | ns   |

| CS2 | ECSPIx_SCLK High or Low Time-Read<br>ECSPIx_SCLK High or Low Time-Write | t <sub>SW</sub>     | 21.5<br>7               | —   | ns   |

| CS4 | ECSPIx_SS_B pulse width                                                 | t <sub>CSLH</sub>   | Half ECSPIx_SCLK period | —   | ns   |

| CS5 | ECSPIx_SS_B Lead Time (CS setup time)                                   | t <sub>SCS</sub>    | 5                       | —   | ns   |

| CS6 | ECSPIx_SS_B Lag Time (CS hold time)                                     | t <sub>HCS</sub>    | 5                       | —   | ns   |

| CS7 | ECSPIx_MOSI Setup Time                                                  | t <sub>Smosi</sub>  | 4                       | —   | ns   |

| CS8 | ECSPIx_MOSI Hold Time                                                   | t <sub>Hmosi</sub>  | 4                       | —   | ns   |

| CS9 | ECSPIx_MISO Propagation Delay (C <sub>LOAD</sub> = 20 pF)<br>•          | t <sub>PDmiso</sub> | 4                       | 19  | ns   |

#### Table 50. ECSPI Slave Mode Timing Parameters

# 4.11.4 Ultra High Speed SD/SDIO/MMC Host Interface (uSDHC) AC Timing

This section describes the electrical information of the uSDHC, which includes SD/eMMC4.3 (Single Data Rate) timing, eMMC4.4/4.41 (Dual Date Rate) timing and SDR104/50(SD3.0) timing.

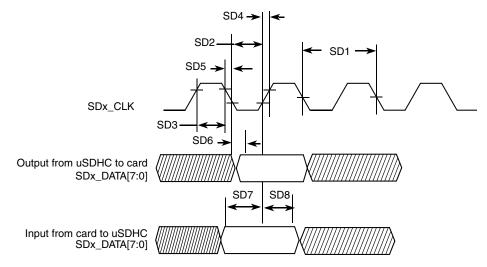

# 4.11.4.1 SD/eMMC4.3 (Single Data Rate) AC Timing

Figure 40 depicts the timing of SD/eMMC4.3, and Table 52 lists the SD/eMMC4.3 timing characteristics.

Figure 40. SD/eMMC4.3 Timing

| Table 52. SD/eMMC4.3 Interface | Timing Specification |

|--------------------------------|----------------------|

|--------------------------------|----------------------|

| ID  | Parameter                                                      | Symbols                      | Min  | Max   | Unit |  |  |  |

|-----|----------------------------------------------------------------|------------------------------|------|-------|------|--|--|--|

|     | Card Input Clock                                               |                              |      |       |      |  |  |  |

| SD1 | Clock Frequency (Low Speed)                                    | f <sub>PP</sub> <sup>1</sup> | 0    | 400   | kHz  |  |  |  |

|     | Clock Frequency (SD/SDIO Full Speed/High Speed)                | f <sub>PP</sub> <sup>2</sup> | 0    | 25/50 | MHz  |  |  |  |

|     | Clock Frequency (MMC Full Speed/High Speed)                    | f <sub>PP</sub> <sup>3</sup> | 0    | 20/52 | MHz  |  |  |  |

|     | Clock Frequency (Identification Mode)                          | f <sub>OD</sub>              | 100  | 400   | kHz  |  |  |  |

| SD2 | Clock Low Time                                                 | t <sub>WL</sub>              | 7    | —     | ns   |  |  |  |

| SD3 | Clock High Time                                                | t <sub>WH</sub>              | 7    | —     | ns   |  |  |  |

| SD4 | Clock Rise Time                                                | t <sub>TLH</sub>             | —    | 3     | ns   |  |  |  |

| SD5 | Clock Fall Time                                                | t <sub>THL</sub>             | —    | 3     | ns   |  |  |  |

|     | uSDHC Output/Card Inputs SDx_CMD, SDx_DATAx (Reference to CLK) |                              |      |       |      |  |  |  |

| SD6 | uSDHC Output Delay                                             | t <sub>OD</sub>              | -6.6 | 3.6   | ns   |  |  |  |

# 4.11.4.4 Bus Operation Condition for 3.3 V and 1.8 V Signaling

Signaling level of SD/eMMC4.3 and eMMC4.4/4.41 modes is 3.3 V. Signaling level of SDR104/SDR50 mode is 1.8 V. The DC parameters for the NVCC\_SD1, NVCC\_SD2 and NVCC\_SD3 supplies are identical to those shown in Table 23, "GPIO DC Parameters," on page 41.

# 4.11.5 Ethernet Controller (ENET) AC Electrical Specifications

The following timing specs are defined at the chip I/O pin and must be translated appropriately to arrive at timing specs/constraints for the physical interface.

# 4.11.5.1 ENET MII Mode Timing

This subsection describes MII receive, transmit, asynchronous inputs, and serial management signal timings.

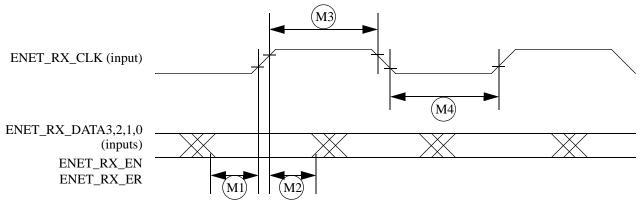

# 4.11.5.1.1 MII Receive Signal Timing (ENET\_RX\_DATA3,2,1,0, ENET\_RX\_EN, ENET\_RX\_ER, and ENET\_RX\_CLK)

The receiver functions correctly up to an ENET\_RX\_CLK maximum frequency of 25 MHz + 1%. There is no minimum frequency requirement. Additionally, the processor clock frequency must exceed twice the ENET\_RX\_CLK frequency.

Figure 43 shows MII receive signal timings. Table 55 describes the timing parameters (M1–M4) shown in the figure.

Figure 43. MII Receive Signal Timing Diagram

Table 55. MII Receive Signal Timing

| ID | Characteristic <sup>1</sup>                                        | Min | Max | Unit               |

|----|--------------------------------------------------------------------|-----|-----|--------------------|

| M1 | ENET_RX_DATA3,2,1,0, ENET_RX_EN, ENET_RX_ER to ENET_RX_CLK setup   | 5   | —   | ns                 |

| M2 | ENET_RX_CLK to ENET_RX_DATA3,2,1,0, ENET_RX_EN,<br>ENET_RX_ER hold | 5   |     | ns                 |

| M3 | ENET_RX_CLK pulse width high                                       | 35% | 65% | ENET_RX_CLK period |

| M4 | ENET_RX_CLK pulse width low                                        | 35% | 65% | ENET_RX_CLK period |

<sup>1</sup> ENET\_RX\_EN, ENET\_RX\_CLK, and ENET0\_RXD0 have the same timing in 10 Mbps 7-wire interface mode.

## Figure 58. TMDS Output Signals Rise and Fall Time Definition

| Symbol                      | Parameter                               | Conditions                                                              | Min  | Тур | Max    | Unit            |  |  |  |

|-----------------------------|-----------------------------------------|-------------------------------------------------------------------------|------|-----|--------|-----------------|--|--|--|

| TMDS Drivers Specifications |                                         |                                                                         |      |     |        |                 |  |  |  |

| —                           | Maximum serial data rate                | _                                                                       | —    | —   | 3.4    | Gbps            |  |  |  |

| F<br>TMDSCLK                | TMDSCLK frequency                       | On TMDSCLKP/N outputs                                                   | 25   | —   | 340    | MHz             |  |  |  |

| PTMDSCLK                    | TMDSCLK period                          | $RL = 50 \Omega$<br>See Figure 54.                                      | 2.94 | —   | 40     | ns              |  |  |  |

| t<br>CDC                    | TMDSCLK duty cycle                      | $t_{CDC} = t_{CPH} / P_{TMDSCLK}$<br>RL = 50 $\Omega$<br>See Figure 54. | 40   | 50  | 60     | %               |  |  |  |

| t<br>CPH                    | TMDSCLK high time                       | RL = 50 $\Omega$<br>See Figure 54.                                      | 4    | 5   | 6      | UI <sup>1</sup> |  |  |  |

| t<br>CPL                    | TMDSCLK low time                        | RL = 50 $\Omega$<br>See Figure 54.                                      | 4    | 5   | 6      | UI <sup>1</sup> |  |  |  |

| _                           | TMDSCLK jitter <sup>2</sup>             | RL = 50 Ω                                                               | —    | —   | 0.25   | UI <sup>1</sup> |  |  |  |

| t<br>SK(p)                  | Intra-pair (pulse) skew                 | RL = 50 Ω<br>See Figure 56.                                             | _    | —   | 0.15   | UI <sup>1</sup> |  |  |  |

| t<br>SK(pp)                 | Inter-pair skew                         | RL = 50 $\Omega$<br>See Figure 57.                                      | —    | —   | 1      | UI <sup>1</sup> |  |  |  |

| t <sub>R</sub>              | Differential output signal rise<br>time | 20–80%<br>RL = 50 Ω<br>See Figure 58.                                   | 75   | -   | 0.4 UI | ps              |  |  |  |

| t <sub>F</sub>              | Differential output signal fall time    | 20–80%<br>RL = 50 Ω<br>See Figure 58.                                   | 75   | -   | 0.4 UI | ps              |  |  |  |

| _                           | Differential signal overshoot           | Referred to $2x V_{SWING}$                                              | —    | —   | 15     | %               |  |  |  |

| _                           | Differential signal undershoot          | Referred to 2x V <sub>SWING</sub>                                       | _    | _   | 25     | %               |  |  |  |

**Table 62. Switching Characteristics**

<sup>1</sup> UI means TMDS clock unit.

$^{2}$  Relative to ideal recovery clock, as specified in the HDMI specification, version 1.4a, section 4.2.3.

| Signal<br>Name <sup>1</sup> | RGB565<br>8 bits<br>2 cycles | RGB565 <sup>2</sup><br>8 bits<br>3 cycles | RGB666 <sup>3</sup><br>8 bits<br>3 cycles | RGB888<br>8 bits<br>3 cycles | YCbCr <sup>4</sup><br>8 bits<br>2 cycles | RGB565 <sup>5</sup><br>16 bits<br>1 cycle | YCbCr <sup>6</sup><br>16 bits<br>1 cycle | YCbCr <sup>7</sup><br>16 bits<br>1 cycle | YCbCr <sup>8</sup><br>20 bits<br>1 cycle |

|-----------------------------|------------------------------|-------------------------------------------|-------------------------------------------|------------------------------|------------------------------------------|-------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|

| IPUx_CSIx_<br>DATA13        | B[1], G[4]                   | R[3],G[5],B[3]                            | R/G/B[5]                                  | R/G/B[1]                     | Y/C[1]                                   | G[4]                                      | Y[1]                                     | Y[1]                                     | Y[3]                                     |

| IPUx_CSIx_<br>DATA14        | B[2], G[5]                   | R[4],G[0],B[4]                            | R/G/B[0]                                  | R/G/B[2]                     | Y/C[2]                                   | G[5]                                      | Y[2]                                     | Y[2]                                     | Y[4]                                     |

| IPUx_CSIx_<br>DATA15        | B[3], R[0]                   | R[0],G[1],B[0]                            | R/G/B[1]                                  | R/G/B[3]                     | Y/C[3]                                   | R[0]                                      | Y[3]                                     | Y[3]                                     | Y[5]                                     |

| IPUx_CSIx_<br>DATA16        | B[4], R[1]                   | R[1],G[2],B[1]                            | R/G/B[2]                                  | R/G/B[4]                     | Y/C[4]                                   | R[1]                                      | Y[4]                                     | Y[4]                                     | Y[6]                                     |

| IPUx_CSIx_<br>DATA17        | G[0], R[2]                   | R[2],G[3],B[2]                            | R/G/B[3]                                  | R/G/B[5]                     | Y/C[5]                                   | R[2]                                      | Y[5]                                     | Y[5]                                     | Y[7]                                     |

| IPUx_CSIx_<br>DATA18        | G[1], R[3]                   | R[3],G[4],B[3]                            | R/G/B[4]                                  | R/G/B[6]                     | Y/C[6]                                   | R[3]                                      | Y[6]                                     | Y[6]                                     | Y[8]                                     |

| IPUx_CSIx_<br>DATA19        | G[2], R[4]                   | R[4],G[5],B[4]                            | R/G/B[5]                                  | R/G/B[7]                     | Y/C[7]                                   | R[4]                                      | Y[7]                                     | Y[7]                                     | Y[9]                                     |

<sup>1</sup> IPUx\_CSIx stands for IPUx\_CSI0 or IPUx\_CSI1.

<sup>2</sup> The MSB bits are duplicated on LSB bits implementing color extension.

<sup>3</sup> The two MSB bits are duplicated on LSB bits implementing color extension.

<sup>4</sup> YCbCr, 8 bits—Supported within the BT.656 protocol (sync embedded within the data stream).

<sup>5</sup> RGB 16 bits—Supported in two ways: (1) As a "generic data" input, with no on-the-fly processing; (2) With on-the-fly processing, but only under some restrictions on the control protocol.

<sup>6</sup> YCbCr 16 bits—Supported as a "generic-data" input, with no on-the-fly processing.

<sup>7</sup> YCbCr 16 bits—Supported as a sub-case of the YCbCr, 20 bits, under the same conditions (BT.1120 protocol).

<sup>8</sup> YCbCr, 20 bits—Supported only within the BT.1120 protocol (syncs embedded within the data stream).

## 4.11.10.2 Sensor Interface Timings

There are three camera timing modes supported by the IPU.

## 4.11.10.2.1 BT.656 and BT.1120 Video Mode

Smart camera sensors, which include imaging processing, usually support video mode transfer. They use an embedded timing syntax to replace the IPUx\_CSIx\_VSYNC and IPUx\_CSIx\_HSYNC signals. The timing syntax is defined by the BT.656/BT.1120 standards.

This operation mode follows the recommendations of ITU BT.656/ ITU BT.1120 specifications. The only control signal used is IPUx\_CSIx\_PIX\_CLK. Start-of-frame and active-line signals are embedded in the data stream. An active line starts with a SAV code and ends with a EAV code. In some cases, digital blanking is inserted in between EAV and SAV code. The CSI decodes and filters out the timing-coding from the data stream, thus recovering IPUx\_CSIx\_VSYNC and IPUx\_CSIx\_HSYNC signals for internal use. On BT.656 one component per cycle is received over the IPUx\_CSIx\_DATA\_EN bus. On BT.1120 two components per cycle are received over the IPUx\_CSIx\_DATA\_EN bus.

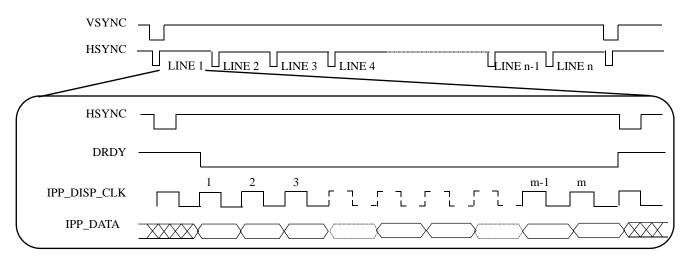

The display access can be whole number of DI clock (Tdiclk) only. The IPP\_DATA can not be moved relative to the local start point. The data bus of the synchronous interface is output direction only.

## 4.11.10.6.2 LCD Interface Functional Description

Figure 63 depicts the LCD interface timing for a generic active matrix color TFT panel. In this figure, signals are shown with negative polarity. The sequence of events for active matrix interface timing is:

- DI\_CLK internal DI clock is used for calculation of other controls.

- IPP\_DISP\_CLK latches data into the panel on its negative edge (when positive polarity is selected). In active mode, IPP\_DISP\_CLK runs continuously.

- HSYNC causes the panel to start a new line. (Usually IPUx\_DIx\_PIN02 is used as HSYNC.)

- VSYNC causes the panel to start a new frame. It always encompasses at least one HSYNC pulse. (Usually IPUx\_DIx\_PIN03 is used as VSYNC.)

- DRDY acts like an output enable signal to the CRT display. This output enables the data to be shifted onto the display. When disabled, the data is invalid and the trace is off. (DRDY can be used either synchronous or asynchronous generic purpose pin as well.)

Figure 63. Interface Timing Diagram for TFT (Active Matrix) Panels

## 4.11.10.6.3 TFT Panel Sync Pulse Timing Diagrams

Figure 64 depicts the horizontal timing (timing of one line), including both the horizontal sync pulse and the data. All the parameters shown in the figure are programmable. All controls are started by

# 4.11.11 LVDS Display Bridge (LDB) Module Parameters

The LVDS interface complies with TIA/EIA 644-A standard. For more details, see TIA/EIA STANDARD 644-A, "*Electrical Characteristics of Low Voltage Differential Signaling (LVDS) Interface Circuits*".

| Parameter                           | Symbol              | Test Condition                                                                                                                                     | Min  | Max   | Units |

|-------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------|

| Differential Voltage Output Voltage | V <sub>OD</sub>     | 100 $\Omega$ Differential load                                                                                                                     | 250  | 450   | mV    |

| Output Voltage High                 | Voh                 | 100 $\Omega$ differential load (0 V Diff—Output High Voltage static)                                                                               | 1.25 | 1.6   | V     |

| Output Voltage Low                  | Vol                 | 100 $\Omega$ differential load (0 V Diff—Output Low Voltage static)                                                                                | 0.9  | 1.25  | V     |

| Offset Static Voltage               | V <sub>OS</sub>     | Two 49.9 $\Omega$ resistors in series between N-P terminal, with output in either Zero or One state, the voltage measured between the 2 resistors. | 1.15 | 1.375 | V     |

| VOS Differential                    | V <sub>OSDIFF</sub> | Difference in $V_{\mbox{\scriptsize OS}}$ between a One and a Zero state                                                                           | -50  | 50    | mV    |

| Output short circuited to GND       | ISA ISB             | With the output common shorted to GND                                                                                                              | -24  | 24    | mA    |

| VT Full Load Test                   | VTLoad              | 100 $\Omega$ Differential load with a 3.74 k $\Omega$ load between GND and IO Supply Voltage                                                       | 247  | 454   | mV    |

Table 69. LVDS Display Bridge (LDB) Electrical Specification

# 4.11.12 MIPI D-PHY Timing Parameters

This section describes MIPI D-PHY electrical specifications, compliant with MIPI CSI-2 version 1.0, D-PHY specification Rev. 1.0 (for MIPI sensor port x2 lanes) and MIPI DSI Version 1.01, and D-PHY specification Rev. 1.0 (and also DPI version 2.0, DBI version 2.0, DSC version 1.0a at protocol layer) (for MIPI display port x2 lanes).

## 4.11.12.1 Electrical and Timing Information

| Symbol                  | Parameters                                                                              | Test Conditions                                                                         | Min | Тур | Мах  | Unit |  |  |  |

|-------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----|-----|------|------|--|--|--|

| Input                   | Input DC Specifications - Apply to DSI_CLK_P/DSI_CLK_N and DSI_DATA_P/DSI_DATA_N inputs |                                                                                         |     |     |      |      |  |  |  |

| VI                      | Input signal voltage range                                                              | Transient voltage range is<br>limited from -300 mV to<br>1600 mV                        | -50 | _   | 1350 | mV   |  |  |  |

| V <sub>LEAK</sub>       | Input leakage current                                                                   | VGNDSH(min) = VI =<br>VGNDSH(max) +<br>VOH(absmax)<br>Lane module in LP Receive<br>Mode | -10 |     | 10   | mA   |  |  |  |

| V <sub>GNDSH</sub>      | Ground Shift                                                                            | —                                                                                       | -50 | —   | 50   | mV   |  |  |  |

| V <sub>OH(absmax)</sub> | Maximum transient output voltage level                                                  | _                                                                                       | —   | —   | 1.45 | V    |  |  |  |

Table 70. Electrical and Timing Information

# 4.11.13.2 Pipelined Data Flow

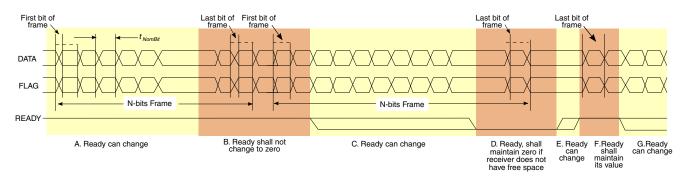

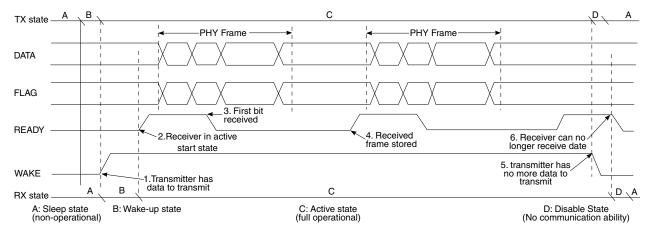

Figure 75. Pipelined Data Flow Ready Signal Timing (Frame Transmission Mode)

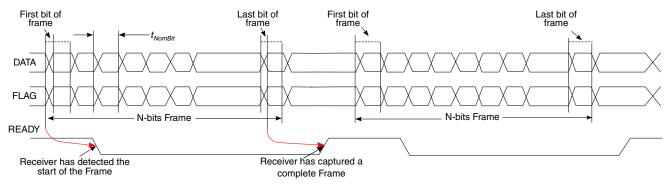

Figure 76. Receiver Real-Time Data Flow READY Signal Timing

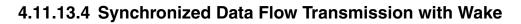

Figure 77. Synchronized Data Flow Transmission with WAKE

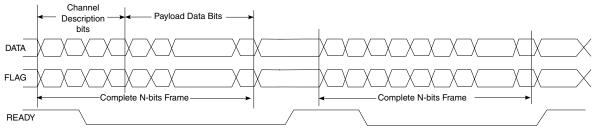

## 4.11.13.5 Stream Transmission Mode Frame Transfer

Figure 78. Stream Transmission Mode Frame Transfer (Synchronized Data Flow)

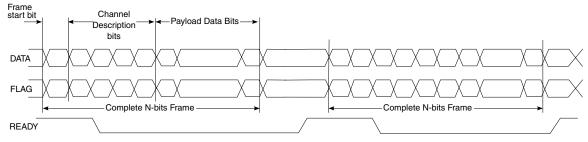

# 4.11.13.6 Frame Transmission Mode (Synchronized Data Flow)

Figure 79. Frame Transmission Mode Transfer of Two Frames (Synchronized Data Flow)

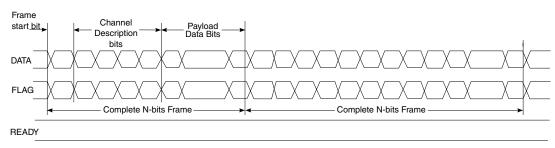

# 4.11.13.7 Frame Transmission Mode (Pipelined Data Flow)

Figure 80. Frame Transmission Mode Transfer of Two Frames (Pipelined Data Flow)

# 4.11.13.8 DATA and FLAG Signal Timing Requirement for a 15 pF Load

## Table 72. DATA and FLAG Timing

| Parameter                                            | Description                                                | 1 Mbit/s | 100 Mbit/s | 200 Mbit/s |

|------------------------------------------------------|------------------------------------------------------------|----------|------------|------------|

| t <sub>Bit, nom</sub>                                | Nominal bit time                                           | 1000 ns  | 10.0 ns    | 5.00 ns    |

| t <sub>Rise, min</sub> and<br><sup>t</sup> Fall, min | Minimum allowed rise and fall time                         | 2.00 ns  | 2.00 ns    | 1.00 ns    |

| t <sub>TxToRxSkew</sub> , maxfq                      | Maximum skew between transmitter and receiver package pins | 50.0 ns  | 0.5.0 ns   | 0.25 ns    |

# 4.11.19 SSI Timing Parameters

This section describes the timing parameters of the SSI module. The connectivity of the serial synchronous interfaces are summarized in Table 81.

| Port          | Signal Nomenclature | Type and Access                          |

|---------------|---------------------|------------------------------------------|

| AUDMUX port 1 | SSI 1               | Internal                                 |

| AUDMUX port 2 | SSI 2               | Internal                                 |

| AUDMUX port 3 | AUD3                | External—AUD3 I/O                        |

| AUDMUX port 4 | AUD4                | External—EIM or CSPI1 I/O through IOMUXC |

| AUDMUX port 5 | AUD5                | External—EIM or SD1 I/O through IOMUXC   |

| AUDMUX port 6 | AUD6                | External—EIM or DISP2 through IOMUXC     |

| AUDMUX port 7 | SSI 3               | Internal                                 |

Table 81. AUDMUX Port Allocation

## NOTE

The terms WL and BL used in the timing diagrams and tables refer to Word Length (WL) and Bit Length (BL).

## 4.11.19.1 SSI Transmitter Timing with Internal Clock

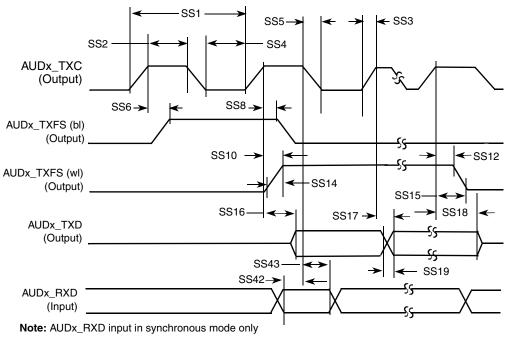

Figure 91 depicts the SSI transmitter internal clock timing and Table 82 lists the timing parameters for the SSI transmitter internal clock.

| ID                                   | Parameter                              | Min  | Мах | Unit |  |

|--------------------------------------|----------------------------------------|------|-----|------|--|

| Synchronous External Clock Operation |                                        |      |     |      |  |

| SS44                                 | AUDx_RXD setup before AUDx_TXC falling | 10.0 | —   | ns   |  |

| SS45                                 | AUDx_RXD hold after AUDx_TXC falling   | 2.0  | _   | ns   |  |

| SS46                                 | AUDx_RXD rise/fall time                | —    | 6.0 | ns   |  |

## Table 84. SSI Transmitter Timing with External Clock (continued)

## NOTE

- All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal AUDx\_TXC/AUDx\_RXC and/or the frame sync AUDx\_TXFS/AUDx\_RXFS shown in the tables and in the figures.

- All timings are on Audiomux Pads when SSI is being used for data transfer.

- The terms WL and BL refer to Word Length (WL) and Bit Length (BL).

- For internal Frame Sync operation using external clock, the frame sync timing is same as that of transmit data (for example, during AC97 mode of operation).

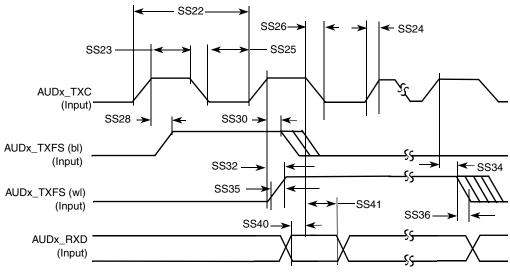

## 4.11.19.4 SSI Receiver Timing with External Clock

Figure 94 depicts the SSI receiver external clock timing and Table 85 lists the timing parameters for the receiver timing with the external clock.

Figure 94. SSI Receiver External Clock Timing Diagram

| ID                       | Parameter                                      | Min  | Max  | Unit |  |  |  |

|--------------------------|------------------------------------------------|------|------|------|--|--|--|

| External Clock Operation |                                                |      |      |      |  |  |  |

| SS22                     | AUDx_TXC/AUDx_RXC clock period                 | 81.4 | —    | ns   |  |  |  |

| SS23                     | AUDx_TXC/AUDx_RXC clock high period            | 36   | —    | ns   |  |  |  |

| SS24                     | AUDx_TXC/AUDx_RXC clock rise time              | —    | 6.0  | ns   |  |  |  |

| SS25                     | AUDx_TXC/AUDx_RXC clock low period             | 36   | —    | ns   |  |  |  |

| SS26                     | AUDx_TXC/AUDx_RXC clock fall time              | —    | 6.0  | ns   |  |  |  |

| SS28                     | AUDx_RXC high to AUDx_TXFS (bl) high           | -10  | 15.0 | ns   |  |  |  |

| SS30                     | AUDx_RXC high to AUDx_TXFS (bl) low            | 10   | —    | ns   |  |  |  |

| SS32                     | AUDx_RXC high to AUDx_TXFS (wl) high           | -10  | 15.0 | ns   |  |  |  |

| SS34                     | AUDx_RXC high to AUDx_TXFS (wl) low            | 10   | —    | ns   |  |  |  |

| SS35                     | AUDx_TXC/AUDx_RXC External AUDx_TXFS rise time | —    | 6.0  | ns   |  |  |  |

| SS36                     | AUDx_TXC/AUDx_RXC External AUDx_TXFS fall time | —    | 6.0  | ns   |  |  |  |

| SS40                     | AUDx_RXD setup time before AUDx_RXC low        | 10   | —    | ns   |  |  |  |

| SS41                     | AUDx_RXD hold time after AUDx_RXC low          | 2    | —    | ns   |  |  |  |

## Table 85. SSI Receiver Timing with External Clock

## NOTE

- All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal AUDx\_TXC/AUDx\_RXC and/or the frame sync AUDx\_TXFS/AUDx\_RXFS shown in the tables and in the figures.

- All timings are on Audiomux Pads when SSI is being used for data transfer.

- The terms, WL and BL, refer to Word Length (WL) and Bit Length (BL).

- For internal Frame Sync operation using external clock, the frame sync timing is same as that of transmit data (for example, during AC97 mode of operation).