#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of Embedded - Microprocessors

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                     | Active                                                                                                              |

|------------------------------------|---------------------------------------------------------------------------------------------------------------------|

| Core Processor                     | ARM® Cortex®-A9                                                                                                     |

| Number of Cores/Bus<br>Width       | 2 Core, 32-Bit                                                                                                      |

| Speed                              | 1GHz                                                                                                                |

| Co-Processors/DSP                  | Multimedia; NEON <sup>™</sup> SIMD                                                                                  |

| RAM Controllers                    | LPDDR2, LVDDR3, DDR3                                                                                                |

| Graphics Acceleration              | Yes                                                                                                                 |

| Display & Interface<br>Controllers | Keypad, LCD                                                                                                         |

| Ethernet                           | 10/100/1000Mbps (1)                                                                                                 |

| SATA                               | -                                                                                                                   |

| USB                                | USB 2.0 + PHY (4)                                                                                                   |

| Voltage - I/O                      | 1.8V, 2.5V, 2.8V, 3.3V                                                                                              |

| Operating Temperature              | -40°C ~ 125°C (TJ)                                                                                                  |

| Security Features                  | ARM TZ, Boot Security, Cryptography, RTIC, Secure Fusebox, Secure JTAG, Secure Memory, Secure RTC, Tamper Detection |

| Package / Case                     | 624-LFBGA                                                                                                           |

| Supplier Device Package            | 624-MAPBGA (21x21)                                                                                                  |

| Purchase URL                       | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx6u6avm10ac                                             |

|                                    |                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Block Mnemonic | Block Name                                  | Subsystem                     | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------------|---------------------------------------------|-------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SDMA           | Smart Direct Memory<br>Access               | System Control<br>Peripherals | <ul> <li>The SDMA is multi-channel flexible DMA engine. It helps in maximizing system performance by off-loading the various cores in dynamic data routing. It has the following features:</li> <li>Powered by a 16-bit Instruction-Set micro-RISC engine</li> <li>Multi-channel DMA supporting up to 32 time-division multiplexed DMA channels</li> <li>48 events with total flexibility to trigger any combination of channels</li> <li>Memory accesses including linear, FIFO, and 2D addressing</li> <li>Shared peripherals between ARM and SDMA</li> <li>Very fast Context-Switching with 2-level priority based preemptive multi-tasking</li> <li>DMA units with auto-flush and prefetch capability</li> <li>Flexible address management for DMA transfers (increment, decrement, and no address changes on source and destination address)</li> <li>DMA ports can handle unit-directional and bi-directional flows (copy mode)</li> <li>Up to 8-word buffer for configurable burst transfers</li> <li>Support of byte-swapping and CRC calculations</li> <li>Library of Scripts and API is available</li> </ul> |

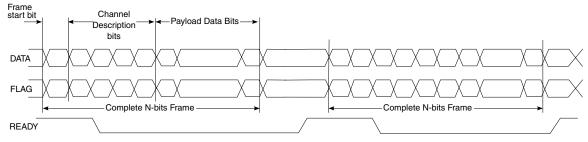

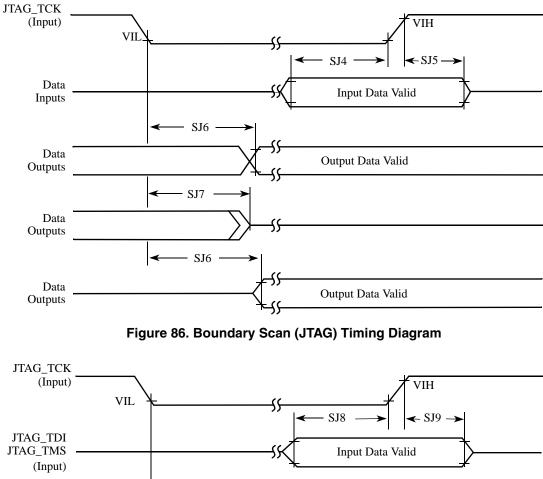

| SJC            | System JTAG Controller                      | System Control<br>Peripherals | The SJC provides JTAG interface, which complies with<br>JTAG TAP standards, to internal logic. The i.MX<br>6Solo/6DualLite processors use JTAG port for<br>production, testing, and system debugging. In addition,<br>the SJC provides BSR (Boundary Scan Register)<br>standard support, which complies with IEEE1149.1 and<br>IEEE1149.6 standards.<br>The JTAG port must be accessible during platform initial<br>laboratory bring-up, for manufacturing tests and<br>troubleshooting, as well as for software debugging by<br>authorized entities. The i.MX 6Solo/6DualLite SJC<br>incorporates three security modes for protecting against<br>unauthorized accesses. Modes are selected through<br>eFUSE configuration.                                                                                                                                                                                                                                                                                                                                                                                            |

| SNVS           | Secure Non-Volatile<br>Storage              | Security                      | Secure Non-Volatile Storage, including Secure Real<br>Time Clock, Security State Machine, Master Key<br>Control, and Violation/Tamper Detection and reporting.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| SPDIF          | Sony Philips Digital<br>Interconnect Format | Multimedia<br>Peripherals     | A standard audio file transfer format, developed jointly<br>by the Sony and Phillips corporations. Has Transmitter<br>and Receiver functionality.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Table 2. i.MX 6Solo/6DualLite Modules List (co | continued) |

|------------------------------------------------|------------|

|------------------------------------------------|------------|

| Parameter<br>Description             | Symbol                                                                                                                             | Min   | Тур                 | Max <sup>1</sup> | Unit | Comment <sup>2</sup>                                                                                                                                     |

|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------|---------------------|------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIO supply<br>voltages <sup>9</sup> | NVCC_CSI,<br>NVCC_EIM,<br>NVCC_ENET,<br>NVCC_GPIO,<br>NVCC_LCD,<br>NVCC_NANDF,<br>NVCC_SD1,<br>NVCC_SD2,<br>NVCC_SD3,<br>NVCC_JTAG | 1.65  | 1.8,<br>2.8,<br>3.3 | 3.6              | V    | _                                                                                                                                                        |

|                                      | NVCC_LVDS_2P5 <sup>10</sup><br>NVCC_MIPI                                                                                           | 2.25  | 2.5                 | 2.75             | V    | _                                                                                                                                                        |

| HDMI supply                          | HDMI_VP                                                                                                                            | 0.99  | 1.1                 | 1.3              | V    | _                                                                                                                                                        |

| voltages                             | HDMI_VPH                                                                                                                           | 2.25  | 2.5                 | 2.75             | V    | _                                                                                                                                                        |

| PCIe supply                          | PCIE_VP                                                                                                                            | 1.023 | 1.1                 | 1.21             | V    | —                                                                                                                                                        |

| voltages                             | PCIE_VPH                                                                                                                           | 2.325 | 2.5                 | 2.75             | V    | —                                                                                                                                                        |

|                                      | PCIE_VPTX                                                                                                                          | 1.023 | 1.1                 | 1.21             | V    | —                                                                                                                                                        |

| Junction<br>temperature              | T<br>J                                                                                                                             | -40   |                     | 125              | °C   | See <i>i.MX</i> 6Solo/6DualLite Product Lifetime Usage<br>Estimates Application Note, AN4725, for<br>information on product lifetime for this processor. |

## Table 8. Operating Ranges (continued)

<sup>1</sup> Applying the maximum voltage results in maximum power consumption and heat generation. NXP recommends a voltage set point = (Vmin + the supply tolerance). This results in an optimized power/speed ratio.

<sup>2</sup> See the Hardware Development Guide for i.MX 6Quad, 6Dual, 6DualLite, 6Solo Families of Applications Processors (IMX6DQ6SDLHDG) for bypass capacitors requirements for each of the \*\_CAP supply outputs.

<sup>3</sup> VDD\_ARM\_IN and VDD\_SOC\_IN must be 125 mV higher than the LDO Output Set Point for correct regulator supply voltage.

<sup>4</sup> In LDO enabled mode, the internal LDO output set points must be configured such that the:

• VDD\_ARM LDO output set point does not exceed the VDD\_SOC LDO output set point by more than 100 mV.

• VDD\_SOC LDO output set point is equal to the VDD\_PU LDO output set point.

The VDD\_ARM LDO output set point can be lower than the VDD\_SOC LDO output set point, however, the minimum output set points shown in this table must be maintained.

- <sup>5</sup> When VDD\_SOC\_IN does not supply PCIE\_VP and PCIE\_VPTX, or when the PCIe PHY is not used, then this maximum can be 1.3 V.

- <sup>6</sup> Run mode: LDO Bypassed is not supported for the 1 GHz option.

- <sup>7</sup> In LDO bypassed mode, the external power supply must ensure that VDD\_ARM\_IN does not exceed VDD\_SOC\_IN by more than 100 mV. The VDD\_ARM\_IN supply voltage can be lower than the VDD\_SOC\_IN supply voltage. The minimum voltages shown in this table must be maintained.

- <sup>8</sup> While setting VDD\_SNVS\_IN voltage with respect to Charging Currents and RTC, refer to Hardware Development Guide for i.MX 6Dual, 6Quad, 6Solo, 6DualLite Families of Applications Processors (IMX6DQ6SDLHDG).

- <sup>9</sup> All digital I/O supplies (NVCC\_xxxx) must be powered under normal conditions whether the associated I/O pins are in use or not and associated IO pins need to have a pull-up or pull-down resistor applied to limit any non-connected gate current.

<sup>10</sup> This supply also powers the pre-drivers of the DDR IO pins, hence, it must be always provided, even when LVDS is not used.

# 4.1.4 External Clock Sources

Each i.MX 6Solo/6DualLite processor has two external input system clocks: a low frequency (RTC\_XTALI) and a high frequency (XTALI).

## Table 10. Maximum Supply Currents (continued)

| Power Line                | Conditions | Max Current                                                                                                                                        |    |  |  |

|---------------------------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----|--|--|

| NVCC_LVDS2P5 <sup>6</sup> | _          | NVCC_LVDS2P5 is connected to<br>VDD_HIGH_CAP at the board level.<br>VDD_HIGH_CAP is capable of<br>handing the current required by<br>NVCC_LVDS2P5. |    |  |  |

|                           | MISC       |                                                                                                                                                    |    |  |  |

| DDR_VREF                  |            | 1                                                                                                                                                  | mA |  |  |

The actual maximum current drawn from VDD\_HIGH\_IN will be as shown plus any additional current drawn from the VDD\_HIGH\_CAP outputs, depending upon actual application configuration (for example, NVCC\_LVDS\_2P5, NVCC\_MIPI, or HDMI and PCIe VPH supplies).

- <sup>2</sup> Under normal operating conditions, the maximum current on VDD\_SNVS\_IN is shown in Table 10. The maximum VDD\_SNVS\_IN current may be higher depending on specific operating configurations, such as BOOT\_MODE[1:0] not equal to 00, or use of the Tamper feature. During initial power on, VDD\_SNVS\_IN can draw up to 1 mA if the supply is capable of sourcing that current. If less than 1 mA is available, the VDD\_SNVS\_CAP charge time will increase.

- <sup>3</sup> This is the maximum current per active USB physical interface.

- <sup>4</sup> The DRAM power consumption is dependent on several factors, such as external signal termination. DRAM power calculators are typically available from the memory vendors. They take in account factors, such as signal termination. See the i.MX 6Solo/DualLite Power Consumption Measurement Application Note (AN4576) for examples of DRAM power consumption during specific use case scenarios.

- <sup>5</sup> General equation for estimated, maximum power consumption of an IO power supply:

- $Imax = N \times C \times V \times (0.5 \times F)$

Where:

1

- N—Number of IO pins supplied by the power line

- C—Equivalent external capacitive load

- V—IO voltage

- (0.5 xF)—Data change rate. Up to 0.5 of the clock rate (F)

- In this equation, Imax is in Amps, C in Farads, V in Volts, and F in Hertz.

- <sup>6</sup> NVCC\_LVDS2P5 is supplied by VDD\_HIGH\_CAP (by external connection) so the maximum supply current is included in the current shown for VDD\_HIGH\_IN. The maximum supply current for NVCC\_LVDS2P5 has not been characterized separately.

## 4.1.6 Low Power Mode Supply Currents

Table 11 shows the current core consumption (not including I/O) of i.MX 6Solo/6DualLite processors in selected low power modes.

| Mode | Test Conditions                                                                        | Supply             | Typical <sup>1</sup> | Units |

|------|----------------------------------------------------------------------------------------|--------------------|----------------------|-------|

| WAIT | • ARM, SoC, and PU LDOs are set to 1.225                                               | VDD_ARM_IN (1.4V)  | 4.5                  |       |

|      | HIGH LDO set to 2.5 V     Clocks are gated.                                            | VDD_SOC_IN (1.4V)  | 23                   | mA    |

|      | <ul> <li>DDR is in self refresh.</li> <li>PLLs are active in bypass (24MHz)</li> </ul> | VDD_HIGH_IN (3.0V) | 13.5                 |       |

|      | Supply Voltages remain ON                                                              | Total              | 79                   | mW    |

| Parameter                                                         | Symbol | Test Condition                                             | Min | Тур | Max                    | Unit |

|-------------------------------------------------------------------|--------|------------------------------------------------------------|-----|-----|------------------------|------|

| Output Pad Transition Times, rise/fall<br>(Max Drive, DSE=111)    | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 2.72/2.79<br>1.51/1.54 |      |

| Output Pad Transition Times, rise/fall<br>(High Drive, DSE=101)   | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 3.20/3.36<br>1.96/2.07 |      |

| Output Pad Transition Times, rise/fall<br>(Medium Drive, DSE=100) | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 3.64/3.88<br>2.27/2.53 | ns   |

| Output Pad Transition Times, rise/fall<br>(Low Drive. DSE=011)    | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 4.32/4.50<br>3.16/3.17 |      |

| Input Transition Times <sup>1</sup>                               | trm    |                                                            | _   | —   | 25                     | ns   |

## Table 29. General Purpose I/O AC Parameters 1.8 V Mode

<sup>1</sup> Hysteresis mode is recommended for inputs with transition times greater than 25 ns.

## Table 30. General Purpose I/O AC Parameters 3.3 V Mode

| Parameter                                                         | Symbol | Test Condition                                             | Min | Тур | Мах                    | Unit |

|-------------------------------------------------------------------|--------|------------------------------------------------------------|-----|-----|------------------------|------|

| Output Pad Transition Times, rise/fall<br>(Max Drive, DSE=101)    | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 1.70/1.79<br>1.06/1.15 |      |

| Output Pad Transition Times, rise/fall<br>(High Drive, DSE=011)   | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 2.35/2.43<br>1.74/1.77 | ns   |

| Output Pad Transition Times, rise/fall<br>(Medium Drive, DSE=010) | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 3.13/3.29<br>2.46/2.60 | 115  |

| Output Pad Transition Times, rise/fall<br>(Low Drive. DSE=001)    | tr, tf | 15 pF Cload, slow slew rate<br>15 pF Cload, fast slew rate | _   | _   | 5.14/5.57<br>4.77/5.15 |      |

| Input Transition Times <sup>1</sup>                               | trm    | _                                                          | —   | —   | 25                     | ns   |

<sup>1</sup> Hysteresis mode is recommended for inputs with transition times greater than 25 ns.

# 4.7.2 DDR I/O AC Parameters

Table 31 shows the AC parameters for DDR I/O operating in LPDDR2 mode. For details on supported DDR memory configurations, see Section 4.9.4, "Multi-Mode DDR Controller (MMDC).

Table 31. DDR I/O LPDDR2 Mode AC Parameters<sup>1</sup>

| Parameter                                              | Symbol   | Test Condition   | Min         | Max         | Unit |

|--------------------------------------------------------|----------|------------------|-------------|-------------|------|

| AC input logic high                                    | Vih(ac)  | —                | Vref + 0.22 | OVDD        | V    |

| AC input logic low                                     | Vil(ac)  | —                | 0           | Vref - 0.22 | V    |

| AC differential input high voltage <sup>2</sup>        | Vidh(ac) | —                | 0.44        | _           | V    |

| AC differential input low voltage                      | Vidl(ac) | —                | _           | 0.44        | V    |

| Input AC differential cross point voltage <sup>3</sup> | Vix(ac)  | Relative to Vref | -0.12       | 0.12        | V    |

| Over/undershoot peak                                   | Vpeak    | —                | —           | 0.35        | V    |

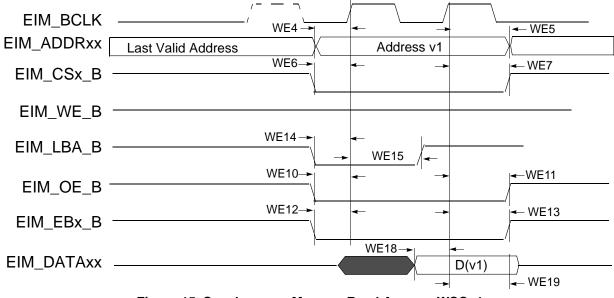

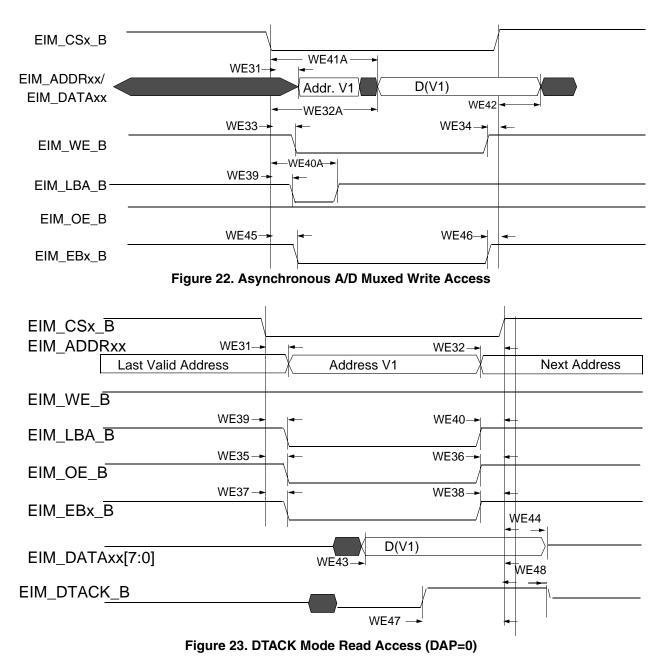

- <sup>1</sup> t is the maximum EIM logic (ACLK\_EXSC) cycle time. The maximum allowed axi\_clk frequency depends on the fixed/non-fixed latency configuration, whereas the maximum allowed EIM\_BCLK frequency is:

- -Fixed latency for both read and write is 104 MHz.

- -Variable latency for read only is 104 MHz.

- -Variable latency for write only is 52 MHz.

- In variable latency configuration for write, if BCD = 0 & WBCDD = 1 or BCD = 1, axi\_clk must be 104 MHz.Write BCD = 1 and 104 MHz ACLK\_EXSC, will result in a EIM\_BCLK of 52 MHz. When the clock branch to EIM is decreased to 104 MHz, other buses are impacted which are clocked from this source. See the CCM chapter of the *i.MX* 6Solo/6DualLite Reference Manual (*IMX*6SDLRM) for a detailed clock tree description.

- <sup>2</sup> EIM\_BCLK parameters are being measured from the 50% point, that is, high is defined as 50% of signal value and low is defined as 50% as signal value.

- <sup>3</sup> For signal measurements, "High" is defined as 80% of signal value and "Low" is defined as 20% of signal value.

Figure 15 to Figure 18 provide few examples of basic EIM accesses to external memory devices with the timing parameters mentioned previously for specific control parameters settings.

Figure 15. Synchronous Memory Read Access, WSC=1

| ID              | Characteristic                           | Min | Мах | Unit               |

|-----------------|------------------------------------------|-----|-----|--------------------|

| M9 <sup>1</sup> | ENET_CRS to ENET_COL minimum pulse width | 1.5 | _   | ENET_TX_CLK period |

<sup>1</sup> ENET\_COL has the same timing in 10-Mbit 7-wire interface mode.

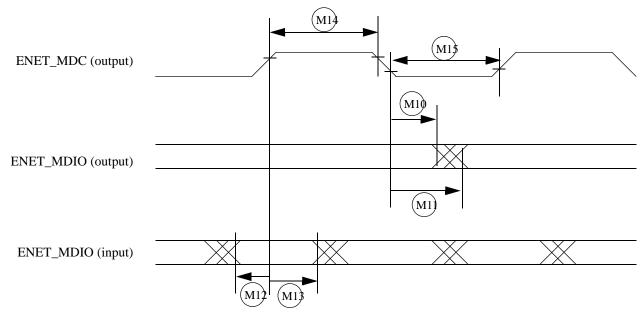

## 4.11.5.1.4 MII Serial Management Channel Timing (ENET\_MDIO and ENET\_MDC)

The MDC frequency is designed to be equal to or less than 2.5 MHz to be compatible with the IEEE 802.3 MII specification. However the ENET can function correctly with a maximum MDC frequency of 15 MHz.

Figure 46 shows MII asynchronous input timings. Table 58 describes the timing parameters (M10–M15) shown in the figure.

Figure 46. MII Serial Management Channel Timing Diagram

| Table 58. MII Serial Management Channel Tir | ning |

|---------------------------------------------|------|

|---------------------------------------------|------|

| ID  | Characteristic                                                             | Min | Max | Unit            |

|-----|----------------------------------------------------------------------------|-----|-----|-----------------|

| M10 | ENET_MDC falling edge to ENET_MDIO output invalid (min. propagation delay) | 0   | _   | ns              |

| M11 | ENET_MDC falling edge to ENET_MDIO output valid (max. propagation delay)   | _   | 5   | ns              |

| M12 | ENET_MDIO (input) to ENET_MDC rising edge setup                            | 18  | —   | ns              |

| M13 | ENET_MDIO (input) to ENET_MDC rising edge hold                             | 0   | —   | ns              |

| M14 | ENET_MDC pulse width high                                                  | 40% | 60% | ENET_MDC period |

| M15 | ENET_MDC pulse width low                                                   | 40% | 60% | ENET_MDC period |

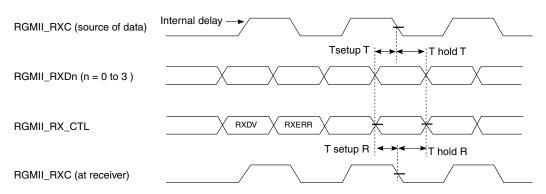

Figure 50. RGMII Receive Signal Timing Diagram with Internal Delay

# 4.11.6 Flexible Controller Area Network (FLEXCAN) AC Electrical Specifications

The Flexible Controller Area Network (FlexCAN) module is a communication controller implementing the CAN protocol according to the CAN 2.0B protocol specification. The processor has two CAN modules available for systems design. Tx and Rx ports for both modules are multiplexed with other I/O pins. See the IOMUXC chapter of the *i.MX 6Solo/6DualLite Reference Manual (IMX6SDLRM)* to see which pins expose Tx and Rx pins; these ports are named FLEXCAN\_TX and FLEXCAN\_RX, respectively.

# 4.11.7 HDMI Module Timing Parameters

## 4.11.7.1 Latencies and Timing Information

Power-up time (time between TX\_PWRON assertion and TX\_READY assertion) for the HDMI 3D Tx PHY while operating with the slowest input reference clock supported (13.5 MHz) is 3.35 ms.

Power-up time for the HDMI 3D Tx PHY while operating with the fastest input reference clock supported (340 MHz) is 133  $\mu$ s.

# 4.11.7.2 Electrical Characteristics

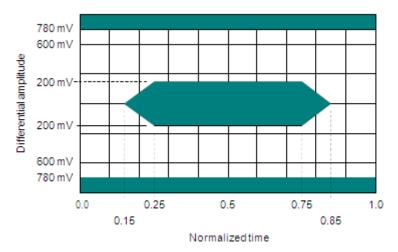

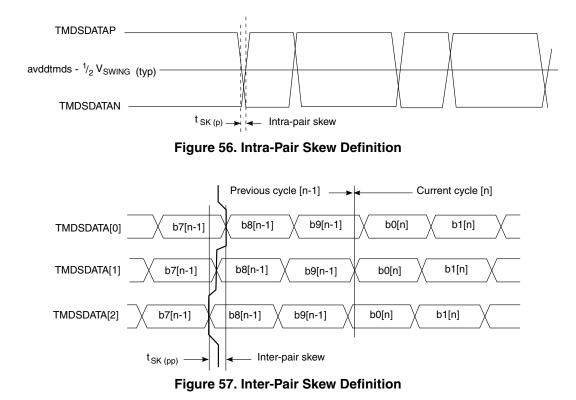

The table below provides electrical characteristics for the HDMI 3D Tx PHY. The following three figures illustrate various definitions and measurement conditions specified in the table below.

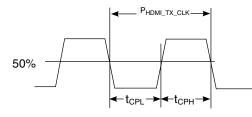

Figure 54. TMDS Clock Signal Definitions

Figure 55. Eye Diagram Mask Definition for HDMI Driver Signal Specification at TP1

i.MX 6Solo/6DualLite Automotive and Infotainment Applications Processors, Rev. 8, 09/2017

## 4.11.10.2.2 Gated Clock Mode

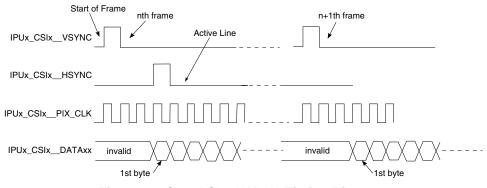

The IPUx\_CSIx\_VSYNC, IPUx\_CSIx\_HSYNC, and IPUx\_CSIx\_PIX\_CLK signals are used in this mode. See Figure 60.

Figure 60. Gated Clock Mode Timing Diagram

A frame starts with a rising edge on IPUx\_CSIx\_VSYNC (all the timings correspond to straight polarity of the corresponding signals). Then IPUx\_CSIx\_HSYNC goes to high and hold for the entire line. Pixel clock is valid as long as IPUx\_CSIx\_HSYNC is high. Data is latched at the rising edge of the valid pixel clocks. IPUx\_CSIx\_HSYNC goes to low at the end of line. Pixel clocks then become invalid and the CSI stops receiving data from the stream. For the next line, the IPUx\_CSIx\_HSYNC timing repeats. For the next frame, the IPUx\_CSIx\_VSYNC timing repeats.

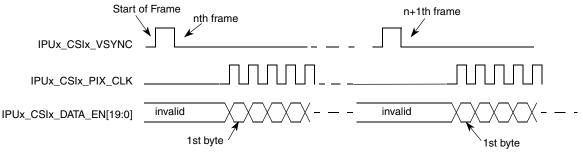

## 4.11.10.2.3 Non-Gated Clock Mode

The timing is the same as the gated-clock mode (described in Section 4.11.10.2.2, "Gated Clock Mode,") except for the IPUx\_CSIx\_HSYNC signal, which is not used (see Figure 61). All incoming pixel clocks are valid and cause data to be latched into the input FIFO. The IPUx\_CSIx\_PIX\_CLK signal is inactive (states low) until valid data is going to be transmitted over the bus.

Figure 61. Non-Gated Clock Mode Timing Diagram

The timing described in Figure 61 is that of a typical sensor. Some other sensors may have a slightly different timing. The CSI can be programmed to support rising/falling-edge triggered IPUx\_CSIx\_VSYNC; active-high/low IPUx\_CSIx\_HSYNC; and rising/falling-edge triggered IPUx\_CSIx\_PIX\_CLK.

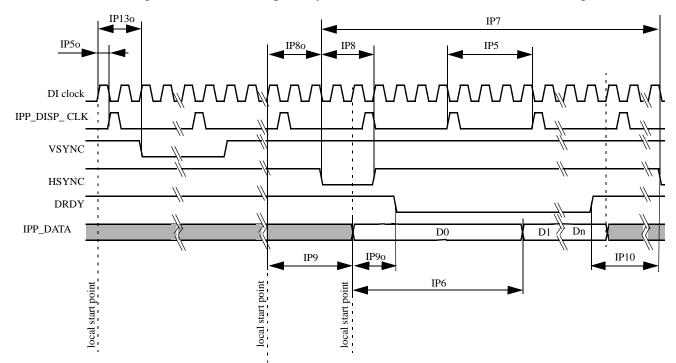

corresponding internal events—local start points. The timing diagrams correspond to inverse polarity of the IPP\_DISP\_CLK signal and active-low polarity of the HSYNC, VSYNC, and DRDY signals.

Figure 64. TFT Panels Timing Diagram—Horizontal Sync Pulse

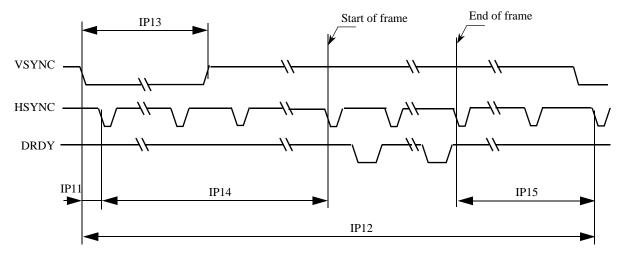

Figure 65 depicts the vertical timing (timing of one frame). All parameters shown in the figure are programmable.

Figure 65. TFT Panels Timing Diagram—Vertical Sync Pulse

# 4.11.11 LVDS Display Bridge (LDB) Module Parameters

The LVDS interface complies with TIA/EIA 644-A standard. For more details, see TIA/EIA STANDARD 644-A, "*Electrical Characteristics of Low Voltage Differential Signaling (LVDS) Interface Circuits*".

| Parameter                           | Symbol              | Test Condition                                                                                                                                     | Min  | Max   | Units |

|-------------------------------------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|-------|

| Differential Voltage Output Voltage | V <sub>OD</sub>     | 100 $\Omega$ Differential load                                                                                                                     | 250  | 450   | mV    |

| Output Voltage High                 | Voh                 | 100 $\Omega$ differential load (0 V Diff—Output High Voltage static)                                                                               | 1.25 | 1.6   | V     |

| Output Voltage Low                  | Vol                 | 100 $\Omega$ differential load (0 V Diff—Output Low Voltage static)                                                                                | 0.9  | 1.25  | V     |

| Offset Static Voltage               | V <sub>OS</sub>     | Two 49.9 $\Omega$ resistors in series between N-P terminal, with output in either Zero or One state, the voltage measured between the 2 resistors. | 1.15 | 1.375 | V     |

| VOS Differential                    | V <sub>OSDIFF</sub> | Difference in $V_{\mbox{\scriptsize OS}}$ between a One and a Zero state                                                                           | -50  | 50    | mV    |

| Output short circuited to GND       | ISA ISB             | With the output common shorted to GND                                                                                                              | -24  | 24    | mA    |

| VT Full Load Test                   | VTLoad              | 100 $\Omega$ Differential load with a 3.74 k $\Omega$ load between GND and IO Supply Voltage                                                       | 247  | 454   | mV    |

Table 69. LVDS Display Bridge (LDB) Electrical Specification

# 4.11.12 MIPI D-PHY Timing Parameters

This section describes MIPI D-PHY electrical specifications, compliant with MIPI CSI-2 version 1.0, D-PHY specification Rev. 1.0 (for MIPI sensor port x2 lanes) and MIPI DSI Version 1.01, and D-PHY specification Rev. 1.0 (and also DPI version 2.0, DBI version 2.0, DSC version 1.0a at protocol layer) (for MIPI display port x2 lanes).

# 4.11.12.1 Electrical and Timing Information

| Symbol                  | Parameters                                                                              | Test Conditions                                                                         | Min | Тур | Мах  | Unit |  |  |  |  |  |  |  |

|-------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|-----|-----|------|------|--|--|--|--|--|--|--|

| Input                   | Input DC Specifications - Apply to DSI_CLK_P/DSI_CLK_N and DSI_DATA_P/DSI_DATA_N inputs |                                                                                         |     |     |      |      |  |  |  |  |  |  |  |

| VI                      | Input signal voltage range                                                              | Transient voltage range is<br>limited from -300 mV to<br>1600 mV                        | -50 | _   | 1350 | mV   |  |  |  |  |  |  |  |

| V <sub>LEAK</sub>       | Input leakage current                                                                   | VGNDSH(min) = VI =<br>VGNDSH(max) +<br>VOH(absmax)<br>Lane module in LP Receive<br>Mode | -10 |     | 10   | mA   |  |  |  |  |  |  |  |

| V <sub>GNDSH</sub>      | Ground Shift                                                                            | —                                                                                       | -50 | —   | 50   | mV   |  |  |  |  |  |  |  |

| V <sub>OH(absmax)</sub> | Maximum transient output voltage level                                                  | _                                                                                       | —   | —   | 1.45 | V    |  |  |  |  |  |  |  |

Table 70. Electrical and Timing Information

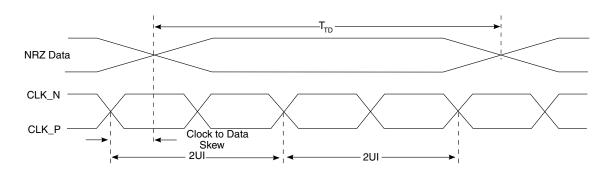

## 4.11.12.8 Reverse High-Speed Data Transmission Timing

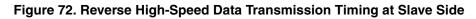

## 4.11.12.9 Low-Power Receiver Timing

Figure 73. Input Glitch Rejection of Low-Power Receivers

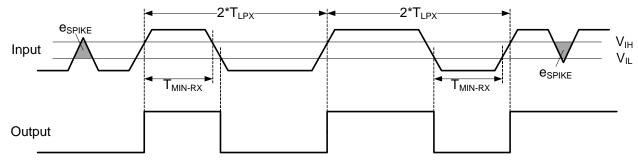

# 4.11.13 HSI Host Controller Timing Parameters

This section describes the timing parameters of the HSI Host Controller which are compliant with High-speed Synchronous Serial Interface (HSI) Physical Layer specification version1.01.

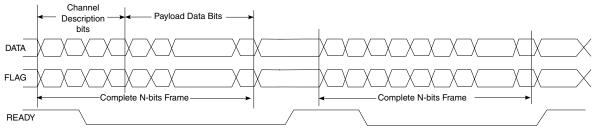

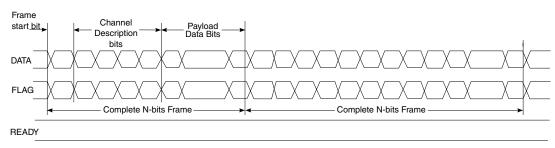

# 4.11.13.1 Synchronous Data Flow

Figure 74. Synchronized Data Flow READY Signal Timing (Frame and Stream Transmission)

## 4.11.13.5 Stream Transmission Mode Frame Transfer

Figure 78. Stream Transmission Mode Frame Transfer (Synchronized Data Flow)

# 4.11.13.6 Frame Transmission Mode (Synchronized Data Flow)

Figure 79. Frame Transmission Mode Transfer of Two Frames (Synchronized Data Flow)

# 4.11.13.7 Frame Transmission Mode (Pipelined Data Flow)

Figure 80. Frame Transmission Mode Transfer of Two Frames (Pipelined Data Flow)

# 4.11.13.8 DATA and FLAG Signal Timing Requirement for a 15 pF Load

## Table 72. DATA and FLAG Timing

| Parameter                                            | Description                                                | 1 Mbit/s | 100 Mbit/s | 200 Mbit/s |

|------------------------------------------------------|------------------------------------------------------------|----------|------------|------------|

| t <sub>Bit, nom</sub>                                | Nominal bit time                                           | 1000 ns  | 10.0 ns    | 5.00 ns    |

| t <sub>Rise, min</sub> and<br>t <sub>Fall, min</sub> | Minimum allowed rise and fall time                         | 2.00 ns  | 2.00 ns    | 1.00 ns    |

| t <sub>TxToRxSkew</sub> , maxfq                      | Maximum skew between transmitter and receiver package pins | 50.0 ns  | 0.5.0 ns   | 0.25 ns    |

| Parameter                                                                        | Symbol             | Min | Мах   | Unit | Comment |

|----------------------------------------------------------------------------------|--------------------|-----|-------|------|---------|

| MLB_SIG/MLB_DATA output valid from transition of MLB_CLK (low to high)           | t <sub>delay</sub> | —   | 10    | ns   | _       |

| Transmitter MLBSIG (MLBDAT) output valid from transition of MLBCLK (low-to-high) | t <sub>delay</sub> | —   | 10.75 | ns   | _       |

<sup>1</sup> The controller can shut off MLB\_CLK to place MediaLB in a low-power state. Depending on the time the clock is shut off, a runt pulse can occur on MLB\_CLK.

<sup>2</sup> MLB\_CLK low/high time includes the pulse width variation.

<sup>3</sup> The MediaLB driver can release the MLB\_DATA/MLB\_SIG line as soon as MLB\_CLK is low; however, the logic state of the final driven bit on the line must remain on the bus for t<sub>mdzh</sub>. Therefore, coupling must be minimized while meeting the maximum load capacitance listed.

Ground = 0.0 V; load capacitance = 40 pF; MediaLB speed = 1024 Fs; Fs = 48 kHz; all timing parameters specified from the valid voltage threshold as listed in Table 76; unless otherwise noted.

| Parameter                                                                        | Symbol             | Min               | Max               | Unit | Comment                                    |

|----------------------------------------------------------------------------------|--------------------|-------------------|-------------------|------|--------------------------------------------|

| MLB_CLK Operating Frequency <sup>1</sup>                                         | f <sub>mck</sub>   | 45.056            | 51.2              | MHz  | 1024xfs at 44.0 kHz<br>1024xfs at 50.0 kHz |

| MLB_CLK rise time                                                                | t <sub>mckr</sub>  | —                 | 1                 | ns   | V <sub>IL</sub> TO V <sub>IH</sub>         |

| MLB_CLK fall time                                                                | t <sub>mckf</sub>  | —                 | 1                 | ns   | V <sub>IH</sub> TO V <sub>IL</sub>         |

| MLB_CLK low time                                                                 | t <sub>mckl</sub>  | 6.1               | —                 | ns   | 2                                          |

| MLB_CLK high time                                                                | t <sub>mckh</sub>  | 9.3               | —                 | ns   | —                                          |

| MLB_SIG/MLB_DATA receiver input valid to MLB_CLK falling                         | t <sub>dsmcf</sub> | 1                 | —                 | ns   | —                                          |

| MLB_SIG/MLB_DATA receiver input hold<br>from MLB_CLK low                         | t <sub>dhmcf</sub> | t <sub>mdzh</sub> | —                 | ns   | —                                          |

| MLB_SIG/MLB_DATA output high<br>impedance from MLB_CLK low                       | t <sub>mcfdz</sub> | 0                 | t <sub>mckl</sub> | ns   | 3                                          |

| Bus Hold from MLB_CLK low                                                        | t <sub>mdzh</sub>  | 2                 | —                 | ns   | —                                          |

| MLB_SIG/MLB_DATA output valid from transition of MLB_CLK (low to high)           | t <sub>delay</sub> |                   | 7                 | ns   | —                                          |

| Transmitter MLBSIG (MLBDAT) output valid from transition of MLBCLK (low-to-high) | t <sub>delay</sub> | —                 | 6                 | ns   | —                                          |

Table 76. MLB 1024 Fs Timing Parameters

The controller can shut off MLB\_CLK to place MediaLB in a low-power state. Depending on the time the clock is shut off, a runt pulse can occur on MLB\_CLK.

<sup>2</sup> MLB\_CLK low/high time includes the pulse width variation.

<sup>3</sup> The MediaLB driver can release the MLB\_DATA/MLB\_SIG line as soon as MLB\_CLK is low; however, the logic state of the final driven bit on the line must remain on the bus for t<sub>mdzh</sub>. Therefore, coupling must be minimized while meeting the maximum load capacitance listed.

Table 77 lists the MediaLB 6-pin interface timing characteristics, and Figure 83 shows the MLB 6-pin delay, setup, and hold times.

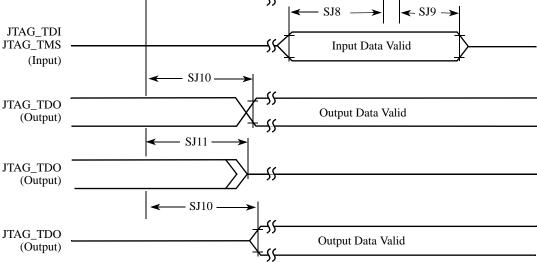

Figure 87. Test Access Port Timing Diagram

| ID   | Parameter                                      | Min  | Max  | Unit |  |  |  |  |  |  |  |  |

|------|------------------------------------------------|------|------|------|--|--|--|--|--|--|--|--|

|      | External Clock Operation                       |      |      |      |  |  |  |  |  |  |  |  |

| SS22 | AUDx_TXC/AUDx_RXC clock period                 | 81.4 | —    | ns   |  |  |  |  |  |  |  |  |

| SS23 | AUDx_TXC/AUDx_RXC clock high period            | 36   | —    | ns   |  |  |  |  |  |  |  |  |

| SS24 | AUDx_TXC/AUDx_RXC clock rise time              | —    | 6.0  | ns   |  |  |  |  |  |  |  |  |

| SS25 | AUDx_TXC/AUDx_RXC clock low period             | 36   | —    | ns   |  |  |  |  |  |  |  |  |

| SS26 | AUDx_TXC/AUDx_RXC clock fall time              | —    | 6.0  | ns   |  |  |  |  |  |  |  |  |

| SS28 | AUDx_RXC high to AUDx_TXFS (bl) high           | -10  | 15.0 | ns   |  |  |  |  |  |  |  |  |

| SS30 | AUDx_RXC high to AUDx_TXFS (bl) low            | 10   | —    | ns   |  |  |  |  |  |  |  |  |

| SS32 | AUDx_RXC high to AUDx_TXFS (wl) high           | -10  | 15.0 | ns   |  |  |  |  |  |  |  |  |

| SS34 | AUDx_RXC high to AUDx_TXFS (wl) low            | 10   | —    | ns   |  |  |  |  |  |  |  |  |

| SS35 | AUDx_TXC/AUDx_RXC External AUDx_TXFS rise time | —    | 6.0  | ns   |  |  |  |  |  |  |  |  |

| SS36 | AUDx_TXC/AUDx_RXC External AUDx_TXFS fall time | —    | 6.0  | ns   |  |  |  |  |  |  |  |  |

| SS40 | AUDx_RXD setup time before AUDx_RXC low        | 10   | —    | ns   |  |  |  |  |  |  |  |  |

| SS41 | AUDx_RXD hold time after AUDx_RXC low          | 2    | —    | ns   |  |  |  |  |  |  |  |  |

## Table 85. SSI Receiver Timing with External Clock

## NOTE

- All the timings for the SSI are given for a non-inverted serial clock polarity (TSCKP/RSCKP = 0) and a non-inverted frame sync (TFSI/RFSI = 0). If the polarity of the clock and/or the frame sync have been inverted, all the timing remains valid by inverting the clock signal AUDx\_TXC/AUDx\_RXC and/or the frame sync AUDx\_TXFS/AUDx\_RXFS shown in the tables and in the figures.

- All timings are on Audiomux Pads when SSI is being used for data transfer.

- The terms, WL and BL, refer to Word Length (WL) and Bit Length (BL).

- For internal Frame Sync operation using external clock, the frame sync timing is same as that of transmit data (for example, during AC97 mode of operation).

## Package Information and Contact Assignments

|                           |      |             |           | Out of Reset Condition <sup>1</sup> |                  |                  |                          |  |  |  |  |

|---------------------------|------|-------------|-----------|-------------------------------------|------------------|------------------|--------------------------|--|--|--|--|

| Ball Name                 | Ball | Power Group | Ball Type | Default<br>Mode<br>(Reset<br>Mode)  | Default Function | Input/<br>Output | Value <sup>2</sup>       |  |  |  |  |

| EIM_EB1                   | K23  | NVCC_EIM    | GPIO      | ALT0                                | EIM_EB1          | Output           | High                     |  |  |  |  |

| EIM_EB2                   | E22  | NVCC_EIM    | GPIO      | ALT5                                | GPIO2_IO30       | Input            | 100 kΩ pull-up           |  |  |  |  |

| EIM_EB3                   | F23  | NVCC_EIM    | GPIO      | ALT5                                | GPIO2_IO31       | Input            | 100 kΩ pull-up           |  |  |  |  |

| EIM_LBA                   | K22  | NVCC_EIM    | GPIO      | ALT0                                | EIM_LBA          | Output           | High                     |  |  |  |  |

| EIM_OE                    | J24  | NVCC_EIM    | GPIO      | ALT0                                | EIM_OE           | Output           | High                     |  |  |  |  |

| EIM_RW                    | K20  | NVCC_EIM    | GPIO      | ALT0                                | EIM_RW           | Output           | High                     |  |  |  |  |

| EIM_WAIT                  | M25  | NVCC_EIM    | GPIO      | ALT0                                | EIM_WAIT         | Input            | 100 kΩ pull-up           |  |  |  |  |

| ENET_CRS_DV               | U21  | NVCC_ENET   | GPIO      | ALT5                                | GPIO1_IO25       | Input            | 100 kΩ pull-up           |  |  |  |  |

| ENET_MDC                  | V20  | NVCC_ENET   | GPIO      | ALT5                                | GPIO1_IO31       | Input            | 100 kΩ pull-up           |  |  |  |  |

| ENET_MDIO                 | V23  | NVCC_ENET   | GPIO      | ALT5                                | GPIO1_IO22       | Input            | 100 kΩ pull-up           |  |  |  |  |

| ENET_REF_CLK <sup>3</sup> | V22  | NVCC_ENET   | GPIO      | ALT5                                | GPIO1_IO23       | Input            | 100 kΩ pull-up           |  |  |  |  |

| ENET_RX_ER                | W23  | NVCC_ENET   | GPIO      | ALT5                                | GPIO1_IO24       | Input            | 100 kΩ pull-up           |  |  |  |  |

| ENET_RXD0                 | W21  | NVCC_ENET   | GPIO      | ALT5                                | GPIO1_IO27       | Input            | 100 kΩ pull-up           |  |  |  |  |

| ENET_RXD1                 | W22  | NVCC_ENET   | GPIO      | ALT5                                | GPIO1_IO26       | Input            | 100 kΩ pull-up           |  |  |  |  |

| ENET_TX_EN                | V21  | NVCC_ENET   | GPIO      | ALT5                                | GPIO1_IO28       | Input            | 100 kΩ pull-up           |  |  |  |  |

| ENET_TXD0                 | U20  | NVCC_ENET   | GPIO      | ALT5 GPIO1_IO30                     |                  | Input            | 100 kΩ pull-up           |  |  |  |  |

| ENET_TXD1                 | W20  | NVCC_ENET   | GPIO      | ALT5                                | GPIO1_IO29       | Input            | 100 kΩ pull-up           |  |  |  |  |

| GPIO_0                    | T5   | NVCC_GPIO   | GPIO      | ALT5                                | GPIO1_IO00       | Input            | 100 k $\Omega$ pull-down |  |  |  |  |

| GPIO_1                    | T4   | NVCC_GPIO   | GPIO      | ALT5                                | GPIO1_IO01       | Input            | 100 kΩ pull-up           |  |  |  |  |

| GPIO_16                   | R2   | NVCC_GPIO   | GPIO      | ALT5                                | GPIO7_IO11       | Input            | 100 kΩ pull-up           |  |  |  |  |

| GPIO_17                   | R1   | NVCC_GPIO   | GPIO      | ALT5                                | GPIO7_IO12       | Input            | 100 kΩ pull-up           |  |  |  |  |

| GPIO_18                   | P6   | NVCC_GPIO   | GPIO      | ALT5                                | GPIO7_IO13       | Input            | 100 kΩ pull-up           |  |  |  |  |

| GPIO_19                   | P5   | NVCC_GPIO   | GPIO      | ALT5                                | GPIO4_IO05       | Input            | 100 kΩ pull-up           |  |  |  |  |

| GPIO_2                    | T1   | NVCC_GPIO   | GPIO      | ALT5                                | GPIO1_IO02       | Input            | 100 kΩ pull-up           |  |  |  |  |

| GPIO_3                    | R7   | NVCC_GPIO   | GPIO      | ALT5                                | GPIO1_IO03       | Input            | 100 kΩ pull-up           |  |  |  |  |

| GPIO_4                    | R6   | NVCC_GPIO   | GPIO      | ALT5                                | GPIO1_IO04       | Input            | 100 kΩ pull-up           |  |  |  |  |

| GPIO_5                    | R4   | NVCC_GPIO   | GPIO      | ALT5                                | GPIO1_IO05       | Input            | 100 kΩ pull-up           |  |  |  |  |

| GPIO_6                    | Т3   | NVCC_GPIO   | GPIO      | ALT5                                | GPIO1_IO06       | Input            | 100 kΩ pull-up           |  |  |  |  |

| GPIO_7                    | R3   | NVCC_GPIO   | GPIO      | ALT5                                | GPIO1_IO07       | Input            | 100 k $\Omega$ pull-up   |  |  |  |  |

| GPIO_8                    | R5   | NVCC_GPIO   | GPIO      | ALT5                                | GPIO1_IO08       | Input            | 100 k $\Omega$ pull-up   |  |  |  |  |

| GPIO_9                    | T2   | NVCC_GPIO   | GPIO      | ALT5                                | GPIO1_IO09       | Input            | 100 k $\Omega$ pull-up   |  |  |  |  |

| HDMI_CLKM                 | J5   | HDMI        | —         | _                                   | HDMI_TX_CLK_N    | -                | —                        |  |  |  |  |

| HDMI_CLKP                 | J6   | HDMI        | —         | _                                   | HDMI_TX_CLK_P    | —                | —                        |  |  |  |  |

| HDMI_D0M                  | K5   | HDMI        | —         | _                                   | HDMI_TX_DATA0_N  | —                | _                        |  |  |  |  |

| HDMI_D0P                  | K6   | HDMI        | —         | _                                   | HDMI_TX_DATA0_P  | —                | _                        |  |  |  |  |

| HDMI_D1M                  | JЗ   | HDMI        | —         | _                                   | HDMI_TX_DATA1_N  | —                | —                        |  |  |  |  |

Table 97. 21 x 21 mm Functional Contact Assignments (continued)

## Package Information and Contact Assignments

| Table 100. 21 x 21 mm, 0.8 mm Pitch Ball Map i.MX 6DualLite (continued) |

|-------------------------------------------------------------------------|

|-------------------------------------------------------------------------|

|   | -           | 2           | ო            | 4           | 5         | 9          | 2            | 8        | 6         | 10         | ÷           | 12        | 13         | 14         | 15         | 16        | 17        | 18        | 19           | 20          | 21          | 22           | 23          | 24          | 25          |   |

|---|-------------|-------------|--------------|-------------|-----------|------------|--------------|----------|-----------|------------|-------------|-----------|------------|------------|------------|-----------|-----------|-----------|--------------|-------------|-------------|--------------|-------------|-------------|-------------|---|

| z | CSI0_DAT4   | CSI0_VSYNC  | CSI0_DAT7    | CSI0_DAT6   | CSI0_DAT9 | CSI0_DAT8  | NVCC_CSI     | GND      | VDDARM_IN | GND        | VDDARM_CAP  | NC        | VDDARM_CAP | VDDARM_IN  | GND        | VDDSOC_IN | VDDPU_CAP | GND       | DI0_DISP_CLK | DI0_PIN3    | DI0_PIN15   | EIM_BCLK     | EIM_DA14    | EIM_DA15    | DIO_PIN2    | Z |

| ٩ | CSI0_PIXCLK | CSI0_DAT5   | CSI0_DATA_EN | CSI0_MCLK   | GPIO_19   | GPIO_18    | NVCC_GPIO    | GND      | VDDARM_IN | GND        | VDDARM_CAP  | GND       | VDDARM_CAP | VDDARM_IN  | GND        |           | VDDPU_CAP | GND       | NVCC_LCD     | DISP0_DAT4  | DISP0_DAT3  | DISP0_DAT1   | DISP0_DAT2  | DISP0_DAT0  | DI0_PIN4    | ٩ |

| œ | GPI0_17     | GPIO_16     | GPIO_7       | GPIO_5      | GPIO_8    | GPIO_4     | GPIO_3       | GND      | VDDARM_IN | VDDSOC_CAP | VDDARM_CAP  | GND       | VDDARM_CAP | VDDARM_IN  | GND        | VDDSOC_IN | GND       | NVCC_DRAM | NVCC_ENET    | DISP0_DAT13 | DISP0_DAT10 | DISP0_DAT8   | DISP0_DAT6  | DISP0_DAT7  | DISP0_DAT5  | æ |

| F | GPIO_2      | GPIO_9      | GPIO_6       | GPIO_1      | GPIO_0    | KEY_COL4   | KEY_ROW3     | GND      | VDDARM_IN | VDDSOC_CAP | GND         | GND       | VDDSOC_CAP | VDDSOC_CAP | GND        | VDDSOC_IN | GND       | NVCC_DRAM | GND          | DISP0_DAT21 | DISP0_DAT16 | DISP0_DAT15  | DISP0_DAT11 | DISP0_DAT12 | DISP0_DAT9  | Т |

| 5 | LVDS0_TX0_P | LVDS0_TX0_N | LVDS0_TX1_P  | LVDS0_TX1_N | KEY_COL3  | KEY_ROW1   | KEY_COL1     | GND      | VDDARM_IN | VDDSOC_CAP | GND         | GND       | VDDSOC_CAP | VDDSOC_CAP | GND        | VDDSOC_IN | GND       | NVCC_DRAM | GND          | ENET_TXD0   | ENET_CRS_DV | DISP0_DAT20  | DISP0_DAT19 | DISP0_DAT17 | DISP0_DAT14 | n |

| > | LVDS0_TX2_P | LVDS0_TX2_N | LVDS0_CLK_P  | LVDS0_CLK_N | KEY_ROW4  | KEY_ROW0   | NVCC_LVDS2P5 | GND      | NVCC_DRAM | NVCC_DRAM  | NVCC_DRAM   | NVCC_DRAM | NVCC_DRAM  | NVCC_DRAM  | NVCC_DRAM  | NVCC_DRAM | NVCC_DRAM | NVCC_DRAM | GND          | ENET_MDC    | ENET_TX_EN  | ENET_REF_CLK | ENET_MDIO   | DISP0_DAT22 | DISP0_DAT18 | v |

| N | LVDS0_TX3_P | LVDS0_TX3_N | GND          | KEY_ROW2    | KEY_COL0  | KEY_COL2   | GND          | GND      | GND       | GND        | GND         | GND       | GND        | DRAM_A4    | GND        | GND       | GND       | GND       | GND          | ENET_TXD1   | ENET_RXD0   | ENET_RXD1    | ENET_RX_ER  | DISP0_DAT23 | DRAM_D63    | M |

| ٨ | LVDS1_TX0_N | LVDS1_TX0_P | LVDS1_CLK_N  | LVDS1_CLK_P | GND       | DRAM_RESET | DRAM_D20     | DRAM_D21 | DRAM_D19  | DRAM_D25   | DRAM_SDCKE0 | DRAM_A15  | DRAM_A7    | DRAM_A3    | DRAM_SDBA1 | DRAM_CS0  | DRAM_D36  | DRAM_D37  | DRAM_D40     | DRAM_D44    | DRAM_DQM7   | DRAM_D59     | DRAM_D62    | GND         | DRAM_D58    | ٨ |

## **Revision History**

| Per l          |         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev.<br>Number | Date    | Substantive Changes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Rev. 4         | 12/2014 | <ul> <li>Table 1, "Example Orderable Part Numbers," on page 3: Speed Grade footnote added as follows:</li> <li>"If a 24 MHz input clock is used (required for USB), the maximum SoC speed is limited to 792 MHz."</li> <li>Figure 1, "Part Number Nomenclature—I.MX 65olo and 6DualLite". Added Silicon Rev 1.3. to diagram</li> <li>Table 2, Modules List, UART 1–5 Description changed: baud rate up from 5MHz to 5Mbps.</li> <li>Added Figure 2, "Example Part Marking," on page 5.</li> <li>Section 1.2, "Features": under, <i>Miscellaneous IPs and interfaces</i>: Changed <i>UARTs</i> bullet, from "up to 4.0 Mbps", to "up to 5.0 Mbps".</li> <li>Table 8, "Operating Ranges," on page 29:</li> <li>— Changed <i>Run mode</i>: VDD_ARM_IN minimum value from 1.05 to 1.125V; for operation up to 396 MHz, and changed <i>LD0 bypassed</i> maximu value from 1.225V to 1.21V; for VDD_SOC_IN.</li> <li>— Changed <i>PCle supply voltages</i>; <i>PClE_VP/PCIE_VPTX</i> maximum value from 1.225V to 1.21V</li> <li>Table 10, "Maximum Supply Currents," on page 29;</li> <li>— Changed VDD_ARM_INfrom single condition to include DualLite and Solo conditions with Maximum current values of 2200 and 1320 mA, respectively.</li> <li>— Added footnote for NVCC_LVDS2PS supply.</li> <li>Table 38, "Reset Timing Parameters": Removed footnote regarding SRC_POR_B rise and fall times.</li> <li>Section 4.9.3, "External Interface Module (EIM)": Changed first paragraph to describe two systems clocks used with EIM: ACLK_EIM_SLOW_CLK_ROVT and ACLK_EXSC (for synchronous mode).</li> <li>Table 48, "DDR3/DDR3L Mode AC Parameters": Added footnote ava or base; changed minimum parameter values for DDR4-DDR7. Added footnote about 15 and 14 th base values.</li> <li>Figure 25, "DDR3 Command and Address Timing Parameters", on page 76; Added DDR0.</li> <li>Table 49, "DDR3/DDR3L Mode AC Parameters", Added footnote seqarding the system clocks used with EIM: from ax_c/k to ACLK_EXSC or ACLK_EXSC to 0.761.7.</li> <li>Table 49, "DDR3/DDR3L Write Cycle,"</li></ul> |

## Table 102. i.MX 6Solo/6DualLite Data Sheet Document Past Revision Histories (continued)