Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                              |

|----------------------------|------------------------------------------------------------------------------|

| Product Status             | Active                                                                       |

| Core Processor             | PIC                                                                          |

| Core Size                  | 8-Bit                                                                        |

| Speed                      | 48MHz                                                                        |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART, USB                                       |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                   |

| Number of I/O              | 16                                                                           |

| Program Memory Size        | 16KB (8K x 16)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 3.8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2V ~ 3.6V                                                                    |

| Data Converters            | A/D 10x10b                                                                   |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                            |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 28-VQFN Exposed Pad                                                          |

| Supplier Device Package    | 28-QFN (6x6)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic18lf24j50t-i-ml |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

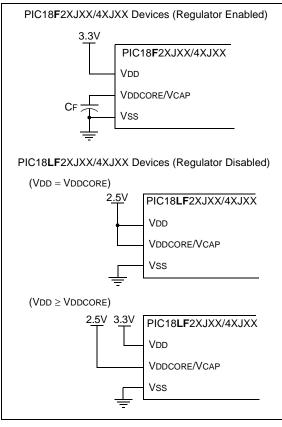

## 2.1.1 PIC18F2XJXX/4XJXX/ LF2XJXX/LF4XJXX DEVICES AND THE ON-CHIP VOLTAGE REGULATOR

PIC18FXXJXX devices have an internal core voltage regulator. On these devices ("PIC18F" in the part number), the regulator is always enabled. The regulator input is taken from the VDD pins of the microcontroller. The output of the regulator is supplied to the VDDCORE/VCAP pin. On these devices, this pin simultaneously serves as both regulator output and microcontroller core power input pin. For these devices, the VDDCORE/VCAP pin should be tied only to a capacitor.

PIC18LFXXJXX devices do not have an internal core voltage regulator. On the low-voltage devices (LF), power must be externally supplied to both VDD and VDDCORE/VCAP.

Whether or not the regulator is used, it is always good design practice to have sufficient capacitance on all supply pins. Examples are shown in Figure 2-3.

The specifications for core voltage and capacitance are listed in Section 6.0 "AC/DC Characteristics Timing Requirements for Program/Verify Test Mode".

## FIGURE 2-3: CONNECTIONS FOR THE ON-CHIP REGULATOR

## 2.2 Memory Maps

The PIC18F2XJXX/4XJXX Family of devices offers program memory sizes of 16, 32, 64, and 128 Kbytes. The memory sizes for different members of the family are shown in Table 2-2. The overall memory maps for all the devices are shown in Figure 2-4.

| TABLE 2-2: | PROGRAM MEMORY SIZES  |

|------------|-----------------------|

|            | FOR PIC18F2XJXX/4XJXX |

|            | FAMILY DEVICES        |

|             | Program Location of Flash |                        |  |  |  |  |

|-------------|---------------------------|------------------------|--|--|--|--|

| Device*     | Memory<br>(Kbytes)        | Configuration<br>Words |  |  |  |  |

| PIC18F24J10 |                           |                        |  |  |  |  |

| PIC18F44J10 |                           |                        |  |  |  |  |

| PIC18F24J11 | 16                        | 3FF8h:3FFFh            |  |  |  |  |

| PIC18F44J11 | 10                        | 36601.36661            |  |  |  |  |

| PIC18F24J50 |                           |                        |  |  |  |  |

| PIC18F44J50 |                           |                        |  |  |  |  |

| PIC18F25J10 |                           |                        |  |  |  |  |

| PIC18F45J10 |                           | 7FF8h:7FFFh            |  |  |  |  |

| PIC18F25J11 | 32                        |                        |  |  |  |  |

| PIC18F45J11 | 32                        |                        |  |  |  |  |

| PIC18F25J50 |                           |                        |  |  |  |  |

| PIC18F45J50 |                           |                        |  |  |  |  |

| PIC18F26J11 |                           |                        |  |  |  |  |

| PIC18F46J11 |                           |                        |  |  |  |  |

| PIC18F26J13 |                           |                        |  |  |  |  |

| PIC18F46J13 | 64                        | FFF8h:FFFFh            |  |  |  |  |

| PIC18F26J50 | 04                        | ГГГОП.ГГГГП            |  |  |  |  |

| PIC18F46J50 |                           |                        |  |  |  |  |

| PIC18F26J53 |                           |                        |  |  |  |  |

| PIC18F46J53 |                           |                        |  |  |  |  |

| PIC18F27J13 |                           |                        |  |  |  |  |

| PIC18F47J13 | 128                       | 1FFF8h:1FFFFh          |  |  |  |  |

| PIC18F27J53 | 120                       | IFFF8N:IFFFFN          |  |  |  |  |

| PIC18F47J53 |                           |                        |  |  |  |  |

Includes PIC18F and PIC18LF devices.

For purposes of code protection, the program memory for every device is treated as a single block. Therefore, enabling code protection, thus protecting the entire code memory and not individual segments.

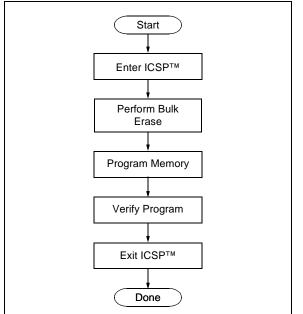

## 2.3 Overview of the Programming Process

Figure 2-5 shows the high-level overview of the programming process in which a Bulk Erase is performed first, then the code memory is programmed. Since only nonvolatile Configuration Words are within the code memory space, the Configuration Words are also programmed as code. Code memory (including the Configuration Words) is then verified to ensure that programming was successful.

## FIGURE 2-5: HIGH-LEVEL PROGRAMMING FLOW

## 2.4 Entering and Exiting ICSP™ Program/Verify Mode

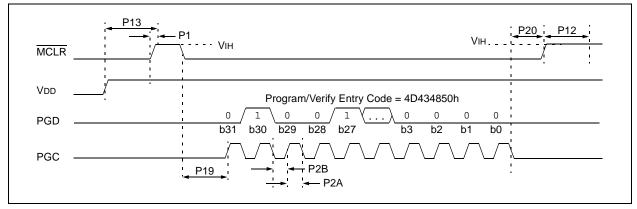

Entry into ICSP modes for PIC18F2XJXX/4XJXX Family devices is somewhat different than previous PIC18 devices. As shown in Figure 2-6, entering ICSP Program/Verify mode requires three steps:

- 1. Voltage is briefly applied to the MCLR pin.

- 2. A 32-bit key sequence is presented on PGD.

- 3. Voltage is reapplied to MCLR and held.

The programming voltage applied to  $\overline{\text{MCLR}}$  is VIH, or essentially, VDD. There is no minimum time requirement for holding at VIH. After VIH is removed, an interval of at least P19 must elapse before presenting the key sequence on PGD.

The key sequence is a specific 32-bit pattern, '0100 1101 0100 0011 0100 1000 0101 0000', which is more easily remembered as 4D434850h in hexadecimal. The device will enter Program/Verify mode only if the sequence is valid. The Most Significant bit of the Most Significant nibble must be shifted in first.

Once the key sequence is complete, VIH must be applied to MCLR and held at that level for as long as Program/Verify mode is to be maintained. An interval of at least time, P20 and P12, must elapse before presenting data on PGD. Signals appearing on PGD before P12 has elapsed may not be interpreted as valid.

On successful entry, the program memory can be accessed and programmed in serial fashion. While in the Program/Verify mode, all unused I/Os are placed in the high-impedance state.

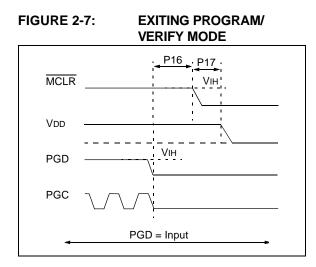

Exiting Program/Verify mode is done by removing VIH from MCLR, as shown in Figure 2-7. The only requirement for exit is that an interval, P16, should elapse between the last clock and program signals on PGC and PGD before removing VIH.

When VIH is reapplied to MCLR, the device will enter the ordinary operational mode and begin executing the application instructions.

## FIGURE 2-6: ENTERING PROGRAM/VERIFY MODE

## 2.5 Serial Program/Verify Operation

The PGC pin is used as a clock input pin and the PGD pin is used for entering command bits and data input/ output during serial operation. Commands and data are transmitted on the rising edge of PGC, latched on the falling edge of PGC, and are Least Significant bit (LSb) first.

## 2.5.1 FOUR-BIT COMMANDS

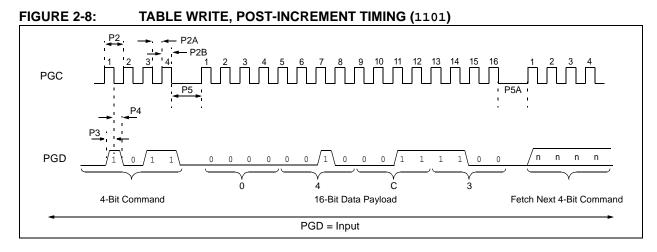

All instructions are 20 bits, consisting of a leading 4-bit command followed by a 16-bit operand, which depends on the type of command being executed. To input a command, PGC is cycled four times. The commands needed for programming and verification are shown in Table 2-3.

Depending on the 4-bit command, the 16-bit operand represents 16 bits of input data or eight bits of input data and eight bits of output data. Throughout this specification, commands and data are presented as illustrated in Table 2-4. The 4-bit command is shown Most Significant bit (MSb) first. The command operand or "Data Payload" is shown <MSB><LSB>. Figure 2-8 demonstrates how to serially present a 20-bit command/operand to the device.

## 2.5.2 CORE INSTRUCTION

The core instruction passes a 16-bit instruction to the CPU core for execution. This is needed to set up registers as appropriate for use with other commands.

### TABLE 2-3: COMMANDS FOR PROGRAMMING

| Description                                            | 4-Bit<br>Command |

|--------------------------------------------------------|------------------|

| Core Instruction<br>(Shift in 16-bit instruction)      | 0000             |

| Shift out TABLAT register                              | 0010             |

| Table Read                                             | 1000             |

| Table Read, Post-Increment                             | 1001             |

| Table Read, Post-Decrement                             | 1010             |

| Table Read, Pre-Increment                              | 1011             |

| Table Write                                            | 1100             |

| Table Write, Post-Increment by 2                       | 1101             |

| Table Write, Start Programming,<br>Post-Increment by 2 | 1110             |

| Table Write, Start Programming                         | 1111             |

## TABLE 2-4: SAMPLE COMMAND SEQUENCE

| 4-Bit<br>Command | Data<br>Payload | Core Instruction                    |

|------------------|-----------------|-------------------------------------|

| 1101             | 3C 40           | Table Write,<br>post-increment by 2 |

## 3.0 DEVICE PROGRAMMING

Programming includes the ability to erase or write the memory within the device.

The EECON1 register is used to control Write or Row Erase operations. The WREN bit must be set to enable writes; this must be done prior to initiating a write sequence. It is strongly recommended that the WREN bit only be set immediately prior to a program or erase operation.

The FREE bit must be set in order to erase the program space being pointed to by the Table Pointer. The erase or write sequence is initiated by setting the WR bit.

## 3.1 ICSP<sup>™</sup> Erase

## 3.1.1 ICSP BULK ERASE

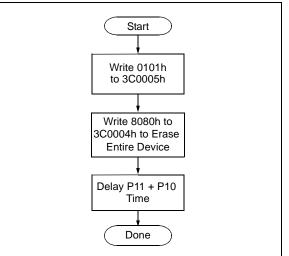

The PIC18F2XJXX/4XJXX Family devices may be Bulk Erased by writing 0180h to the table address, 3C0005h:3C0004h. The basic sequence is shown in Table 3-1 and demonstrated in Figure 3-1.

Since the code-protect Configuration bit is stored in the program code within code memory, a Bulk Erase operation will also clear any code-protect settings for the device.

The actual Bulk Erase function is a self-timed operation. Once the erase has started (falling edge of the 4th PGC after the NOP command), serial execution will cease until the erase completes (parameter P11). During this time, PGC may continue to toggle but PGD must be held low.

### TABLE 3-1: BULK ERASE COMMAND SEQUENCE

| 4-Bit<br>Command | Data<br>Payload | Core Instruction         |

|------------------|-----------------|--------------------------|

| 0000             | 0E 3C           | MOVLW 3Ch                |

| 0000             | 6E F8           | MOVWF TBLPTRU            |

| 0000             | 0E 00           | MOVLW 00h                |

| 0000             | 6E F7           | MOVWF TBLPTRH            |

| 0000             | 0E 05           | MOVLW 05h                |

| 0000             | 6E F6           | MOVWF TBLPTRL            |

| 1100             | 01 01           | Write 01h to 3C0005h     |

| 0000             | 0E 3C           | MOVLW 3Ch                |

| 0000             | 6E F8           | MOVWF TBLPTRU            |

| 0000             | 0E 00           | MOVLW 00h                |

| 0000             | 6E F7           | MOVWF TBLPTRH            |

| 0000             | 0E 04           | MOVLW 04h                |

| 0000             | 6E F6           | MOVWF TBLPTRL            |

| 1100             | 80 80           | Write 80h TO 3C0004h to  |

|                  |                 | erase entire device.     |

| 0000             | 00 00           | NOP                      |

| 0000             | 00 00           | Hold PGD low until erase |

|                  |                 | completes.               |

## BULK ERASE FLOW

#### FIGURE 3-2: **BULK ERASE TIMING** P10 2 PGC P5 P5A P5 P5A P11 PGD 0 0 1 1 0 0 0 0 0 0 0 0 0 0 0 0 n n 4-Bit Command 16-Bit Data Payload 16-Bit 16-Bit 4-Bit Command Erase Time 4-Bit Command Data Payload Data Payload PGD = Input

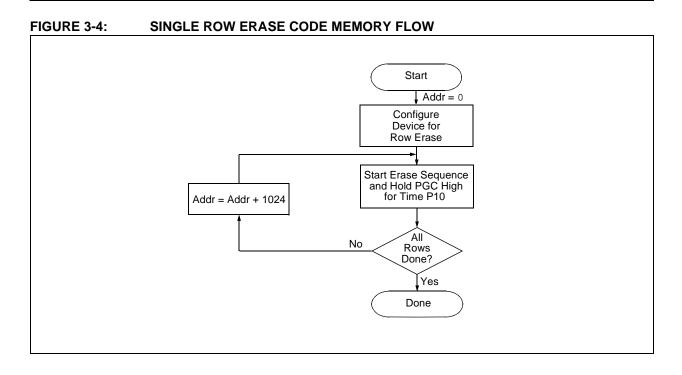

## 3.2.1 MODIFYING CODE MEMORY

The previous programming example assumed that the device had been Bulk Erased prior to programming. It may be the case, however, that the user wishes to modify only a section of an already programmed device.

As described in **Section 4.2 "Verify Code Memory and Configuration Word**", the appropriate number of bytes required for the erase buffer must be read out of code memory and buffered. Modifications can be made on this buffer. Then, the block of code memory that was read out must be erased and rewritten with the modified data. The code sequence is shown in Table 3-4. The WREN bit must be set if the WR bit in EECON1 is used to initiate a write sequence.

## 3.2.2 CONFIGURATION WORD PROGRAMMING

Since the Flash Configuration Words are stored in program memory, they are programmed as if they were program data. Refer to Section 3.2 "Code Memory Programming" and Section 3.2.1 "Modifying Code Memory" for methods and examples on programming or modifying program memory. See also Section 5.0 "Configuration Word" for additional information on the Configuration Words.

| 4-Bit<br>Command                         | Data Payload                             | Core Instruction                                                                |

|------------------------------------------|------------------------------------------|---------------------------------------------------------------------------------|

| Step 1: Set the                          | Table Pointer for the block to b         | be erased.                                                                      |

| 0000                                     | 0E <addr[21:16]><br/>6E F8</addr[21:16]> | MOVLW <addr[21:16]><br/>MOVWF TBLPTRU</addr[21:16]>                             |

| 0000                                     | 0E <addr[8:15]></addr[8:15]>             | MOVLW <addr[8:15]></addr[8:15]>                                                 |

| 0000                                     | 6E F7                                    | MOVWF TBLPTRH                                                                   |

| 0000                                     | 0E <addr[7:0]></addr[7:0]>               | MOVLW <addr[7:0]></addr[7:0]>                                                   |

| 0000                                     | 6E F6                                    | MOVWF TBLPTRL                                                                   |

| Step 2: Read an                          | d modify code memory (see                | Section 4.1 "Read Code Memory").                                                |

| Step 3: Enable r                         | nemory writes and set up an e            | erase.                                                                          |

| 0000                                     | 84 A6                                    | BSF EECON1, WREN                                                                |

| 0000                                     | 88 A6                                    | BSF EECON1, FREE                                                                |

| Step 4: Initiate e                       | rase.                                    | ·                                                                               |

| 0000                                     | 82 A6                                    | BSF EECON1, WR                                                                  |

| 0000                                     | 00 00                                    | NOP - hold PGC high for time P10.                                               |

| Step 5: Load wri                         | te buffer. The correct bytes w           | ill be selected based on the Table Pointer.                                     |

| 0000                                     | 0E <addr[21:16]></addr[21:16]>           | MOVLW <addr[21:16]></addr[21:16]>                                               |

| 0000                                     | 6E F8                                    | MOVWF TBLPTRU                                                                   |

| 0000                                     | 0E <addr[8:15]></addr[8:15]>             | MOVLW <addr[8:15]></addr[8:15]>                                                 |

| 0000                                     | 6E F7                                    | MOVWF TBLPTRH                                                                   |

| 0000                                     | OE <addr[7:0]></addr[7:0]>               | MOVLW <addr[7:0]></addr[7:0]>                                                   |

| 0000                                     | 6E F6                                    | MOVWF TBLPTRL                                                                   |

| 1101                                     | <msb><lsb></lsb></msb>                   | Write 2 bytes and post-increment address by 2.                                  |

| •                                        | •                                        | Repeat write operation 30 more times to fill the write buffer                   |

| •                                        |                                          | Repeat white operation so more times to this the write burler                   |

| 1111                                     | <msb><lsb></lsb></msb>                   | Write 2 bytes and start programming.                                            |

| 0000                                     | 00 00                                    | NOP - hold PGC high for time P9.                                                |

|                                          |                                          | if rewriting the entire 1024 bytes of the erase page size).                     |

|                                          |                                          | <b>.</b>                                                                        |

| Step 7: To contir<br>iteration of the lo |                                          | eps 1 through 5, where the Address Pointer is incremented by 1024 bytes at each |

| Step 8: Disable                          | writes.                                  |                                                                                 |

| 0000                                     | 94 A6                                    | BCF EECON1, WREN                                                                |

## TABLE 3-4: MODIFYING CODE MEMORY

## 3.3 Endurance and Retention

To maintain the endurance specification of the Flash program memory cells, each byte should never be programmed more than once between erase operations. Before attempting to modify the contents of a specific byte of Flash memory a second time, an erase operation (either a Bulk Erase or a Row Erase which includes that byte) should be performed.

## 4.0 READING THE DEVICE

## 4.1 Read Code Memory

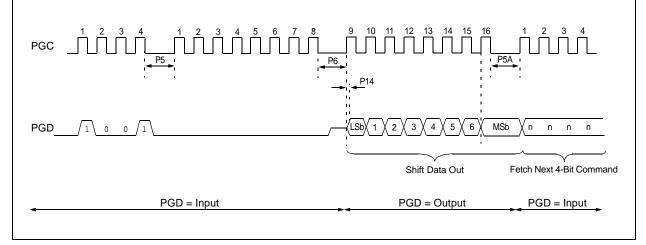

Code memory is accessed one byte at a time via the 4-bit command, '1001' (table read, post-increment). The contents of memory pointed to by the Table Pointer (TBLPTRU:TBLPTRH:TBLPTRL) are serially output on PGD.

The 4-bit command is shifted in LSb first. The read is executed during the next eight clocks, then shifted out on PGD during the last eight clocks, LSb to MSb. A

delay of P6 must be introduced after the falling edge of the 8th PGC of the operand to allow PGD to transition from an input to an output. During this time, PGC must be held low (see Figure 4-1). This operation also increments the Table Pointer by one, pointing to the next byte in code memory for the next read.

This technique will work to read any memory in the 000000h to 3FFFFFh address space, so it also applies to reading the Configuration registers.

| 4-Bit<br>Command  | Data Payload                                                                                                        | Core Instruction                                                                                                                            |

|-------------------|---------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|

| Step 1: Set Table | Pointer.                                                                                                            |                                                                                                                                             |

|                   | <pre>0E <addr[21:16]> 6E F8 0E <addr[15:8]> 6E F7 0E <addr[7:0]> 6E F6</addr[7:0]></addr[15:8]></addr[21:16]></pre> | MOVLW Addr[21:16]<br>MOVWF TBLPTRU<br>MOVLW <addr[15:8]><br/>MOVWF TBLPTRH<br/>MOVLW <addr[7:0]><br/>MOVWF TBLPTRL</addr[7:0]></addr[15:8]> |

| Step 2: Read mer  | nory and then shift out on P                                                                                        | GD, LSb to MSb.                                                                                                                             |

| 1001              | 00 00                                                                                                               | TBLRD *+                                                                                                                                    |

## FIGURE 4-1: TABLE READ, POST-INCREMENT INSTRUCTION TIMING (1001)

## 5.0 CONFIGURATION WORD

The Configuration Words of the PIC18F2XJXX/4XJXX Family devices are implemented as volatile memory registers. All of the Configuration registers (CONFIG1L, CONFIG1H, CONFIG2L, CONFIG2H, CONFIG3L, CONFIG3H, CONFIG4L, and CONFIG4H) are automatically loaded following each device Reset.

The data for these registers is taken from the four Flash Configuration Words located at the end of program memory. Configuration data is stored in order, starting with CONFIG1L in the lowest Flash address and ending with CONFIG4H in the highest. The mapping to specific Configuration Words is shown in Table 5-1. Users should always reserve these locations for Configuration Word data and write their application code accordingly.

The upper four bits of each Flash Configuration Word should always be stored in program memory as '1111'. This is done so these program memory addresses will always be '1111 xxxx xxxx 'and interpreted as a NOP instruction if they were ever to be executed. Because the corresponding bits in the Configuration registers are unimplemented, they will not change the device's configuration.

The Configuration and Device ID registers are summarized in Table 5-2. A listing of the individual Configuration bits and their options is provided in Table 5-3.

#### TABLE 5-1: MAPPING OF THE FLASH CONFIGURATION WORDS TO THE CONFIGURATION REGISTERS

| Configuration<br>Register | Flash<br>Configuration<br>Byte <sup>(1)</sup> | Configuration<br>Register<br>Address |  |  |  |  |

|---------------------------|-----------------------------------------------|--------------------------------------|--|--|--|--|

| CONFIG1L                  | XFF8h                                         | 300000h                              |  |  |  |  |

| CONFIG1H                  | XFF9h                                         | 300001h                              |  |  |  |  |

| CONFIG2L                  | XFFAh                                         | 300002h                              |  |  |  |  |

| CONFIG2H                  | XFFBh                                         | 300003h                              |  |  |  |  |

| CONFIG3L                  | XFFCh                                         | 300004h                              |  |  |  |  |

| CONFIG3H                  | XFFDh                                         | 300005h                              |  |  |  |  |

| CONFIG4L <sup>(2)</sup>   | XFFEh                                         | 300006h                              |  |  |  |  |

| CONFIG4H <sup>(2)</sup>   | XFFFh                                         | 300007h                              |  |  |  |  |

|                           |                                               |                                      |  |  |  |  |

**Note 1:** See Table 2-2 for the complete addresses within code space for specific devices and memory sizes.

2: Unimplemented in PIC18F45J10 family devices.

| File    | Name                  | Bit 7 | Bit 6 | Bit 5  | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Default/<br>Unprogrammed<br>Value |

|---------|-----------------------|-------|-------|--------|-------|--------|--------|--------|--------|-----------------------------------|

| 300000h | CONFIG1L              | DEBUG | XINST | STVREN | _     | —      | _      | _      | WDTEN  | 1111                              |

| 300001h | CONFIG1H              | (1)   | (1)   | (1)    | (1)   | (2)    | CP0    | _      | _      | 01                                |

| 300002h | CONFIG2L              | IESO  | FCMEN | —      | —     | —      | FOSC2  | FOSC1  | FOSC0  | 11111                             |

| 300003h | CONFIG2H              | _(1)  | (1)   | _(1)   | _(1)  | WDTPS3 | WDTPS2 | WDTPS1 | WDTPS0 | 1111                              |

| 300005h | CONFIG3H              | (1)   | (1)   | (1)    | (1)   | —      | —      | —      | CCP2MX | 1                                 |

| 3FFFFEh | DEVID1 <sup>(3)</sup> | DEV2  | DEV1  | DEV0   | REV4  | REV3   | REV2   | REV1   | REV0   | See Table                         |

| 3FFFFFh | DEVID2 <sup>(3)</sup> | DEV10 | DEV9  | DEV8   | DEV7  | DEV6   | DEV5   | DEV4   | DEV3   | See Table                         |

## TABLE 5-2: PIC18F45J10 FAMILY DEVICES: CONFIGURATION BITS AND DEVICE IDs

Legend: -= unimplemented. Shaded cells are unimplemented, read as '0'.

**Note** 1: The value of these bits in program memory should always be '1'. This ensures that the location is executed as a NOP if it is accidentally executed.

2: This bit should always be maintained at '0'.

3: DEVID registers are read-only and cannot be programmed by the user.

| Bit Name   | Configuration<br>Words | Description                                                                                                                                                                                                                                                                             |  |  |  |

|------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| DEBUG      | CONFIG1L               | <ul> <li>Background Debugger Enable bit</li> <li>1 = Background debugger disabled, RB6 and RB7 configured as general purpose I/O pins</li> <li>0 = Background debugger enabled, RB6 and RB7 are dedicated to in-circuit deb</li> </ul>                                                  |  |  |  |

| XINST      | CONFIG1L               | Extended Instruction Set Enable bit<br>1 = Instruction set extension and Indexed Addressing mode enabled<br>0 = Instruction set extension and Indexed Addressing mode disabled<br>(Legacy mode)                                                                                         |  |  |  |

| STVREN     | CONFIG1L               | Stack Overflow/Underflow Reset Enable bit<br>1 = Reset on stack overflow/underflow enabled<br>0 = Reset on stack overflow/underflow disabled                                                                                                                                            |  |  |  |

| WDTEN      | CONFIG1L               | Watchdog Timer Enable bit<br>1 = WDT enabled<br>0 = WDT disabled (control is placed on SWDTEN bit)                                                                                                                                                                                      |  |  |  |

| CP0        | CONFIG1H               | Code Protection bit<br>1 = Program memory is not code-protected<br>0 = Program memory is code-protected                                                                                                                                                                                 |  |  |  |

| IESO       | CONFIG2L               | Internal/External Oscillator Switchover bit<br>1 = Oscillator Switchover mode enabled<br>0 = Oscillator Switchover mode disabled                                                                                                                                                        |  |  |  |

| FCMEN      | CONFIG2L               | Fail-Safe Clock Monitor Enable bit<br>1 = Fail-Safe Clock Monitor enabled<br>0 = Fail-Safe Clock Monitor disabled                                                                                                                                                                       |  |  |  |

| FOSC2      | CONFIG2L               | Default Oscillator Select bit<br>1 = Clock designated by FOSC<1:0> is enabled as system clock when<br>OSCCON<1:0> = 00<br>0 = INTRC is enabled as system clock when OSCCON<1:0> = 00                                                                                                    |  |  |  |

| FOSC<1:0>  | CONFIG2L               | Primary Oscillator Select bits         11 = EC oscillator, PLL enabled and under software control, CLKO function on OSC2         10 = EC oscillator, CLKO function on OSC2         01 = HS oscillator, PLL enabled and under software control         00 = HS oscillator                |  |  |  |

| WDTPS<3:0> | CONFIG2H               | Watchdog Timer Postscale Select bits<br>1111 = 1:32,768<br>1110 = 1:16,384<br>1101 = 1:8,192<br>1100 = 1:4,096<br>1011 = 1:2,048<br>1010 = 1:1,024<br>1000 = 1:256<br>0111 = 1:128<br>0110 = 1:64<br>0101 = 1:32<br>0100 = 1:16<br>0011 = 1:8<br>0010 = 1:4<br>0001 = 1:2<br>0000 = 1:1 |  |  |  |

| CCP2MX     | CONFIG3H               | 0000 = 1:1<br>CCP2 MUX bit<br>1 = CCP2 is multiplexed with RC1<br>0 = CCP2 is multiplexed with RB3                                                                                                                                                                                      |  |  |  |

## TABLE 5-3: PIC18F45J10 FAMILY DEVICES: BIT DESCRIPTIONS

## TABLE 5-4: PIC18F46J11 AND PIC18F46J50 FAMILY DEVICES: CONFIGURATION BITS AND DEVICE IDs

| File    | Name     | Bit 7    | Bit 6    | Bit 5                | Bit 4                | Bit 3                  | Bit 2                  | Bit 1                 | Bit 0                 | Default/<br>Unprogrammed<br>Value <sup>(1)</sup> |

|---------|----------|----------|----------|----------------------|----------------------|------------------------|------------------------|-----------------------|-----------------------|--------------------------------------------------|

| 300000h | CONFIG1L | DEBUG    | XINST    | STVREN               | —                    | PLLDIV2 <sup>(3)</sup> | PLLDIV1 <sup>(3)</sup> | PLLDIV0(3)            | WDTEN                 | 111- 1111                                        |

| 300001h | CONFIG1H | (2)      | (2)      | (2)                  | (2)                  | (4)                    | CP0                    | CPDIV1 <sup>(3)</sup> | CPDIV0 <sup>(3)</sup> | 0111                                             |

| 300002h | CONFIG2L | IESO     | FCMEN    | _                    | LPT1OSC              | T1DIG                  | FOSC2                  | FOSC1                 | FOSC0                 | 11-1 1111                                        |

| 300003h | CONFIG2H | (2)      | (2)      | (2)                  | (2)                  | WDTPS3                 | WDTPS2                 | WDTPS1                | WDTPS0                | 1111                                             |

| 300004h | CONFIG3L | DSWDTPS3 | DSWDTPS2 | DSWDTPS1             | DSWDTPS0             | DSWDTEN                | DSBOREN                | RTCOSC                | DSWDTOSC              | 1111 1111                                        |

| 300005h | CONFIG3H | (2)      | (2)      | (2)                  | (2)                  | MSSPMSK                | _                      | _                     | IOL1WAY               | 11                                               |

| 300006h | CONFIG4L | WPCFG    | WPEND    | WPFP5 <sup>(5)</sup> | WPFP4 <sup>(6)</sup> | WPFP3                  | WPFP2                  | WPFP1                 | WPFP0                 | 1111 1111                                        |

| 300007h | CONFIG4H | (2)      | (2)      | (2)                  | (2)                  | _                      | _                      | _                     | WPDIS                 | 1                                                |

| 3FFFFEh | DEVID1   | DEV2     | DEV1     | DEV0                 | REV4                 | REV3                   | REV2                   | REV1                  | REV0                  | XXXX XXXX                                        |

| 3FFFFFh | DEVID2   | DEV10    | DEV9     | DEV8                 | DEV7                 | DEV6                   | DEV5                   | DEV4                  | DEV3                  | 0100 00xx                                        |

Legend: x = unknown, u = unchanged, - = unimplemented. Shaded cells are unimplemented, read as '0'.

**Note** 1: Values reflect the unprogrammed state as received from the factory and following Power-on Resets. In all other Reset states, the configuration bytes maintain their previously programmed states.

2: The value of these bits in program memory should always be '1'. This ensures that the location is executed as a NOP if it is accidentally executed.

3: These bits are not implemented in PIC18F46J11 family devices.

4: This bit should always be maintained at '0'.

5: This bit is not available on 32K and 16K memory devices (X4J11, X4J50, X5J11, and X5J50 devices) and should always be maintained at '0' on those devices.

6: This bit is not available on 16K memory devices (X4J11 and X4J50 devices) and should always be maintained at '0' on those devices.

## TABLE 5-5: PIC18F46J11 AND PIC18F46J50 FAMILY DEVICES: BIT DESCRIPTIONS

| Bit Name                   | Configuration<br>Words | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

|----------------------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| DEBUG                      | CONFIG1L               | Background Debugger Enable bit<br>1 = Background debugger disabled, RB6 and RB7 configured as general purpose<br>I/O pins<br>0 = Background debugger enabled, RB6 and RB7 are dedicated to in-circuit debug                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| XINST                      | CONFIG1L               | Enhanced Instruction Set Enable bit<br>1 = Instruction set extension and Indexed Addressing mode enabled<br>0 = Instruction set extension and Indexed Addressing mode disabled (Legacy mode)                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| STVREN                     | CONFIG1L               | Stack Overflow/Underflow Reset Enable bit<br>1 = Reset on stack overflow/underflow enabled<br>0 = Reset on stack overflow/underflow disabled                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| PLLDIV<2:0> <sup>(3)</sup> | CONFIG1L               | PLL Input Divider bits<br>Divider must be selected to provide a 4 MHz input into the 96 MHz PLL.<br>111 = No divide – oscillator used directly (4 MHz input)<br>110 = Oscillator divided by 2 (8 MHz input)<br>101 = Oscillator divided by 3 (12 MHz input)<br>100 = Oscillator divided by 4 (16 MHz input)<br>011 = Oscillator divided by 5 (20 MHz input)<br>010 = Oscillator divided by 6 (24 MHz input)<br>001 = Oscillator divided by 10 (40 MHz input)<br>000 = Oscillator divided by 12 (48 MHz input) |  |  |  |  |

| WDTEN                      | CONFIG1L               | Watchdog Timer Enable bit<br>1 = WDT enabled<br>0 = WDT disabled (control is placed on SWDTEN bit)                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

Note 1: The Configuration bits can only be programmed indirectly by programming the Flash Configuration Word.

The Configuration bits are reset to '1' only on VDD Reset; it is reloaded with the programmed value at any device Reset.

These bits are not implemented in PIC18F46J11 family devices.

4: Once this bit is cleared, all the Configuration registers which reside in the last page are also protected. To disable code protection, perform an ICSP<sup>™</sup> Bulk Erase operation.

### TABLE 5-5: PIC18F46J11 AND PIC18F46J50 FAMILY DEVICES: BIT DESCRIPTIONS (CONTINUED)

| Bit Name  | Configuration<br>Words | Description                                                                                                                                                                                                                                                           |  |  |  |  |  |

|-----------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| WPFP<5:0> | CONFIG4L               | Nrite/Erase Protect Page Start/End Location bits<br>Jsed with WPEND bit to define which pages in Flash will be write/erase-protected.                                                                                                                                 |  |  |  |  |  |

| WPDIS     | CONFIG4H               | <ul> <li>Write Protect Disable bit</li> <li>1 = WPFP&lt;5:0&gt;, WPEND and WPCFG bits ignored; all Flash memory may be erased or written</li> <li>0 = WPFP&lt;5:0&gt;, WPEND and WPCFG bits enabled; write/erase-protect active for the selected region(s)</li> </ul> |  |  |  |  |  |

| DEV<2:0>  | DEVID1                 | Device ID bits<br>Used with the DEV<10:3> bits in the Device ID Register 2 to identify the part number.                                                                                                                                                               |  |  |  |  |  |

| REV<4:0>  | DEVID1                 | Revision ID bits<br>Indicate the device revision.                                                                                                                                                                                                                     |  |  |  |  |  |

| DEV<10:3> | DEVID2                 | Device ID bits<br>Used with the DEV<2:0> bits in the Device ID Register 1 to identify the part number.                                                                                                                                                                |  |  |  |  |  |

**Note 1:** The Configuration bits can only be programmed indirectly by programming the Flash Configuration Word.

The Configuration bits are reset to '1' only on VDD Reset; it is reloaded with the programmed value at any device Reset.

These bits are not implemented in PIC18F46J11 family devices.

4: Once this bit is cleared, all the Configuration registers which reside in the last page are also protected. To disable code protection, perform an ICSP™ Bulk Erase operation.

## TABLE 5-6:PIC18F47J13 AND PIC18F47J53 FAMILY DEVICES: CONFIGURATION BITS AND<br/>DEVICE IDs

| File    | Name     | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3                  | Bit 2   | Bit 1                 | Bit 0                 | Default/<br>Unprogrammed<br>Value <sup>(1)</sup> |

|---------|----------|----------|----------|----------|----------|------------------------|---------|-----------------------|-----------------------|--------------------------------------------------|

| 300000h | CONFIG1L | DEBUG    | XINST    | STVREN   | CFGPLLEN | PLLDIV2                | PLLDIV1 | PLLDIV0               | WDTEN                 | 111- 1111                                        |

| 300001h | CONFIG1H | (2)      | (2)      | (2)      | (2)      | (4)                    | CP0     | CPDIV1 <sup>(3)</sup> | CPDIV0 <sup>(3)</sup> | 0111                                             |

| 300002h | CONFIG2L | IESO     | FCMEN    | CLKOEC   | SOSCSEL1 | SOSCSEL0               | FOSC2   | FOSC1                 | FOSC0                 | 1111 1111                                        |

| 300003h | CONFIG2H | (2)      | (2)      | (2)      | (2)      | WDTPS3                 | WDTPS2  | WDTPS1                | WDTPS0                | 1111                                             |

| 300004h | CONFIG3L | DSWDTPS3 | DSWDTPS2 | DSWDTPS1 | DSWDTPS0 | DSWDTEN                | DSBOREN | RTCOSC                | DSWDTOSC              | 1111 1111                                        |

| 300005h | CONFIG3H | (2)      | (2)      | (2)      | (2)      | MSSPMSK                | PLLSEL  | ADCSEL                | IOL1WAY               | 1111                                             |

| 300006h | CONFIG4L | WPCFG    | WPFP6    | WPFP5    | WPFP4    | WPFP3                  | WPFP2   | WPFP1                 | WPFP0                 | 1111 1111                                        |

| 300007h | CONFIG4H | (2)      | (2)      | (2)      | (2)      | LS48MHZ <sup>(3)</sup> | -       | WPEND                 | WPDIS                 | 1-11                                             |

| 3FFFFEh | DEVID1   | DEV2     | DEV1     | DEV0     | REV4     | REV3                   | REV2    | REV1                  | REV0                  | xxxx xxxx                                        |

| 3FFFFFh | DEVID2   | DEV10    | DEV9     | DEV8     | DEV7     | DEV6                   | DEV5    | DEV4                  | DEV3                  | 0101 10xx                                        |

Legend: x = unknown, u = unchanged, - = unimplemented. Shaded cells are unimplemented, read as '0'.

**Note** 1: Values reflect the unprogrammed state as received from the factory and following Power-on Resets. In all other Reset states, the configuration bytes maintain their previously programmed states.

2: The value of these bits in program memory should always be '1'. This ensures that the location is executed as a NOP if it is accidentally executed.

3: These bits are not implemented in PIC18F47J13 family devices.

4: This bit should always be maintained at '0'.

| Bit Name                  | Configuration<br>Words    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DEBUG                     | CONFIG1L                  | <ul> <li>Background Debugger Enable bit</li> <li>1 = Background debugger disabled, RB6 and RB7 configured as general purpose I/O pins</li> <li>0 = Background debugger enabled, RB6 and RB7 are dedicated to in-circuit debug</li> </ul>                                                                                                                                                                                                                                                                     |

| XINST                     | CONFIG1L                  | Enhanced Instruction Set Enable bit<br>1 = Instruction set extension and Indexed Addressing mode enabled<br>0 = Instruction set extension and Indexed Addressing mode disabled (Legacy mode)                                                                                                                                                                                                                                                                                                                 |

| STVREN                    | CONFIG1L                  | Stack Overflow/Underflow Reset Enable bit<br>1 = Reset on stack overflow/underflow enabled<br>0 = Reset on stack overflow/underflow disabled                                                                                                                                                                                                                                                                                                                                                                 |

| CFGPLLEN                  | CONFIG1L                  | Enable PLL on Start-up bit<br>1 = PLL enabled on start-up. Not recommended for low-voltage designs.<br>0 = PLL disabled on start-up. Firmware may later enable PLL through OSCTUNE<6>.                                                                                                                                                                                                                                                                                                                       |

| PLLDIV<2:0>               | CONFIG1L                  | 96 MHz PLL Input Divider bits<br>Divider must be selected to provide a 4 MHz input into the 96 MHz PLL.<br>111 =No divide – oscillator used directly (4 MHz input)<br>110 =Oscillator divided by 2 (8 MHz input)<br>101 =Oscillator divided by 3 (12 MHz input)<br>100 =Oscillator divided by 4 (16 MHz input)<br>011 =Oscillator divided by 5 (20 MHz input)<br>010 =Oscillator divided by 6 (24 MHz input)<br>001 =Oscillator divided by 10 (40 MHz input)<br>000 =Oscillator divided by 12 (48 MHz input) |

| WDTEN                     | CONFIG1L                  | Watchdog Timer Enable bit<br>1 = WDT enabled<br>0 = WDT disabled (control is placed on the SWDTEN bit)                                                                                                                                                                                                                                                                                                                                                                                                       |

| CP0 <sup>(4)</sup>        | CONFIG1H                  | Code Protection bit<br>1 = Program memory is not code-protected<br>0 = Program memory is code-protected                                                                                                                                                                                                                                                                                                                                                                                                      |

| CPDIV<1:0> <sup>(3)</sup> | CONFIG1H                  | CPU System Clock Selection bits<br>11 = No CPU system clock divide<br>10 = CPU system clock divided by 2<br>01 = CPU system clock divided by 3<br>00 = CPU system clock divided by 6                                                                                                                                                                                                                                                                                                                         |

| IESO                      | CONFIG2L <sup>(1,2)</sup> | Two-Speed Start-up (Internal/External Oscillator Switchover) Control bit<br>1 = Oscillator Switchover mode enabled<br>0 = Oscillator Switchover mode disabled                                                                                                                                                                                                                                                                                                                                                |

| FCMEN                     | CONFIG2L <sup>(1,2)</sup> | Fail-Safe Clock Monitor Enable bit<br>1 = Fail-Safe Clock Monitor enabled<br>0 = Fail-Safe Clock Monitor disabled                                                                                                                                                                                                                                                                                                                                                                                            |

| CLKOEC                    | CONFIG2L                  | EC Mode Clock Output Enable bit<br>1 = CLKO output signal active on the RA6 pin (EC mode only)<br>0 = CLKO output disabled                                                                                                                                                                                                                                                                                                                                                                                   |

| SOSCSEL<1:0>              | CONFIG2L                  | Secondary Oscillator Circuit Selection bits<br>11 = High-power SOSC circuit selected<br>10 = Digital Input mode (SCLKI)<br>01 = Low-power SOSC circuit selected<br>00 = Reserved                                                                                                                                                                                                                                                                                                                             |

## TABLE 5-7: PIC18F47J13 AND PIC18F47J53 FAMILY DEVICES: BIT DESCRIPTIONS

Note 1: The Configuration bits can only be programmed indirectly by programming the Flash Configuration Word.

2: The Configuration bits are reset to '1' only on VDD Reset; it is reloaded with the programmed value at any device Reset.

**3:** These bits are not implemented in PIC18F47J13 family devices.

4: Once this bit is cleared, all the Configuration registers which reside in the last page are also protected. To disable code protection, perform an ICSP™ Bulk Erase operation.

5: Not implemented on PIC18F47J53 family devices.

| Bit Name    | Configuration<br>Words    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FOSC<2:0>   | CONFIG2L <sup>(1,2)</sup> | Oscillator Selection bits<br>111 =EC+PLL (S/W controlled by PLLEN bit), CLKO on RA6<br>110 =EC oscillator (PLL always disabled) with CLKO on RA6<br>101 =HS+PLL (S/W controlled by PLLEN bit)<br>100 =HS oscillator (PLL always disabled)<br>011 =INTOSCPLLO, internal oscillator with PLL (S/W controlled by PLLEN bit), CLKO on<br>RA6, port function on RA7<br>010 =INTOSCPLL, internal oscillator with PLL (S/W controlled by PLLEN bit), port<br>function on RA6 and RA7<br>001 =INTOSCO, internal oscillator, INTOSC or INTRC (PLL always disabled), CLKO on<br>RA6, port function on RA7<br>000 =INTOSC, internal oscillator INTOSC or INTRC (PLL always disabled), port function<br>on RA6 and RA7 |

| WDTPS<3:0>  | CONFIG2H <sup>(1,2)</sup> | Watchdog Timer Postscale Select bits         1111 = 1:32,768         1110 = 1:16,384         1101 = 1:8,192         1100 = 1:4,096         1011 = 1:2,048         1010 = 1:1,024         1000 = 1:256         0111 = 1:248         0101 = 1:32         0100 = 1:164         0011 = 1:32         0100 = 1:40         0011 = 1:32         0100 = 1:40         0001 = 1:20         0000 = 1:1                                                                                                                                                                                                                                                                                                                 |

| DSWTPS<3:0> | CONFIG3L                  | Deep Sleep Watchdog Timer Postscale Select bits<br>The DSWDT prescaler is 32; this creates an approximate base time unit of 1 ms.<br>1111 = 1:2,147,483,648 (25.7 days)<br>1110 = 1:536,870,912 (6.4 days)<br>1101 = 1:134,217,728 (38.5 hours)<br>1000 = 1:33,554,432 (9.6 hours)<br>1011 = 1:8,388,608 (2.4 hours)<br>1010 = 1:2,097,152 (36 minutes)<br>1001 = 1:524,288 (9 minutes)<br>1000 = 1:131,072 (135 seconds)<br>0111 = 1:32,768 (34 seconds)<br>0110 = 1:8,192 (8.5 seconds)<br>0101 = 1:2,048 (2.1 seconds)<br>0101 = 1:212 (528 ms)<br>0011 = 1:128 (132 ms)<br>0010 = 1:32 (33 ms)<br>0001 = 1:8 (8.3 ms)<br>0000 = 1:2 (2.1 ms)                                                           |

| DSWDTEN     | CONFIG3L                  | Deep Sleep Watchdog Timer Enable bit<br>1 = DSWDT enabled<br>0 = DSWDT disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| DSBOREN     | CONFIG3L                  | Deep Sleep BOR Enable bit<br>1 = BOR enabled in Deep Sleep<br>0 = BOR disabled in Deep Sleep (does not affect operation in non Deep Sleep modes)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

#### TABLE 5-7: PIC18F47J13 AND PIC18F47J53 FAMILY DEVICES: BIT DESCRIPTIONS (CONTINUED)

**Note 1:** The Configuration bits can only be programmed indirectly by programming the Flash Configuration Word.

The Configuration bits are reset to '1' only on VDD Reset; it is reloaded with the programmed value at any device Reset.

These bits are not implemented in PIC18F47J13 family devices.

4: Once this bit is cleared, all the Configuration registers which reside in the last page are also protected. To disable code protection, perform an ICSP<sup>™</sup> Bulk Erase operation.

5: Not implemented on PIC18F47J53 family devices.

| Bit Name                 | Configuration<br>Words | Description                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|--------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| RTCOSC                   | CONFIG3L               | RTCC Reference Clock Select bit         1 = RTCC uses T1OSC/T1CKI as reference clock         0 = RTCC uses INTRC as reference clock                                                                                                                                                                                                                                                     |  |  |  |  |  |

| DSWDTOSC                 | CONFIG3L               | DSWDT Reference Clock Select bit<br>1 = DSWDT uses INTRC as reference clock<br>0 = DSWDT uses T1OSC/T1CKI as reference clock                                                                                                                                                                                                                                                            |  |  |  |  |  |

| MSSPMSK <sup>(1,2)</sup> | CONFIG3H               | MSSP 7-Bit Address Masking Mode Enable bit<br>1 = 7-Bit Address Masking mode enable<br>0 = 5-Bit Address Masking mode enable                                                                                                                                                                                                                                                            |  |  |  |  |  |

| PLLSEL <sup>(5)</sup>    | CONFIG3H               | PLL Selection bit<br>1 = 4x PLL selected<br>0 = 96 MHz PLL selected                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| ADCSEL                   | CONFIG3H               | ADC Mode Selection bit<br>1 = 10-Bit ADC mode selected<br>0 = 12-Bit ADC mode selected                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| IOL1WAY                  | CONFIG3H               | <ul> <li>IOLOCK Bit One-Way Set Enable bit</li> <li>1 = The IOLOCK bit (PPSCON&lt;0&gt;) can be set once, provided the unlock sequence has been completed. Once set, the Peripheral Pin Select registers cannot be written to a second time.</li> <li>0 = The IOLOCK bit (PPSCON&lt;0&gt;) can be set and cleared as needed, provided the unlock sequence has been completed</li> </ul> |  |  |  |  |  |

| WPCFG                    | CONFIG4L               | <ul> <li>Write/Erase Protect Configuration Words Page bit (valid when WPDIS = 0)</li> <li>1 = Configuration Words page is not erase/write-protected unless WPEND and WPFP&lt;6:0&gt; settings include the Configuration Words page</li> <li>0 = Configuration Words page is erase/write-protected, regardless of WPEND and WPFP&lt;6:0&gt;</li> </ul>                                   |  |  |  |  |  |

| WPFP<6:0>                | CONFIG4L               | Write/Erase Protect Page Start/End Location bits<br>Used with WPEND bit to define which pages in Flash will be write/erase-protected.                                                                                                                                                                                                                                                   |  |  |  |  |  |

| WPEND                    | CONFIG4H               | Write/Erase Protect Region Select bit (valid when WPDIS = 0)<br>1 = Flash pages, WPFP<6:0> to Configuration Words page, are write/erase-protected<br>0 = Flash pages, 0 to WPFP<6:0> are write/erase-protected                                                                                                                                                                          |  |  |  |  |  |

| WPDIS                    | CONFIG4H               | <ul> <li>Write Protect Disable bit</li> <li>1 = WPFP&lt;6:0&gt;, WPEND and WPCFG bits ignored; all Flash memory may be erased or written</li> <li>0 = WPFP&lt;6:0&gt;, WPEND and WPCFG bits enabled; write/erase-protect active for the selected region(s)</li> </ul>                                                                                                                   |  |  |  |  |  |

| LS48MHZ <sup>(3)</sup>   | CONFIG4H               | System Clock Selection bit<br>1 = System clock is expected at 48 MHz, FS/LS USB CLKEN's divide-by is set to 8<br>0 = System clock is expected at 24 MHz, FS/LS USB CLKEN's divide-by is set to 4                                                                                                                                                                                        |  |  |  |  |  |

| DEV<2:0>                 | DEVID1                 | Device ID bits<br>Used with the DEV<10:3> bits in the Device ID Register 2 to identify the part number.                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| REV<4:0>                 | DEVID1                 | Revision ID bits<br>Indicate the device revision.                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| DEV<10:3>                | DEVID2                 | Device ID bits<br>Used with the DEV<2:0> bits in the Device ID Register 1 to identify the part number.                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

### TABLE 5-7: PIC18F47J13 AND PIC18F47J53 FAMILY DEVICES: BIT DESCRIPTIONS (CONTINUED)

Note 1: The Configuration bits can only be programmed indirectly by programming the Flash Configuration Word.

2: The Configuration bits are reset to '1' only on VDD Reset; it is reloaded with the programmed value at any device Reset.

**3:** These bits are not implemented in PIC18F47J13 family devices.

4: Once this bit is cleared, all the Configuration registers which reside in the last page are also protected. To disable code protection, perform an ICSP<sup>™</sup> Bulk Erase operation.

5: Not implemented on PIC18F47J53 family devices.

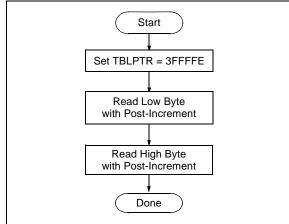

## 5.1 Device ID Word

The Device ID Word for the PIC18F2XJXX/4XJXX Family devices is located at 3FFFFEh:3FFFFFh. These read-only bits may be used by the programmer to identify what device type is being programmed and read out normally, even after code protection has been enabled. The process for reading the Device IDs is shown in Figure 5-1. A complete list of Device ID values for the PIC18F2XJXX/4XJXX Family is presented in Table 5-8.

## TABLE 5-8: DEVICE ID VALUE

|              | Device ID Value |           |  |  |  |

|--------------|-----------------|-----------|--|--|--|

| Device       | DEVID2          | DEVID1    |  |  |  |

| PIC18F24J10  | 1Dh             | 000x xxxx |  |  |  |

| PIC18F25J10  | 1Ch             | 000x xxxx |  |  |  |

| PIC18F44J10  | 1Dh             | 001x xxxx |  |  |  |

| PIC18F45J10  | 1Ch             | 001x xxxx |  |  |  |

| PIC18LF24J10 | 1Dh             | 010x xxxx |  |  |  |

| PIC18LF25J10 | 1Ch             | 010x xxxx |  |  |  |

| PIC18LF44J10 | 1Dh             | 011x xxxx |  |  |  |

| PIC18LF45J10 | 1Ch             | 011x xxxx |  |  |  |

| PIC18F25J11  | 4Dh             | 101x xxxx |  |  |  |

| PIC18F24J11  | 4Dh             | 100x xxxx |  |  |  |

| PIC18F26J11  | 4Dh             | 110x xxxx |  |  |  |

| PIC18F45J11  | 4Eh             | 000x xxxx |  |  |  |

| PIC18F44J11  | 4Dh             | 111x xxxx |  |  |  |

| PIC18F46J11  | 4Eh             | 001x xxxx |  |  |  |

| PIC18F24J50  | 4Ch             | 000x xxxx |  |  |  |

| PIC18F25J50  | 4Ch             | 001x xxxx |  |  |  |

| PIC18F26J50  | 4Ch             | 010x xxxx |  |  |  |

| PIC18F44J50  | 4Ch             | 011x xxxx |  |  |  |

| PIC18F45J50  | 4Ch             | 100x xxxx |  |  |  |

## TABLE 5-8: DEVICE ID VALUE (CONTINUED)

|              | Device ID VALUE (CONTINUED |           |  |  |

|--------------|----------------------------|-----------|--|--|

| Device       | DEVID2                     | DEVID1    |  |  |

| PIC18F46J50  | 4Ch                        | 101x xxxx |  |  |

| PIC18LF2450  | 4Ch                        | 110x xxxx |  |  |

| PIC18LF25J50 | 4Ch                        | 111x xxxx |  |  |

| PIC18LF26J50 | 4Dh                        | 000x xxxx |  |  |

| PIC18LF44J50 | 4Dh                        | 001x xxxx |  |  |

| PIC18LF45J50 | 4Dh                        | 010x xxxx |  |  |

| PIC18LF46J50 | 4Dh                        | 011x xxxx |  |  |

| PIC18LF24J11 | 4Eh                        | 010x xxxx |  |  |

| PIC18LF25J11 | 4Eh                        | 011x xxxx |  |  |

| PIC18LF26J11 | 4Eh                        | 100x xxxx |  |  |

| PIC18LF44J11 | 4Eh                        | 101x xxxx |  |  |

| PIC18LF45J11 | 4Eh                        | 110x xxxx |  |  |

| PIC18LF46J11 | 4Eh                        | 111x xxxx |  |  |

| PIC18F26J13  | 59h                        | 001x xxxx |  |  |

| PIC18F27J13  | 59h                        | 011x xxxx |  |  |

| PIC18F46J13  | 59h                        | 101x xxxx |  |  |

| PIC18F47J13  | 59h                        | 111x xxxx |  |  |

| PIC18LF26J13 | 5Bh                        | 001x xxxx |  |  |

| PIC18LF27J13 | 5Bh                        | 011x xxxx |  |  |

| PIC18LF46J13 | 5Bh                        | 101x xxxx |  |  |

| PIC18LF47J13 | 5Bh                        | 111x xxxx |  |  |

| PIC18F26J53  | 58h                        | 001x xxxx |  |  |

| PIC18F27J53  | 58h                        | 011x xxxx |  |  |

| PIC18F46J53  | 58h                        | 101x xxxx |  |  |

| PIC18F47J53  | 58h                        | 111x xxxx |  |  |

| PIC18LF26J53 | 5Ah                        | 001x xxxx |  |  |

| PIC18LF27J53 | 5Ah                        | 011x xxxx |  |  |

| PIC18LF46J53 | 5Ah                        | 101x xxxx |  |  |

| PIC18LF47J53 | 5Ah                        | 111x xxxx |  |  |

## 5.2 Checksum Computation

The checksum is calculated by summing the contents of all code memory locations and the device Configuration Words, appropriately masked. The Least Significant 16 bits of this sum are the checksum.

The checksum calculation differs depending on whether or not code protection is enabled. Since the code memory locations read out differently depending on the code-protect setting, the table describes how to manipulate the actual code memory values to simulate the values that would be read from a protected device. When calculating a checksum by reading a device, the entire code memory can simply be read and summed. The Configuration Words can always be read.

Table 5-9 describes how to calculate the checksum for each device.

| Device                     | Code<br>Protection | Checksum                                                                                                                                                                        |

|----------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIC18F24J10<br>PIC18F44J10 | Off                | SUM[000000:003FF7] + ([003FF8] & E1h) + ([003FF9] & 04h) + ([003FFA] & C7h) + ([003FFB] & 0Fh) + ([003FFD] & 01h)                                                               |

| FIC10F44J10                | On                 | 0000h                                                                                                                                                                           |

| PIC18F24J11<br>PIC18F44J11 | Off                | SUM[000000:003FF7] + ([003FF8] & E1h) + ([003FF9] & FCh) + ([003FFA] & DFh) + ([003FFB] & FFh) + ([003FFC] & FFh) + ([003FFD] & F9h) + ([003FFE] & FFh) + ([003FFF] & F1h)      |

|                            | On                 | 0000h                                                                                                                                                                           |

| PIC18F24J50<br>PIC18F44J50 | Off                | SUM[000000:003FF7] + ([003FF8] & EFh) + ([003FF9] & FFh) + ([003FFA] & DFh) + ([003FFB] & FFh) + ([003FFC] & FFh) + ([003FFF] & F9h) + ([003FFF] & F1h)                         |

|                            | On                 | 0000h                                                                                                                                                                           |

| PIC18F25J10<br>PIC18F45J10 | Off                | SUM[000000:007FF7] + ([007FF8] & E1h) + ([007FF9] & 04h) + ([007FFA] & C7h) + ([007FFB] & 0Fh) + ([007FFD] & 01h)                                                               |

| FIC 10F40J10               | On                 | 0000h                                                                                                                                                                           |

| PIC18F25J11<br>PIC18F45J11 | Off                | SUM[000000:007FF7] + ([007FF8] & E1h) + ([007FF9] & FCh) + ([007FFA] & DFh) + ([007FFB] & FFh) + ([007FFC] & FFh) + ([007FFD] & F9h) + ([007FFE] & FFh) + ([007FFF] & F1h)      |

|                            | On                 | 0000h                                                                                                                                                                           |

| PIC18F25J50<br>PIC18F45J50 | Off                | SUM[000000:007FF7] + ([007FF8] & EFh) + ([007FF9] & FFh) + ([007FFA] & DFh) + ([007FFB] & FFh) + ([007FFC] & FFh) + ([007FFF] & F9h) + ([007FFF] & F1h)                         |

|                            | On                 | 0000h                                                                                                                                                                           |

| PIC18F26J11<br>PIC18F46J11 | Off                | SUM[000000:00FFF7] + ([00FFF8] & E1h) + ([00FFF9] & FCh) + ([00FFFA] & DFh) + ([00FFFB] & FFh) + ([00FFFC] & FFh) + ([00FFFD] & F9h) + ([00FFFF] & F1h)                         |