Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| 2 014110                   |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-VQFN (9x9)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx330f064h-v-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 5: PIN NAMES FOR 100-PIN DEVICES (CONTINUED)

| 100-PIN TQFP | (TOP VIEW) <sup>(1,2)</sup> |

|--------------|-----------------------------|

|--------------|-----------------------------|

PIC32MX430F064L PIC32MX450F128L PIC32MX450F256L PIC32MX470F512L

100

|       |                       |       | 1                   |

|-------|-----------------------|-------|---------------------|

| Pin # | Full Pin Name         | Pin # | Full Pin Name       |

| 71    | RPD11/PMCS1/RD11      | 86    | VDD                 |

| 72    | RPD0/INT0/RD0         | 87    | RPF0/PMD11/RF0      |

| 73    | SOSCI/RPC13/RC13      | 88    | RPF1/PMD10/RF1      |

| 74    | SOSCO/RPC14/T1CK/RC14 | 89    | RPG1/PMD9/RG1       |

| 75    | Vss                   | 90    | RPG0/PMD8/RG0       |

| 76    | AN24/RPD1/RD1         | 91    | TRCLK/RA6           |

| 77    | AN25/RPD2/RD2         | 92    | TRD3/CTED8/RA7      |

| 78    | AN26/RPD3/RD3         | 93    | PMD0/RE0            |

| 79    | RPD12/PMD12/RD12      | 94    | PMD1/RE1            |

| 80    | PMD13/RD13            | 95    | TRD2/RG14           |

| 81    | RPD4/PMWR/RD4         | 96    | TRD1/RG12           |

| 82    | RPD5/PMRD/RD5         | 97    | TRD0/RG13           |

| 83    | PMD14/RD6             | 98    | AN20/CTPLS/PMD2/RE2 |

| 84    | PMD15/RD7             | 99    | RPE3/PMD3/RE3       |

| 85    | VCAP                  | 100   | AN21/PMD4/RE4       |

Note

1:

The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RBx-RGx) can be used as a change notification pin (CNBx-CNGx). See Section 12.0 "I/O Ports" for more information.

Coprocessor 0 also contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including alignment errors in data, external events or program errors. Table 3-3 lists the exception types in order of priority.

| Exception | Description                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Reset     | Assertion MCLR or a Power-on Reset (POR).                                                                                               |

| DSS       | EJTAG debug single step.                                                                                                                |

| DINT      | EJTAG debug interrupt. Caused by the assertion of the external <i>EJ_DINT</i> input or by setting the EjtagBrk bit in the ECR register. |

| NMI       | Assertion of NMI signal.                                                                                                                |

| Interrupt | Assertion of unmasked hardware or software interrupt signal.                                                                            |

| DIB       | EJTAG debug hardware instruction break matched.                                                                                         |

| AdEL      | Fetch address alignment error. Fetch reference to protected address.                                                                    |

| IBE       | Instruction fetch bus error.                                                                                                            |

| DBp       | EJTAG breakpoint (execution of SDBBP instruction).                                                                                      |

| Sys       | Execution of SYSCALL instruction.                                                                                                       |

| Вр        | Execution of BREAK instruction.                                                                                                         |

| RI        | Execution of a reserved instruction.                                                                                                    |

| CpU       | Execution of a coprocessor instruction for a coprocessor that is not enabled.                                                           |

| CEU       | Execution of a CorExtend instruction when CorExtend is not enabled.                                                                     |

| Ov        | Execution of an arithmetic instruction that overflowed.                                                                                 |

| Tr        | Execution of a trap (when trap condition is true).                                                                                      |

| DDBL/DDBS | EJTAG Data Address Break (address only) or EJTAG data value break on store (address + value).                                           |

| AdEL      | Load address alignment error. Load reference to protected address.                                                                      |

| AdES      | Store address alignment error. Store to protected address.                                                                              |

| DBE       | Load or store bus error.                                                                                                                |

| DDBL      | EJTAG data hardware breakpoint matched in load data compare.                                                                            |

# TABLE 3-3: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE EXCEPTION TYPES

# 3.3 Power Management

The MIPS<sup>®</sup> M4K<sup>®</sup> processor core offers a number of power management features, including low-power design, active power management and power-down modes of operation. The core is a static design that supports slowing or Halting the clocks, which reduces system power consumption during Idle periods.

### 3.3.1 INSTRUCTION-CONTROLLED POWER MANAGEMENT

The mechanism for invoking Power-Down mode is through execution of the WAIT instruction. For more information on power management, see Section 27.0 "Power-Saving Features".

### 3.3.2 LOCAL CLOCK GATING

The majority of the power consumed by the PIC32MX330/350/370/430/450/470 family core is in the clock tree and clocking registers. The PIC32MX family uses extensive use of local gated-clocks to reduce this dynamic power consumption.

# 3.4 EJTAG Debug Support

The MIPS<sup>®</sup> M4K<sup>®</sup> processor core provides for an Enhanced JTAG (EJTAG) interface for use in the software debug of application and kernel code. In addition to standard User mode and Kernel modes of operation, the M4K<sup>®</sup> core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification define which registers are selected and how they are used. NOTES:

## TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION

| Internet Course(1)                  | IDO # | Vector |              | Persistent   |             |              |           |

|-------------------------------------|-------|--------|--------------|--------------|-------------|--------------|-----------|

| Interrupt Source <sup>(1)</sup>     | IRQ # | #      | Flag         | Enable       | Priority    | Sub-priority | Interrupt |

|                                     |       | Highe  | st Natural O | der Priority |             |              |           |

| CT – Core Timer Interrupt           | 0     | 0      | IFS0<0>      | IEC0<0>      | IPC0<4:2>   | IPC0<1:0>    | No        |

| CS0 – Core Software Interrupt 0     | 1     | 1      | IFS0<1>      | IEC0<1>      | IPC0<12:10> | IPC0<9:8>    | No        |

| CS1 – Core Software Interrupt 1     | 2     | 2      | IFS0<2>      | IEC0<2>      | IPC0<20:18> | IPC0<17:16>  | No        |

| INT0 – External Interrupt           | 3     | 3      | IFS0<3>      | IEC0<3>      | IPC0<28:26> | IPC0<25:24>  | No        |

| T1 – Timer1                         | 4     | 4      | IFS0<4>      | IEC0<4>      | IPC1<4:2>   | IPC1<1:0>    | No        |

| IC1E – Input Capture 1 Error        | 5     | 5      | IFS0<5>      | IEC0<5>      | IPC1<12:10> | IPC1<9:8>    | Yes       |

| IC1 – Input Capture 1               | 6     | 5      | IFS0<6>      | IEC0<6>      | IPC1<12:10> | IPC1<9:8>    | Yes       |

| OC1 – Output Compare 1              | 7     | 6      | IFS0<7>      | IEC0<7>      | IPC1<20:18> | IPC1<17:16>  | No        |

| INT1 – External Interrupt 1         | 8     | 7      | IFS0<8>      | IEC0<8>      | IPC1<28:26> | IPC1<25:24>  | No        |

| T2 – Timer2                         | 9     | 8      | IFS0<9>      | IEC0<9>      | IPC2<4:2>   | IPC2<1:0>    | No        |

| IC2E – Input Capture 2              | 10    | 9      | IFS0<10>     | IEC0<10>     | IPC2<12:10> | IPC2<9:8>    | Yes       |

| IC2 – Input Capture 2               | 11    | 9      | IFS0<11>     | IEC0<11>     | IPC2<12:10> | IPC2<9:8>    | Yes       |

| OC2 – Output Compare 2              | 12    | 10     | IFS0<12>     | IEC0<12>     | IPC2<20:18> | IPC2<17:16>  | No        |

| INT2 – External Interrupt 2         | 13    | 11     | IFS0<13>     | IEC0<13>     | IPC2<28:26> | IPC2<25:24>  | No        |

| T3 – Timer3                         | 14    | 12     | IFS0<14>     | IEC0<14>     | IPC3<4:2>   | IPC3<1:0>    | No        |

| IC3E – Input Capture 3              | 15    | 13     | IFS0<15>     | IEC0<15>     | IPC3<12:10> | IPC3<9:8>    | Yes       |

| IC3 – Input Capture 3               | 16    | 13     | IFS0<16>     | IEC0<16>     | IPC3<12:10> | IPC3<9:8>    | Yes       |

| OC3 – Output Compare 3              | 17    | 14     | IFS0<17>     | IEC0<17>     | IPC3<20:18> | IPC3<17:16>  | No        |

| INT3 – External Interrupt 3         | 18    | 15     | IFS0<18>     | IEC0<18>     | IPC3<28:26> | IPC3<25:24>  | No        |

| T4 – Timer4                         | 19    | 16     | IFS0<19>     | IEC0<19>     | IPC4<4:2>   | IPC4<1:0>    | No        |

| IC4E – Input Capture 4 Error        | 20    | 17     | IFS0<20>     | IEC0<20>     | IPC4<12:10> | IPC4<9:8>    | Yes       |

| IC4 – Input Capture 4               | 21    | 17     | IFS0<21>     | IEC0<21>     | IPC4<12:10> | IPC4<9:8>    | Yes       |

| OC4 – Output Compare 4              | 22    | 18     | IFS0<22>     | IEC0<22>     | IPC4<20:18> | IPC4<17:16>  | No        |

| INT4 – External Interrupt 4         | 23    | 19     | IFS0<23>     | IEC0<23>     | IPC4<28:26> | IPC4<25:24>  | No        |

| T5 – Timer5                         | 24    | 20     | IFS0<24>     | IEC0<24>     | IPC5<4:2>   | IPC5<1:0>    | No        |

| IC5E – Input Capture 5 Error        | 25    | 21     | IFS0<25>     | IEC0<25>     | IPC5<12:10> | IPC5<9:8>    | Yes       |

| IC5 – Input Capture 5               | 26    | 21     | IFS0<26>     | IEC0<26>     | IPC5<12:10> | IPC5<9:8>    | Yes       |

| OC5 – Output Compare 5              | 27    | 22     | IFS0<27>     | IEC0<27>     | IPC5<20:18> | IPC5<17:16>  | No        |

| AD1 – ADC1 Convert done             | 28    | 23     | IFS0<28>     | IEC0<28>     | IPC5<28:26> | IPC5<25:24>  | Yes       |

| FSCM – Fail-Safe Clock Monitor      | 29    | 24     | IFS0<29>     | IEC0<29>     | IPC6<4:2>   | IPC6<1:0>    | No        |

| RTCC – Real-Time Clock and Calendar | 30    | 25     | IFS0<30>     | IEC0<30>     | IPC6<12:10> | IPC6<9:8>    | No        |

| FCE – Flash Control Event           | 31    | 26     | IFS0<31>     | IEC0<31>     | IPC6<20:18> | IPC6<17:16>  | No        |

| CMP1 – Comparator Interrupt         | 32    | 27     | IFS1<0>      | IEC1<0>      | IPC6<28:26> | IPC6<25:24>  | No        |

| CMP2 – Comparator Interrupt         | 33    | 28     | IFS1<1>      | IEC1<1>      | IPC7<4:2>   | IPC7<1:0>    | No        |

| USB – USB Interrupts                | 34    | 29     | IFS1<2>      | IEC1<2>      | IPC7<12:10> | IPC7<9:8>    | Yes       |

| SPI1E – SPI1 Fault                  | 35    | 30     | IFS1<3>      | IEC1<3>      | IPC7<20:18> | IPC7<17:16>  | Yes       |

| SPI1RX – SPI1 Receive Done          | 36    | 30     | IFS1<4>      | IEC1<4>      | IPC7<20:18> | IPC7<17:16>  | Yes       |

| SPI1TX – SPI1 Transfer Done         | 37    | 30     | IFS1<5>      | IEC1<5>      | IPC7<20:18> | IPC7<17:16>  | Yes       |

| U1E – UART1 Fault                   | 38    | 31     | IFS1<6>      | IEC1<6>      | IPC7<28:26> | IPC7<25:24>  | Yes       |

| U1RX – UART1 Receive Done           | 39    | 31     | IFS1<7>      | IEC1<7>      | IPC7<28:26> | IPC7<25:24>  | Yes       |

| U1TX – UART1 Transfer Done          | 40    | 31     | IFS1<8>      | IEC1<8>      | IPC7<28:26> | IPC7<25:24>  | Yes       |

| I2C1B – I2C1 Bus Collision Event    | 41    | 32     | IFS1<9>      | IEC1<9>      | IPC8<4:2>   | IPC8<1:0>    | Yes       |

| I2C1S – I2C1 Slave Event            | 42    | 32     | IFS1<10>     | IEC1<10>     | IPC8<4:2>   | IPC8<1:0>    | Yes       |

| I2C1M – I2C1 Master Event           | 43    | 32     | IFS1<11>     | IEC1<11>     | IPC8<4:2>   | IPC8<1:0>    | Yes       |

| CNA – PORTA Input Change Interrupt  | 44    | 33     | IFS1<12>     | IEC1<12>     | IPC8<12:10> | IPC8<9:8>    | Yes       |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX330/350/370/430/450/470 Controller Family Features" for the list of available peripherals.

| TABLE 7-2: IN | ITERRUPT REGISTER | MAP (CONTINUED) |

|---------------|-------------------|-----------------|

|---------------|-------------------|-----------------|

| ess                         |                  | <sup>0</sup> |       |       |       |       |              |              |           | Bits             |           |      |           |             |           |             |             |             |               |      |           |       |           |  |           |  |           |  |           |  |           |  |         |  |           |  |   |   |   |    |            |  |        |        |      |

|-----------------------------|------------------|--------------|-------|-------|-------|-------|--------------|--------------|-----------|------------------|-----------|------|-----------|-------------|-----------|-------------|-------------|-------------|---------------|------|-----------|-------|-----------|--|-----------|--|-----------|--|-----------|--|-----------|--|---------|--|-----------|--|---|---|---|----|------------|--|--------|--------|------|

| Virtual Address<br>(BF88_#) | Register<br>Name | Bit Range    | 31/15 | 30/14 | 29/13 | 28/12 | 27/11        | 26/10        | 25/9      | 24/8             | 23/7      | 22/6 | 21/5      | 20/4        | 19/3      | 18/2        | 17/1        | 16/0        | All<br>Resets |      |           |       |           |  |           |  |           |  |           |  |           |  |         |  |           |  |   |   |   |    |            |  |        |        |      |

| 10F0                        | IPC6             | 31:16        | _     | _     | —     | (     | CMP1IP<2:0   | >            | CMP1IS    | S<1:0>           | _         | _    | —         | F           | CEIP<2:0> |             | FCEIS       | S<1:0>      | 0000          |      |           |       |           |  |           |  |           |  |           |  |           |  |         |  |           |  |   |   |   |    |            |  |        |        |      |

| 101.0                       | IF CO            | 15:0         | —     | _     | —     |       | RTCCIP<2:0   | >            | RTCCIS    | S<1:0>           | _         | _    | —         | FS          | SCMIP<2:0 | >           | FSCMIS<1:0> |             | 0000          |      |           |       |           |  |           |  |           |  |           |  |           |  |         |  |           |  |   |   |   |    |            |  |        |        |      |

| 1100                        | IPC7             | 31:16        |       | _     | _     |       | U1IP<2:0>    | J1IP<2:0> U1 |           | <1:0>            | _         | _    | _         | SPI1IP<2:0> |           | SPI1IP<2:0> |             | SPI1IS<1:0> |               | 0000 |           |       |           |  |           |  |           |  |           |  |           |  |         |  |           |  |   |   |   |    |            |  |        |        |      |

| 1100                        | IPC7             | 15:0         |       | _     | _     | ι     | JSBIP<2:0>(2 | 2)           | USBIS<    | :1:0> <b>(2)</b> | _         | _    | _         | CI          | MP2IP<2:0 | >           | CMP2        | S<1:0>      | 0000          |      |           |       |           |  |           |  |           |  |           |  |           |  |         |  |           |  |   |   |   |    |            |  |        |        |      |

| 1110                        | IPC8             | 31:16        | _     | —     | —     |       | SPI2IP<2:0>  |              | SPI2IS    | <1:0>            | _         | _    | —         | PMPIP<2:0>  |           |             | PMPIS<1:0>  |             | 0000          |      |           |       |           |  |           |  |           |  |           |  |           |  |         |  |           |  |   |   |   |    |            |  |        |        |      |

| 1110                        | IPCo             | 15:0         | _     | —     | —     |       | CNIP<2:0>    |              | CNIP<2:0> |                  | CNIP<2:0> |      | CNIP<2:0> |             | CNIP<2:0> |             | CNIP<2:0>   |             | CNIP<2:0>     |      | CNIP<2:0> |       | CNIP<2:0> |  | CNIP<2:0> |  | CNIP<2:0> |  | CNIP<2:0> |  | CNIP<2:0> |  | CNIS<1: |  | CNIS<1:0> |  | _ | _ | — | 12 | 2C1IP<2:0> |  | 12C115 | 6<1:0> | 0000 |

| 1100                        | IPC9             | 31:16        | _     | _     | _     |       | U4IP<2:0>    |              | U4IP<2:0> |                  | U4IP<2:0> |      | U4IS<     | <1:0>       | _         | _           | —           | l           | J3IP<2:0>     |      | U3IS-     | <1:0> | 0000      |  |           |  |           |  |           |  |           |  |         |  |           |  |   |   |   |    |            |  |        |        |      |

| 1120                        | IPC9             | 15:0         |       | _     | _     |       | I2C2IP<2:0>  |              | I2C2IS    | <1:0>            | _         | _    | _         | l           | J2IP<2:0> |             | U2IS-       | <1:0>       | 0000          |      |           |       |           |  |           |  |           |  |           |  |           |  |         |  |           |  |   |   |   |    |            |  |        |        |      |

| 1120                        | IPC10            | 31:16        | _     | —     | —     | I     | DMA1IP<2:0   | >            | DMA1IS    | S<1:0>           | _         | _    | —         | DI          | MA0IP<2:0 | >           | DMA0        | S<1:0>      | 0000          |      |           |       |           |  |           |  |           |  |           |  |           |  |         |  |           |  |   |   |   |    |            |  |        |        |      |

| 1130                        | IPCIU            | 15:0         | _     | _     | _     | (     | CTMUIP<2:0   | >            | CTMU      | S<1:0>           | _         | _    | —         | l           | J5IP<2:0> |             | U5IS-       | <1:0>       | 0000          |      |           |       |           |  |           |  |           |  |           |  |           |  |         |  |           |  |   |   |   |    |            |  |        |        |      |

| 11.10                       | IPC11            | 31:16        | _     | —     | —     | —     | —            | —            | —         | —                | _         | _    | —         | —           | —         | —           | _           | _           | 0000          |      |           |       |           |  |           |  |           |  |           |  |           |  |         |  |           |  |   |   |   |    |            |  |        |        |      |

| 1140                        | IPUTT            | 15:0         | _     | -     |       |       | DMA3IP<2:0   | >            | DMA3IS    | S<1:0>           | _         | _    | _         | DI          | MA2IP<2:0 | >           | DMA2I       | S<1:0>      | 0000          |      |           |       |           |  |           |  |           |  |           |  |           |  |         |  |           |  |   |   |   |    |            |  |        |        |      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This bit is only available on 100-pin devices.

2: This bit is only implemented on devices with a USB module.

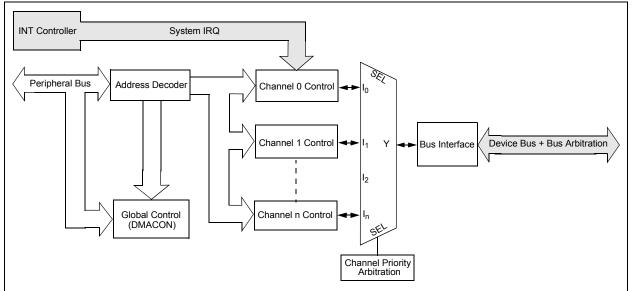

# 10.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 31. "Direct Memory Access (DMA) Controller" (DS60001117), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32 Direct Memory Access (DMA) controller is a bus master module useful for data transfers between different devices without CPU intervention. The source and destination of a DMA transfer can be any of the memory mapped modules existent in the PIC32 (such as Peripheral Bus (PBUS) devices: SPI, UART, PMP, etc.) or memory itself.

Following are some of the key features of the DMA controller module:

- Four identical channels, each featuring:

- Auto-increment source and destination address registers

- Source and destination pointers

- Memory to memory and memory to peripheral transfers

- Automatic word-size detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source and destination

- Fixed priority channel arbitration

- · Flexible DMA channel operating modes:

- Manual (software) or automatic (interrupt) DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- · Flexible DMA requests:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any (appropriate) observable interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Pattern (data) match transfer termination

- · Multiple DMA channel status interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- DMA debug support features:

- Most recent address accessed by a DMA channel

- Most recent DMA channel to transfer data

- · CRC Generation module:

- CRC module can be assigned to any of the available channels

- CRC module is highly configurable

# FIGURE 10-1: DMA BLOCK DIAGRAM

## TABLE 10-3: DMA CHANNEL 0 THROUGH CHANNEL 3 REGISTER MAP (CONTINUED)

| ess                         |                                 |               |            |             |            |              |              |            |            | Bi     | ts                   |        |        |                  |                  |        |        |        |            |

|-----------------------------|---------------------------------|---------------|------------|-------------|------------|--------------|--------------|------------|------------|--------|----------------------|--------|--------|------------------|------------------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15      | 30/14       | 29/13      | 28/12        | 27/11        | 26/10      | 25/9       | 24/8   | 23/7                 | 22/6   | 21/5   | 20/4             | 19/3             | 18/2   | 17/1   | 16/0   | All Resets |

| 3170                        | DCH1SSIZ                        | 31:16         | _          | _           | _          | _            |              | _          | _          | _      |                      | —      | _      | _                | —                | _      | _      |        | 0000       |

| 0170                        | DOITIOOIZ                       | 15:0          |            |             |            |              |              |            |            | CHSSIZ | 2<15:0>              | t      |        |                  | i                |        | i      |        | 0000       |

| 3180                        | DCH1DSIZ                        | 31:16         | —          | —           | —          | _            | —            | —          | —          | —      | —                    | —      | —      | —                | —                | —      | —      | —      | 0000       |

| 0100                        | DOITIDOIL                       | 15:0          |            |             |            |              |              |            |            | CHDSIZ | 2<15:0>              |        |        |                  |                  |        |        |        | 0000       |

| 3190                        | DCH1SPTR                        | 31:16         | —          | —           | _          | —            | —            | —          | _          | —      | —                    | —      | _      | —                | —                | _      | —      | —      | 0000       |

|                             |                                 | 15:0          |            |             |            |              |              |            |            | CHSPT  | R<15:0>              |        |        |                  |                  |        |        |        | 0000       |

| 31A0                        | DCH1DPTR                        | 31:16         | —          | —           | —          | —            | —            | —          | —          | —      | —                    | —      | —      | —                | —                | —      | —      | —      | 0000       |

|                             |                                 | 15:0          |            |             |            |              |              |            |            | CHDPTI | R<15:0>              |        |        |                  |                  |        |        |        | 0000       |

| 31B0                        | DCH1CSIZ                        | 31:16         | _          | _           | —          |              | _            | —          | _          | —      | _                    | —      | _      | —                | _                | —      | —      | _      | 0000       |

|                             |                                 | 15:0          |            |             |            |              |              |            |            | CHCSIZ | 2<15:0>              |        |        |                  |                  |        |        |        | 0000       |

| 31C0                        | DCH1CPTR                        | 31:16         | _          | _           | —          | —            | _            | —          | _          | —      | —                    | —      | _      | —                | —                | —      | —      | _      | 0000       |

|                             |                                 | 15:0          |            |             |            |              |              |            |            | CHCPTI | ≺<15:0>              |        |        |                  |                  |        |        |        | 0000       |

| 31D0                        | DCH1DAT                         | 31:16         | _          | _           |            |              | _            |            |            | _      | _                    | —      | _      |                  |                  | _      | —      | _      | 0000       |

|                             |                                 | 15:0          |            | _           |            | _            | _            |            |            | _      |                      |        |        | CHPDA            |                  |        |        |        | 0000       |

| 31E0                        | DCH2CON                         | 31:16         | —          | _           |            | _            | _            |            |            | —      | -                    | -      | —      | —                | _                | -      | _      |        | 0000       |

| -                           |                                 | 15:0          | CHBUSY     | _           | _          | _            | _            | _          |            | CHCHNS | CHEN                 | CHAED  | CHCHN  | CHAEN            |                  | CHEDET | CHPR   | 1<1:0> | 0000       |

| 31F0                        | DCH2ECON                        | 31:16         | —          | _           | _          |              | -            | _          | _          | _      | CFORCE               | CABORT | PATEN  | CHAIR            |                  |        |        |        | 00FF       |

|                             |                                 | 15:0          |            |             |            | CHSIR        |              |            |            |        | CHSDIE               | CABORT | CHDDIE | SIRQEN<br>CHDHIE | AIRQEN<br>CHBCIE |        |        |        | FFF8       |

| 3200                        | DCH2INT                         | 31:16<br>15:0 | —          | _           | _          | _            | _            | _          | _          | _      | CHSDIE               | CHSHIE | CHDDIE | CHDHIE           | CHBCIE           | CHCCIE | CHTAIE | CHERIE | 0000       |

| -                           |                                 | 31:16         | —          | _           | _          | _            | _            | _          | —          | —      | CHODIF               | CHONIF | CHUDIF | CHDHIF           | CUBCIL           | CHCCIF | CHIAIF | CHERIF | 0000       |

| 3210                        | DCH2SSA                         | 15:0          |            |             |            |              |              |            |            | CHSSA  | <31:0>               |        |        |                  |                  |        |        |        | 0000       |

| -                           |                                 | 31:16         |            |             |            |              |              |            |            |        |                      |        |        |                  |                  |        |        |        | 0000       |

| 3220                        | DCH2DSA                         | 15:0          |            |             |            |              |              |            |            | CHDSA  | <31:0>               |        |        |                  |                  |        |        |        | 0000       |

|                             |                                 | 31:16         | _          | _           | _          | _            | _            | _          | _          | _      | _                    |        | _      | _                | _                | _      | _      | _      | 0000       |

| 3230                        | DCH2SSIZ                        | 15:0          |            |             |            |              |              |            |            | CHSSIZ | /<15 <sup>.</sup> 0> |        |        |                  |                  |        |        |        | 0000       |

|                             |                                 | 31:16         | _          | _           | _          | _            | _            | _          | _          | _      |                      | _      | _      | _                | _                | _      | _      | _      | 0000       |

| 3240                        | DCH2DSIZ                        | 15:0          |            |             |            |              |              |            |            | CHDSIZ | /<15 <sup>.</sup> 0> |        |        |                  |                  |        |        |        | 0000       |

|                             |                                 | 31:16         | _          |             | _          |              |              | _          |            | _      |                      |        | _      | _                |                  |        |        |        | 0000       |

| 3250                        | DCH2SPTR                        | 15:0          |            |             |            |              |              |            |            | CHSPT  | R<15:0>              |        |        |                  |                  |        |        |        | 0000       |

|                             |                                 | 31:16         | _          |             | _          |              |              | _          |            | _      | _                    |        | _      | _                |                  |        |        | _      | 0000       |

| 3260                        | DCH2DPTR                        | 15:0          |            |             |            |              |              |            |            | CHDPT  | R<15:0>              |        |        |                  |                  |        |        |        | 0000       |

|                             |                                 | 31:16         | _          |             |            |              |              | _          |            | _      | _                    |        | _      | _                |                  |        |        |        | 0000       |

| 3270                        | DCH2CSIZ                        | 15:0          |            |             |            |              |              |            |            | CHCSIZ | 2<15:0>              |        |        |                  |                  |        |        |        | 0000       |

| Leger                       | <b>d:</b> x = 11                |               | value on R | eset: — = I | unimplemer | nted, read a | s '0'. Reset | values are | shown in h |        |                      |        |        |                  |                  |        |        |        |            |

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|----------------------|----------------------|-------------------|-------------------|------------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |

| 31.24        | -                 | -                 | -                    | -                    | —                 | -                 | —                      |                  |

| 23:16        | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |

| 23.10        | -                 |                   | -                    |                      |                   |                   | —                      |                  |

| 15:8         | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |

| 15.6         | -                 | -                 | -                    | -                    | —                 | -                 | —                      | -                |

|              | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS           | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS             | R/WC-0, HS       |

| 7:0          | BTSEF             | BMXEF             | DMAEF <sup>(1)</sup> | BTOEF <sup>(2)</sup> | DFN8EF            | CRC16EF           | CRC5EF <sup>(4)</sup>  | PIDEF            |

|              | DISEF             | DIVIAEF           | DIVIAEL, ,           | BIVEF                | DENOER            | GRUIDEF           | EOFEF <sup>(3,5)</sup> | FIDEF            |

### REGISTER 11-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable bit |                    |  |  |  |

|-------------------|-------------------------|----------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, re  | ad as '0'          |  |  |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared       | x = Bit is unknown |  |  |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 BTSEF: Bit Stuff Error Flag bit

- 1 = Packet is rejected due to bit stuff error

- 0 = Packet is accepted

- bit 6 BMXEF: Bus Matrix Error Flag bit

1 = The base address, of the BDT, or the address of an individual buffer pointed to by a BDT entry, is invalid.

0 = No address error

- bit 5 **DMAEF:** DMA Error Flag bit<sup>(1)</sup> 1 = USB DMA error condition detected

- 0 = No DMA error

- bit 4 **BTOEF:** Bus Turnaround Time-Out Error Flag bit<sup>(2)</sup>

- 1 = Bus turnaround time-out has occurred

- 0 = No bus turnaround time-out

#### bit 3 **DFN8EF:** Data Field Size Error Flag bit

- 1 = Data field received is not an integral number of bytes

- 0 = Data field received is an integral number of bytes

#### bit 2 CRC16EF: CRC16 Failure Flag bit

- 1 = Data packet rejected due to CRC16 error

- 0 = Data packet accepted

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- **2:** This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

## TABLE 12-2: OUTPUT PIN SELECTION (CONTINUED)

| RPn Port Pin         | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection        |

|----------------------|----------|-------------|----------------------------------------------|

| RPD9                 | RPD9R    | RPD9R<3:0>  | 0000 = No Connect                            |

| RPG6                 | RPG6R    | RPG6R<3:0>  | 0001 = U3RTS                                 |

| RPB8                 | RPB8R    | RPB8R<3:0>  | 0010 = U4TX                                  |

| RPB15                | RPB15R   | RPB15R<3:0> | 0011 = REFCLKO<br>0100 = U5TX <sup>(4)</sup> |

| RPD4                 | RPD4R    | RPD4R<3:0>  | 0100 = 001 x 0                               |

| RPB0                 | RPB0R    | RPB0R<3:0>  | 0110 = Reserved                              |

| RPE3                 | RPE3R    | RPE3R<3:0>  | 0111 = <u>SS1</u>                            |

| RPB7                 | RPB7R    | RPB7R<3:0>  | 1000 = SDO1                                  |

| RPB2                 | RPB2R    | RPB2R<3:0>  | 1001 = Reserved                              |

| RPF12 <sup>(4)</sup> | RPF12R   | RPF12R<3:0> | 1010 = Reserved                              |

| RPD12 <sup>(4)</sup> | RPD12R   | RPD12R<3:0> |                                              |

| RPF8 <sup>(4)</sup>  | RPF8R    | RPF8R<3:0>  | 1100 - Reserved                              |

| RPC3 <sup>(4)</sup>  | RPC3R    | RPC3R<3:0>  | 1110 = Reserved                              |

| RPE9 <sup>(4)</sup>  | RPE9R    | RPE9R<3:0>  | 1111 = Reserved                              |

| RPD1                 | RPD1R    | RPD1R<3:0>  | 0000 = No Connect                            |

| RPG9                 | RPG9R    | RPG9R<3:0>  | 0001 = U2RTS                                 |

| RPB14                | RPB14R   | RPB14R<3:0> | 0010 = Reserved<br>0011 = U1RTS              |

| RPD0                 | RPD0R    | RPD0R<3:0>  | $0100 = U5TX^{(4)}$                          |

| RPD8                 | RPD8R    | RPD8R<3:0>  | 0101 = Reserved                              |

| RPB6                 | RPB6R    | RPB6R<3:0>  | 0110 = <u>SS2</u>                            |

| RPD5                 | RPD5R    | RPD5R<3:0>  | 0111 = Reserved<br>1000 = SDO1               |

| RPF3 <sup>(3)</sup>  | RPF3R    | RPF3R<3:0>  | 1000 = SDOT                                  |

| RPF6 <sup>(1)</sup>  | RPF6R    | RPF6R<3:0>  | 1010 = Reserved                              |

| RPF13 <sup>(4)</sup> | RPF13R   | RPF13R<3:0> | 1011 = OC2                                   |

| RPC2 <sup>(4)</sup>  | RPC2R    | RPC2R<3:0>  | 1100 = OC1<br>1101 = Reserved                |

| RPE8 <sup>(4)</sup>  | RPE8R    | RPE8R<3:0>  | 1110 = Reserved                              |

| RPF2 <sup>(5)</sup>  | RPF2R    | RPF2R<3:0>  | 1111 = Reserved                              |

**Note 1:** This selection is only available on General Purpose devices.

**2:** This selection is only available on 64-pin General Purpose devices.

3: This selection is only available on 100-pin General Purpose devices.

4: This selection is only available on 100-pin USB and General Purpose devices.

5: This selection is not available on 64-pin USB devices.

| Bit<br>Range | Bit<br>31/23/15/7 |     |       | Bit Bit<br>29/21/13/5 28/20/12/4 |     | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-----|-------|----------------------------------|-----|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0 | U-0   | U-0                              | U-0 | U-0               | U-0              | U-0              |

| 31:24        | -                 | _   | _     | _                                | _   |                   | _                | _                |

| 00.40        | U-0               | U-0 | U-0   | U-0                              | U-0 | U-0               | U-0              | U-0              |

| 23:16        | -                 | _   | —     | -                                | _   | _                 | _                | —                |

| 15.0         | R/W-0             | U-0 | R/W-0 | U-0                              | U-0 | U-0               | U-0              | U-0              |

| 15:8         | ON                | _   | SIDL  | _                                | _   |                   | _                | —                |

| 7.0          | U-0               | U-0 | U-0   | U-0                              | U-0 | U-0               | U-0              | U-0              |

| 7:0          | _                 |     | _     | _                                | _   | _                 | _                |                  |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Change Notice (CN) Control ON bit

- 1 = CN is enabled

- 0 = CN is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Control bit

- 1 = CPU Idle Mode halts CN operation

- 0 = CPU Idle does not affect CN operation

- bit 12-0 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 |                   | _                 | _                 | _                 | _                | —                |

| 23:16        | U-0               | U-0 U-0           |                   | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | _                 |                   |                   | _                 | _                 | _                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R-0               | U-0               | U-0              | U-0              |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | TWDIS             | TWIP              | _                 | _                | —                |

| 7.0          | R/W-0             | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0            | U-0              |

| 7:0          | TGATE             |                   | TCKPS             | S<1:0>            | _                 | TSYNC             | TCS              | _                |

### REGISTER 13-1: T1CON: TYPE A TIMER CONTROL REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

| DIL 31-10 | ommplemented: Read as 0                                                                                                                                                        |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | ON: Timer On bit <sup>(1)</sup>                                                                                                                                                |

|           | 1 = Timer is enabled                                                                                                                                                           |

|           | 0 = Timer is disabled                                                                                                                                                          |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                     |

| bit 13    | SIDL: Stop in Idle Mode bit                                                                                                                                                    |

|           | <ul><li>1 = Discontinue operation when device enters Idle mode</li><li>0 = Continue operation even in Idle mode</li></ul>                                                      |

| bit 12    | TWDIS: Asynchronous Timer Write Disable bit                                                                                                                                    |

|           | <ul><li>1 = Writes to TMR1 are ignored until pending write operation completes</li><li>0 = Back-to-back writes are enabled (Legacy Asynchronous Timer functionality)</li></ul> |

| bit 11    | TWIP: Asynchronous Timer Write in Progress bit                                                                                                                                 |

|           | In Asynchronous Timer mode:                                                                                                                                                    |

|           | 1 = Asynchronous write to TMR1 register in progress                                                                                                                            |

|           | 0 = Asynchronous write to TMR1 register complete                                                                                                                               |

|           | In Synchronous Timer mode:<br>This bit is read as '0'.                                                                                                                         |

| bit 10-8  | Unimplemented: Read as '0'                                                                                                                                                     |

| bit 7     | TGATE: Timer Gated Time Accumulation Enable bit                                                                                                                                |

|           | When TCS = 1:                                                                                                                                                                  |

|           | This bit is ignored.                                                                                                                                                           |

|           | When TCS = 0:<br>1 = Gated time accumulation is enabled                                                                                                                        |

|           | 0 = Gated time accumulation is disabled                                                                                                                                        |

| bit 6     | Unimplemented: Read as '0'                                                                                                                                                     |

| bit 5-4   | TCKPS<1:0>: Timer Input Clock Prescale Select bits                                                                                                                             |

|           | 11 = 1:256 prescale value                                                                                                                                                      |

|           | 10 = 1:64 prescale value                                                                                                                                                       |

|           | 01 = 1:8 prescale value<br>00 = 1:1 prescale value                                                                                                                             |

| bit 3     |                                                                                                                                                                                |

| DILO      | Unimplemented: Read as '0'                                                                                                                                                     |

|           |                                                                                                                                                                                |

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 20-1: UxMODE: UARTx MODE REGISTER

| Bit<br>Range | Bit Bit<br>31/23/15/7 30/22/14/6 |        | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|----------------------------------|--------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0                              | U-0    | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                                  | —      | _                 | _                 | _                 | —                 | —                | —                |

| 22:16        | U-0                              | U-0    | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                                | —      | _                 | _                 | —                 | -                 | —                | —                |

| 45.0         | R/W-0                            | U-0    | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 15:8         | 0N <sup>(1)</sup>                | —      | SIDL              | IREN              | RTSMD             | _                 | UEN              | <1:0>            |

| 7.0          | R/W-0                            | R/W-0  | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | WAKE                             | LPBACK | ABAUD             | RXINV             | BRGH              | PDSEL             | <1:0>            | STSEL            |

## Legend:

| Legena.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** UARTx Enable bit<sup>(1)</sup>

- 1 = UARTx is enabled. UARTx pins are controlled by UARTx as defined by UEN<1:0> and UTXEN control bits

- UARTx is disabled. All UARTx pins are controlled by corresponding bits in the PORTx, TRISx and LATx registers; UARTx power consumption is minimal

#### bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when device enters Idle mode

- 0 = Continue operation in Idle mode

- bit 12 IREN: IrDA Encoder and Decoder Enable bit

- 1 = IrDA is enabled

- 0 = IrDA is disabled

- bit 11 **RTSMD:** Mode Selection for UxRTS Pin bit

- 1 =  $\overline{\text{UxRTS}}$  pin is in Simplex mode

- $0 = \overline{\text{UxRTS}}$  pin is in Flow Control mode

#### bit 10 Unimplemented: Read as '0'

#### bit 9-8 UEN<1:0>: UARTx Enable bits

- 11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 10 = UxTX, UxRX,  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins are enabled and used

- 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register

- bit 7 WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit

- 1 = Wake-up is enabled

- 0 = Wake-up is disabled

- bit 6 LPBACK: UARTx Loopback Mode Select bit

- 1 = Loopback mode is enabled

- 0 = Loopback mode is disabled

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

# 22.1 Control Registers

## TABLE 22-1: RTCC REGISTER MAP

| ess                         |                                 | 0         |        |       |         |          |             |                      |        |              | Bits     |          |              |      |         |         |         |       | 8         |

|-----------------------------|---------------------------------|-----------|--------|-------|---------|----------|-------------|----------------------|--------|--------------|----------|----------|--------------|------|---------|---------|---------|-------|-----------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15  | 30/14 | 29/13   | 28/12    | 27/11       | 26/10                | 25/9   | 24/8         | 23/7     | 22/6     | 21/5         | 20/4 | 19/3    | 18/2    | 17/1    | 16/0  | All Reset |

| 0200                        | RTCCON                          | 31:16     | _      | _     | _       | -        | _           | -                    |        |              |          |          | CAL<         | 9:0> |         |         |         |       | 0000      |

| 0200                        | RICCON                          | 15:0      | ON     | _     | SIDL    | —        | _           | -                    |        | _            | RTSECSEL | RTCCLKON | _            | _    | RTCWREN | RTCSYNC | HALFSEC | RTCOE | 0000      |

| 0210                        |                                 | 31:16     | —      | _     | _       | —        | _           | -                    |        | _            | —        | _        | _            | _    | —       | _       | —       | —     | 0000      |

| 0210                        |                                 | 15:0      | ALRMEN | CHIME | PIV     | ALRMSYNC |             | AMASK<3:0> ARPT<7:0> |        |              |          |          |              | 0000 |         |         |         |       |           |

| 0220                        | 3                               | 31:16     |        | HR10  | 0<3:0>  |          | HR01<3:0>   |                      |        |              | MIN10<   | 3:0>     |              |      | MIN01   | <3:0>   |         | xxxx  |           |

| 0220                        |                                 | 15:0      |        | SEC1  | 0<3:0>  |          | SEC01<3:0>  |                      |        |              |          |          | _            |      |         |         | xx00    |       |           |

| 0230                        | RTCDATE                         | 31:16     |        | YEAR  | 10<3:0> |          | YEAR01<3:0> |                      |        | MONTH10<3:0> |          |          | MONTH01<3:0> |      |         |         | xxxx    |       |           |

| 0230                        | RIODAIL                         | 15:0      |        | DAY1  | 0<3:0>  |          |             | DAY01                | 1<3:0> |              | —        | _        | _            | _    |         | WDAY0   | 1<3:0>  |       | xx00      |

| 0240                        |                                 | 31:16     |        | HR10  | 0<3:0>  |          |             | HR01                 | <3:0>  |              |          | MIN10<   | 3:0>         |      |         | MIN01   | <3:0>   |       | xxxx      |

| 0240                        | 240 ALRMTIME                    | 15:0      |        | SEC1  | 0<3:0>  |          |             | SEC07                | 1<3:0> |              | —        | _        | _            | _    | _       | —       | —       | —     | xx00      |

| 0250                        | 250 ALRMDATE                    | 31:16     | —      | _     | _       | _        | —           | —                    | _      | _            |          | MONTH10  | <3:0>        |      |         | MONTH   | 01<3:0> |       | 00xx      |

| 0200                        |                                 | 15:0      |        | DAY1  | 0<3:0>  |          |             | DAY01                | 1<3:0> |              | —        | _        | _            | _    |         | WDAY0   | 1<3:0>  |       | xx0x      |

PIC32MX330/350/370/430/450/470

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

# TABLE 23-1: ADC REGISTER MAP (CONTINUED)

| ess                         |                  | 0             |                                    | Bits                                         |       |       |       |       |         |            |          |          |      |      | ŝ    |      |      |      |            |

|-----------------------------|------------------|---------------|------------------------------------|----------------------------------------------|-------|-------|-------|-------|---------|------------|----------|----------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range     | 31/15                              | 30/14                                        | 29/13 | 28/12 | 27/11 | 26/10 | 25/9    | 24/8       | 23/7     | 22/6     | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 9110                        | ADC1BUFA         | 31:16<br>15:0 |                                    | ADC Result Word A (ADC1BUFA<31:0>) 0000 0000 |       |       |       |       |         |            |          |          |      |      |      |      |      |      |            |

| 9120                        | ADC1BUFB         | 31:16<br>15:0 |                                    | ADC Result Word B (ADC1BUFB<31:0>) 0000 0000 |       |       |       |       |         |            |          |          |      |      |      |      |      |      |            |

| 9130                        | ADC1BUFC         | 31:16<br>15:0 |                                    |                                              |       |       |       |       | ADC Res | ult Word C | (ADC1BUF | C<31:0>) |      |      |      |      |      |      | 0000       |

| 9140                        | ADC1BUFD         | 31:16<br>15:0 |                                    |                                              |       |       |       |       | ADC Res | ult Word D | (ADC1BUF | D<31:0>) |      |      |      |      |      |      | 0000       |

| 9150                        | ADC1BUFE         | 31:16<br>15:0 | ADC Result Word E (ADC1BUFE<31:0>) |                                              |       |       |       |       |         |            |          |          |      |      |      |      |      |      |            |

| 9160                        | ADC1BUFF         | 31:16<br>15:0 |                                    |                                              |       |       |       |       |         |            |          |          |      |      |      |      |      |      |            |

PIC32MX330/350/370/430/450/470

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for details.

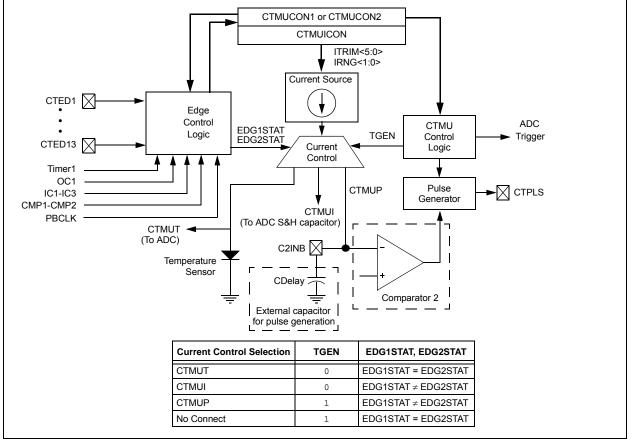

# 26.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 37. "Charge Time Measurement Unit (CTMU)" (DS60001167), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Charge Time Measurement Unit (CTMU) is a flexible analog module that has a configurable current source with a digital configuration circuit built around it. The CTMU can be used for differential time measurement between pulse sources and can be used for generating an asynchronous pulse. By working with other on-chip analog modules, the CTMU can be used for high resolution time measurement, measure capacitance, measure relative changes in capacitance or generate output pulses with a specific time delay. The CTMU is ideal for interfacing with capacitive-based sensors.

FIGURE 26-1: CTMU BLOCK DIAGRAM

The CTMU module includes the following key features:

- Up to 13 channels available for capacitive or time measurement input

- · On-chip precision current source

- 16-edge input trigger sources

- · Selection of edge or level-sensitive inputs

- Polarity control for each edge source

- Control of edge sequence

- Control of response to edges

- · High precision time measurement

- Time delay of external or internal signal asynchronous to system clock

- · Integrated temperature sensing diode

- · Control of current source during auto-sampling

- Four current source ranges

- · Time measurement resolution of one nanosecond

A block diagram of the CTMU is shown in Figure 26-1.

# 27.0 POWER-SAVING FEATURES

| Note: | This data sheet summarizes the features<br>of the PIC32MX330/350/370/430/450/470<br>family of devices. It is not intended to be a<br>comprehensive reference source. To<br>complement the information in this data<br>sheet, refer to <b>Section 10.</b> " <b>Power-</b><br><b>Saving Features</b> " (DS60001130), which<br>is available from the <i>Documentation</i> ><br><i>Reference Manual</i> section of the<br>Microphin PIC22 work arite |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | (www.microchip.com/pic32).                                                                                                                                                                                                                                                                                                                                                                                                                       |

This section describes power-saving features for the PIC32MX330/350/370/430/450/470 family of devices. These PIC32 devices offer a total of nine methods and modes, organized into two categories, that allow the user to balance power consumption with device performance. In all of the methods and modes described in this section, power-saving is controlled by software.

# 27.1 Power Saving with CPU Running

When the CPU is running, power consumption can be controlled by reducing the CPU clock frequency, lowering the PBCLK and by individually disabling modules. These methods are grouped into the following categories:

- FRC Run mode: the CPU is clocked from the FRC clock source with or without postscalers.

- LPRC Run mode: the CPU is clocked from the LPRC clock source.

- Sosc Run mode: the CPU is clocked from the Sosc clock source.

In addition, the Peripheral Bus Scaling mode is available where peripherals are clocked at the programmable fraction of the CPU clock (SYSCLK).

# 27.2 CPU Halted Methods

The device supports two power-saving modes, Sleep and Idle, both of which Halt the clock to the CPU. These modes operate with all clock sources, as listed below:

- Posc Idle mode: the system clock is derived from the Posc. The system clock source continues to operate. Peripherals continue to operate, but can optionally be individually disabled.

- FRC Idle mode: the system clock is derived from the FRC with or without postscalers. Peripherals continue to operate, but can optionally be individually disabled.

- Sosc Idle mode: the system clock is derived from the Sosc. Peripherals continue to operate, but can optionally be individually disabled.

- LPRC Idle mode: the system clock is derived from the LPRC. Peripherals continue to operate, but can optionally be individually disabled. This is the lowest power mode for the device with a clock

running.

• Sleep mode: the CPU, the system clock source and any peripherals that operate from the system clock source are Halted. Some peripherals can operate in Sleep using specific clock sources. This is the lowest power mode for the device.

# 27.3 Power-Saving Operation

Peripherals and the CPU can be Halted or disabled to further reduce power consumption.

## 27.3.1 SLEEP MODE

Sleep mode has the lowest power consumption of the device power-saving operating modes. The CPU and most peripherals are Halted. Select peripherals can continue to operate in Sleep mode and can be used to wake the device from Sleep. See the individual peripheral module sections for descriptions of behavior in Sleep.

Sleep mode includes the following characteristics:

- The CPU is Halted.

- The system clock source is typically shutdown. See Section 27.3.3 "Peripheral Bus Scaling Method" for specific information.

- There can be a wake-up delay based on the oscillator selection.

- The Fail-Safe Clock Monitor (FSCM) does not operate during Sleep mode.

- The BOR circuit remains operative during Sleep mode.

- The WDT, if enabled, is not automatically cleared prior to entering Sleep mode.

- Some peripherals can continue to operate at limited functionality in Sleep mode. These peripherals include I/O pins that detect a change in the input signal, WDT, ADC, UART and peripherals that use an external clock input or the internal LPRC oscillator (e.g., RTCC, Timer1 and Input Capture).

- I/O pins continue to sink or source current in the same manner as they do when the device is not in Sleep.

- The USB module can override the disabling of the Posc or FRC. Refer to the USB section for specific details.

- Modules can be individually disabled by software prior to entering Sleep in order to further reduce consumption.