Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 100MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-VQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx330f064ht-i-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MCUS

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the documents listed in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

## 2.1 Basic Connection Requirements

Getting started with the PIC32MX330/350/370/430/ 450/470 family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins, even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- VCAP pin (see 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins, used for In-Circuit Serial Programming (ICSP<sup>™</sup>) and debugging purposes (see **2.5** "ICSP Pins")

- OSC1 and OSC2 pins, when external oscillator source is used (see 2.8 "External Oscillator Pins")

The following pins may be required:

VREF+/VREF- pins, used when external voltage reference for the ADC module is implemented.

**Note:** The AVDD and AVSS pins must be connected, regardless of ADC use and the ADC voltage reference source.

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1  $\mu$ F (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

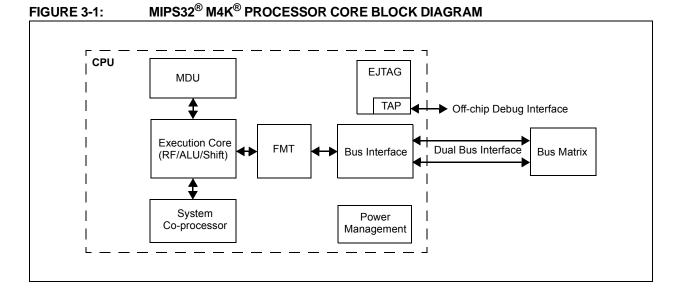

# 3.0 CPU

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 2.** "CPU" (DS60001113), which is available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). Resources for the MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core are available at http://www.imgtec.com.

The the MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core is the heart of the PIC32MX330/350/370/430/450/470 device processor. The CPU fetches instructions, decodes each instruction, fetches source operands, executes each instruction and writes the results of instruction execution to the proper destinations.

## 3.1 Features

- 5-stage pipeline

- · 32-bit address and data paths

- MIPS32<sup>®</sup> Enhanced Architecture (Release 2):

- Multiply-accumulate and multiply-subtract instructions

- Targeted multiply instruction

- Zero/One detect instructions

- WAIT instruction

- Conditional move instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- GPR shadow registers to minimize latency for interrupt handlers

- Bit field manipulation instructions

- MIPS16e<sup>®</sup> Code Compression:

- 16-bit encoding of 32-bit instructions to improve code density

- Special PC-relative instructions for efficient loading of addresses and constants

- SAVE and RESTORE macro instructions for setting up and tearing down stack frames within subroutines

- Improved support for handling 8 and 16-bit data types

- Simple Fixed Mapping Translation (FMT) Mechanism:

- Simple Dual Bus Interface:

- Independent 32-bit address and data buses

- Transactions can be aborted to improve interrupt latency

- Autonomous Multiply/Divide Unit (MDU):

- Maximum issue rate of one 32x16 multiply per clock

- Maximum issue rate of one 32x32 multiply every other clock

- Early-in iterative divide. Minimum 11 and maximum 33 clock latency (dividend (*rs*) sign extension-dependent)

- · Power Control:

- Minimum frequency: 0 MHz

- Low-Power mode (triggered by WAIT instruction)

- Extensive use of local gated clocks

- · EJTAG Debug and Instruction Trace:

- Support for single stepping

- Virtual instruction and data address/value

- Breakpoints

## 3.2 Architecture Overview

The MIPS32<sup>®</sup> M4K<sup>®</sup> processor core contains several logic blocks working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- Execution Unit

- Multiply/Divide Unit (MDU)

- System Control Coprocessor (CP0)

- Fixed Mapping Translation (FMT)

- Dual Internal Bus interfaces

- Power Management

- MIPS16e<sup>®</sup> Support

- Enhanced JTAG (EJTAG) Controller

### 3.2.1 EXECUTION UNIT

The MIPS32<sup>®</sup> M4K<sup>®</sup> processor core execution unit implements a load/store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation. One additional register file shadow set (containing thirty-two registers) is added to minimize context switching overhead during interrupt/exception processing. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction

address

- Logic for branch determination and branch target address calculation

- · Load aligner

- Bypass multiplexers used to avoid stalls when executing instruction streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing bitwise logical operations

- Shifter and store aligner

## 3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

The MIPS32<sup>®</sup> M4K<sup>®</sup> processor core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows MDU operations to be partially masked by system stalls and/or other integer unit instructions.

The high-performance MDU consists of a 32x16 booth recoded multiplier, result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x16) represents the *rs* operand. The second number ('16' of 32x16) represents the *rt* operand. The PIC32 core only checks the value of the latter (*rt*) operand to determine how many times the operation must pass through the multiplier. The 16x16 and 32x16 operations pass through the multiplier once. A 32x32 operation passes through the multiplier twice.

The MDU supports execution of one 16x16 or 32x16 multiply operation every clock cycle; 32x32 multiply operations can be issued every other clock cycle. Appropriate interlocks are implemented to stall the issuance of back-to-back 32x32 multiply operations. The multiply operand size is automatically determined by logic built into the MDU.

Divide operations are implemented with a simple 1 bit per clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If *rs* is 8 bits wide, 23 iterations are skipped. For a 16-bit wide *rs*, 15 iterations are skipped and for a 24-bit wide *rs*, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation is completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the PIC32 core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

| DIVIDE UNIT LATENCIES AND REPEAT RATES |                                                |         |             |  |  |  |  |  |  |

|----------------------------------------|------------------------------------------------|---------|-------------|--|--|--|--|--|--|

| Op code                                | Operand Size (mul <i>rt</i> ) (div <i>rs</i> ) | Latency | Repeat Rate |  |  |  |  |  |  |

| MULT/MULTU, MADD/MADDU,                | 16 bits                                        | 1       | 1           |  |  |  |  |  |  |

| MSUB/MSUBU                             | 32 bits                                        | 2       | 2           |  |  |  |  |  |  |

| MUL                                    | 16 bits                                        | 2       | 1           |  |  |  |  |  |  |

|                                        | 32 bits                                        | 3       | 2           |  |  |  |  |  |  |

| DIV/DIVU                               | 8 bits                                         | 12      | 11          |  |  |  |  |  |  |

|                                        | 16 bits                                        | 19      | 18          |  |  |  |  |  |  |

|                                        | 24 bits                                        | 26      | 25          |  |  |  |  |  |  |

|                                        | 32 bits                                        | 33      | 32          |  |  |  |  |  |  |

## TABLE 3-1: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE HIGH-PERFORMANCE INTEGER MULTIPLY/ DIVIDE UNIT LATENCIES AND REPEAT RATES

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | —                 |                  | —                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | _                 | _                 | —                 | _                 | _                 | —                 | —                | —                |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |

| 15:8         | BMXDKPBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 7:0          | BMXDKPBA<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |

### REGISTER 4-2: BMXDKPBA: DATA RAM KERNEL PROGRAM BASE ADDRESS REGISTER

#### Legend:

| Legenu.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-10 **BMXDKPBA<15:10>:** DRM Kernel Program Base Address bits When non-zero, this value selects the relative base address for kernel program space in RAM

bit 9-0 BMXDKPBA<9:0>: Read-Only bits Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernel mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

NOTES:

# PIC32MX330/350/370/430/450/470

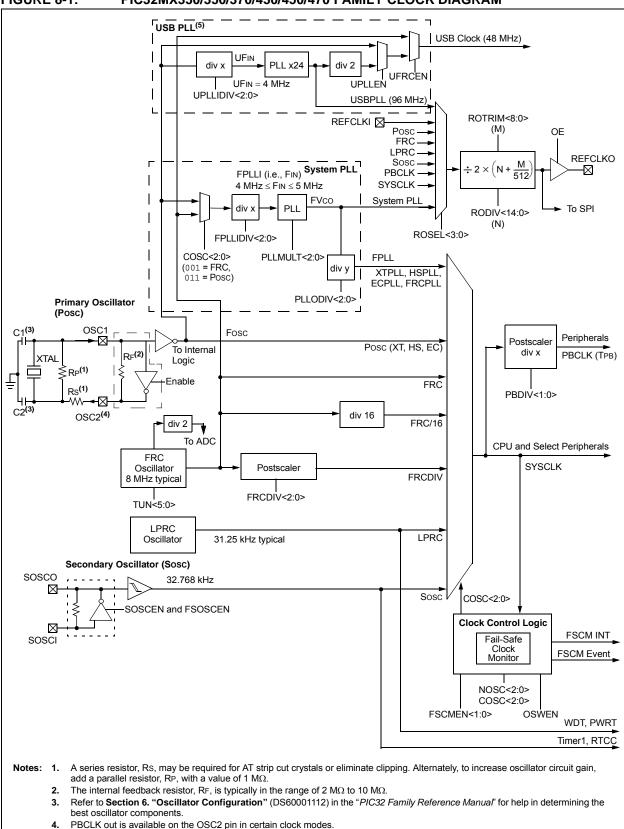

#### FIGURE 8-1: PIC32MX330/350/370/430/450/470 FAMILY CLOCK DIAGRAM

5. USB PLL is available on PIC32MX4XX devices only.

## TABLE 11-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       |       |       |       |       |      |      | Bi             | ts       |       |          |         |        |           |          |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|----------------|----------|-------|----------|---------|--------|-----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7           | 22/6     | 21/5  | 20/4     | 19/3    | 18/2   | 17/1      | 16/0     | All Resets |

| 5280                        | U1FRML <sup>(3)</sup>           | 31:16     | _     |       |       | —     | —     | —     |      |      |                | —        |       | _        | _       | —      |           |          | 0000       |

| 5260                        | UTFRIVIL                        | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    |                |          |       | FRML<    | 7:0>    |        |           |          | 0000       |

| 5290                        | U1FRMH <sup>(3)</sup>           | 31:16     | —     | _     |       | _     | _     | _     | _    | _    | -              | —        | _     | —        | —       | _      |           |          | 0000       |

| 5290                        |                                 | 15:0      | —     | —     | —     | —     | —     | —     | _    | —    | _              | —        | _     | _        | —       |        | FRMH<2:0> | >        | 0000       |

| 52A0                        | U1TOK                           | 31:16     | —     | _     | —     | _     | _     | _     | _    | —    |                | -        |       | _        | -       | _      | —         | —        | 0000       |

| JZAU                        | UTION                           | 15:0      | —     | —     | —     | —     | —     | —     | _    | —    |                | PID      | <3:0> | -        |         | EP     | <3:0>     | •        | 0000       |

| 52B0                        | U1SOF                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    |                | —        | _     | —        | _       | _      |           | _        | 0000       |

| 52.00                       | 0130F                           | 15:0      | —     | —     | _     | —     | —     | —     | _    | _    |                |          |       | CNT<7    | 7:0>    |        |           |          | 0000       |

| 52C0                        | U1BDTP2                         | 31:16     | —     | _     | -     | _     | _     | _     | _    | _    |                | —        |       | —        | _       | _      |           |          | 0000       |

| 5200                        | UIBDIF2                         | 15:0      | —     | _     | -     | _     | _     | _     | _    | _    |                |          |       | BDTPTRH  | <23:16> |        |           |          | 0000       |

| 52D0                        | U1BDTP3                         | 31:16     | —     | _     | -     | _     | _     | _     | _    | _    |                | —        |       | —        | _       | _      |           |          | 0000       |

| 52D0                        | UIBDIF3                         | 15:0      | —     | _     | -     | _     | _     | _     | _    | _    | BDTPTRU<31:24> |          |       |          | 0000    |        |           |          |            |

| 52E0                        | U1CNFG1                         | 31:16     | —     | _     | -     | _     | _     | _     | _    | _    |                | —        |       | —        | _       | _      |           |          | 0000       |

|                             |                                 | 15:0      | —     | —     | _     | —     | —     | —     | _    | _    | UTEYE          | UOEMON   |       | USBSIDL  | —       | _      |           | UASUSPNE | 0000       |

| 5300                        | U1FP0 -                         | 31:16     | _     | _     |       | _     | _     | _     | _    |      | _              | —        | _     | —        | —       | —      |           |          | 0000       |

| 5500                        |                                 | 15:0      | —     | _     | -     | _     | _     | _     | _    | _    | LSPD           | RETRYDIS |       | EPCONDIS | EPRXEN  | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5310                        | U1EP1                           | 31:16     | —     | _     | -     | _     | _     | _     | _    | _    |                | —        |       | —        | _       | _      |           |          | 0000       |

| 5510                        | UILFI                           | 15:0      | _     | _     |       | —     | —     | —     | _    |      | _              | —        | _     | EPCONDIS | EPRXEN  | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5320                        | U1EP2                           | 31:16     | —     | —     | _     | —     | —     | —     | —    |      | _              | —        | _     | —        | _       | —      |           |          | 0000       |

| 5520                        | UILFZ                           | 15:0      | —     | _     | _     | _     | _     | _     | _    | _    |                | —        |       | EPCONDIS | EPRXEN  | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5330                        | U1EP3                           | 31:16     | —     | —     | _     | —     | —     | —     | —    |      | _              | —        | _     | —        | _       | —      |           |          | 0000       |

| 5550                        | UTEI 3                          | 15:0      | _     | —     | —     | —     | —     | —     | —    | —    |                | —        |       | EPCONDIS | EPRXEN  | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5340                        | U1EP4                           | 31:16     | —     | —     | —     | —     | —     | —     | _    | —    | _              | —        | _     | _        | —       | —      | _         | _        | 0000       |

| 5540                        | 01214                           | 15:0      | _     | —     | —     | —     | —     | —     | —    | —    |                | —        |       | EPCONDIS | EPRXEN  | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5350                        | U1EP5                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | _    | -              | —        | _     | _        | —       | —      | _         | —        | 0000       |

| 5550                        | UTEI 5                          | 15:0      | _     | —     | —     | —     | —     | —     | —    | —    |                | —        |       | EPCONDIS | EPRXEN  | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5360                        | U1EP6                           | 31:16     | _     | —     | —     | —     | —     | —     | —    | —    |                | —        |       | _        | —       | —      | —         | —        | 0000       |

| 5500                        | UILI U                          | 15:0      | —     | _     | —     | _     | _     | _     | —    | —    | _              | —        | _     | EPCONDIS | EPRXEN  | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5370                        | U1EP7                           | 31:16     | —     | _     | _     | _     | _     | _     | _    | _    |                | —        |       | -        | —       | —      |           |          | 0000       |

| 3370                        | UILF /                          | 15:0      | —     | _     | _     | _     | _     | _     | —    | _    | _              | —        | _     | EPCONDIS | EPRXEN  | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

| 5380                        | U1EP8                           | 31:16     | —     | —     | _     | —     | —     | —     | _    | _    |                | —        |       | -        | —       | —      |           | —        | 0000       |

| 5500                        | UILFO                           | 15:0      | _     | _     | _     | —     | —     | —     | _    |      |                | —        |       | EPCONDIS | EPRXEN  | EPTXEN | EPSTALL   | EPHSHK   | 0000       |

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

This register does not have associated CLR, SET and INV registers. 3:

4: Reset value for this bit is undefined.

# PIC32MX330/350/370/430/450/470

#### REGISTER 11-7: U1IE: USB INTERRUPT ENABLE REGISTER

|              |                   | •                 |                   |                   |                   |                   |                       |                         |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|-------------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0        |

| 31:24        | U-0                   | U-0                     |

| 31.24        | -                 | —                 | —                 | -                 | —                 | —                 | -                     | —                       |

| 23:16        | U-0                   | U-0                     |

| 23.10        | -                 | —                 | —                 | -                 | —                 | —                 | -                     | —                       |

| 15:8         | U-0                   | U-0                     |

| 15.0         |                   | _                 | —                 | _                 | —                 | _                 | _                     | —                       |

|              | R/W-0                 | R/W-0                   |

| 7:0          | STALLIE           |                   | RESUMEIE          |                   | TONIE             | SOFIE             | UERRIE <sup>(1)</sup> | URSTIE <sup>(2)</sup>   |

|              |                   | ATTACHIE          |                   | IDLEIE            | TRNIE             |                   | UEKRIE                | DETACHIE <sup>(3)</sup> |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

| bit 7 | <b>STALLIE:</b> STALL Handshake Interrupt Enable bit<br>1 = STALL interrupt is enabled<br>0 = STALL interrupt is disabled         |

|-------|-----------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | ATTACHIE: ATTACH Interrupt Enable bit<br>1 = ATTACH interrupt is enabled<br>0 = ATTACH interrupt is disabled                      |

| bit 5 | <b>RESUMEIE:</b> RESUME Interrupt Enable bit<br>1 = RESUME interrupt is enabled<br>0 = RESUME interrupt is disabled               |

| bit 4 | IDLEIE: Idle Detect Interrupt Enable bit<br>1 = Idle interrupt is enabled<br>0 = Idle interrupt is disabled                       |

| bit 3 | <b>TRNIE:</b> Token Processing Complete Interrupt Enable bit<br>1 = TRNIF interrupt is enabled<br>0 = TRNIF interrupt is disabled |

| bit 2 | <b>SOFIE:</b> SOF Token Interrupt Enable bit<br>1 = SOFIF interrupt is enabled<br>0 = SOFIF interrupt is disabled                 |

| bit 1 | UERRIE: USB Error Interrupt Enable bit <sup>(1)</sup><br>1 = USB Error interrupt is enabled                                       |

- 1 = USB Error interrupt is enabled 0 = USB Error interrupt is disabled

- bit 0 URSTIE: USB Reset Interrupt Enable bit<sup>(2)</sup>

- 1 = URSTIF interrupt is enabled

- 0 = URSTIF interrupt is disabled

- DETACHIE: USB Detach Interrupt Enable bit<sup>(3)</sup>

- 1 = DATTCHIF interrupt is enabled

- 0 = DATTCHIF interrupt is disabled

**Note 1:** For an interrupt to propagate USBIF, the UERRIE bit (U1IE<1>) must be set.

- 2: Device mode.

- 3: Host mode.

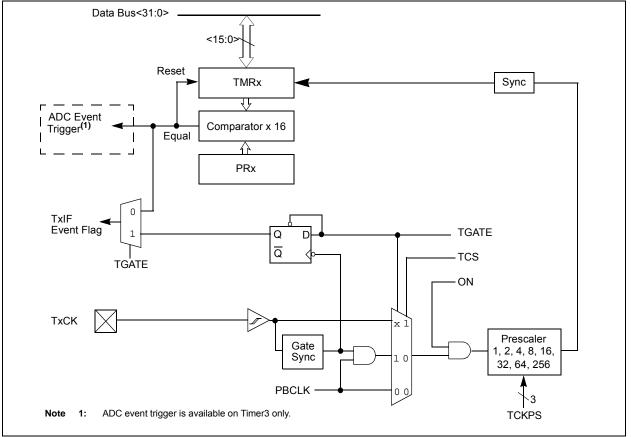

# 14.0 TIMER2/3, TIMER4/5

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32MX330/350/370/430/450/470 family of devices features four synchronous 16-bit timers (default) that can operate as a free-running interval timer for various timing applications and counting external events. The following modes are supported:

- Synchronous internal 16-bit timer

- Synchronous internal 16-bit gated timer

- · Synchronous external 16-bit timer

Two 32-bit synchronous timers are available by combining Timer2 with Timer3 and Timer4 with Timer5. The 32-bit timers can operate in three modes:

- · Synchronous internal 32-bit timer

- · Synchronous internal 32-bit gated timer

- · Synchronous external 32-bit timer

- Note: In this chapter, references to registers, TxCON, TMRx and PRx, use 'x' to represent Timer2 through 5 in 16-bit modes. In 32-bit modes, 'x' represents Timer2 or 4; 'y' represents Timer3 or 5.

## 14.1 Additional Supported Features

- Selectable clock prescaler

- Timers operational during CPU idle

- Time base for Input Capture and Output Compare modules (Timer2 and Timer3 only)

- ADC event trigger (Timer3 in 16-bit mode, Timer2/ 3 in 32-bit mode)

- Fast bit manipulation using CLR, SET, and INV registers

## FIGURE 14-1: TIMER2, 3, 4, 5 BLOCK DIAGRAM (16-BIT)

## REGISTER 14-1: TxCON: TYPE B TIMER CONTROL REGISTER (CONTINUED)

- bit 3 T32: 32-Bit Timer Mode Select bit<sup>(2)</sup>

- 1 = Odd numbered and even numbered timers form a 32-bit timer

- 0 = Odd numbered and even numbered timers form a separate 16-bit timer

- bit 2 Unimplemented: Read as '0'

- bit 1 **TCS:** Timer Clock Source Select bit<sup>(3)</sup>

- 1 = External clock from TxCK pin

- 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit is available only on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer3 and Timer5). All timer functions are set through the even numbered timers.

- 4: While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 31:24        |                   | _                 | _                 | RXBUFELM<4:0>     |                   |                   |                  |                  |  |  |

| 23:16        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 23.10        |                   | _                 | —                 | TXBUFELM<4:0>     |                   |                   |                  |                  |  |  |

| 15.0         | U-0               | U-0               | U-0               | R/C-0, HS         | R-0               | U-0               | U-0              | R-0              |  |  |

| 15:8         |                   | —                 | _                 | FRMERR            | SPIBUSY           | —                 | _                | SPITUR           |  |  |

| 7.0          | R-0               | R/W-0             | R-0               | U-0               | R-1               | U-0               | R-0              | R-0              |  |  |

| 7:0          | SRMT              | SPIROV            | SPIRBE            | _                 | SPITBE            |                   | SPITBF           | SPIRBF           |  |  |

## REGISTER 18-3: SPIxSTAT: SPI STATUS REGISTER

| Legend:           | C = Clearable bit | HS = Set in hardware     |                    |  |  |  |

|-------------------|-------------------|--------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, r | ead as '0'         |  |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared     | x = Bit is unknown |  |  |  |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 **RXBUFELM<4:0>:** Receive Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **TXBUFELM<4:0>:** Transmit Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 15-13 Unimplemented: Read as '0'

- bit 12 **FRMERR:** SPI Frame Error status bit

- 1 = Frame error is detected

- 0 = No Frame error is detected

- This bit is only valid when FRMEN = 1.

- bit 11 SPIBUSY: SPI Activity Status bit

- 1 = SPI peripheral is currently busy with some transactions

- 0 = SPI peripheral is currently idle

- bit 10-9 Unimplemented: Read as '0'

- bit 8 SPITUR: Transmit Under Run bit

- 1 = Transmit buffer has encountered an underrun condition

- 0 = Transmit buffer has no underrun condition

This bit is only valid in Framed Sync mode; the underrun condition must be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or writing a '0' to SPITUR.

- bit 7 **SRMT:** Shift Register Empty bit (valid only when ENHBUF = 1)

- 1 = When SPI module shift register is empty

- 0 = When SPI module shift register is not empty

- bit 6 SPIROV: Receive Overflow Flag bit

- 1 = A new data is completely received and discarded. The user software has not read the previous data in the SPIxBUF register.

- 0 = No overflow has occurred

This bit is set in hardware; can bit only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or by writing a '0' to SPIROV.

- bit 5 SPIRBE: RX FIFO Empty bit (valid only when ENHBUF = 1) 1 = RX FIFO is empty (CRPTR = SWPTR)

- 0 = RX FIFO is not empty (CRPTR  $\neq$  SWPTR)

- bit 4 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4   | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|---------------------|-------------------|-------------------|------------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 51.24        | EDG1MOD           | EDG1POL           |                   | EDG1S               |                   | EDG2STAT          | EDG1STAT               |                  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | U-0                    | U-0              |

| 23.10        | EDG2MOD           | EDG2POL           |                   | EDG2S               | —                 | _                 |                        |                  |

| 15:0         | R/W-0             | U-0               | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 15:8         | ON                | —                 | CTMUSIDL          | TGEN <sup>(1)</sup> | EDGEN             | EDGSEQEN          | IDISSEN <sup>(2)</sup> | CTTRIG           |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 7:0          | ITRIM<5:0>        |                   |                   |                     |                   |                   |                        | <1:0>            |

#### REGISTER 26-1: CTMUCON: CTMU CONTROL REGISTER

#### Legend:

| 3                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31 EDG1MOD: Edge 1 Edge Sampling Select bit

1 = Input is edge-sensitive

0 = Input is level-sensitive

bit 30 EDG1POL: Edge 1 Polarity Select bit

1 = Edge 1 programmed for a positive edge response

0 = Edge 1 programmed for a negative edge response

#### bit 29-26 EDG1SEL<3:0>: Edge 1 Source Select bits

#### 1111 = Reserved

1110 = C2OUT pin is selected

- 1101 = C1OUT pin is selected

- 1100 = IC3 Capture Event is selected

- 1011 = IC2 Capture Event is selected

- 1010 = IC1 Capture Event is selected

- 1001 = CTED8 pin is selected

- 1000 = CTED7 pin is selected

- 0111 = CTED6 pin is selected

- 0110 = CTED5 pin is selected

- 0101 = CTED4 pin is selected

- 0100 = CTED3 pin is selected

- 0011 = CTED1 pin is selected

- 0010 = CTED2 pin is selected

- 0001 = OC1 Compare Event is selected

## 0000 = Timer1 Event is selected

## bit 25 EDG2STAT: Edge 2 Status bit

Indicates the status of Edge 2 and can be written to control edge source

- 1 = Edge 2 has occurred

- 0 = Edge 2 has not occurred

- **Note 1:** When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 31-42) in Section 31.0 "Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

# 29.0 INSTRUCTION SET

The PIC32MX330/350/370/430/450/470 family instruction set complies with the MIPS32<sup>®</sup> Release 2 instruction set architecture. The PIC32 device family does not support the following features:

- · Core extend instructions

- Coprocessor 1 instructions

- Coprocessor 2 instructions

Note: Refer to "MIPS32<sup>®</sup> Architecture for Programmers Volume II: The MIPS32<sup>®</sup> Instruction Set" at www.imgtec.com for more information.

## TABLE 31-32: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS (CONTINUED)

| AC CHARACTERISTICS |                       |                                                                           | $ \begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \\ \end{array} $ |   |    |    |   |  |

|--------------------|-----------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|----|---|--|

| Param.<br>No.      | Symbol                | Characteristics <sup>(1)</sup>                                            | Min. Typical <sup>(2)</sup> Max. Units Conditions                                                                                                                                                                                                                                                                                                        |   |    |    |   |  |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\downarrow$ or SCKx $\uparrow$ Input | 175                                                                                                                                                                                                                                                                                                                                                      |   |    | ns | — |  |

| SP51               | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance<br>(Note 4)                        | 5                                                                                                                                                                                                                                                                                                                                                        |   | 25 | ns | _ |  |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx ↑ after SCKx Edge                                                     | Тscк +<br>20                                                                                                                                                                                                                                                                                                                                             | _ | _  | ns | _ |  |

| SP60               | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge                                  |                                                                                                                                                                                                                                                                                                                                                          |   | 25 | ns |   |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: The minimum clock period for SCKx is 40 ns.

**4:** Assumes 50 pF load on all SPIx pins.

| AC CHA        | Standard Operating Conditions: 2.3V to 3.6V<br>(unless otherwise stated)RACTERISTICSOperating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Comme<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for Indust<br>$-40^{\circ}C \le TA \le +105^{\circ}C$ for V-ter |                                                                         |                                                   | ′0°C for Commercial<br>+85°C for Industrial |         |      |                                                           |

|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------|---------------------------------------------|---------|------|-----------------------------------------------------------|

| Param.<br>No. | Symbol                                                                                                                                                                                                                                                             | Characteristics                                                         | Min. Typical <sup>(1)</sup> Max. Units Conditions |                                             |         |      | Conditions                                                |

| Clock P       | arameter                                                                                                                                                                                                                                                           | S                                                                       |                                                   |                                             |         |      |                                                           |

| AD50          | TAD                                                                                                                                                                                                                                                                | ADC Clock Period <sup>(2)</sup>                                         | 65                                                |                                             |         | ns   | See Table 31-36                                           |

| Conver        | Conversion Rate                                                                                                                                                                                                                                                    |                                                                         |                                                   |                                             |         |      |                                                           |

| AD55          | TCONV                                                                                                                                                                                                                                                              | Conversion Time                                                         | _                                                 | 12 Tad                                      | _       | _    | —                                                         |

| AD56          | FCNV                                                                                                                                                                                                                                                               | Throughput Rate                                                         | _                                                 | _                                           | 1000    | ksps | AVDD = 3.0V to 3.6V                                       |

|               |                                                                                                                                                                                                                                                                    | (Sampling Speed) <sup>(4)</sup>                                         | _                                                 | —                                           | 400     | ksps | AVDD = 2.5V to 3.6V                                       |

| AD57          | TSAMP                                                                                                                                                                                                                                                              | Sample Time                                                             | 2 Tad                                             | _                                           | —       | _    | —                                                         |

| Timing        | Paramete                                                                                                                                                                                                                                                           | rs                                                                      |                                                   |                                             |         |      |                                                           |

| AD60          | TPCS                                                                                                                                                                                                                                                               | Conversion Start from Sample<br>Trigger <sup>(3)</sup>                  | —                                                 | 1.0 Tad                                     |         | _    | Auto-Convert Trigger<br>(SSRC<2:0> = 111)<br>not selected |

| AD61          | TPSS                                                                                                                                                                                                                                                               | Sample Start from Setting<br>Sample (SAMP) bit                          | 0.5 TAD                                           | —                                           | 1.5 TAD | _    | -                                                         |

| AD62          | Tcss                                                                                                                                                                                                                                                               | Conversion Completion to<br>Sample Start (ASAM = $1$ ) <sup>(3)</sup>   | —                                                 | 0.5 Tad                                     | —       | _    | -                                                         |

| AD63          | Tdpu                                                                                                                                                                                                                                                               | Time to Stabilize Analog Stage<br>from ADC Off to ADC On <sup>(3)</sup> | _                                                 | _                                           | 2       | μS   | _                                                         |

#### TABLE 31-37: ANALOG-TO-DIGITAL CONVERSION TIMING REQUIREMENTS

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Because the sample caps will eventually lose charge, clock rates below 10 kHz can affect linearity performance, especially at elevated temperatures.

3: Characterized by design but not tested.

4: Refer to Table 31-36 for detailed conditions.

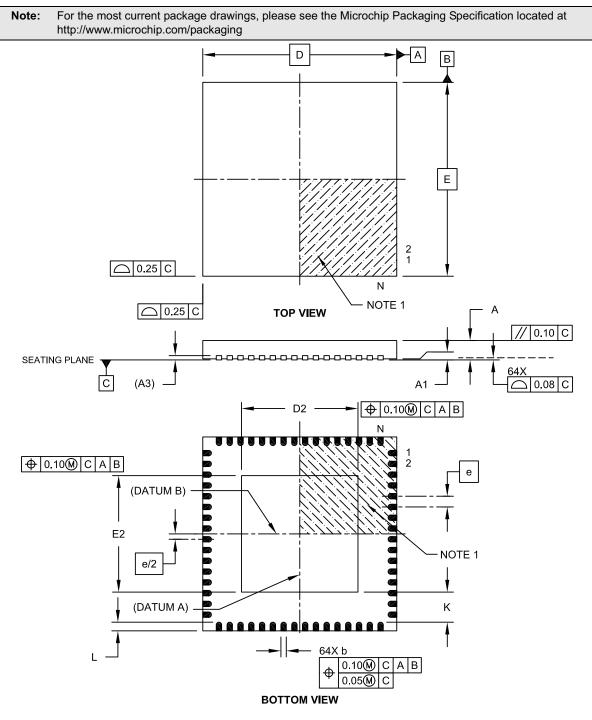

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

Microchip Technology Drawing C04-154A Sheet 1 of 2

## **Revision E (October 2015)**

This revision includes the following updates, as listed in Table A-4.

## TABLE A-4: MAJOR SECTION UPDATES

| Section                                                  | Update Description                                                             |

|----------------------------------------------------------|--------------------------------------------------------------------------------|

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs" | Section 2.10 "Sosc Design Recommendations" was removed.                        |

| 31.0 "Electrical<br>Characteristics"                     | The Power-Down Current (IPD) DC Characteristics were updated (see Table 31-7). |

## **Revision F (September 2016)**

This revision includes the following updates, as listed in Table A-5.

## TABLE A-5: MAJOR SECTION UPDATES

| Section                                                    | Update Description                                                                                                                                                                                             |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "32-bit Microcontrollers (up<br>to 512 KB Flash and 128 KB | The PIC32MX450F128HB and PIC32MX470F512LB devices and Note 4 were added to the family features table (see Table 1).                                                                                            |

| SRAM) with Audio/                                          | Note 2 in the 64-pin device pin table was updated (see Table 2).                                                                                                                                               |

| Graphics/Touch (HMI), USB,<br>and Advanced Analog"         | Note 2 in the 64-pin device pin table was updated and Note 4 was removed (see Table 3).                                                                                                                        |

|                                                            | Note 2 and Note 3 in the 100-pin device pin table was updated (see Table 4).                                                                                                                                   |

|                                                            | Note 3 in the 124-pin device pin table was updated (see Table 6).                                                                                                                                              |

|                                                            | Note 2 in the 124-pin device pin table was updated (see Table 7).                                                                                                                                              |

|                                                            | RPF3 was removed from USB devices (see Table 3, Table 5, and Table 7).                                                                                                                                         |

| 1.0 "Device Overview"                                      | The Pinout I/O Descriptions for pins $\overline{\text{U5CTS}}$ , $\overline{\text{U5RTS}}$ , $\overline{\text{U5RX}}$ , and $\overline{\text{U5TX}}$ in 64-pin QFN/TQFP packages were updated (see Table 1-1). |

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs"   | 2.10 "EMI/EMC/EFT (IEC 61000-4-4 and IEC 61000-4-2) Suppression Considerations" was added.                                                                                                                     |

| 8.0 "Oscillator                                            | The Clock Diagram was updated (see Figure 8-1).                                                                                                                                                                |

| Configuration"                                             | The Center Frequency values in the TUN<5:0> bits (OSCTUN<5:0>) were updated (see Register 8-2).                                                                                                                |

| 12.0 "I/O Ports"                                           | Note references in the Input Pin Selection table were updated (see Table 12-1).                                                                                                                                |

|                                                            | Note references in the Output Pin Selection table were updated (see Table 12-2).                                                                                                                               |

|                                                            | PORTF Register Maps were updated (see Table 12-11 and Table 12-3).                                                                                                                                             |

|                                                            | Note 1 was added to the Peripheral Pin Select Input Register Map (see Table 12-17).                                                                                                                            |

| 31.0 "Electrical                                           | The conditions for parameter DI60b (IICH) were updated (see Table 31-8).                                                                                                                                       |

| Characteristics"                                           | Parameter DO50a (Csosc) was removed.                                                                                                                                                                           |

|                                                            | The maximum value for parameter OS10 (Fosc) was updated (see Table 31-18).                                                                                                                                     |

|                                                            | Parameter PM7 (TDHOLD) was updated (see Table 31-39).                                                                                                                                                          |

|                                                            | Note 1 was added to the DC Characteristics: Program Memory (see Table 31-12).                                                                                                                                  |

| 33.0 "Packaging<br>Information"                            | The Land Pattern for 64-pin QFN packages was updated.                                                                                                                                                          |

| "Product Identification System"                            | The Software Targeting category was added.                                                                                                                                                                     |

# INDEX

| Α                                         |     |

|-------------------------------------------|-----|

| AC Characteristics                        | 295 |

| 10-Bit Conversion Rate Parameters         | 318 |

| ADC Specifications                        | 316 |

| Analog-to-Digital Conversion Requirements | 319 |

| EJTAG Timing Requirements                 | 327 |

| Internal FRC Accuracy                     | 297 |

| Internal RC Accuracy                      | 297 |

| OTG Electrical Specifications             | 325 |

| Parallel Master Port Read Requirements    | 323 |

| Parallel Master Port Write                | 324 |

| Parallel Master Port Write Requirements   | 324 |

| Parallel Slave Port Requirements          | 322 |

| PLL Clock Timing                          | 297 |

| Analog-to-Digital Converter (ADC)         | 233 |

| Assembler                                 |     |

| MPASM Assembler                           | 276 |

## В

| Block Diagrams                                  |        |

|-------------------------------------------------|--------|

| ADC Module                                      | 233    |

| Comparator I/O Operating Modes                  | 243    |

| Comparator Voltage Reference                    | 247    |

| Connections for On-Chip Voltage Regulator       | 272    |

| CPU                                             | 35     |

| CTMU Configurations                             |        |

| Time Measurement                                | 251    |

| DMA                                             | 93     |

| I2C Circuit                                     | 198    |

| Input Capture                                   |        |

| Interrupt Controller                            |        |

| JTAG Programming, Debugging and Trace Ports     |        |

| Output Compare Module                           | 185    |

| PMP Pinout and Connections to External Devices. | 213    |

| Prefetch Module                                 | 83     |

| Reset System                                    | 59     |

| RTCC                                            | 223    |

| SPI Module                                      | 189    |

| Timer1                                          |        |

| Timer2/3/4/5 (16-Bit)                           |        |

| Typical Multiplexed Port Structure              | 7, 353 |

| UART                                            | 205    |

| WDT and Power-up Timer                          | 177    |

| Brown-out Reset (BOR)                           |        |

| and On-Chip Voltage Regulator                   | 272    |

|                                                 |        |

# С

| C Compilers                             |          |

|-----------------------------------------|----------|

| MPLAB C18                               |          |

| Charge Time Measurement Unit. See CTMU. |          |

| Clock Diagram                           | 74       |

| Comparator                              |          |

| Specifications                          | 293, 294 |

| Comparator Module                       |          |

| Comparator Voltage Reference (CVref     |          |

| Configuration Bit                       |          |

| Configuring Analog Port Pins            |          |

| CPU                                     |          |

| Architecture Overview                   |          |

| Coprocessor 0 Registers                 |          |

| Core Exception Types                    |          |

| EJTAG Debug Support                     |          |

| Power Management                        |          |

| -                                       |          |

| CPU Module<br>CTMU                   | 27, 35 |

|--------------------------------------|--------|

| Registers                            | 253    |

| Customer Change Notification Service | 359    |

| Customer Notification Service        | 359    |

| Customer Support                     | 359    |

|                                      |        |

# D

| DC and AC Characteristics              |     |

|----------------------------------------|-----|

| Graphs and Tables                      | 329 |

| DC Characteristics                     | 280 |

| I/O Pin Input Specifications           | 287 |

| I/O Pin Output Specifications          | 290 |

| Idle Current (IIDLE)                   | 283 |

| Power-Down Current (IPD)               | 284 |

| Program Memory                         | 292 |

| Temperature and Voltage Specifications | 281 |

| Development Support                    | 275 |

| Direct Memory Access (DMA) Controller  |     |

## Е

| —                                   |     |

|-------------------------------------|-----|

| Electrical Characteristics          | 279 |

| AC                                  | 295 |

| Errata                              | 14  |

| External Clock                      |     |

| Timer1 Timing Requirements          | 301 |

| Timer2, 3, 4, 5 Timing Requirements | 302 |

| Timing Requirements                 | 296 |

| F                                   |     |

| Flash Program Memory                | 53  |

| RTSP Operation                      | 53  |

|                                     |     |

## Н

| High Voltage Detect (I | HVD)                | 61, | 272, | 291 |

|------------------------|---------------------|-----|------|-----|

|                        | ··· <b>-</b> /····· | ,   | ,    |     |

# I

| I/O Ports                                 | 137 |

|-------------------------------------------|-----|

| Parallel I/O (PIO)                        | 138 |

| Write/Read Timing                         | 138 |

| Input Change Notification                 | 138 |

| Instruction Set                           | 273 |

| Inter-Integrated Circuit (I2C             | 197 |

| Internal Voltage Reference Specifications | 294 |

| Internet Address                          | 359 |

| Interrupt Controller                      | 63  |

| IRG, Vector and Bit Location              | 64  |

## Μ

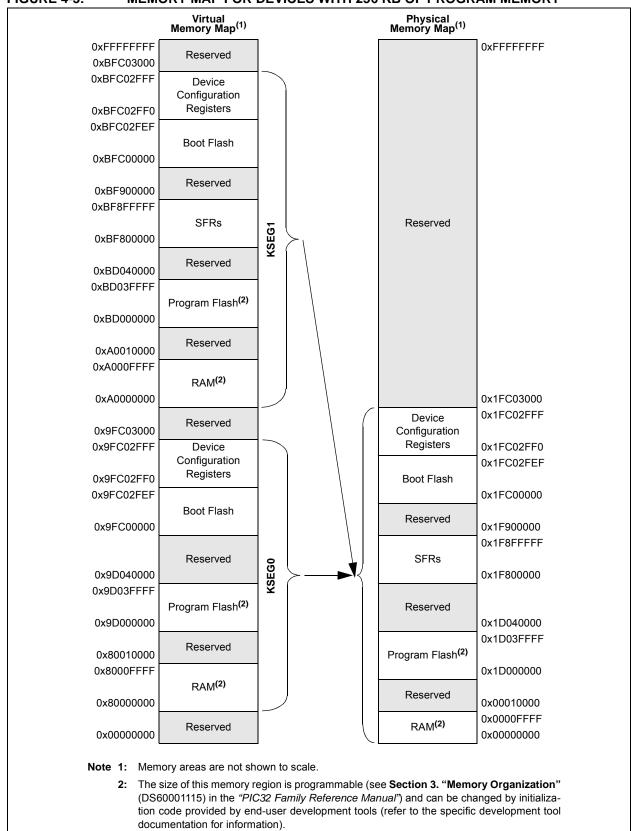

| Memory Maps                                        |       |

|----------------------------------------------------|-------|

| Devices with 128 KB of Program Memory              | 41    |

| Devices with 256 KB of Program Memory              | 42    |

| Devices with 512 KB of Program Memory              | 43    |

| Devices with 64 KB of Program Memory               | 40    |

| Memory Organization                                | 39    |

| Layout                                             | 39    |

| Microchip Internet Web Site                        | . 359 |

| MPLAB ASM30 Assembler, Linker, Librarian           | . 276 |

| MPLAB Integrated Development Environment Software. | . 275 |

| MPLAB PM3 Device Programmer                        | . 277 |

| MPLAB REAL ICE In-Circuit Emulator System          | . 277 |

| MPLINK Object Linker/MPLIB Object Librarian        | . 276 |

|                                                    |       |