Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 64KB (64K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 16K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

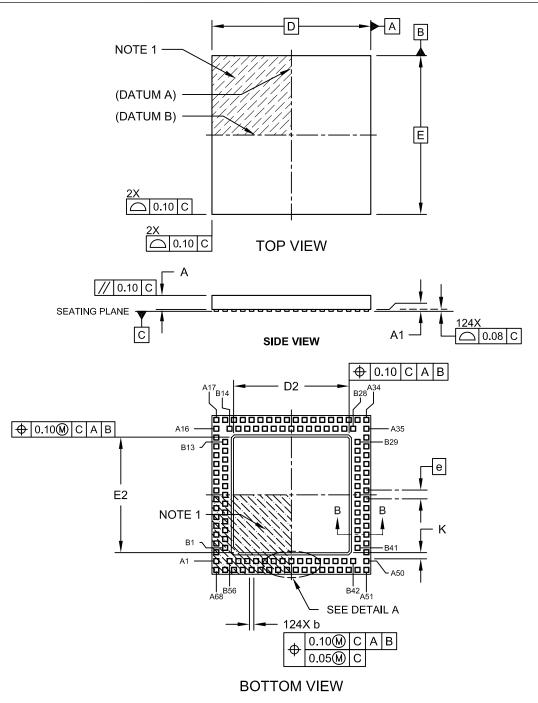

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx330f064l-v-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

### TABLE 10-3: DMA CHANNEL 0 THROUGH CHANNEL 3 REGISTER MAP

| ess                         |                                 | 0             |        |       |       |       |        |       |      | Bi         | its     |        |        |        |         |        |        |        |            |

|-----------------------------|---------------------------------|---------------|--------|-------|-------|-------|--------|-------|------|------------|---------|--------|--------|--------|---------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14 | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8       | 23/7    | 22/6   | 21/5   | 20/4   | 19/3    | 18/2   | 17/1   | 16/0   | All Resets |

|                             | DCH0CON                         | 31:16         | _      | _     |       | _     |        | _     | _    | _          | _       | _      | _      | _      | _       | _      | _      |        | 0000       |

| 3060                        | DCHUCON                         | 15:0          | CHBUSY | —     | _     | —     | _      | —     | —    | CHCHNS     | CHEN    | CHAED  | CHCHN  | CHAEN  | _       | CHEDET | CHPR   | l<1:0> | 0000       |

| 3070                        | DCH0ECON                        | 31:16         | —      | —     | —     | —     | _      | —     | _    | —          |         | 1      | -      |        | Q<7:0>  | •      |        |        | 00FF       |

| 0070                        | DOINCEOUN                       | 15:0          |        |       |       | CHSIR | Q<7:0> |       |      |            | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN  | —      | —      | —      | FFF8       |

| 3080                        | DCH0INT                         | 31:16         | —      | —     | —     | —     | -      | —     | —    | —          | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE | 0000       |

| 0000                        | Borioitti                       | 15:0          | —      | —     | —     | —     | —      | —     | —    | —          | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3090                        | DCH0SSA                         | 31:16<br>15:0 |        |       |       |       |        |       |      | CHSSA      | <31:0>  |        |        |        |         |        |        |        | 0000       |

|                             |                                 | 31:16         |        |       |       |       |        |       |      |            |         |        |        |        |         |        |        |        | 0000       |

| 30A0                        | DCH0DSA                         | 15:0          |        |       |       |       |        |       |      | CHDSA      | A<31:0> |        |        |        |         |        |        |        | 0000       |

|                             |                                 | 31:16         | _      | _     | _     |       | _      | _     | _    | _          | _       | _      | _      | _      | _       | _      |        | _      | 0000       |

| 30B0                        | DCH0SSIZ                        | 15:0          |        |       |       |       |        |       |      | CHSSIZ     | Z<15:0> |        |        |        |         |        |        |        | 0000       |

|                             |                                 | 31:16         | _      | _     | _     | _     | _      | _     | _    | _          | _       | _      | _      | _      | _       | _      | _      | _      | 0000       |

| 30C0                        | DCH0DSIZ                        | 15:0          |        |       |       |       |        |       |      | CHDSIZ     | Z<15:0> |        |        |        |         |        |        |        | 0000       |

| 0000                        |                                 | 31:16         | —      | _     | —     | —     | —      | —     | —    | _          | —       |        | _      | —      | _       | _      | —      | _      | 0000       |

| 30D0                        | DCH0SPTR                        | 15:0          |        |       |       |       |        |       |      | CHSPT      | R<15:0> |        |        |        |         | •      |        |        | 0000       |

| 2050                        |                                 | 31:16         | _      | _     | _     | —     | _      | _     | _    | _          | _       | _      | _      | _      | _       | _      | _      | _      | 0000       |

| 30E0                        | DCH0DPTR                        | 15:0          |        |       |       |       |        |       |      | CHDPT      | R<15:0> |        |        |        |         |        |        |        | 0000       |

| 2050                        | DCH0CSIZ                        | 31:16         | —      |       | _     | _     | _      | _     | _    | _          | _       | _      | _      | _      | _       | —      | _      | _      | 0000       |

| 30FU                        | DCHUCSIZ                        | 15:0          |        |       |       |       |        |       |      | CHCSIZ     | Z<15:0> |        |        |        |         |        |        |        | 0000       |

| 3100                        | DCH0CPTR                        | 31:16         | —      | _     |       | —     |        | _     | _    | —          | _       | _      | _      | _      | _       | _      | _      |        | 0000       |

| 3100                        | DCHUCFTK                        | 15:0          |        |       |       |       |        |       |      | CHCPT      | R<15:0> |        | -      |        |         |        |        |        | 0000       |

| 3110                        | DCH0DAT                         | 31:16         | —      | —     |       | —     | _      | —     | —    | —          |         | —      | —      | —      | —       | —      | —      | —      | 0000       |

| 5110                        | DONUDAI                         | 15:0          | —      | —     | _     | —     | _      |       | —    | —          |         |        |        | CHPDA  | AT<7:0> |        |        |        | 0000       |

| 3120                        | DCH1CON                         | 31:16         | —      | —     | _     | —     | —      |       | —    |            | —       | —      | —      | —      | —       | —      | —      | —      | 0000       |

| 0120                        | Bonnoon                         | 15:0          | CHBUSY | —     | —     | —     | _      | —     | —    | CHCHNS     | CHEN    | CHAED  | CHCHN  | CHAEN  |         | CHEDET | CHPR   | l<1:0> | 0000       |

| 3130                        | DCH1ECON                        | 31:16         | —      | —     | —     | —     | —      | —     | —    | —          |         | 1      | -      |        | Q<7:0>  | -      |        |        | OOFF       |

| 0.00                        |                                 | 15:0          |        |       |       | CHSIR | Q<7:0> |       |      |            | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN  | —      |        | —      | FFF8       |

| 3140                        | DCH1INT                         | 31:16         | -      | _     | _     | —     | _      | —     | _    | —          | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE | 0000       |

| 55                          |                                 | 15:0          | —      | _     | —     | —     | —      | —     | —    | -          | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3150                        | DCH1SSA                         | 31:16         |        |       |       |       |        |       |      | CHSSA      | <31:0>  |        |        |        |         |        |        |        | 0000       |

|                             |                                 | 15:0          |        |       |       |       |        |       |      |            |         |        |        |        |         |        |        |        | 0000       |

| 3160                        | DCH1DSA                         | 31:16         |        |       |       |       |        |       |      | CHDSA      | <31:0>  |        |        |        |         |        |        |        | 0000       |

|                             |                                 | 15:0          |        |       |       |       |        |       |      | exadecimal |         |        |        |        |         |        |        |        | 0000       |

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for Note 1: more information.

# PIC32MX330/350/370/430/450/470

#### REGISTER 10-12: DCHxSSIZ: DMA CHANNEL 'x' SOURCE SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        |                   | -                 | —                 | —                 | —                 | —                 | —                | —                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        |                   | —                 | —                 | —                 | _                 | —                 | _                | _                |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         |                   | CHSSIZ<15:8>      |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          |                   |                   |                   | CHSSIZ            | <7:0>             |                   |                  |                  |  |

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSSIZ<15:0>: Channel Source Size bits

1111111111111111 = 65,535 byte source size

#### **REGISTER 10-13: DCHxDSIZ: DMA CHANNEL 'x' DESTINATION SIZE REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | —                 | _                 | _                 | —                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | —                 | _                 | —                 | _                | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | CHDSIZ            | <15:8>            |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   |                   |                   | CHDSIZ            | <7:0>             |                   |                  |                  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

# TABLE 12-14: PORTF REGISTER MAP FOR PIC32MX430F064H, PIC32MX450F128H, PIC32MX450F256H, AND PIC32MX470F512H DEVICES ONLY

|                             |                                 | U         | ONLY  |       |       |       |       |       |      |      |      |      |              |              |              |      |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|--------------|--------------|--------------|------|--------------|--------------|---------------|

| ess                         |                                 | 6         |       |       |       |       |       |       |      | Bi   | its  |      |              |              |              |      |              |              |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5         | 20/4         | 19/3         | 18/2 | 17/1         | 16/0         | All<br>Resets |

| 6510                        | TRISF                           | 31:16     |       | -     | —     | —     | -     | —     | —    | —    | -    | -    | —            | _            | —            | _    | —            | -            | 0000          |

| 0310                        | TRIO                            | 15:0      | _     | _     | —     | —     | _     | —     |      |      | _    |      | TRISF5       | TRISF4       | TRISF3       | _    | TRISF1       | TRISF0       | xxxx          |

| 6520                        | PORTF                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —            | -            | —            | —    |              | —            | 0000          |

| 0020                        | TORM                            | 15:0      | _     | _     | —     | —     | _     |       |      |      | _    |      | RF5          | RF4          | RF3          | _    | RF1          | RF0          | xxxx          |

| 6530                        | LATF                            | 31:16     | —     | —     | —     | —     | _     | —     | —    | —    | _    |      | —            | —            | —            | —    |              | —            | 0000          |

| 0000                        | 5                               | 15:0      | —     | —     | —     | —     | _     | —     | —    | —    | _    | _    | LATF5        | LATF4        | LATF3        | —    | LATF1        | LATF0        | xxxx          |

| 6540                        | ODCF                            | 31:16     | —     | —     | —     | —     | _     | —     | —    | —    | _    | _    | —            | —            | —            | —    |              | —            | 0000          |

| 0010                        | 0001                            | 15:0      | —     | —     | —     | —     | _     | —     | —    | —    | _    | _    | ODCF5        | ODCF4        | ODCF3        | —    | ODCF1        | ODCF0        | xxxx          |

| 6550                        | CNPUF                           | 31:16     | —     | —     | —     | —     | _     | —     | —    | —    | —    | —    | —            | _            | —            | —    | _            | —            | 0000          |

| 0000                        |                                 | 15:0      | —     | —     | —     | —     | _     | —     | —    | —    | _    | _    | CNPUF5       | CNPUF4       | CNPUF3       | —    | CNPUF1       | CNPUF0       | xxxx          |

| 6560                        | CNPDF                           | 31:16     | —     | —     | —     | —     | -     | —     | —    | —    | —    | _    | —            | -            | _            | —    | -            | —            | 0000          |

|                             | 0.11 5.                         | 15:0      | —     | —     | —     | —     | -     | —     | —    | —    | —    | _    | CNPDF5       | CNPDF4       | CNPDF3       | —    | CNPDF1       | CNPDF0       | xxxx          |

| 6570                        | CNCONF                          | 31:16     | _     | —     | —     | _     | _     | —     | —    | —    | —    |      | —            | _            | —            | _    |              | _            | 0000          |

| 00.0                        | 0.10011                         | 15:0      | ON    | —     | SIDL  | —     | -     | —     | —    | —    | —    | —    | —            | -            | —            | —    | —            | —            | 0000          |

| 6580                        | CNENF                           | 31:16     | —     | —     | —     | —     | -     | —     | —    | —    | —    | —    | —            | -            | _            | —    | -            | —            | 0000          |

|                             |                                 | 15:0      | —     | —     | —     | —     | -     | —     | —    | —    | —    | —    | CNIEF5       | CNIEF4       | CNIEF3       | —    | CNIEF1       | CNIEF0       | xxxx          |

|                             |                                 | 31:16     |       | —     | _     | —     | _     | —     | —    | —    | —    |      |              |              | —            | _    |              | —            | 0000          |

| 6590                        | CNSTATF                         | 15:0      |       | _     | _     | _     | _     | _     | —    | —    | _    | _    | CN<br>STATF5 | CN<br>STATF4 | CN<br>STATF3 | _    | CN<br>STATF1 | CN<br>STATF0 | xxxx          |

Legend: x = Unknown value on Reset; - = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

# PIC32MX330/350/370/430/450/470

# 16.1 Control Register

#### REGISTER 16-1: ICxCON: INPUT CAPTURE 'x' CONTROL REGISTER

| Bit Range                                                 | Bit<br>31/23/15/7                                                                                                                                                                                                                                                                                                                                                                  | Bit<br>30/22/14/6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Bit<br>29/21/13/5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Bit<br>28/20/12/4                                                                                                     | Bit<br>27/19/11/3          | Bit<br>26/18/10/2         | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------|------------------|------------------|

| 31:24                                                     | U-0                                                                                                                                                                                                                                                                                                                                                                                | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | U-0                                                                                                                   | U-0                        | U-0                       | U-0              | U-0              |

| 01.24                                                     | —                                                                                                                                                                                                                                                                                                                                                                                  | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | —                                                                                                                     | —                          | —                         | —                | —                |

| 23:16                                                     | U-0                                                                                                                                                                                                                                                                                                                                                                                | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | U-0                                                                                                                   | U-0                        | U-0                       | U-0              | U-0              |

|                                                           | —                                                                                                                                                                                                                                                                                                                                                                                  | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | —                                                                                                                     | —                          |                           | —                |                  |

| 15:8                                                      | R/W-0                                                                                                                                                                                                                                                                                                                                                                              | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | U-0                                                                                                                   | U-0                        | U-0                       | R/W-0            | R/W-0            |

|                                                           | ON <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                  | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | SIDL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | —                                                                                                                     | —                          | —                         | FEDGE            | C32              |

| 7:0                                                       | R/W-0                                                                                                                                                                                                                                                                                                                                                                              | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | R-0                                                                                                                   | R-0                        | R/W-0                     | R/W-0            | R/W-0            |

|                                                           | ICTMR                                                                                                                                                                                                                                                                                                                                                                              | ICI<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ICOV                                                                                                                  | ICBNE                      |                           | ICM<2:0>         |                  |