Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx330f064lt-i-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS

|          |                        | Pin Numb        | er                                |             |                |                                                                                                                                                                                                   |

|----------|------------------------|-----------------|-----------------------------------|-------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA                   | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                                       |

| AN0      | 16                     | 25              | B14                               |             | Analog         |                                                                                                                                                                                                   |

| AN1      | 15                     | 24              | A15                               | I           | Analog         |                                                                                                                                                                                                   |

| AN2      | 14                     | 23              | B13                               | I           | Analog         |                                                                                                                                                                                                   |

| AN3      | 13                     | 22              | A13                               | I           | Analog         |                                                                                                                                                                                                   |

| AN4      | 12                     | 21              | B11                               | I           | Analog         |                                                                                                                                                                                                   |

| AN5      | 11                     | 20              | A12                               | I           | Analog         |                                                                                                                                                                                                   |

| AN6      | 17                     | 26              | A20                               | I           | Analog         |                                                                                                                                                                                                   |

| AN7      | 18                     | 27              | B16                               | I           | Analog         |                                                                                                                                                                                                   |

| AN8      | 21                     | 32              | A23                               | I           | Analog         |                                                                                                                                                                                                   |

| AN9      | 22                     | 33              | B19                               | I           | Analog         |                                                                                                                                                                                                   |

| AN10     | 23                     | 34              | A24                               | I           | Analog         |                                                                                                                                                                                                   |

| AN11     | 24                     | 35              | B20                               | I           | Analog         |                                                                                                                                                                                                   |

| AN12     | 27                     | 41              | B23                               | I           | Analog         |                                                                                                                                                                                                   |

| AN13     | 28                     | 42              | A28                               | I           | Analog         | Analog input channels.                                                                                                                                                                            |

| AN14     | 29                     | 43              | B24                               | I           | Analog         |                                                                                                                                                                                                   |

| AN15     | 30                     | 44              | A29                               | I           | Analog         |                                                                                                                                                                                                   |

| AN16     | 4                      | 10              | A7                                | I           | Analog         |                                                                                                                                                                                                   |

| AN17     | 5                      | 11              | B6                                | I           | Analog         |                                                                                                                                                                                                   |

| AN18     | 6                      | 12              | A8                                | I           | Analog         |                                                                                                                                                                                                   |

| AN19     | 8                      | 14              | A9                                | I           | Analog         |                                                                                                                                                                                                   |

| AN20     | 62                     | 98              | A66                               | I           | Analog         |                                                                                                                                                                                                   |

| AN21     | 64                     | 100             | A67                               | I           | Analog         |                                                                                                                                                                                                   |

| AN22     | 1                      | 3               | B2                                | I           | Analog         |                                                                                                                                                                                                   |

| AN23     | 2                      | 4               | A4                                | I           | Analog         |                                                                                                                                                                                                   |

| AN24     | 49                     | 76              | A52                               | I           | Analog         |                                                                                                                                                                                                   |

| AN25     | 50                     | 77              | B42                               | I           | Analog         |                                                                                                                                                                                                   |

| AN26     | 51                     | 78              | A53                               | I           | Analog         |                                                                                                                                                                                                   |

| AN27     | 3                      | 5               | B3                                | I           | Analog         |                                                                                                                                                                                                   |

| CLKI     | 39                     | 63              | B34                               | I           | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.                                                                                                                            |

| CLKO     | 40                     | 64              | A42                               | 0           | _              | Oscillator crystal output. Connects to crystal or reso-<br>nator in Crystal Oscillator mode. Optionally functions<br>as CLKO in RC and EC modes. Always associated<br>with the OSC2 pin function. |

| OSC1     | 39                     | 63              | B34                               | I           | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                                   |

| OSC2     | 40                     | 64              | A42                               | 0           | _              | Oscillator crystal output. Connects to crystal or reso-<br>nator in Crystal Oscillator mode. Optionally functions<br>as CLKO in RC and EC modes.                                                  |

| SOSCI    | 47                     | 73              | A47                               | Ι           | ST/CMOS        | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                                    |

| SOSCO    | 48                     | 74              | B40                               | 0           | —              | 32.768 kHz low-power oscillator crystal output.                                                                                                                                                   |

| -        | ST = Schm              |                 | tible input or o<br>out with CMOS |             |                | alog = Analog input P = Power<br>= Output I = Input                                                                                                                                               |

TTL = TTL input buffer

Note 1: This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

**3:** This pin is not available on 64-pin devices.

## 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MCUS

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the documents listed in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

## 2.1 Basic Connection Requirements

Getting started with the PIC32MX330/350/370/430/ 450/470 family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins, even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- VCAP pin (see 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins, used for In-Circuit Serial Programming (ICSP<sup>™</sup>) and debugging purposes (see **2.5** "ICSP Pins")

- OSC1 and OSC2 pins, when external oscillator source is used (see 2.8 "External Oscillator Pins")

The following pins may be required:

VREF+/VREF- pins, used when external voltage reference for the ADC module is implemented.

**Note:** The AVDD and AVSS pins must be connected, regardless of ADC use and the ADC voltage reference source.

## 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1  $\mu$ F (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 31:24        |                   |                   | _                 | —                 | _                 | —                 |                  | —                |  |  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 23:16        | _                 | —                 | —                 | —                 |                   | —                 | —                | —                |  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |  |  |  |

| 15:8         | BMXDUPBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R-0 R-0           |                   | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | BMXDU             | PBA<7:0>          |                   |                  |                  |  |  |  |  |  |  |

#### REGISTER 4-4: BMXDUPBA: DATA RAM USER PROGRAM BASE ADDRESS REGISTER

## Legend:

| Legenu.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-10 BMXDUPBA<15:10>: DRM User Program Base Address bits

When non-zero, the value selects the relative base address for User mode program space in RAM, BMXDUPBA must be greater than BMXDUDBA.

bit 9-0 BMXDUPBA<9:0>: Read-Only bits Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernel mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

## 5.1 Control Registers

## TABLE 5-1: FLASH CONTROLLER REGISTER MAP

| ess                         |                        | 0         |       |                                              |       |       |       |       |      | Bi        | ts        |      |      |      |      |      |      |      | 6          |

|-----------------------------|------------------------|-----------|-------|----------------------------------------------|-------|-------|-------|-------|------|-----------|-----------|------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name       | Bit Range | 31/15 | 30/14                                        | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8      | 23/7      | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| E400                        | NVMCON <sup>(1)</sup>  | 31:16     |       |                                              |       |       |       |       |      |           |           |      |      |      |      |      |      |      |            |

| 1400                        | NVINCON /              | 15:0      | WR    | VR WREN WRERR LVDERR LVDSTAT NVMOP<3:0> 0000 |       |       |       |       |      |           |           |      |      |      |      |      |      |      |            |

| F410                        | NVMKEY                 | 31:16     |       |                                              |       |       |       |       |      | NVMKE     | V<31·0>   |      |      |      |      |      |      |      | 0000       |

|                             |                        | 15:0      |       |                                              |       |       |       |       |      |           |           |      |      | 0000 |      |      |      |      |            |

| E420                        | NVMADDR <sup>(1)</sup> | 31:16     |       |                                              |       |       |       |       |      | NVMADE    | D-31.05   |      |      |      |      |      |      |      | 0000       |

| 1 420                       | NVINADDIX              | 15:0      |       |                                              |       |       |       |       |      | INVINADL  | 11-31.02  |      |      |      |      |      |      |      | 0000       |

| F430                        | NVMDATA                | 31:16     |       |                                              |       |       |       |       |      | NVMDAT    | A-21:0>   |      |      |      |      |      |      |      | 0000       |

| F430                        | NVINDATA               | 15:0      |       |                                              |       |       |       |       |      | INVIVIDAI | A<31.0>   |      |      |      |      |      |      |      | 0000       |

| F440                        | NVMSRC                 | 31:16     |       |                                              |       |       |       |       |      | VMSRCA    | 221.05    |      |      |      |      |      |      |      | 0000       |

| F440                        | ADDR                   | 15:0      |       |                                              |       |       |       |       | I    | NVIVISRCA | JUK<31:0> | •    |      |      |      |      |      |      | 0000       |

PIC32MX330/350/370/430/450/470

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4     | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|----------------------|-----------------------|------------------------|-------------------|------------------|------------------|--|

| 24.04        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0              | U-0              |  |

| 31:24        | _                 | —                 | —                    | —                     | —                      | —                 | —                | _                |  |

| 23:16        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0              | U-0              |  |

| 23.10        | —                 | —                 | -                    | —                     | —                      | —                 |                  | —                |  |

| 45.0         | R/W-0             | R/W-0             | R-0                  | R-0                   | R-0                    | U-0               | U-0              | U-0              |  |

| 15:8         | WR                | WREN              | WRERR <sup>(1)</sup> | LVDERR <sup>(1)</sup> | LVDSTAT <sup>(1)</sup> | —                 | —                | _                |  |

| 7.0          | U-0               | U-0               | U-0                  | U-0                   | R/W-0                  | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | —                 | —                 |                      | —                     |                        | NVMOF             | °<3:0>           |                  |  |

#### REGISTER 5-1: NVMCON: PROGRAMMING CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

|-------------------|------------------|-----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

| bit 15   | WR: Write Control bit                                                                                               |

|----------|---------------------------------------------------------------------------------------------------------------------|

|          | This bit is writable when WREN = 1 and the unlock sequence is followed.                                             |

|          | 1 = Initiate a Flash operation. Hardware clears this bit when the operation completes                               |

|          | 0 = Flash operation complete or inactive                                                                            |

| bit 14   | WREN: Write Enable bit                                                                                              |

|          | 1 = Enable writes to WR bit and enables LVD circuit                                                                 |

|          | 0 = Disable writes to WR bit and disables LVD circuit                                                               |

|          | This is the only bit in this register reset by a device Reset.                                                      |

| bit 13   | WRERR: Write Error bit <sup>(1)</sup>                                                                               |

|          | This bit is read-only and is automatically set by hardware.                                                         |

|          | 1 = Program or erase sequence did not complete successfully                                                         |

|          | 0 = Program or erase sequence completed normally                                                                    |

| bit 12   | LVDERR: Low-Voltage Detect Error bit (LVD circuit must be enabled) <sup>(1)</sup>                                   |

|          | This bit is read-only and is automatically set by hardware.                                                         |

|          | 1 = Low-voltage detected (possible data corruption, if WRERR is set)                                                |

|          | 0 = Voltage level is acceptable for programming                                                                     |

| bit 11   | LVDSTAT: Low-Voltage Detect Status bit (LVD circuit must be enabled) <sup>(1)</sup>                                 |

|          | This bit is read-only and is automatically set, and cleared, by hardware.                                           |

|          | 1 = Low-voltage event active                                                                                        |

|          | 0 = Low-voltage event NOT active                                                                                    |

| bit 10-4 | Unimplemented: Read as '0'                                                                                          |

| bit 3-0  | NVMOP<3:0>: NVM Operation bits                                                                                      |

|          | These bits are writable when WREN = 0.                                                                              |

|          | 1111 = Reserved                                                                                                     |

|          | •                                                                                                                   |

|          |                                                                                                                     |

|          | 0111 = Reserved                                                                                                     |

|          | 0110 = No operation                                                                                                 |

|          | 0101 = Program Flash (PFM) erase operation: erases PFM, if all pages are not write-protected                        |

|          | 0100 = Page erase operation: erases page selected by NVMADDR, if it is not write-protected                          |

|          | 0011 = Row program operation: programs row selected by NVMADDR, if it is not write-protected<br>0010 = No operation |

|          | 0001 = Word program operation: programs word selected by NVMADDR, if it is not write-protected                      |

|          | 0000 = No operation                                                                                                 |

|          |                                                                                                                     |

|          |                                                                                                                     |

**Note 1:** This bit is cleared by setting NVMOP = 0000, and initiating a Flash operation (i.e., WR).

| REGIST  | ER 7-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER (CONTINUED)                                                                                                                    |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 9-8 | IS1<1:0>: Interrupt Subpriority bits<br>11 = Interrupt subpriority is 3<br>10 = Interrupt subpriority is 2<br>01 = Interrupt subpriority is 1<br>00 = Interrupt subpriority is 0 |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                       |

| bit 4-2 | IP0<2:0>: Interrupt Priority bits                                                                                                                                                |

|         | <pre>111 = Interrupt priority is 7</pre>                                                                                                                                         |

|         | 001 = Interrupt priority is 1<br>000 = Interrupt is disabled                                                                                                                     |

| bit 1-0 | ISO<1:0>: Interrupt Subpriority bits                                                                                                                                             |

|         | <pre>11 = Interrupt subpriority is 3 10 = Interrupt subpriority is 2 01 = Interrupt subpriority is 1 00 = Interrupt subpriority is 0</pre>                                       |

| Note:   | This register represents a generic definition of the IPCx register. Refer to Table 7-1 for the exact bit definitions.                                                            |

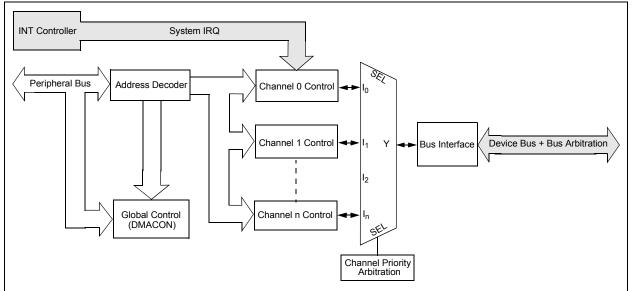

## 10.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 31. "Direct Memory Access (DMA) Controller" (DS60001117), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32 Direct Memory Access (DMA) controller is a bus master module useful for data transfers between different devices without CPU intervention. The source and destination of a DMA transfer can be any of the memory mapped modules existent in the PIC32 (such as Peripheral Bus (PBUS) devices: SPI, UART, PMP, etc.) or memory itself.

Following are some of the key features of the DMA controller module:

- Four identical channels, each featuring:

- Auto-increment source and destination address registers

- Source and destination pointers

- Memory to memory and memory to peripheral transfers

- Automatic word-size detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source and destination

- Fixed priority channel arbitration

- · Flexible DMA channel operating modes:

- Manual (software) or automatic (interrupt) DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- · Flexible DMA requests:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any (appropriate) observable interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Pattern (data) match transfer termination

- · Multiple DMA channel status interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- DMA debug support features:

- Most recent address accessed by a DMA channel

- Most recent DMA channel to transfer data

- · CRC Generation module:

- CRC module can be assigned to any of the available channels

- CRC module is highly configurable

## FIGURE 10-1: DMA BLOCK DIAGRAM

#### REGISTER 10-9: DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER (CONTINUED)

bit 4 **CHDHIF:** Channel Destination Half Full Interrupt Flag bit

- 1 = Channel Destination Pointer has reached midpoint of destination (CHDPTR = CHDSIZ/2)

- 0 = No interrupt is pending

- bit 3 CHBCIF: Channel Block Transfer Complete Interrupt Flag bit

- 1 = A block transfer has been completed (the larger of CHSSIZ/CHDSIZ bytes has been transferred), or a pattern match event occurs

- 0 = No interrupt is pending

- bit 2 CHCCIF: Channel Cell Transfer Complete Interrupt Flag bit

- 1 = A cell transfer has been completed (CHCSIZ bytes have been transferred)

- 0 = No interrupt is pending

- bit 1 CHTAIF: Channel Transfer Abort Interrupt Flag bit

- 1 = An interrupt matching CHAIRQ has been detected and the DMA transfer has been aborted

- 0 = No interrupt is pending

- bit 0 CHERIF: Channel Address Error Interrupt Flag bit

- 1 = A channel address error has been detected

- Either the source or the destination address is invalid.

- 0 = No interrupt is pending

| Bit<br>Range   | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|----------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24<br>23:16 |                   | _                 |                   |                   |                   | —                 |                  | —                |

| 22:16          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10          | -                 | _                 |                   |                   | -                 | —                 |                  | —                |

| 15:8           | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0           | -                 | _                 |                   |                   | -                 | —                 |                  | —                |

| 7:0            | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | R/W-0            |

| 7.0            | IDIE              | T1MSECIE          | LSTATEIE          | ACTVIE            | SESVDIE           | SESENDIE          |                  | VBUSVDIE         |

#### REGISTER 11-2: U10TGIE: USB OTG INTERRUPT ENABLE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **IDIE:** ID Interrupt Enable bit

- 1 = ID interrupt is enabled

- 0 = ID interrupt is disabled

- bit 6 T1MSECIE: 1 Millisecond Timer Interrupt Enable bit

- 1 = 1 millisecond timer interrupt is enabled

- 0 = 1 millisecond timer interrupt is disabled

- bit 5 LSTATEIE: Line State Interrupt Enable bit

- 1 = Line state interrupt is enabled

- 0 = Line state interrupt is disabled

- bit 4 ACTVIE: Bus Activity Interrupt Enable bit

- 1 = ACTIVITY interrupt is enabled

- 0 = ACTIVITY interrupt is disabled

- bit 3 SESVDIE: Session Valid Interrupt Enable bit

- 1 = Session valid interrupt is enabled

- 0 = Session valid interrupt is disabled

- bit 2 SESENDIE: B-Session End Interrupt Enable bit

- 1 = B-session end interrupt is enabled

- 0 = B-session end interrupt is disabled

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIE: A-VBUS Valid Interrupt Enable bit

- 1 = A-VBUS valid interrupt is enabled

- 0 = A-VBUS valid interrupt is disabled

|                             |                                 | P         | C32MX         | 430F064       | L, PIC3       | 2MX450        | F128L,        | PIC32M        | X450F2       | 56L, AN      | ID PIC3      | 2MX47        | 0F512L       | DEVIC        | ES ONL       | .Y           |              |              |               |

|-----------------------------|---------------------------------|-----------|---------------|---------------|---------------|---------------|---------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| ess                         |                                 |           |               |               |               |               |               |               |              | Bits         | 6            |              |              |              |              |              |              |              |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14         | 29/13         | 28/12         | 27/11         | 26/10         | 25/9         | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6300                        | ANSELD                          | 31:16     |               | —             | —             | —             | —             |               | —            | —            | —            |              | —            | —            | —            |              | —            |              | 0000          |

|                             |                                 | 15:0      | _             | —             | —             | _             | —             | —             | —            | —            | —            | _            | —            | —            | ANSELD3      | ANSELD2      | ANSELD1      | _            | 000E          |

| 6310                        | TRISD                           | 31:16     | _             | —             | —             | —             | —             | —             | —            | —            | —            |              | —            | _            | _            | _            | —            | _            | 0000          |

|                             | _                               | 15:0      | TRISD15       | TRISD14       | TRISD13       | TRISD12       | TRISD11       | TRISD10       | TRISD9       | TRISD8       | TRISD7       | TRISD6       | TRISD5       | TRISD4       | TRISD3       | TRISD2       | TRISD1       | TRISD0       | xxxx          |

| 5320                        | PORTD                           | 31:16     | _             | —             | _             | —             | —             | —             | —            | —            | —            |              | —            | —            |              | —            | —            | _            | 0000          |

|                             | _                               | 15:0      | RD15          | RD14          | RD13          | RD12          | RD11          | RD10          | RD9          | RD8          | RD7          | RD6          | RD5          | RD4          | RD3          | RD2          | RD1          | RD0          | xxxx          |

| 6330                        | LATD                            | 31:16     |               | —             | —             | —             | —             | —             | —            | —            | —            | —            | —            | —            | —            |              | —            | —            | 0000          |

|                             |                                 | 15:0      | LATD15        | LATD14        | LATD13        | LATD12        | LATD11        | LATD10        | LATD9        | LATD8        | LATD7        | LATD6        | LATD5        | LATD4        | LATD3        | LATD2        | LATD1        | LATD0        | XXXX          |

| 6340                        | ODCD                            | 31:16     | —             | —             | —             | —             | —             | —             | —            | —            | —            | —            | —            | —            | —            | —            | —            | _            | 0000          |

|                             |                                 | 15:0      | ODCD15        | ODCD14        | ODCD13        | ODCD12        | ODCD11        | ODCD10        | ODCD9        | ODCD8        | ODCD7        | ODCD6        | ODCD5        | ODCD4        | ODCD3        | ODCD2        | ODCD1        | ODCD0        | xxxx          |

| 6350                        | CNPUD                           | 31:16     | -             | —             | —             | —             | —             | -             | —            | —            | —            | —            | —            | —            | —            | —            | —            | -            | 0000          |

|                             |                                 | 15:0      | CNPUD15       | CNPUD14       | CNPUD13       | CNPUD12       | CNPUD11       | CNPUD10       |              | CNPUD8       | CNPUD7       | CNPUD6       | CNPUD5       | CNPUD4       | CNPUD3       | CNPUD2       | CNPUD1       | CNPUD0       | xxxx          |

| 6360                        | CNPDD                           | 31:16     | -             | —             | —             | —             | —             | -             | —            | —            | —            | —            | _            | —            | —            | —            | —            | _            | 0000          |

|                             |                                 |           | CNPDD15       | -             | CNPDD13       | CNPDD12       | CNPDD11       | CNPDD10       |              | CNPDD8       | -            | CNPDD6       |              | CNPDD4       | CNPDD3       | CNPDD2       | CNPDD1       | CNPDD0       | XXXX          |

| 6370                        | CNCOND                          | 31:16     | _             |               | -             |               |               |               |              |              |              |              |              |              |              | _            |              |              | 0000          |

|                             |                                 | 15:0      | ON            |               | SIDL          |               |               |               |              |              |              |              |              |              |              | _            |              |              | 0000          |

| 6380                        | CNEND                           | 31:16     | -             | -             | -             | -             |               |               | -            | -            | -            |              | -            | -            | -            | -            |              |              | 0000          |

|                             |                                 | 15:0      | CNIED15       | CNIED14       | CNIED13       | CNIED12       | CNIED11       | CNIED10       | CNIED9       | CNIED8       | CNIED7       | CNIED6       | CNIED5       | CNIED4       | CNIED3       | CNIED2       | CNIED1       | CNIED0       | XXXX          |

| 6200                        |                                 | 31:16     | -             | -             | —             | —             | —             | -             | -            | -            | -            | -            | —            | -            | —            | —            | —            | -            | 0000          |

| 6390                        | CNSTATD                         | 15:0      | CNS<br>TATD15 | CN<br>STATD14 | CN<br>STATD13 | CN<br>STATD12 | CN<br>STATD11 | CN<br>STATD10 | CN<br>STATD9 | CN<br>STATD8 | CN<br>STATD7 | CN<br>STATD6 | CN<br>STATD5 | CN<br>STATD4 | CN<br>STATD3 | CN<br>STATD2 | CN<br>STATD1 | CN<br>STATD0 | xxxx          |

## TABLE 12-7: PORTD REGISTER MAP FOR PIC32MX330F064L, PIC32MX350F128L, PIC32MX350F256L, PIC32MX370F512L,

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

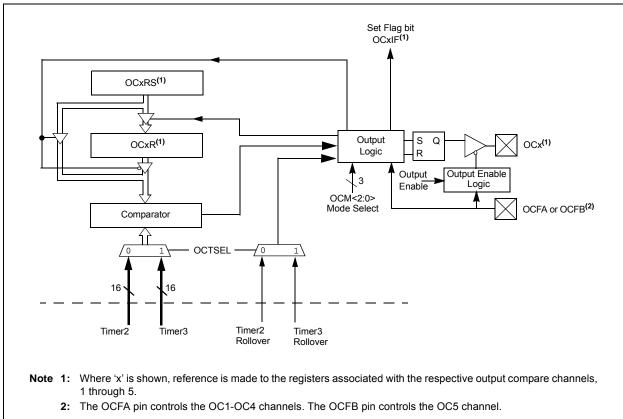

## 17.0 OUTPUT COMPARE

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 16. "Output Compare" (DS60001111), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Output Compare module is used to generate a single pulse or a train of pulses in response to selected time base events. For all modes of operation, the Output Compare module compares the values stored in the OCxR and/or the OCxRS registers to the value in the selected timer. When a match occurs, the Output Compare module generates an event based on the selected mode of operation.

The following are key features of this module:

- Multiple Output Compare modules in a device

- Programmable interrupt generation on compare event

- Single and Dual Compare modes

- Single and continuous output pulse generation

- Pulse-Width Modulation (PWM) mode

- Hardware-based PWM Fault detection and automatic output disable

- Can operate from either of two available 16-bit time bases or a single 32-bit time base

## FIGURE 17-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

# PIC32MX330/350/370/430/450/470

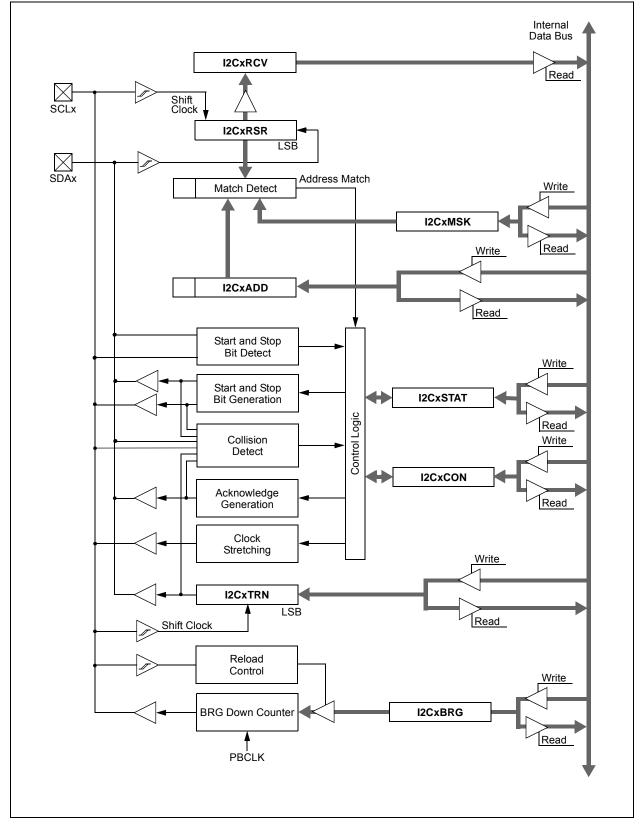

## FIGURE 19-1: I<sup>2</sup>C BLOCK DIAGRAM

## PIC32MX330/350/370/430/450/470

## REGISTER 19-1: I2CxCON: I<sup>2</sup>C CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                 | —                 | —                 | —                 | —                 | _                 | _                | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | —                 | —                 | _                 | _                 | _                | _                |  |  |  |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-1, HC         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | 0N <sup>(1)</sup> | —                 | SIDL              | SCLREL            | STRICT            | A10M              | DISSLW           | SMEN             |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |  |  |  |

| 7:0          | GCEN              | STREN             | ACKDT             | ACKEN             | RCEN              | PEN               | RSEN             | SEN              |  |  |  |

| Legend:           | HC = Cleared in Hardware |                                    |                    |  |  |  |

|-------------------|--------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** I<sup>2</sup>C Enable bit<sup>(1)</sup>

- 1 = Enables the  $I^2C$  module and configures the SDA and SCL pins as serial port pins

- 0 = Disables the  $I^2$ C module; all  $I^2$ C pins are controlled by PORT functions

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

- **SCLREL:** SCLx Release Control bit (when operating as I<sup>2</sup>C slave)

- 1 = Release SCLx clock

bit 12

- 0 = Hold SCLx clock low (clock stretch)

- If STREN = 1:

Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware clear at beginning of slave transmission. Hardware clear at end of slave reception.

#### If STREN = 0:

Bit is R/S (i.e., software can only write '1' to release clock). Hardware clear at beginning of slave transmission.

- bit 11 STRICT: Strict I<sup>2</sup>C Reserved Address Rule Enable bit

- 1 = Strict reserved addressing is enforced. Device does not respond to reserved address space or generate addresses in reserved address space.

- 0 = Strict I<sup>2</sup>C Reserved Address Rule is not enabled

#### bit 10 A10M: 10-bit Slave Address bit

- 1 = I2CxADD is a 10-bit slave address

- 0 = I2CxADD is a 7-bit slave address

- bit 9 **DISSLW:** Disable Slew Rate Control bit

- 1 = Slew rate control is disabled

- 0 = Slew rate control is enabled

- bit 8 SMEN: SMBus Input Levels bit

- 1 = Enable I/O pin thresholds compliant with SMBus specification

- 0 = Disable SMBus input thresholds

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

NOTES:

|                             | LE 20-1:              |           |        | HROUG   |        |       |        |       |       | -0)         |                 |         |       |          |          |      |          |       | -          |

|-----------------------------|-----------------------|-----------|--------|---------|--------|-------|--------|-------|-------|-------------|-----------------|---------|-------|----------|----------|------|----------|-------|------------|

| ess)                        |                       | ۵         |        |         |        |       |        |       |       | Bi          | ts              |         |       |          |          |      |          |       | s          |

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15  | 30/14   | 29/13  | 28/12 | 27/11  | 26/10 | 25/9  | 24/8        | 23/7            | 22/6    | 21/5  | 20/4     | 19/3     | 18/2 | 17/1     | 16/0  | All Resets |

| 6440                        |                       | 31:16     | _      |         |        | —     | _      | —     |       | —           | —               | —       | —     | —        | —        | —    | —        | _     | 0000       |

| 0440                        | U3BKG.                | 15:0      |        |         |        | -     |        |       | Bau   | d Rate Gene | erator Pres     | caler   |       |          | -        | -    | -        |       | 0000       |

| 6600 U4N                    |                       | 31:16     | _      | —       | —      | —     | —      | _     | _     | —           | —               | —       | —     | —        | —        | —    | —        | —     | 0000       |

|                             | OIMODE                | 15:0      | ON     | —       | SIDL   | IREN  | RTSMD  | —     | UEN   | <1:0>       | WAKE            | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0>   | STSEL | 0000       |

| 6610                        | U4STA <sup>(1)</sup>  | 31:16     | —      | —       | —      | —     | —      | —     | —     | ADM_EN      | DM_EN ADDR<7:0> |         |       |          |          | 0000 |          |       |            |

| 0010                        | 04017                 | 15:0      | UTXISE | EL<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISI          | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR     | URXDA | FFFF       |

| 6620                        | U4TXREG               | 31:16     | —      | —       | —      | —     | —      | —     | —     | —           | —               | _       | —     | —        | —        | —    | —        | —     | 0000       |

| 0020                        |                       | 15:0      | —      | —       | —      | —     | —      | —     | —     | TX8         |                 |         |       | Transmit | Register |      |          |       | 0000       |

| 6630                        | U4RXREG               | 31:16     | —      | —       | —      | —     | —      | _     | _     | —           | —               | —       | —     | _        | —        | —    | —        | —     | 0000       |

|                             | 0.1.0.1.20            | 15:0      | _      | —       | —      | —     | —      | _     | _     | RX8         |                 |         |       | Receive  | Register |      |          |       | 0000       |

| 6640                        | U4BRG <sup>(1)</sup>  | 31:16     | —      | _       | _      | —     | —      | _     | —     | _           | —               | —       | —     | —        | —        | —    | —        | —     | 0000       |

|                             | 0.5.10                | 15:0      |        |         |        |       |        |       |       |             |                 |         | 0000  |          |          |      |          |       |            |

| 6800                        | U5MODE <sup>(1)</sup> | 31:16     | _      | _       | —      | —     | —      | —     |       | —           | —               |         | —     | —        | _        |      | <u> </u> | _     | 0000       |

|                             |                       | 10.0      | ON     | —       | SIDL   | IREN  | RTSMD  | —     | UEN   | <1:0>       | WAKE            | LPBACK  | ABAUD | RXINV    | BRGH     | PDSE | L<1:0>   | STSEL | 0000       |

| 6810                        | U5STA <sup>(1)</sup>  | 31:16     | _      |         | _      | —     | —      | —     |       | ADM_EN      |                 |         |       |          | R<7:0>   | 1    | 1        |       | 0000       |

|                             |                       | 15:0      | UTXISE | EL<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXIS           | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR | OERR     | URXDA | FFFF       |

| 6820                        | U5TXREG               | 31:16     | _      | _       | _      | —     | —      | —     |       | —           | —               | —       | —     | —        | —        |      | <u> </u> | _     | 0000       |

| 0020                        |                       | 15:0      | _      | —       | —      | —     | —      | _     | _     | TX8         |                 |         |       | Transmit | Register |      |          |       | 0000       |

| 6830                        | U5RXREG               | 31:16     | _      | —       | —      | —     | —      | _     | _     | —           | —               | —       | —     | —        | —        | —    | —        | —     | 0000       |

|                             |                       | 15:0      | _      | _       | _      |       | —      | _     |       | RX8         |                 |         |       | Receive  | Register |      |          |       | 0000       |

| 6840                        | U5BRG <sup>(1)</sup>  | 31:16     | _      | _       | _      | —     | —      | _     | —     | —           | _               | —       | —     | _        | —        | —    | —        | —     | 0000       |

|                             |                       | 15:0      |        |         |        |       |        |       | Bau   | d Rate Gene | erator Pres     | caler   |       |          |          |      |          |       | 0000       |

#### TABLE 20-1: UART1 THROUGH UART5 REGISTER MAP (CONTINUED)

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>3/15/7<br>R          | Bit<br>30/22/14/6<br>R | Bit<br>29/21/13/5    | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                        | Bit<br>26/18/10/2                                                                   | Bit<br>25/17/9/1                                                                        | Bit<br>24/16/8/0                                                                               |  |  |  |  |  |  |  |  |  |

|-----------------------------|------------------------|----------------------|-------------------|------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| R                           | R                      | Р                    |                   |                                          |                                                                                     |                                                                                         | 24/10/0/0                                                                                      |  |  |  |  |  |  |  |  |  |

|                             |                        | R                    | R                 | R                                        | R                                                                                   | R                                                                                       | R                                                                                              |  |  |  |  |  |  |  |  |  |

|                             | VER<                   | :3:0> <sup>(1)</sup> |                   | DEVID<27:24> <sup>(1)</sup>              |                                                                                     |                                                                                         |                                                                                                |  |  |  |  |  |  |  |  |  |

| R                           | R                      | R                    | R                 | R                                        | R                                                                                   | R                                                                                       | R                                                                                              |  |  |  |  |  |  |  |  |  |

| DEVID<23:16> <sup>(1)</sup> |                        |                      |                   |                                          |                                                                                     |                                                                                         |                                                                                                |  |  |  |  |  |  |  |  |  |

| R                           | R                      | R                    | R                 | R                                        | R                                                                                   | R                                                                                       | R                                                                                              |  |  |  |  |  |  |  |  |  |

| DEVID<15:8> <sup>(1)</sup>  |                        |                      |                   |                                          |                                                                                     |                                                                                         |                                                                                                |  |  |  |  |  |  |  |  |  |

| R                           | R                      | R                    | R                 | R                                        | R                                                                                   | R                                                                                       | R                                                                                              |  |  |  |  |  |  |  |  |  |

|                             |                        |                      | DEVID<            | 7:0>(1)                                  |                                                                                     | DEVID<7:0>(1)                                                                           |                                                                                                |  |  |  |  |  |  |  |  |  |

| R                           | 2                      | R R                  | R R               | DEVID<2<br>R R R R<br>DEVID<7<br>R R R R | DEVID<23:16> <sup>(1)</sup><br>R R R R R<br>DEVID<15:8> <sup>(1)</sup><br>R R R R R | DEVID<23:16> <sup>(1)</sup><br>R R R R R R<br>DEVID<15:8> <sup>(1)</sup><br>R R R R R R | DEVID<23:16>(1)       R     R     R     R       DEVID<15:8> <sup>(1)</sup> R     R     R     R |  |  |  |  |  |  |  |  |  |

### REGISTER 28-6: DEVID: DEVICE AND REVISION ID REGISTER

#### Legend:

| Logona.           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 31-28 VER<3:0>: Revision Identifier bits<sup>(1)</sup>

bit 27-0 **DEVID<27:0>:** Device ID<sup>(1)</sup>

Note 1: See the "PIC32 Flash Programming Specification" (DS60001145) for a list of Revision and Device ID values.

### 30.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 30.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 30.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 30.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

## 30.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

| AC CHA        | RACTERIS | STICS                      |                        | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |       |                            |  |  |

|---------------|----------|----------------------------|------------------------|------------------------------------------------------|------|-------|----------------------------|--|--|

| Param.<br>No. | Symbol   | Charact                    | eristics               | Min.                                                 | Max. | Units | Conditions                 |  |  |

| IS34          | THD:STO  | Stop Condition             | 100 kHz mode           | 4000                                                 | _    | ns    | —                          |  |  |

|               |          | Hold Time                  | 400 kHz mode           | 600                                                  | _    | ns    |                            |  |  |

|               |          |                            | 1 MHz mode<br>(Note 1) | 250                                                  |      | ns    |                            |  |  |

| IS40          | TAA:SCL  | Output Valid from<br>Clock | 100 kHz mode           | 0                                                    | 3500 | ns    | —                          |  |  |

|               |          |                            | 400 kHz mode           | 0                                                    | 1000 | ns    |                            |  |  |

|               |          |                            | 1 MHz mode<br>(Note 1) | 0                                                    | 350  | ns    |                            |  |  |

| IS45          | TBF:SDA  | Bus Free Time              | 100 kHz mode           | 4.7                                                  | —    | μs    | The amount of time the bus |  |  |

|               |          |                            | 400 kHz mode           | 1.3                                                  |      | μs    | must be free before a new  |  |  |

|               |          |                            | 1 MHz mode<br>(Note 1) | 0.5                                                  | —    | μS    | transmission can start     |  |  |

| IS50          | Св       | Bus Capacitive Lo          | ading                  |                                                      | 400  | pF    | —                          |  |  |

## TABLE 31-34: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE) (CONTINUED)

**Note 1:** Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

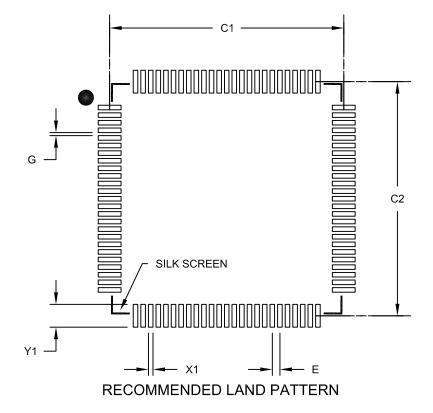

100-Lead Plastic Thin Quad Flatpack (PF) - 14x14x1 mm Body 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | MILLIMETERS |      |          |      |

|---------------------------|-------------|------|----------|------|

| Dimensior                 | MIN         | NOM  | MAX      |      |

| Contact Pitch             | E           |      | 0.50 BSC | -    |

| Contact Pad Spacing       | C1          |      | 15.40    |      |

| Contact Pad Spacing       | C2          |      | 15.40    |      |

| Contact Pad Width (X100)  | X1          |      |          | 0.30 |

| Contact Pad Length (X100) | Y1          |      |          | 1.50 |

| Distance Between Pads     | G           | 0.20 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2110B