#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 124-VFTLA Dual Rows, Exposed Pad                                                |

| Supplier Device Package    | 124-VTLA (9x9)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx330f064lt-v-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

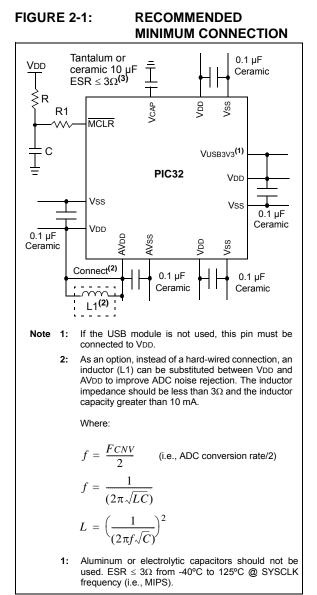

## 2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve power supply stability. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ . This capacitor should be located as close to the device as possible.

# 2.3 Capacitor on Internal Voltage Regulator (VCAP)

#### 2.3.1 INTERNAL REGULATOR MODE

A low-ESR (3 ohm) capacitor is required on the VCAP pin, which is used to stabilize the internal voltage regulator output. The VCAP pin must not be connected to VDD, and must have a CEFC capacitor, with at least a 6V rating, connected to ground. The type can be ceramic or tantalum. Refer to **Section 31.0 "Electrical Characteristics"** for additional information on CEFC specifications.

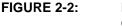

## 2.4 Master Clear (MCLR) Pin

The  $\overline{\text{MCLR}}$  pin provides two specific device functions:

- Device Reset

- · Device programming and debugging

Pulling The  $\overline{\text{MCLR}}$  pin low generates a device Reset. Figure 2-2 illustrates a typical  $\overline{\text{MCLR}}$  circuit. During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as illustrated in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components illustrated in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

3:

## EXAMPLE OF MCLR PIN CONNECTIONS

No pull-ups or bypass capacitors are allowed on

active debug/program PGECx/PGEDx pins.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        |                   | _                 | _                 | —                 | _                 | —                 |                  | —                |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | _                 | —                 | —                 | —                 |                   | —                 | —                | —                |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |  |

| 15:8         | BMXDUPBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 7:0          |                   |                   |                   | BMXDU             | PBA<7:0>          |                   |                  |                  |  |  |  |  |

### REGISTER 4-4: BMXDUPBA: DATA RAM USER PROGRAM BASE ADDRESS REGISTER

## Legend:

| Legenu.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-10 BMXDUPBA<15:10>: DRM User Program Base Address bits

When non-zero, the value selects the relative base address for User mode program space in RAM, BMXDUPBA must be greater than BMXDUDBA.

bit 9-0 BMXDUPBA<9:0>: Read-Only bits Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernel mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

## TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION

| Internet Course(1)                  | IDO # | Vector |              | Persistent   |             |              |           |

|-------------------------------------|-------|--------|--------------|--------------|-------------|--------------|-----------|

| Interrupt Source <sup>(1)</sup>     | IRQ # | #      | Flag         | Enable       | Priority    | Sub-priority | Interrupt |

|                                     |       | Highe  | st Natural O | der Priority |             |              |           |

| CT – Core Timer Interrupt           | 0     | 0      | IFS0<0>      | IEC0<0>      | IPC0<4:2>   | IPC0<1:0>    | No        |

| CS0 – Core Software Interrupt 0     | 1     | 1      | IFS0<1>      | IEC0<1>      | IPC0<12:10> | IPC0<9:8>    | No        |

| CS1 – Core Software Interrupt 1     | 2     | 2      | IFS0<2>      | IEC0<2>      | IPC0<20:18> | IPC0<17:16>  | No        |

| INT0 – External Interrupt           | 3     | 3      | IFS0<3>      | IEC0<3>      | IPC0<28:26> | IPC0<25:24>  | No        |

| T1 – Timer1                         | 4     | 4      | IFS0<4>      | IEC0<4>      | IPC1<4:2>   | IPC1<1:0>    | No        |

| IC1E – Input Capture 1 Error        | 5     | 5      | IFS0<5>      | IEC0<5>      | IPC1<12:10> | IPC1<9:8>    | Yes       |

| IC1 – Input Capture 1               | 6     | 5      | IFS0<6>      | IEC0<6>      | IPC1<12:10> | IPC1<9:8>    | Yes       |

| OC1 – Output Compare 1              | 7     | 6      | IFS0<7>      | IEC0<7>      | IPC1<20:18> | IPC1<17:16>  | No        |

| INT1 – External Interrupt 1         | 8     | 7      | IFS0<8>      | IEC0<8>      | IPC1<28:26> | IPC1<25:24>  | No        |

| T2 – Timer2                         | 9     | 8      | IFS0<9>      | IEC0<9>      | IPC2<4:2>   | IPC2<1:0>    | No        |

| IC2E – Input Capture 2              | 10    | 9      | IFS0<10>     | IEC0<10>     | IPC2<12:10> | IPC2<9:8>    | Yes       |

| IC2 – Input Capture 2               | 11    | 9      | IFS0<11>     | IEC0<11>     | IPC2<12:10> | IPC2<9:8>    | Yes       |

| OC2 – Output Compare 2              | 12    | 10     | IFS0<12>     | IEC0<12>     | IPC2<20:18> | IPC2<17:16>  | No        |

| INT2 – External Interrupt 2         | 13    | 11     | IFS0<13>     | IEC0<13>     | IPC2<28:26> | IPC2<25:24>  | No        |

| T3 – Timer3                         | 14    | 12     | IFS0<14>     | IEC0<14>     | IPC3<4:2>   | IPC3<1:0>    | No        |

| IC3E – Input Capture 3              | 15    | 13     | IFS0<15>     | IEC0<15>     | IPC3<12:10> | IPC3<9:8>    | Yes       |

| IC3 – Input Capture 3               | 16    | 13     | IFS0<16>     | IEC0<16>     | IPC3<12:10> | IPC3<9:8>    | Yes       |

| OC3 – Output Compare 3              | 17    | 14     | IFS0<17>     | IEC0<17>     | IPC3<20:18> | IPC3<17:16>  | No        |

| INT3 – External Interrupt 3         | 18    | 15     | IFS0<18>     | IEC0<18>     | IPC3<28:26> | IPC3<25:24>  | No        |

| T4 – Timer4                         | 19    | 16     | IFS0<19>     | IEC0<19>     | IPC4<4:2>   | IPC4<1:0>    | No        |

| IC4E – Input Capture 4 Error        | 20    | 17     | IFS0<20>     | IEC0<20>     | IPC4<12:10> | IPC4<9:8>    | Yes       |

| IC4 – Input Capture 4               | 21    | 17     | IFS0<21>     | IEC0<21>     | IPC4<12:10> | IPC4<9:8>    | Yes       |

| OC4 – Output Compare 4              | 22    | 18     | IFS0<22>     | IEC0<22>     | IPC4<20:18> | IPC4<17:16>  | No        |

| INT4 – External Interrupt 4         | 23    | 19     | IFS0<23>     | IEC0<23>     | IPC4<28:26> | IPC4<25:24>  | No        |

| T5 – Timer5                         | 24    | 20     | IFS0<24>     | IEC0<24>     | IPC5<4:2>   | IPC5<1:0>    | No        |

| IC5E – Input Capture 5 Error        | 25    | 21     | IFS0<25>     | IEC0<25>     | IPC5<12:10> | IPC5<9:8>    | Yes       |

| IC5 – Input Capture 5               | 26    | 21     | IFS0<26>     | IEC0<26>     | IPC5<12:10> | IPC5<9:8>    | Yes       |

| OC5 – Output Compare 5              | 27    | 22     | IFS0<27>     | IEC0<27>     | IPC5<20:18> | IPC5<17:16>  | No        |

| AD1 – ADC1 Convert done             | 28    | 23     | IFS0<28>     | IEC0<28>     | IPC5<28:26> | IPC5<25:24>  | Yes       |

| FSCM – Fail-Safe Clock Monitor      | 29    | 24     | IFS0<29>     | IEC0<29>     | IPC6<4:2>   | IPC6<1:0>    | No        |

| RTCC – Real-Time Clock and Calendar | 30    | 25     | IFS0<30>     | IEC0<30>     | IPC6<12:10> | IPC6<9:8>    | No        |

| FCE – Flash Control Event           | 31    | 26     | IFS0<31>     | IEC0<31>     | IPC6<20:18> | IPC6<17:16>  | No        |

| CMP1 – Comparator Interrupt         | 32    | 27     | IFS1<0>      | IEC1<0>      | IPC6<28:26> | IPC6<25:24>  | No        |

| CMP2 – Comparator Interrupt         | 33    | 28     | IFS1<1>      | IEC1<1>      | IPC7<4:2>   | IPC7<1:0>    | No        |

| USB – USB Interrupts                | 34    | 29     | IFS1<2>      | IEC1<2>      | IPC7<12:10> | IPC7<9:8>    | Yes       |

| SPI1E – SPI1 Fault                  | 35    | 30     | IFS1<3>      | IEC1<3>      | IPC7<20:18> | IPC7<17:16>  | Yes       |

| SPI1RX – SPI1 Receive Done          | 36    | 30     | IFS1<4>      | IEC1<4>      | IPC7<20:18> | IPC7<17:16>  | Yes       |

| SPI1TX – SPI1 Transfer Done         | 37    | 30     | IFS1<5>      | IEC1<5>      | IPC7<20:18> | IPC7<17:16>  | Yes       |

| U1E – UART1 Fault                   | 38    | 31     | IFS1<6>      | IEC1<6>      | IPC7<28:26> | IPC7<25:24>  | Yes       |

| U1RX – UART1 Receive Done           | 39    | 31     | IFS1<7>      | IEC1<7>      | IPC7<28:26> | IPC7<25:24>  | Yes       |

| U1TX – UART1 Transfer Done          | 40    | 31     | IFS1<8>      | IEC1<8>      | IPC7<28:26> | IPC7<25:24>  | Yes       |

| I2C1B – I2C1 Bus Collision Event    | 41    | 32     | IFS1<9>      | IEC1<9>      | IPC8<4:2>   | IPC8<1:0>    | Yes       |

| I2C1S – I2C1 Slave Event            | 42    | 32     | IFS1<10>     | IEC1<10>     | IPC8<4:2>   | IPC8<1:0>    | Yes       |

| I2C1M – I2C1 Master Event           | 43    | 32     | IFS1<11>     | IEC1<11>     | IPC8<4:2>   | IPC8<1:0>    | Yes       |

| CNA – PORTA Input Change Interrupt  | 44    | 33     | IFS1<12>     | IEC1<12>     | IPC8<12:10> | IPC8<9:8>    | Yes       |

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX330/350/370/430/450/470 Controller Family Features" for the list of available peripherals.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 |       |       | Bit<br>26/18/10/2             | Bit<br>25/17/9/1          | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------|-------|-------------------------------|---------------------------|------------------|--|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0   | U-0   | U-0                           | U-0                       | U-0              |  |  |  |

| 31:24        | _                 | —                 | —                 | —     | —     | —                             | —                         | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0   | U-0   | U-0                           | U-0                       | U-0              |  |  |  |

| 23:16        | —                 | —                 | —                 | —     | —     | —                             | —                         | —                |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0   | U-0   | R/W-0                         | R/W-0                     | R/W-0            |  |  |  |

| 15:8         | _                 | —                 | _                 | —     | —     | S                             | SRIPL<2:0> <sup>(1)</sup> |                  |  |  |  |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0 | R/W-0 | R/W-0<br><5:0> <sup>(1)</sup> | R/W-0                     | R/W-0            |  |  |  |

| 7:0          | _                 | —                 |                   |       |       |                               |                           |                  |  |  |  |

#### REGISTER 7-2: INTSTAT: INTERRUPT STATUS REGISTER

## Legend:

| Logonan           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-11 Unimplemented: Read as '0'

- bit 10-8 **SRIPL<2:0>:** Requested Priority Level bits<sup>(1)</sup> 111-000 = The priority level of the latest interrupt presented to the CPU

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 VEC<5:0>: Interrupt Vector bits<sup>(1)</sup> 11111-00000 = The interrupt vector that is presented to the CPU

- Note 1: This value should only be used when the interrupt controller is configured for Single Vector mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31:24        | IPTMR<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16        | IPTMR<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         | IPTMR<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                   |                   |                   | IPTM              | R<7:0>            |                   |                  |                  |  |  |  |  |  |

#### REGISTER 7-3: IPTMR: INTERRUPT PROXIMITY TIMER REGISTER

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 **IPTMR<31:0>:** Interrupt Proximity Timer Reload bits Used by the Interrupt Proximity Timer as a reload value when the Interrupt Proximity timer is triggered by an interrupt event.

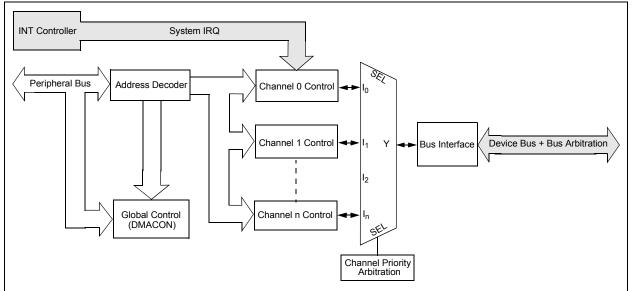

## 10.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 31. "Direct Memory Access (DMA) Controller" (DS60001117), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32 Direct Memory Access (DMA) controller is a bus master module useful for data transfers between different devices without CPU intervention. The source and destination of a DMA transfer can be any of the memory mapped modules existent in the PIC32 (such as Peripheral Bus (PBUS) devices: SPI, UART, PMP, etc.) or memory itself.

Following are some of the key features of the DMA controller module:

- Four identical channels, each featuring:

- Auto-increment source and destination address registers

- Source and destination pointers

- Memory to memory and memory to peripheral transfers

- Automatic word-size detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source and destination

- Fixed priority channel arbitration

- · Flexible DMA channel operating modes:

- Manual (software) or automatic (interrupt) DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- · Flexible DMA requests:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any (appropriate) observable interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Pattern (data) match transfer termination

- · Multiple DMA channel status interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- DMA debug support features:

- Most recent address accessed by a DMA channel

- Most recent DMA channel to transfer data

- · CRC Generation module:

- CRC module can be assigned to any of the available channels

- CRC module is highly configurable

## FIGURE 10-1: DMA BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | -                 | —                 | _                 | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | —                 | -                 | -                 | —                 | _                 | _                | —                |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         |                   | —                 | _                 | _                 | —                 |                   | _                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHPDAT            | 7:0>              |                   |                  |                  |

## REGISTER 10-18: DCHxDAT: DMA CHANNEL 'x' PATTERN DATA REGISTER

## Legend:

| =0901141          |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

#### bit 7-0 **CHPDAT<7:0>:** Channel Data Register bits

Pattern Terminate mode: Data to be matched must be stored in this register to allow terminate on match.

All other modes: Unused. NOTES:

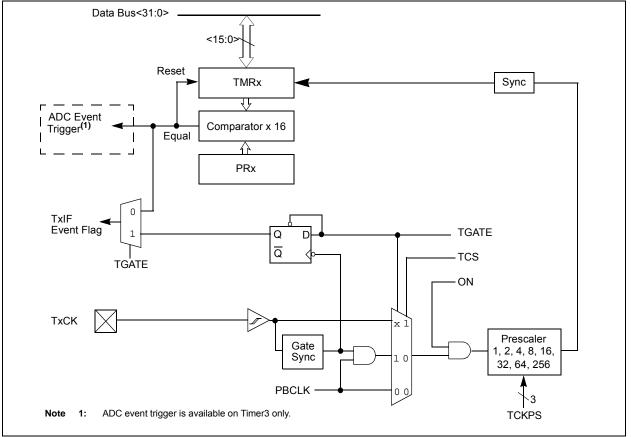

## 14.0 TIMER2/3, TIMER4/5

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32MX330/350/370/430/450/470 family of devices features four synchronous 16-bit timers (default) that can operate as a free-running interval timer for various timing applications and counting external events. The following modes are supported:

- Synchronous internal 16-bit timer

- Synchronous internal 16-bit gated timer

- · Synchronous external 16-bit timer

Two 32-bit synchronous timers are available by combining Timer2 with Timer3 and Timer4 with Timer5. The 32-bit timers can operate in three modes:

- · Synchronous internal 32-bit timer

- · Synchronous internal 32-bit gated timer

- · Synchronous external 32-bit timer

- Note: In this chapter, references to registers, TxCON, TMRx and PRx, use 'x' to represent Timer2 through 5 in 16-bit modes. In 32-bit modes, 'x' represents Timer2 or 4; 'y' represents Timer3 or 5.

## 14.1 Additional Supported Features

- Selectable clock prescaler

- Timers operational during CPU idle

- Time base for Input Capture and Output Compare modules (Timer2 and Timer3 only)

- ADC event trigger (Timer3 in 16-bit mode, Timer2/ 3 in 32-bit mode)

- Fast bit manipulation using CLR, SET, and INV registers

## FIGURE 14-1: TIMER2, 3, 4, 5 BLOCK DIAGRAM (16-BIT)

#### REGISTER 16-1: ICXCON: INPUT CAPTURE 'X' CONTROL REGISTER (CONTINUED)

- bit 2-0 ICM<2:0>: Input Capture Mode Select bits

- 111 = Interrupt-Only mode (only supported while in Sleep mode or Idle mode)

- 110 = Simple Capture Event mode every edge, specified edge first and every edge thereafter

- 101 = Prescaled Capture Event mode every sixteenth rising edge

- 100 = Prescaled Capture Event mode every fourth rising edge

- 011 = Simple Capture Event mode every rising edge

- 010 = Simple Capture Event mode every falling edge

- 001 = Edge Detect mode every edge (rising and falling)

- 000 = Input Capture module is disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### 17.1 **Control Registers**

## TABLE 17-1: OUTPUT COMPARE 1 THROUGH OUTPUT COMPARE 5 REGISTER MAP

| ess                         |                                 |               |       |       |       |       |       |       |      | Bi     | ts       |      |      |       |        |      |            |      |              |

|-----------------------------|---------------------------------|---------------|-------|-------|-------|-------|-------|-------|------|--------|----------|------|------|-------|--------|------|------------|------|--------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8   | 23/7     | 22/6 | 21/5 | 20/4  | 19/3   | 18/2 | 17/1       | 16/0 | All Resets   |

|                             | OC1CON                          | 31:16         | _     | —     | —     | _     | _     | —     | —    | _      | _        | _    | —    | —     | _      |      | —          |      | 0000         |

| 3000                        |                                 | 15:0          | ON    | —     | SIDL  | _     | _     | —     | —    | _      | -        |      | OC32 | OCFLT | OCTSEL |      | OCM<2:0>   |      | 0000         |

| 3010                        | OC1R                            | 31:16         |       |       |       |       |       |       |      | OC1R   | <31.0>   |      |      |       |        |      |            |      | xxxx         |

| 0010                        | oom                             | 15:0          |       |       |       |       |       |       |      | 00111  | -011.0-  |      |      |       |        |      |            |      | xxxx         |

| 3020                        | OC1RS                           | 31:16         |       |       |       |       |       |       |      | OC1RS  | 6<31:0>  |      |      |       |        |      |            |      | XXXX         |

|                             |                                 | 15:0          |       |       |       |       |       |       |      |        |          |      |      |       |        |      | -          |      | XXXX         |

| 3200                        | OC2CON                          | 31:16         |       |       | -     | _     | _     |       |      | _      |          |      | —    | —<br> |        |      | -          | —    | 0000         |

|                             |                                 | 15:0<br>31:16 | ON    | —     | SIDL  |       |       |       |      |        | —        | —    | OC32 | OCFLT | OCTSEL |      | OCM<2:0>   |      | 0000         |

| 3210                        | OC2R                            | 15:0          |       |       |       |       |       |       |      | OC2R   | <31:0>   |      |      |       |        |      |            |      | xxxx<br>xxxx |

|                             |                                 | 31.16         |       |       |       |       |       |       |      |        |          |      |      |       |        |      |            |      | XXXX         |

| 3220                        | OC2RS                           | 15:0          |       |       |       |       |       |       |      | OC2RS  | \$<31:0> |      |      |       |        |      |            |      | xxxx         |

|                             |                                 | 31.16         | _     |       | _     |       | _     | _     | _    |        | _        | _    | _    | _     |        | _    | _          | _    | 0000         |

| 3400                        | OC3CON                          | 15:0          | ON    | _     | SIDL  | _     | _     | _     | _    | _      | _        | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0>   |      | 0000         |

| 0440                        | 0000                            | 31:16         |       |       |       |       |       |       |      | 0000   | -04-05   |      |      | •     |        |      |            |      | xxxx         |

| 3410                        | OC3R                            | 15:0          |       |       |       |       |       |       |      | OC3R   | <31.0>   |      |      |       |        |      |            |      | xxxx         |

| 3420                        | OC3RS                           | 31:16         |       |       |       |       |       |       |      | OC3RS  | <31·0>   |      |      |       |        |      |            |      | xxxx         |

| 0420                        | 000110                          | 15:0          |       |       |       |       |       |       |      | 000110 | -01.04   |      |      |       |        |      |            |      | xxxx         |

| 3600                        | OC4CON                          | 31:16         |       | _     | —     | _     | —     | —     | —    | _      | _        | _    | —    | —     | —      | _    | —          | —    | 0000         |

|                             |                                 | 15:0          | ON    | —     | SIDL  | —     | —     | —     | —    | —      | —        | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0>   |      | 0000         |

| 3610                        | OC4R                            | 31:16         | -     |       |       |       |       |       |      | OC4R   | <31:0>   |      |      |       |        |      |            |      | XXXX         |

|                             |                                 | 15:0          |       |       |       |       |       |       |      |        |          |      |      |       |        |      |            |      | XXXX         |

| 3620                        | OC4RS                           | 31:16<br>15:0 |       |       |       |       |       |       |      | OC4RS  | \$<31:0> |      |      |       |        |      |            |      | xxxx         |

|                             |                                 | 31:16         |       |       | _     |       | _     | _     | _    |        | _        | _    | _    |       |        | _    | _          |      | xxxx<br>0000 |

| 3800                        | OC5CON                          | 15:0          | ON    |       | SIDL  |       |       |       |      |        | _        |      | OC32 | OCFLT | OCTSEL |      | OCM<2:0>   |      | 0000         |

|                             |                                 | 31:16         |       |       | OIDE  |       |       |       |      |        |          |      | 0002 | OOLEI | OUTOLL |      | 00111-2.04 |      | xxxx         |

| 3810                        | OC5R                            | 15:0          |       |       |       |       |       |       |      | OC5R   | <31:0>   |      |      |       |        |      |            |      | xxxx         |

|                             | 0.0555                          | 31.16         |       |       |       |       |       |       |      | 0.05-0 |          |      |      |       |        |      |            |      | xxxx         |

| 3820                        | OC5RS                           | 15:0          | 1     |       |       |       |       |       |      | OC5RS  | s<31:0>  |      |      |       |        |      |            |      | xxxx         |

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information. Note 1:

| REGISTE | R 19-1: I2CxCON: I <sup>2</sup> C CONTROL REGISTER (CONTINUED)                                                                                                                                                                                                                                                                                            |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7   | <ul> <li>GCEN: General Call Enable bit (when operating as I<sup>2</sup>C slave)</li> <li>1 = Enable interrupt when a general call address is received in the I2CxRSR (module is enabled for reception)</li> <li>0 = General call address disabled</li> </ul>                                                                                              |

| bit 6   | <b>STREN:</b> SCLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)<br>Used in conjunction with SCLREL bit.<br>1 = Enable software or receive clock stretching<br>0 = Disable software or receive clock stretching                                                                                                                     |

| bit 5   | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)<br>Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Send NACK during Acknowledge<br>0 = Send ACK during Acknowledge                                                                                        |

| bit 4   | <ul> <li>ACKEN: Acknowledge Sequence Enable bit</li> <li>(when operating as I<sup>2</sup>C master, applicable during master receive)</li> <li>1 = Initiate Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit.<br/>Hardware clear at end of master Acknowledge sequence.</li> <li>0 = Acknowledge sequence not in progress</li> </ul> |

| bit 3   | <ul> <li>RCEN: Receive Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Enables Receive mode for I<sup>2</sup>C. Hardware clear at end of eighth bit of master receive data byte.</li> <li>0 = Receive sequence not in progress</li> </ul>                                                                                               |

| bit 2   | <ul> <li>PEN: Stop Condition Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Initiate Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence.</li> <li>0 = Stop condition not in progress</li> </ul>                                                                                                       |

| bit 1   | <ul> <li>RSEN: Repeated Start Condition Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Initiate Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of master Repeated Start sequence.</li> <li>0 = Repeated Start condition not in progress</li> </ul>                                                              |

| bit 0   | <ul> <li>Start Condition Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Initiate Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence.</li> <li>0 = Start condition not in progress</li> </ul>                                                                                                        |

**Note 1:** When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

## REGISTER 19-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER (CONTINUED)

| <ul> <li>1 = Indicates that a Stop bit has been detected last</li> <li>0 = Stop bit was not detected last<br/>Hardware set or clear when Start, Repeated Start or Stop detected.</li> <li>5: Start bit</li> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last<br/>Hardware set or clear when Start, Repeated Start or Stop detected.</li> <li>8: Read/Write Information bit (when operating as I<sup>2</sup>C slave)</li> <li>1 = Read – indicates data transfer is output from slave</li> <li>0 = Write – indicates data transfer is input to slave<br/>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> <li>1 RBF: Receive Buffer Full Status bit</li> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty<br/>Hardware set when I2CxRCV is written with received byte. Hardware clear when software<br/>reads I2CxRCV.</li> <li>0 TBF: Transmit Buffer Full Status bit</li> <li>1 = Transmit in progress I2CxTRN is full</li> </ul> | bit 4 | P: Stop bit                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------|

| <ul> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> <li>bit 3 S: Start bit <ol> <li>= Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>= Start bit was not detected last</li> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> </ol> </li> <li>bit 2 R_W: Read/Write Information bit (when operating as I<sup>2</sup>C slave) <ol> <li>= Read – indicates data transfer is output from slave</li> <li>Write – indicates data transfer is input to slave</li> <li>Write – indicates data transfer is of I<sup>2</sup>C device address byte.</li> </ol> </li> <li>bit 1 RBF: Receive Buffer Full Status bit <ol> <li>= Receive not complete, I2CxRCV is full</li> <li>= Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> </ol> </li> <li>bit 0 TBF: Transmit Buffer Full Status bit</li> </ul>                                                                                                |       | 1 = Indicates that a Stop bit has been detected last                              |

| bit 3       S: Start bit         1 = Indicates that a Start (or Repeated Start) bit has been detected last         0 = Start bit was not detected last         Hardware set or clear when Start, Repeated Start or Stop detected.         bit 2       R_W: Read/Write Information bit (when operating as I <sup>2</sup> C slave)         1 = Read – indicates data transfer is output from slave         0 = Write – indicates data transfer is input to slave         Hardware set or clear after reception of I <sup>2</sup> C device address byte.         bit 1       RBF: Receive Buffer Full Status bit         1 = Receive complete, I2CxRCV is full       0 = Receive not complete, I2CxRCV is empty         Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.         bit 0       TBF: Transmit Buffer Full Status bit                                                                                                                                                                                                         |       |                                                                                   |

| <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last<br/>Hardware set or clear when Start, Repeated Start or Stop detected.</li> <li>bit 2 R_W: Read/Write Information bit (when operating as I<sup>2</sup>C slave)</li> <li>1 = Read – indicates data transfer is output from slave</li> <li>0 = Write – indicates data transfer is input to slave<br/>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> <li>bit 1 RBF: Receive Buffer Full Status bit</li> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty<br/>Hardware set when I2CxRCV is written with received byte. Hardware clear when software<br/>reads I2CxRCV.</li> <li>bit 0 TBF: Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                                                          |       | Hardware set or clear when Start, Repeated Start or Stop detected.                |

| <ul> <li>0 = Start bit was not detected last<br/>Hardware set or clear when Start, Repeated Start or Stop detected.</li> <li>bit 2 R_W: Read/Write Information bit (when operating as I<sup>2</sup>C slave)         <ol> <li>1 = Read – indicates data transfer is output from slave</li> <li>0 = Write – indicates data transfer is input to slave</li> <li>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> </ol> </li> <li>bit 1 RBF: Receive Buffer Full Status bit         <ol> <li>= Receive complete, I2CxRCV is full</li> <li>= Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> </ol> </li> <li>bit 0 TBF: Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                                                                                                   | bit 3 | S: Start bit                                                                      |

| bit 2 <b>R_W:</b> Read/Write Information bit (when operating as I²C slave)1 = Read – indicates data transfer is output from slave0 = Write – indicates data transfer is input to slaveHardware set or clear after reception of I²C device address byte.bit 1 <b>RBF:</b> Receive Buffer Full Status bit1 = Receive complete, I2CxRCV is full0 = Receive not complete, I2CxRCV is emptyHardware set when I2CxRCV is written with received byte. Hardware clear when softwarebit 0 <b>TBF:</b> Transmit Buffer Full Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |       |                                                                                   |

| <ul> <li>1 = Read – indicates data transfer is output from slave</li> <li>0 = Write – indicates data transfer is input to slave</li> <li>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> <li>bit 1 RBF: Receive Buffer Full Status bit</li> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> <li>bit 0 TBF: Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       | Hardware set or clear when Start, Repeated Start or Stop detected.                |

| <ul> <li>0 = Write – indicates data transfer is input to slave<br/>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> <li>bit 1 <b>RBF:</b> Receive Buffer Full Status bit</li> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty<br/>Hardware set when I2CxRCV is written with received byte. Hardware clear when software<br/>reads I2CxRCV.</li> <li>bit 0 <b>TBF:</b> Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave) |

| <ul> <li>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> <li>bit 1 <b>RBF:</b> Receive Buffer Full Status bit</li> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> <li>bit 0 <b>TBF:</b> Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       | 1 = Read – indicates data transfer is output from slave                           |

| bit 1 <b>RBF:</b> Receive Buffer Full Status bit         1 = Receive complete, I2CxRCV is full         0 = Receive not complete, I2CxRCV is empty         Hardware set when I2CxRCV is written with received byte. Hardware clear when software         reads I2CxRCV.         bit 0 <b>TBF:</b> Transmit Buffer Full Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |       |                                                                                   |

| <ul> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> <li>bit 0 TBF: Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       | Hardware set or clear after reception of I <sup>2</sup> C device address byte.    |

| <ul> <li>0 = Receive not complete, I2CxRCV is empty<br/>Hardware set when I2CxRCV is written with received byte. Hardware clear when software<br/>reads I2CxRCV.</li> <li>bit 0 TBF: Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 1 | RBF: Receive Buffer Full Status bit                                               |

| Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.         bit 0 <b>TBF:</b> Transmit Buffer Full Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       | 1 = Receive complete, I2CxRCV is full                                             |

| reads I2CxRCV.<br>bit 0 <b>TBF:</b> Transmit Buffer Full Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       | 0 = Receive not complete, I2CxRCV is empty                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       |                                                                                   |

| 1 = Transmit in progress_I2CxTRN is full                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 0 | TBF: Transmit Buffer Full Status bit                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       | 1 = Transmit in progress, I2CxTRN is full                                         |

| 0 = Transmit complete, I2CxTRN is empty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       | 0 = Transmit complete, I2CxTRN is empty                                           |

Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.

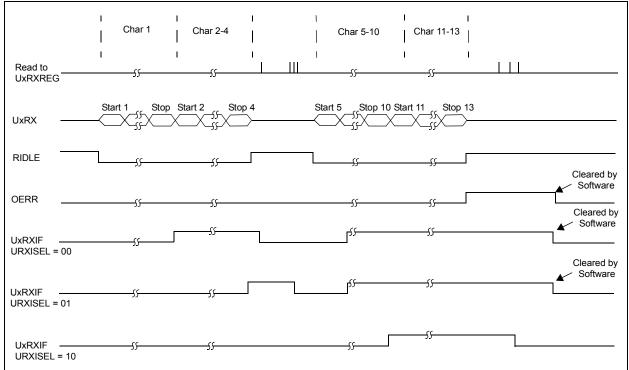

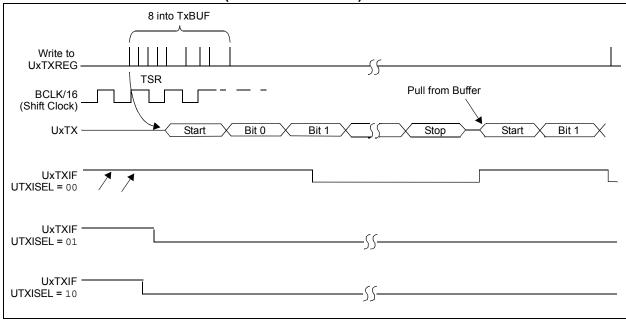

## 20.2 Timing Diagrams

Figure 20-2 and Figure 20-3 illustrate typical receive and transmit timing for the UART module.

## FIGURE 20-2: UART RECEPTION

#### FIGURE 20-3: TRANSMISSION (8-BIT OR 9-BIT DATA)

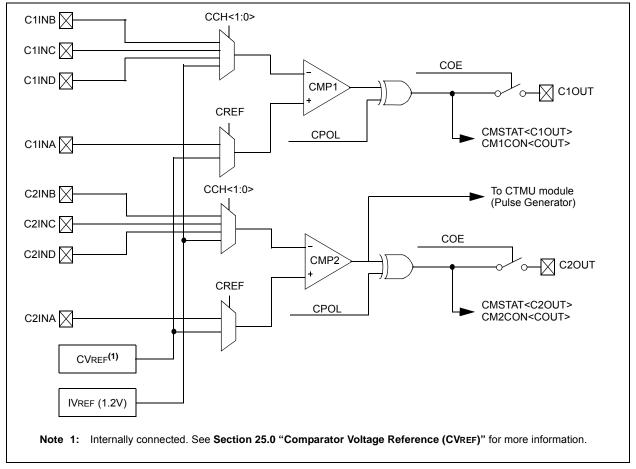

## 24.0 COMPARATOR

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer Section 19. to "Comparator" (DS60001110), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Analog Comparator module contains two comparators that can be configured in a variety of ways.

The following are key features of this module:

- · Selectable inputs available include:

- Analog inputs multiplexed with I/O pins

- On-chip internal absolute voltage reference (IVREF)

- Comparator voltage reference (CVREF)

- · Outputs can be Inverted

- Selectable interrupt generation

A block diagram of the comparator module is provided in Figure 24-1.

#### FIGURE 24-1: COMPARATOR BLOCK DIAGRAM

## TABLE 31-15: COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

| DC CHARACTERISTICS |        |                                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^\circ C \leq TA \leq +70^\circ C \mbox{ for Commercial} \\ -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-temp} \end{array}$ |   |                    |          |                                                                  |  |

|--------------------|--------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------------|----------|------------------------------------------------------------------|--|

| Param.<br>No.      | Symbol | Characteristics                                              | Min. Typ. Max.                                                                                                                                                                                                                                                                                                                               |   | Units              | Comments |                                                                  |  |

| D312               | TSET   | Internal 4-bit DAC<br>Comparator Reference<br>Settling time. | _                                                                                                                                                                                                                                                                                                                                            |   | 10                 | μs       | See Note 1                                                       |  |

| D313 DACREFH       |        | CVREF Input Voltage<br>Reference Range                       | AVss                                                                                                                                                                                                                                                                                                                                         |   | AVDD               | V        | CVRSRC with CVRSS = 0                                            |  |

|                    |        |                                                              | VREF-                                                                                                                                                                                                                                                                                                                                        |   | VREF+              | V        | CVRSRC with CVRSS = 1                                            |  |

| D314               | DVREF  | CVREF Programmable<br>Output Range                           | 0                                                                                                                                                                                                                                                                                                                                            | _ | 0.625 x<br>DACREFH | V        | 0 to 0.625 DACREFH with<br>DACREFH/24 step size                  |  |

|                    |        |                                                              | 0.25 x<br>DACREFH                                                                                                                                                                                                                                                                                                                            | — | 0.719 x<br>DACREFH | V        | 0.25 x DACREFH to 0.719<br>DACREFH with DACREFH/<br>32 step size |  |

| D315               | DACRES | Resolution                                                   | _                                                                                                                                                                                                                                                                                                                                            | _ | DACREFH/24         |          | CVRCON <cvrr> = 1</cvrr>                                         |  |

|                    |        |                                                              | —                                                                                                                                                                                                                                                                                                                                            |   | DACREFH/32         |          | CVRCON <cvrr> = 0</cvrr>                                         |  |

| D316               | DACACC | Absolute Accuracy <sup>(2)</sup>                             | —                                                                                                                                                                                                                                                                                                                                            | _ | 1/4                | LSB      | DACREFH/24,<br>CVRCON <cvrr> = 1</cvrr>                          |  |

|                    |        |                                                              | _                                                                                                                                                                                                                                                                                                                                            |   | 1/2                | LSB      | DACREFH/32,<br>CVRCON <cvrr> = 0</cvrr>                          |  |

**Note 1:** Settling time was measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but is not tested in manufacturing.

2: These parameters are characterized but not tested.

#### TABLE 31-16: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| DC CHARACTERISTICS |        |                                 | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                   |  |       |                                                                                                    |  |

|--------------------|--------|---------------------------------|------------------------------------------------------|-------------------|--|-------|----------------------------------------------------------------------------------------------------|--|

| Param.<br>No.      | Symbol | Characteristics                 | Min.                                                 | Min. Typical Max. |  | Units | Comments                                                                                           |  |

| D321               | Cefc   | External Filter Capacitor Value | 8                                                    | 10                |  | μF    | Capacitor must be low series<br>resistance (3 ohm). Typical<br>voltage on the VCAP pin is<br>1.8V. |  |

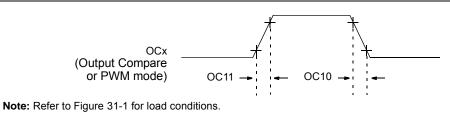

## TABLE 31-27: OUTPUT COMPARE MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                        |      |       |                    |

|--------------------|--------|--------------------------------|------------------------------------------------------|------------------------|------|-------|--------------------|

| Param.<br>No.      | Symbol | Characteristics <sup>(1)</sup> | Min.                                                 | Typical <sup>(2)</sup> | Max. | Units | Conditions         |

| OC10               | TccF   | OCx Output Fall Time           | —                                                    | —                      | _    | ns    | See parameter DO32 |

| OC11               | TccR   | OCx Output Rise Time           | —                                                    | —                      | _    | ns    | See parameter DO31 |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

## FIGURE 31-9: OCx/PWM MODULE TIMING CHARACTERISTICS

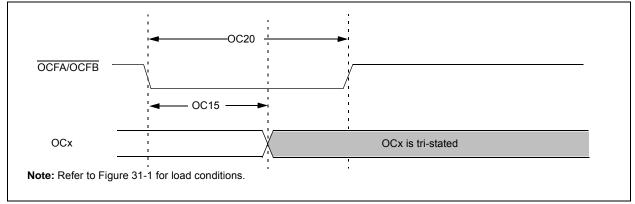

## TABLE 31-28: SIMPLE OCx/PWM MODE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |                        |     |       |            |

|--------------------|--------|------------------------------------------------------|-----|------------------------|-----|-------|------------|

| Param<br>No.       | Symbol | Characteristics <sup>(1)</sup>                       | Min | Typical <sup>(2)</sup> | Max | Units | Conditions |

| OC15               | Tfd    | Fault Input to PWM I/O Change                        | —   | —                      | 50  | ns    | _          |

| OC20               | TFLT   | Fault Input Pulse Width                              | 50  | —                      | _   | ns    | —          |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

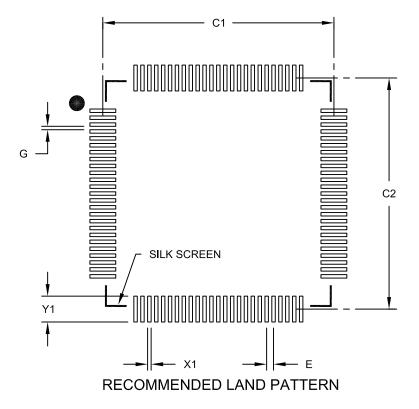

# PIC32MX330/350/370/430/450/470

100-Lead Plastic Thin Quad Flatpack (PT)-12x12x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | MILLIMETERS |      |       |      |

|---------------------------|-------------|------|-------|------|

| Dimensior                 | MIN         | NOM  | MAX   |      |

| Contact Pitch             | 0.40 BSC    |      |       |      |

| Contact Pad Spacing       |             |      | 13.40 |      |

| Contact Pad Spacing       | C2          |      | 13.40 |      |

| Contact Pad Width (X100)  | X1          |      |       | 0.20 |

| Contact Pad Length (X100) | Y1          |      |       | 1.50 |

| Distance Between Pads     | G           | 0.20 |       |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2100B

# PIC32MX330/350/370/430/450/470

NOTES: