Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-VQFN (9x9)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx350f128h-i-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

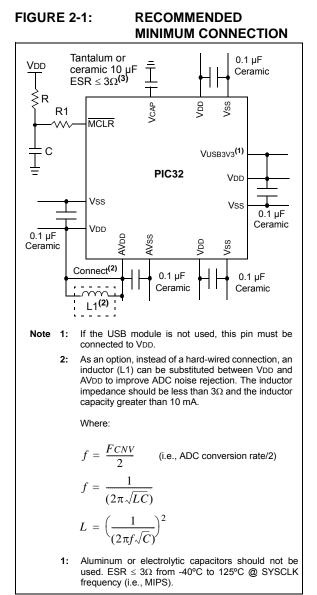

### 2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve power supply stability. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ . This capacitor should be located as close to the device as possible.

# 2.3 Capacitor on Internal Voltage Regulator (VCAP)

### 2.3.1 INTERNAL REGULATOR MODE

A low-ESR (3 ohm) capacitor is required on the VCAP pin, which is used to stabilize the internal voltage regulator output. The VCAP pin must not be connected to VDD, and must have a CEFC capacitor, with at least a 6V rating, connected to ground. The type can be ceramic or tantalum. Refer to **Section 31.0 "Electrical Characteristics"** for additional information on CEFC specifications.

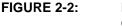

# 2.4 Master Clear (MCLR) Pin

The  $\overline{\text{MCLR}}$  pin provides two specific device functions:

- Device Reset

- · Device programming and debugging

Pulling The  $\overline{\text{MCLR}}$  pin low generates a device Reset. Figure 2-2 illustrates a typical  $\overline{\text{MCLR}}$  circuit. During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as illustrated in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components illustrated in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

3:

### EXAMPLE OF MCLR PIN CONNECTIONS

No pull-ups or bypass capacitors are allowed on

active debug/program PGECx/PGEDx pins.

# 3.2 Architecture Overview

The MIPS32<sup>®</sup> M4K<sup>®</sup> processor core contains several logic blocks working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- Execution Unit

- Multiply/Divide Unit (MDU)

- System Control Coprocessor (CP0)

- Fixed Mapping Translation (FMT)

- Dual Internal Bus interfaces

- Power Management

- MIPS16e<sup>®</sup> Support

- Enhanced JTAG (EJTAG) Controller

### 3.2.1 EXECUTION UNIT

The MIPS32<sup>®</sup> M4K<sup>®</sup> processor core execution unit implements a load/store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation. One additional register file shadow set (containing thirty-two registers) is added to minimize context switching overhead during interrupt/exception processing. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction

address

- Logic for branch determination and branch target address calculation

- · Load aligner

- Bypass multiplexers used to avoid stalls when executing instruction streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing bitwise logical operations

- Shifter and store aligner

# 3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

The MIPS32<sup>®</sup> M4K<sup>®</sup> processor core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows MDU operations to be partially masked by system stalls and/or other integer unit instructions.

The high-performance MDU consists of a 32x16 booth recoded multiplier, result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x16) represents the *rs* operand. The second number ('16' of 32x16) represents the *rt* operand. The PIC32 core only checks the value of the latter (*rt*) operand to determine how many times the operation must pass through the multiplier. The 16x16 and 32x16 operations pass through the multiplier once. A 32x32 operation passes through the multiplier twice.

The MDU supports execution of one 16x16 or 32x16 multiply operation every clock cycle; 32x32 multiply operations can be issued every other clock cycle. Appropriate interlocks are implemented to stall the issuance of back-to-back 32x32 multiply operations. The multiply operand size is automatically determined by logic built into the MDU.

Divide operations are implemented with a simple 1 bit per clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If *rs* is 8 bits wide, 23 iterations are skipped. For a 16-bit wide *rs*, 15 iterations are skipped and for a 24-bit wide *rs*, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation is completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the PIC32 core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

|                         | ATENCIES AND REPEAT RATES                      |         |             |

|-------------------------|------------------------------------------------|---------|-------------|

| Op code                 | Operand Size (mul <i>rt</i> ) (div <i>rs</i> ) | Latency | Repeat Rate |

| MULT/MULTU, MADD/MADDU, | 16 bits                                        | 1       | 1           |

| MSUB/MSUBU              | 32 bits                                        | 2       | 2           |

| MUL                     | 16 bits                                        | 2       | 1           |

|                         | 32 bits                                        | 3       | 2           |

| DIV/DIVU                | 8 bits                                         | 12      | 11          |

|                         | 16 bits                                        | 19      | 18          |

|                         | 24 bits                                        | 26      | 25          |

|                         | 32 bits                                        | 33      | 32          |

# TABLE 3-1: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE HIGH-PERFORMANCE INTEGER MULTIPLY/ DIVIDE UNIT LATENCIES AND REPEAT RATES

# 4.2 Bus Matrix Registers

### TABLE 4-2: BUS MATRIX REGISTER MAP

| ress                        | 2                       | e         |       |                               |       |       |       |           |      |      |      | Bits          |      |           |           |           |          |          |               |

|-----------------------------|-------------------------|-----------|-------|-------------------------------|-------|-------|-------|-----------|------|------|------|---------------|------|-----------|-----------|-----------|----------|----------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name        | Bit Range | 31/15 | 30/14                         | 29/13 | 28/12 | 27/11 | 26/10     | 25/9 | 24/8 | 23/7 | 22/6          | 21/5 | 20/4      | 19/3      | 18/2      | 17/1     | 16/0     | All<br>Resets |

| 2000                        | BMXCON <sup>(1)</sup>   | 31:16     | —     |                               |       |       |       | BMXCHEDMA |      |      | —    | —             |      | BMXERRIXI | BMXERRICD | BMXERRDMA | BMXERRDS | BMXERRIS | 041F          |

| 2000                        | BIVIACON                | 15:0      | _     | <u> BMXARB&lt;2:0&gt;</u> 004 |       |       |       |           |      |      |      |               |      |           | 0047      |           |          |          |               |

| 2010                        | BMXDKPBA <sup>(1)</sup> | 31:16     | _     |                               |       |       |       |           |      |      |      |               |      |           |           | 0000      |          |          |               |

| 2010                        | DIVIADIAL DA            | 15:0      |       |                               |       |       |       |           |      |      |      |               |      |           |           |           | 0000     |          |               |

| 2020                        | BMXDUDBA <sup>(1)</sup> | 31:16     | —     |                               |       |       |       |           |      |      |      |               |      |           | 0000      |           |          |          |               |

| 2020                        |                         | 15:0      |       | BMXDUDBA<15:0> 000            |       |       |       |           |      |      |      |               |      |           |           |           |          | 0000     |               |

| 2030                        | BMXDUPBA <sup>(1)</sup> | 31:16     | _     | _                             | —     | —     | —     | —         | _    | —    | _    | _             | _    | —         | —         | —         |          | —        | 0000          |

| 2000                        | 5                       | 15:0      |       |                               |       |       |       |           |      |      | BM   | XDUPBA<15:0>  | •    |           |           |           |          |          | 0000          |

| 2040                        | BMXDRMSZ                | 31:16     |       |                               |       |       |       |           |      |      | BM   | XDRMSZ<31:0>  |      |           |           |           |          |          | xxxx          |

|                             |                         | 15:0      |       | 1                             |       |       |       |           |      |      |      |               |      |           |           |           |          |          | xxxx          |

| 2050                        | BMXPUPBA <sup>(1)</sup> | 31:16     | —     | _                             | —     | —     | —     | -         | —    | —    | —    | —             | —    | —         |           | BMXPUPBA  | <19:16>  |          | 0000          |

|                             |                         | 15:0      |       |                               |       |       |       |           |      |      | BM   | XPUPBA<15:0>  |      |           |           |           |          |          | 0000          |

| 2060                        | BMXPFMSZ                | 31:16     |       |                               |       |       |       |           |      |      | BM   | XPFMSZ<31:0>  |      |           |           |           |          |          | XXXX          |

|                             |                         | 15:0      |       |                               |       |       |       |           |      |      |      |               |      |           |           |           |          |          | xxxx          |

| 2070                        | BMXBOOTSZ               | 31:16     |       |                               |       |       |       |           |      |      | BMX  | (BOOTSZ<31:0) | >    |           |           |           |          |          | 0000          |

|                             |                         | 15:0      |       |                               |       |       |       |           |      |      |      |               |      |           |           |           |          |          | 0000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   |                   |                   |                   |                   | —                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   |                   |                   |                   |                   | —                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | -                 | -                 | —                 | —                 | -                 | —                 | —                | _                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | DPPULUP           | DMPULUP           | DPPULDWN          | DMPULDWN          | VBUSON            | OTGEN             | VBUSCHG          | VBUSDIS          |

### REGISTER 11-4: U10TGCON: USB OTG CONTROL REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

### bit 31-8 Unimplemented: Read as '0'

| bit 7 | DPPULUP: D+ Pull-Up Enable bit |

|-------|--------------------------------|

|       |                                |

- 1 = D+ data line pull-up resistor is enabled

- 0 = D+ data line pull-up resistor is disabled

### bit 6 **DMPULUP:** D- Pull-Up Enable bit

- 1 = D- data line pull-up resistor is enabled

- 0 = D- data line pull-up resistor is disabled

### bit 5 **DPPULDWN:** D+ Pull-Down Enable bit

- 1 = D+ data line pull-down resistor is enabled

- 0 = D+ data line pull-down resistor is disabled

### bit 4 DMPULDWN: D- Pull-Down Enable bit

- 1 = D- data line pull-down resistor is enabled

- 0 = D- data line pull-down resistor is disabled

- bit 3 **VBUSON:** VBUS Power-on bit

- 1 = VBUS line is powered

- 0 = VBUS line is not powered

- bit 2 OTGEN: OTG Functionality Enable bit

- 1 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under software control

- 0 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under USB hardware control

### bit 1 VBUSCHG: VBUS Charge Enable bit

- 1 = VBUS line is charged through a pull-up resistor

- 0 = VBUS line is not charged through a resistor

### bit 0 VBUSDIS: VBUS Discharge Enable bit

- 1 = VBUS line is discharged through a pull-down resistor

- 0 = VBUS line is not discharged through a resistor

# 12.1 Parallel I/O (PIO) Ports

All port pins have ten registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

### 12.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx, and TRISx registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the presence of outputs higher than VDD (e.g., 5V) on any desired 5V-tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the **"Device Pin Tables"** section for the available pins and their functionality.

# 12.1.2 CONFIGURING ANALOG AND DIGITAL PORT PINS

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs must have their corresponding ANSEL and TRIS bits set. In order to use port pins for I/O functionality with digital modules, such as Timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

If the TRIS bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or Comparator module.

When the PORT register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

# 12.1.3 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be an NOP.

# 12.1.4 INPUT CHANGE NOTIFICATION

The input change notification function of the I/O ports allows the PIC32MX330/350/370/430/450/470 devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature can detect input change-of-states even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a change-of-state.

Five control registers are associated with the CN functionality of each I/O port. The CNENx registers contain the CN interrupt enable control bits for each of the input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

The CNSTATx register indicates whether a change occurred on the corresponding pin since the last read of the PORTx bit.

Each I/O pin also has a weak pull-up and every I/O pin has a weak pull-down connected to it. The pullups act as a current source or sink source connected to the pin, and eliminate the need for external resistors when push-button or keypad devices are connected. The pull-ups and pull-downs are enabled separately using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

| Note: | Pull-ups and pull-downs on change notifi-<br>cation pins should always be disabled<br>when the port pin is configured as a digital |

|-------|------------------------------------------------------------------------------------------------------------------------------------|

|       | output. They should also be disabled on                                                                                            |

|       | 5V tolerant pins when the pin voltage can                                                                                          |

|       | exceed VDD.                                                                                                                        |

An additional control register (CNCONx) is shown in Register 12-3.

# 12.2 CLR, SET, and INV Registers

Every I/O module register has a corresponding CLR (clear), SET (set) and INV (invert) register designed to provide fast atomic bit manipulations. As the name of the register implies, a value written to a SET, CLR or INV register effectively performs the implied operation, but only on the corresponding base register and only bits specified as '1' are modified. Bits specified as '0' are not modified.

Reading SET, CLR and INV registers returns undefined values. To see the affects of a write operation to a SET, CLR or INV register, the base register must be read.

|                             | PIC32MX430F064L, PIC32MX450F128L, PIC32MX450F256L, AND PIC32MX470F512L DEVICES ONLY |           |               |               |               |               |               |               |              |              |              |              |              |              |              | .Y           |              |              |               |

|-----------------------------|-------------------------------------------------------------------------------------|-----------|---------------|---------------|---------------|---------------|---------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| ess                         |                                                                                     |           |               |               |               |               |               |               |              | Bits         | 6            |              |              |              |              |              |              |              |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup>                                                     | Bit Range | 31/15         | 30/14         | 29/13         | 28/12         | 27/11         | 26/10         | 25/9         | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6300                        | ANSELD                                                                              | 31:16     |               | —             | —             | —             | —             |               | —            | —            | —            |              | —            | —            | —            |              | —            |              | 0000          |

|                             |                                                                                     | 15:0      | _             | —             | —             | _             | —             | —             | —            | —            | —            | _            | —            | —            | ANSELD3      | ANSELD2      | ANSELD1      | _            | 000E          |

| 6310                        | TRISD                                                                               | 31:16     | _             | —             | —             | —             | —             | —             | —            | —            | —            |              | —            | _            | _            | _            | —            | _            | 0000          |

|                             | _                                                                                   | 15:0      | TRISD15       | TRISD14       | TRISD13       | TRISD12       | TRISD11       | TRISD10       | TRISD9       | TRISD8       | TRISD7       | TRISD6       | TRISD5       | TRISD4       | TRISD3       | TRISD2       | TRISD1       | TRISD0       | xxxx          |

| 5320                        | PORTD                                                                               | 31:16     | _             | —             | _             | —             | —             | —             | —            | —            | —            |              | —            | —            |              | —            | —            | _            | 0000          |

|                             | _                                                                                   | 15:0      | RD15          | RD14          | RD13          | RD12          | RD11          | RD10          | RD9          | RD8          | RD7          | RD6          | RD5          | RD4          | RD3          | RD2          | RD1          | RD0          | xxxx          |

| 6330                        | LATD                                                                                | 31:16     |               | —             | —             | —             | —             | —             | —            | —            | —            | —            | —            | —            | —            |              | —            | —            | 0000          |

|                             |                                                                                     | 15:0      | LATD15        | LATD14        | LATD13        | LATD12        | LATD11        | LATD10        | LATD9        | LATD8        | LATD7        | LATD6        | LATD5        | LATD4        | LATD3        | LATD2        | LATD1        | LATD0        | XXXX          |

| 6340                        | ODCD                                                                                | 31:16     | —             | —             | —             | —             | —             | —             | —            | —            | —            | —            | —            | —            | —            | —            | —            | _            | 0000          |

|                             |                                                                                     | 15:0      | ODCD15        | ODCD14        | ODCD13        | ODCD12        | ODCD11        | ODCD10        | ODCD9        | ODCD8        | ODCD7        | ODCD6        | ODCD5        | ODCD4        | ODCD3        | ODCD2        | ODCD1        | ODCD0        | xxxx          |

| 6350                        | CNPUD                                                                               | 31:16     | -             | —             | —             | —             | —             | -             | —            | —            | —            | —            | —            | —            | —            | —            | —            | -            | 0000          |

|                             |                                                                                     | 15:0      | CNPUD15       | CNPUD14       | CNPUD13       | CNPUD12       | CNPUD11       | CNPUD10       |              | CNPUD8       | CNPUD7       | CNPUD6       | CNPUD5       | CNPUD4       | CNPUD3       | CNPUD2       | CNPUD1       | CNPUD0       | xxxx          |

| 6360                        | CNPDD                                                                               | 31:16     | -             | —             | —             | —             | —             | -             | —            | —            | —            | —            | _            | —            | —            | —            | —            | -            | 0000          |

|                             |                                                                                     |           | CNPDD15       | -             | CNPDD13       | CNPDD12       | CNPDD11       | CNPDD10       |              | CNPDD8       | -            | CNPDD6       |              | CNPDD4       | CNPDD3       | CNPDD2       | CNPDD1       | CNPDD0       | XXXX          |

| 6370                        | CNCOND                                                                              | 31:16     | _             |               | -             |               |               |               |              |              |              |              |              |              |              | _            |              |              | 0000          |

|                             |                                                                                     | 15:0      | ON            |               | SIDL          |               |               |               |              |              |              |              |              |              |              | _            |              |              | 0000          |

| 6380                        | CNEND                                                                               | 31:16     | -             | -             | -             | -             |               |               |              | -            | -            |              | -            | -            | -            | -            |              |              | 0000          |

|                             |                                                                                     | 15:0      | CNIED15       | CNIED14       | CNIED13       | CNIED12       | CNIED11       | CNIED10       | CNIED9       | CNIED8       | CNIED7       | CNIED6       | CNIED5       | CNIED4       | CNIED3       | CNIED2       | CNIED1       | CNIED0       | XXXX          |

| 6200                        |                                                                                     | 31:16     | -             | -             | —             | —             | —             | -             | -            | -            | -            | -            | —            | -            | —            | —            | —            | -            | 0000          |

| 6390                        | CNSTATD                                                                             | 15:0      | CNS<br>TATD15 | CN<br>STATD14 | CN<br>STATD13 | CN<br>STATD12 | CN<br>STATD11 | CN<br>STATD10 | CN<br>STATD9 | CN<br>STATD8 | CN<br>STATD7 | CN<br>STATD6 | CN<br>STATD5 | CN<br>STATD4 | CN<br>STATD3 | CN<br>STATD2 | CN<br>STATD1 | CN<br>STATD0 | xxxx          |

# TABLE 12-7: PORTD REGISTER MAP FOR PIC32MX330F064L, PIC32MX350F128L, PIC32MX350F256L, PIC32MX370F512L,

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

# TABLE 12-12: PORTF REGISTER MAP FOR PIC32MX430F064L, PIC32MX450F128L, PIC32MX450F256L, AND PIC32MX470F512L DEVICES ONLY

|                             |                                 | U         | UNLY  |       |               |               |       |       |      |              |      |      |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|---------------|---------------|-------|-------|------|--------------|------|------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| ess                         |                                 | Ô         |       |       |               |               |       |       |      | Bit          | s    |      |              |              |              |              |              |              |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13         | 28/12         | 27/11 | 26/10 | 25/9 | 24/8         | 23/7 | 22/6 | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6510                        | TRISF                           | 31:16     | _     |       | —             | —             | _     | —     | _    | —            | _    | -    | —            | _            | —            | -            | —            | _            | 0000          |

| 0010                        | -                               | 15:0      | —     | —     | TRISF13       | TRISF12       | —     | —     | _    | TRISF8       | —    | —    | TRISF5       | TRISF4       | TRISF3       | TRISF2       | TRISF1       | TRISF0       | xxxx          |

| 6520                        | PORTF                           | 31:16     | _     | _     | —             |               | _     | _     |      | —            | _    |      | —            | _            | _            | _            | —            |              | 0000          |

|                             |                                 | 15:0      | —     | _     | RF13          | RF12          | —     | —     |      | RF8          | —    | _    | RF5          | RF4          | RF3          | RF2          | RF1          | RF0          | XXXX          |

| 6530                        | LATF                            | 31:16     | —     | _     | —             | _             | —     | —     |      | —            | —    | _    | —            | —            | —            | _            | —            |              | 0000          |

|                             |                                 | 15:0      | —     | _     | LATF13        | LATF12        | —     | —     |      | LATF8        | —    | _    | LATF5        | LATF4        | LATF3        | LATF2        | LATF1        | LATF0        | XXXX          |

| 6540                        | ODCF                            | 31:16     | —     | _     | —             | _             | —     | —     |      | —            | —    | _    | —            | —            | —            | _            | —            |              | 0000          |

|                             |                                 | 15:0      | —     | _     | ODCF13        | ODCF12        | —     | —     |      | ODCF8        | —    | _    | ODCF5        | ODCF4        | ODCF3        | ODCF2        | ODCF1        | ODCF0        | xxxx          |

| 6550                        | CNPUF                           | 31:16     | _     |       | —             |               | _     | _     |      | —            | _    |      | —            | _            |              | _            | —            |              | 0000          |

|                             |                                 | 15:0      | —     | _     | CNPUF13       | CNPUF12       | —     | _     | _    | CNPUF8       | _    |      | CNPUF5       | CNPUF4       | CNPDF3       | CNPUF2       | CNPUF1       | CNPUF0       | XXXX          |

| 6560                        | CNPDF                           | 31:16     | —     | _     | -             |               | —     | _     | _    | —            | _    |      | —            | —            | —            | —            | —            | —            | 0000          |

|                             | _                               | 15:0      | —     | _     | CNPDF13       | CNPDF12       | —     | _     | _    | CNPDF8       | _    |      | CNPDF5       | CNPFF4       | CNPDF3       | CNPDF2       | CNPDF1       | CNPDF0       | XXXX          |

| 6570                        | CNCONF                          | 31:16     | _     | _     | -             |               | —     | _     | _    | —            | _    |      | —            | _            | —            | _            | _            | _            | 0000          |

|                             |                                 | 15:0      | ON    | _     | SIDL          | —             | _     | —     | _    | _            | _    | —    | —            | _            | —            | _            | _            | _            | 0000          |

| 6580                        | CNENF                           | 31:16     | —     | _     | -             |               | —     | _     | _    | —            | _    |      | —            | —            | —            | —            | —            | —            | 0000          |

|                             | _                               | 15:0      | —     | _     | CNIEF13       | CNIEF12       | —     | _     | _    | CNIEF8       | _    |      | CNIEF5       | CNIEF4       | CNIEF3       | CNIEF2       | CNIEF1       | CNIEF0       | XXXX          |

| 0500                        |                                 | 31:16     | —     |       | —             | —             | —     | —     | —    | —            | —    |      | —            |              | —            |              | _            |              | 0000          |

| 6590                        | CNSTATF                         | 15:0      | —     | —     | CN<br>STATF13 | CN<br>STATF12 | —     | —     | —    | CN<br>STATF8 | _    | —    | CN<br>STATF5 | CN<br>STATF4 | CN<br>STATF3 | CN<br>STATF2 | CN<br>STATF1 | CN<br>STATF0 | xxxx          |

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. Legend:

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit Bit 31/23/15/7 30/22/14 |     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-----------------------------|-----|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0                         | U-0 | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                           | _   | _                 | _                 | _                 | _                 | —                | _                |

| 00.40        | U-0                         | U-0 | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                           | —   | _                 | _                 | _                 | —                 | _                | _                |

| 45.0         | R/W-0                       | U-0 | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1,2)</sup>         | —   | _                 | _                 | —                 | _                 | —                | —                |

| 7.0          | U-0                         | R-y | R-y               | R-y               | R-y               | R-y               | R/W-0            | R/W-0            |

| 7:0          |                             |     | S                 | WDTWINEN          | WDTCLR            |                   |                  |                  |

### REGISTER 15-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Legend:           | y = Values set from Configuration bits on POR |                          |                    |  |  |  |  |  |  |

|-------------------|-----------------------------------------------|--------------------------|--------------------|--|--|--|--|--|--|

| R = Readable bit  | W = Writable bit                              | U = Unimplemented bit, I | read as '0'        |  |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                              | '0' = Bit is cleared     | x = Bit is unknown |  |  |  |  |  |  |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Watchdog Timer Enable bit<sup>(1,2)</sup>

- 1 = Enables the WDT if it is not enabled by the device configuration

- 0 = Disable the WDT if it was enabled in software

- bit 14-7 Unimplemented: Read as '0'

- bit 6-2 **SWDTPS<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value from Device Configuration bits On reset, these bits are set to the values of the WDTPS <4:0> of Configuration bits.

- bit 1 WDTWINEN: Watchdog Timer Window Enable bit

- 1 = Enable windowed Watchdog Timer

- 0 = Disable windowed Watchdog Timer

- bit 0 WDTCLR: Watchdog Timer Reset bit

- 1 = Writing a '1' will clear the WDT

- 0 = Software cannot force this bit to a '0'

- **Note 1:** A read of this bit results in a '1' if the Watchdog Timer is enabled by the device configuration or software.

- 2: When using the 1:1 PBCLK divisor, the user software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

### REGISTER 16-1: ICXCON: INPUT CAPTURE 'X' CONTROL REGISTER (CONTINUED)

- bit 2-0 ICM<2:0>: Input Capture Mode Select bits

- 111 = Interrupt-Only mode (only supported while in Sleep mode or Idle mode)

- 110 = Simple Capture Event mode every edge, specified edge first and every edge thereafter

- 101 = Prescaled Capture Event mode every sixteenth rising edge

- 100 = Prescaled Capture Event mode every fourth rising edge

- 011 = Simple Capture Event mode every rising edge

- 010 = Simple Capture Event mode every falling edge

- 001 = Edge Detect mode every edge (rising and falling)

- 000 = Input Capture module is disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### 20.1 **Control Registers**

# TABLE 20-1: UART1 THROUGH UART5 REGISTER MAP

| ess)                        |                       | Ð         |        |         |        |       |        |       |       | Bi          | ts                                             |         |       |          |          |       |        |       | s          |

|-----------------------------|-----------------------|-----------|--------|---------|--------|-------|--------|-------|-------|-------------|------------------------------------------------|---------|-------|----------|----------|-------|--------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15  | 30/14   | 29/13  | 28/12 | 27/11  | 26/10 | 25/9  | 24/8        | 23/7                                           | 22/6    | 21/5  | 20/4     | 19/3     | 18/2  | 17/1   | 16/0  | All Resets |

| 6000                        | U1MODE <sup>(1)</sup> | 31:16     | _      |         | -      | _     | _      |       |       | _           | _                                              | —       | _     | _        |          | _     |        |       | 0000       |

| 0000                        | UTMODE: /             | 15:0      | ON     |         | SIDL   | IREN  | RTSMD  |       | UEN   | <1:0>       | WAKE                                           | LPBACK  | ABAUD | RXINV    | BRGH     | PDSEI | _<1:0> | STSEL | 0000       |

| 6010                        | U1STA <sup>(1)</sup>  | 31:16     | —      | _       | —      | _     | —      | _     | _     | ADM_EN      |                                                |         |       | ADDR     | <7:0>    |       |        |       | 0000       |

| 0010                        | 01317                 | 15:0      | UTXISE | L<1:0>  | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | T URXISEL<1:0> ADDEN RIDLE PERR FERR OERR URXI |         |       |          | URXDA    | FFFF  |        |       |            |

| 6020                        | U1TXREG               | 31:16     | —      | _       | —      | _     | —      | _     | _     | —           | _                                              | _       | —     | —        | _        | —     | _      | _     | 0000       |

| 0020                        | UTIXILEO              | 15:0      | —      | _       | —      | _     | _      | _     | _     | TX8         | 8 Transmit Register                            |         |       |          |          |       | 0000   |       |            |

| 6030                        | U1RXREG               | 31:16     | —      | —       | —      | —     | —      | —     | —     | —           | —                                              | —       | —     | —        | —        | —     | —      | —     | 0000       |

| 0000                        | ONVILO                | 15:0      | —      | —       | —      | —     | —      | —     | —     | RX8         |                                                |         |       | Receive  | Register |       |        |       | 0000       |

| 6040                        | U1BRG <sup>(1)</sup>  | 31:16     | —      | —       | —      | —     | —      | —     | —     | —           |                                                | —       | —     | —        | —        | —     | —      | —     | 0000       |

| 0010                        | OTDICO                | 15:0      |        |         |        |       |        |       | Bau   | d Rate Gene | Generator Prescaler 00                         |         |       |          |          |       | 0000   |       |            |

| 6200                        | U2MODE <sup>(1)</sup> | 31:16     | —      | —       | —      | —     | —      | —     | —     | —           | _                                              | —       | —     | —        | —        | —     | —      | —     | 0000       |

|                             |                       | 15:0      | ON     | —       | SIDL   | IREN  | RTSMD  | —     | UEN   |             | WAKE                                           | LPBACK  | ABAUD | RXINV    | BRGH     | PDSEI | _<1:0> | STSEL | 0000       |

| 6210                        | U2STA <sup>(1)</sup>  | 31:16     | —      | —       | —      | _     | —      | —     | —     | ADM_EN      |                                                |         | 1     | ADDR     |          |       |        |       | 0000       |

|                             |                       | 15:0      | UTXISE | L<1:0>  | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISE                                         | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR  | OERR   | URXDA | FFFF       |

| 6220                        | U2TXREG               | 31:16     | _      |         | —      | _     | _      | _     |       | —           | _                                              | —       | —     |          | —        | _     | —      | _     | 0000       |

|                             |                       | 15:0      | _      |         | —      | _     | _      | _     |       | TX8         |                                                |         |       | Transmit | Register |       |        |       | 0000       |

| 6230                        | U2RXREG               | 31:16     | —      | —       | —      | —     | —      | —     | —     | —           | _                                              | —       | —     | —        | —        | —     | —      | —     | 0000       |

|                             |                       | 15:0      | —      | —       | —      | —     | —      | —     | —     | RX8         |                                                |         |       | Receive  | Register |       |        |       | 0000       |

| 6240                        | U2BRG <sup>(1)</sup>  | 31:16     | _      | _       | _      | _     | —      | —     |       | —           | _                                              | —       | —     | _        | —        | _     | —      | —     | 0000       |

|                             |                       | 15:0      |        |         |        |       |        |       | Bau   | d Rate Gene | erator Pres                                    | caler   |       |          |          |       |        |       | 0000       |

| 6400                        | U3MODE <sup>(1)</sup> | 31:16     | _      | _       | —      | _     | —      | _     | _     | —           |                                                | —       | —     | —        | —        | —     | —      | —     | 0000       |

|                             |                       | 15:0      | ON     | _       | SIDL   | IREN  | RTSMD  | _     | UEN   | -           | WAKE                                           | LPBACK  | ABAUD | RXINV    | BRGH     | PDSEI | _<1:0> | STSEL | 0000       |

| 6410                        | U3STA <sup>(1)</sup>  | 31:16     | —      | —       | —      | -     | -      | -     | -     | ADM_EN      |                                                |         | 10051 | ADDR     | -        |       | 0505   |       | 0000       |

|                             |                       | 15:0      | UTXISE | :L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISE                                         | =L<1:0> | ADDEN | RIDLE    | PERR     | FERR  | OERR   | URXDA | FFFF       |

| 6420                        | U3TXREG               | 31:16     | _      | _       |        | —     | _      | _     | _     | —<br>       | —                                              | —       | —     | —<br>—   | —        | -     | —      | —     | 0000       |

|                             |                       | 15:0      | -      | _       | —      | _     | _      | _     |       | TX8         |                                                |         |       |          |          | 0000  |        |       |            |

| 6430                        | U3RXREG               | 31:16     | _      | _       | _      | _     | _      | _     | _     | -           | —                                              | —       | —     | —        | —        | —     | —      | —     | 0000       |

|                             |                       | 15:0      | — [    | —       | —      | —     | —      | —     | —     | RX8         |                                                |         |       | Receive  | Register |       |        |       | 0000       |

x = unknown value on Reset; ---- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV registers" for more informa-Note 1: tion.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1    | Bit<br>24/16/8/0    |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|---------------------|

| 24.24        | U-0                 | U-0                 |

| 31:24        | —                 | —                 | —                 | _                 | —                 | —                 | —                   | —                   |

| 00.40        | U-0                 | U-0                 |

| 23:16        | —                 | —                 | —                 | _                 | —                 | —                 | —                   | —                   |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0               | R/W-0               |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDL              | _                 | —                 | F                 | ORM<2:0>            |                     |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0, HSC          | R/C-0, HSC          |

|              |                   | SSRC<2:0>         |                   | CLRASAM           |                   | ASAM              | SAMP <sup>(2)</sup> | DONE <sup>(3)</sup> |

### REGISTER 23-1: AD1CON1: ADC CONTROL REGISTER 1

### Legend:

bit 14

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** ADC Operating Mode bit<sup>(1)</sup>

- 1 = ADC module is operating

- 0 = ADC module is not operating

- Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

- bit 12-11 Unimplemented: Read as '0'

### bit 10-8 **FORM<2:0>:** Data Output Format bits

- 011 = Signed Fractional 16-bit (DOUT = 0000 0000 0000 0000 sddd ddd0 0000)

- 010 = Fractional 16-bit (DOUT = 0000 0000 0000 0000 dddd dddd dd00 0000)

- 000 = Integer 16-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

- 111 = Signed Fractional 32-bit (DOUT = sddd dddd dd00 0000 0000 0000 0000)

- 110 = Fractional 32-bit (DOUT = dddd dddd dd00 0000 0000 0000 0000)

- 101 = Signed Integer 32-bit (DOUT = ssss ssss ssss ssss ssss sssd dddd dddd)

- 100 = Integer 32-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

### bit 7-5 SSRC<2:0>: Conversion Trigger Source Select bits

- 111 = Internal counter ends sampling and starts conversion (auto convert)

- 110 = Reserved

- 101 = Reserved

- 100 = Reserved

- 011 = CTMU ends sampling and starts conversion

- 010 = Timer 3 period match ends sampling and starts conversion

- 001 = Active transition on INTO pin ends sampling and starts conversion

- 000 = Clearing SAMP bit ends sampling and starts conversion

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: If ASAM = 0, software can write a '1' to start sampling. This bit is automatically set by hardware if ASAM = 1. If SSRC = 0, software can write a '0' to end sampling and start conversion. If SSRC ≠ 0, this bit is automatically cleared by hardware to end sampling and start conversion.

- 3: This bit is automatically set by hardware when ADC is complete. Software can write a '0' to clear this bit (a write of '1' is not allowed). Clearing this bit does not affect any operation already in progress. This bit is automatically cleared by hardware at the start of a new conversion.

### REGISTER 23-1: AD1CON1: ADC CONTROL REGISTER 1 (CONTINUED)

bit 4 **CLRASAM:** Stop Conversion Sequence bit (when the first ADC interrupt is generated)

- 1 = Stop conversions when the first ADC interrupt is generated. Hardware clears the ASAM bit when the ADC interrupt is generated.

- 0 = Normal operation, buffer contents will be overwritten by the next conversion sequence

- bit 3 Unimplemented: Read as '0'

- bit 2 ASAM: ADC Sample Auto-Start bit

- 1 = Sampling begins immediately after last conversion completes; SAMP bit is automatically set.

0 = Sampling begins when SAMP bit is set

- bit 1 **SAMP:** ADC Sample Enable bit<sup>(2)</sup>

- 1 = The ADC sample and hold amplifier is sampling

- 0 = The ADC sample/hold amplifier is holding

- When ASAM = 0, writing '1' to this bit starts sampling.

- When SSRC = 000, writing '0' to this bit will end sampling and start conversion.

- bit 0 **DONE:** Analog-to-Digital Conversion Status bit<sup>(3)</sup>

- 1 = Analog-to-digital conversion is done

- 0 = Analog-to-digital conversion is not done or has not started

Clearing this bit will not affect any operation in progress.

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: If ASAM = 0, software can write a '1' to start sampling. This bit is automatically set by hardware if ASAM = 1. If SSRC = 0, software can write a '0' to end sampling and start conversion. If SSRC ≠ 0, this bit is automatically cleared by hardware to end sampling and start conversion.

- **3:** This bit is automatically set by hardware when ADC is complete. Software can write a '0' to clear this bit (a write of '1' is not allowed). Clearing this bit does not affect any operation already in progress. This bit is automatically cleared by hardware at the start of a new conversion.

NOTES:

# REGISTER 26-1: CTMUCON: CTMU CONTROL REGISTER (CONTINUED)

| REGIST    | ER 26-1: CIMUCON: CIMU CONTROL REGISTER (CONTINUE                                                                                     |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------|

| bit 24    | EDG1STAT: Edge 1 Status bit                                                                                                           |

|           | Indicates the status of Edge 1 and can be written to control edge source                                                              |

|           | 1 = Edge 1 has occurred                                                                                                               |

|           | 0 = Edge 1 has not occurred                                                                                                           |

| bit 23    | EDG2MOD: Edge 2 Edge Sampling Select bit                                                                                              |

|           | 1 = Input is edge-sensitive                                                                                                           |

|           | 0 = Input is level-sensitive                                                                                                          |

| bit 22    | EDG2POL: Edge 2 Polarity Select bit                                                                                                   |

|           | 1 = Edge 2 programmed for a positive edge response                                                                                    |

|           | 0 = Edge 2 programmed for a negative edge response                                                                                    |

| DIT 21-18 | EDG2SEL<3:0>: Edge 2 Source Select bits                                                                                               |

|           | 1111 = Reserved                                                                                                                       |

|           | 1110 = C2OUT pin is selected<br>1101 = C1OUT pin is selected                                                                          |

|           | 1100 = PBCLK clock is selected                                                                                                        |

|           | 1011 = IC3 Capture Event is selected                                                                                                  |

|           | 1010 = IC2 Capture Event is selected                                                                                                  |

|           | 1001 = IC1 Capture Event is selected                                                                                                  |

|           | 1000 = CTED13 pin is selected                                                                                                         |

|           | 0111 = CTED12 pin is selected<br>0110 = CTED11 pin is selected                                                                        |

|           | 0101 = CTED10 pin is selected                                                                                                         |

|           | 0100 = CTED9 pin is selected                                                                                                          |

|           | 0011 = CTED1 pin is selected                                                                                                          |

|           | 0010 = CTED2 pin is selected                                                                                                          |

|           | 0001 = OC1 Compare Event is selected                                                                                                  |

|           | 0000 = Timer1 Event is selected                                                                                                       |

|           | Unimplemented: Read as '0'                                                                                                            |

| bit 15    | ON: ON Enable bit                                                                                                                     |

|           | 1 = Module is enabled<br>0 = Module is disabled                                                                                       |

| bit 14    |                                                                                                                                       |

| bit 13    | Unimplemented: Read as '0'                                                                                                            |

| DIL 15    | CTMUSIDL: Stop in Idle Mode bit                                                                                                       |

|           | <ul> <li>1 = Discontinue module operation when device enters Idle mode</li> <li>0 = Continue module operation in Idle mode</li> </ul> |

| bit 12    | <b>TGEN:</b> Time Generation Enable bit <sup>(1)</sup>                                                                                |

|           | 1 = Enables edge delay generation                                                                                                     |

|           | 0 = Disables edge delay generation                                                                                                    |

| bit 11    | EDGEN: Edge Enable bit                                                                                                                |

|           | 1 = Edges are not blocked                                                                                                             |

|           | 0 = Edges are blocked                                                                                                                 |

- **Note 1:** When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 31-42) in Section 31.0 "Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

# 27.4.1 CONTROLLING CONFIGURATION CHANGES

Because peripherals can be disabled during run time, some restrictions on disabling peripherals are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to enabled or disabled peripherals:

- Control register lock sequence

- · Configuration bit select lock

### 27.4.1.1 Control Register Lock

Under normal operation, writes to the PMDx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the PMDLOCK Configuration bit (CFGCON<12>). Setting PMDLOCK prevents writes to the control registers; clearing PMDLOCK allows writes.

To set or clear PMDLOCK, an unlock sequence must be executed. Refer to **Section 6.** "Oscillator" (DS60001112) in the "*PIC32 Family Reference Manual*" for details.

### 27.4.1.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the PMDx registers. The PMDL1WAY Configuration bit (DEVCFG3<28>) blocks the PMDLOCK bit from being cleared after it has been set once. If PMDLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable PMD functionality is to perform a device Reset.

|                    |                     |             |                                                                           |                                          | -DOWN CURRENT (IPD)<br>nditions: 2.3V to 3.6V (unless otherwise stated) |  |  |  |  |  |

|--------------------|---------------------|-------------|---------------------------------------------------------------------------|------------------------------------------|-------------------------------------------------------------------------|--|--|--|--|--|

| DC CHARACTERISTICS |                     |             | Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial |                                          |                                                                         |  |  |  |  |  |

|                    |                     |             | -40°C $\leq$ TA $\leq$ +85°C for Industrial                               |                                          |                                                                         |  |  |  |  |  |

|                    |                     |             |                                                                           | -40°C $\leq$ TA $\leq$ +105°C for V-temp |                                                                         |  |  |  |  |  |

| Param. No.         | Typ. <sup>(2)</sup> | Max.        | Units                                                                     |                                          | Conditions                                                              |  |  |  |  |  |

| PIC32MX330         | ) Device            | s Only      |                                                                           |                                          |                                                                         |  |  |  |  |  |

| Power-Down         | n Curren            | it (IPD) (N | lote 1)                                                                   |                                          |                                                                         |  |  |  |  |  |

| DC40k              | 20                  | 55          | μΑ                                                                        | -40°C                                    |                                                                         |  |  |  |  |  |

| DC40I              | 38                  | 55          | μΑ                                                                        | +25°C                                    | Base Power-Down Current                                                 |  |  |  |  |  |

| DC40n              | 128                 | 167         | μΑ                                                                        | +85°C                                    | Base Power-Down Current                                                 |  |  |  |  |  |

| DC40m              | 261                 | 419         | μA                                                                        | +105°C                                   |                                                                         |  |  |  |  |  |

| PIC32MX430         | Device              | s Only      |                                                                           |                                          |                                                                         |  |  |  |  |  |

| Power-Down         | n Curren            | nt (IPD) (N | lote 1)                                                                   |                                          |                                                                         |  |  |  |  |  |

| DC40k              | 12                  | 28          | μΑ                                                                        | -40°C                                    |                                                                         |  |  |  |  |  |

| DC40I              | 21                  | 28          | μΑ                                                                        | +25°C                                    | Base Power-Down Current                                                 |  |  |  |  |  |

| DC40n              | 128                 | 167         | μΑ                                                                        | +85°C                                    |                                                                         |  |  |  |  |  |

| DC40m              | 261                 | 419         | μA                                                                        | +105°C                                   |                                                                         |  |  |  |  |  |

| PIC32MX350         | 0F128 De            | evices O    | nly                                                                       |                                          |                                                                         |  |  |  |  |  |

| Power-Down         | n Curren            | it (IPD) (N | lote 1)                                                                   |                                          |                                                                         |  |  |  |  |  |

| DC40k              | 31                  | 70          | μΑ                                                                        | -40°C                                    |                                                                         |  |  |  |  |  |

| DC40I              | 45                  | 70          | μΑ                                                                        | +25°C                                    | Base Power-Down Current                                                 |  |  |  |  |  |

| DC40n              | 175                 | 280         | μΑ                                                                        | +85°C                                    |                                                                         |  |  |  |  |  |

| DC40m              | 415                 | 600         | μA                                                                        | +105°C                                   |                                                                         |  |  |  |  |  |

| PIC32MX450         | 0F128 De            | evices O    | nly                                                                       |                                          |                                                                         |  |  |  |  |  |

| Power-Dow          | n Curren            | it (IPD) (N | lote 1)                                                                   |                                          |                                                                         |  |  |  |  |  |

| DC40k              | 19                  | 35          | μA                                                                        | -40°C                                    |                                                                         |  |  |  |  |  |

| DC40I              | 28                  | 35          | μA                                                                        | +25°C                                    | Base Power-Down Current                                                 |  |  |  |  |  |

| DC40n              | 175                 | 280         | μA                                                                        | +85°C                                    |                                                                         |  |  |  |  |  |

| DC40m              | 415                 | 600         | μA                                                                        | +105°C                                   |                                                                         |  |  |  |  |  |

| Note 1: Th         | ne test co          | onditions   | for IPD m                                                                 | easurements are                          | as follows:                                                             |  |  |  |  |  |

#### TABLE 31-7. DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Sleep mode, program Flash memory Wait states = 7, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is set

- · WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- · RTCC and JTAG are disabled

- Voltage regulator is off during Sleep mode (VREGS bit in the RCON register = 0)

- 2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The  $\Delta$  current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.