Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Betano                     |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

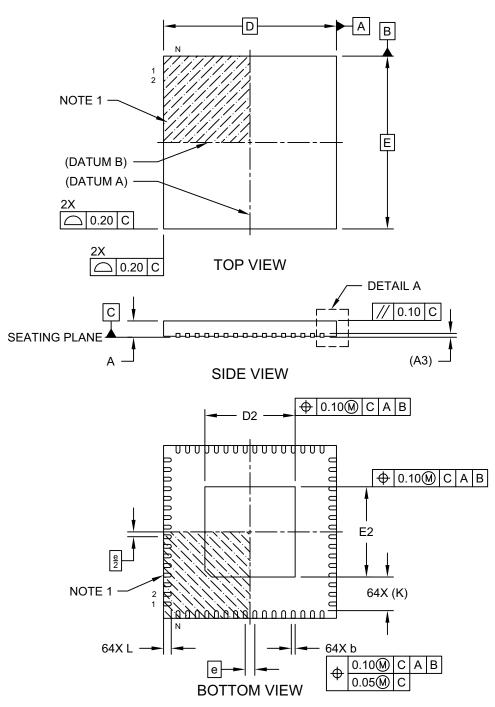

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-VQFN (9x9)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx350f128h-v-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                        | Pin Numb                 | er                                                  |             |                |                                                                                 |

|----------|------------------------|--------------------------|-----------------------------------------------------|-------------|----------------|---------------------------------------------------------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP          | 124-pin<br>VTLA                                     | Pin<br>Type | Buffer<br>Type | Description                                                                     |

| CTED4    | 22                     | 33                       | B19                                                 | 1           | ST             | CTMU External Edge Input 4                                                      |

| CTED5    | 29                     | 43                       | B24                                                 | I           | ST             | CTMU External Edge Input 5                                                      |

| CTED6    | 30                     | 44                       | A29                                                 | I           | ST             | CTMU External Edge Input 6                                                      |

| CTED7    | —                      | 9                        | B5                                                  | I           | ST             | CTMU External Edge Input 7                                                      |

| CTED8    | —                      | 92                       | A62                                                 | I           | ST             | CTMU External Edge Input 8                                                      |

| CTED9    | —                      | 60                       | A40                                                 | I           | ST             | CTMU External Edge Input 9                                                      |

| CTED10   | 21                     | 32                       | A23                                                 | I           | ST             | CTMU External Edge Input 10                                                     |

| CTED11   | 23                     | 34                       | A24                                                 | I           | ST             | CTMU External Edge Input 11                                                     |

| CTED12   | 15                     | 24                       | A15                                                 | I           | ST             | CTMU External Edge Input 12                                                     |

| CTED13   | 14                     | 23                       | B13                                                 | I           | ST             | CTMU External Edge Input 13                                                     |

| MCLR     | 7                      | 13                       | B7                                                  | I/P         | ST             | Master Clear (Reset) input. This pin is an active-low Reset to the device.      |

| AVdd     | 19                     | 30                       | A22                                                 | Р           | Р              | Positive supply for analog modules. This pin must be<br>connected at all times. |

| AVss     | 20                     | 31                       | B18                                                 | Р           | Р              | Ground reference for analog modules                                             |

| Vdd      | 10, 26, 38,<br>57      | 2, 16, 37,<br>46, 62, 86 | B1, A10, A14,<br>B21, A30,<br>A41, A48,<br>A59, B53 | Ρ           | _              | Positive supply for peripheral logic and I/O pins                               |

| Vcap     | 56                     | 85                       | B48                                                 | Р           | —              | Capacitor for Internal Voltage Regulator                                        |

| Vss      | 9, 25, 41              | 15, 36, 45,<br>65, 75    | A3, B8, B12,<br>A25, B25,<br>A43, B41,<br>A63       | Ρ           | _              | Ground reference for logic and I/O pins                                         |

| VREF+    | 16                     | 29                       | B17                                                 | I           | Analog         | Analog Voltage Reference (High) Input                                           |

| VREF-    | 15                     | 28                       | A21                                                 | I           | Analog         | Analog Voltage Reference (Low) Input                                            |

#### TARI E 1-1. PINOLIT I/O DESCRIPTIONS (CONTINUED)

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer

Analog = Analog input O = Output

I = Input

Note 1: This pin is only available on devices without a USB module.

This pin is only available on devices with a USB module. 2:

3: This pin is not available on 64-pin devices.

# **10.1 Control Registers**

# TABLE 10-1: DMA GLOBAL REGISTER MAP

| ess                         |                                 | 0         |       |       |       |         |         |       |      | Bit      | S       |      |      |      |      |      |          |      | ŝ         |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|---------|---------|-------|------|----------|---------|------|------|------|------|------|----------|------|-----------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12   | 27/11   | 26/10 | 25/9 | 24/8     | 23/7    | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1     | 16/0 | All Reset |

| 2000                        | DMACON                          | 31:16     | -     | _     | -     | —       | —       | _     | —    | —        | —       | —    | _    | —    | -    | —    | —        | _    | 0000      |

| 3000                        | DIVIACON                        | 15:0      | ON    | _     | _     | SUSPEND | DMABUSY | —     | _    | _        | _       | _    | _    | —    | —    | _    | —        | _    | 0000      |

| 2010                        | DMASTAT                         | 31:16     |       | _     | —     | —       | —       | _     | —    | —        | —       | —    | _    | _    | —    | _    | —        | _    | 0000      |

| 3010                        | DIVIASTAT                       | 15:0      |       | _     | —     | —       | —       | _     | —    | —        | —       | —    | _    | _    | RDWR | C    | MACH<2:0 | >    | 0000      |

| 2020                        | DMAADDR                         | 31:16     |       |       |       |         |         |       |      | DMAADD   | D-21.05 |      |      |      |      |      |          |      | 0000      |

| 3020                        | DIVIAADDR                       | 15:0      |       |       |       |         |         |       |      | DIVIAADD | KN01.02 |      |      |      |      |      |          |      | 0000      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

# TABLE 10-2: DMA CRC REGISTER MAP

| ess                         |                                 |           |       |                |       |                  |       |           |      | Bi   | ts        |        | _      |      |      |      |          |      |            |

|-----------------------------|---------------------------------|-----------|-------|----------------|-------|------------------|-------|-----------|------|------|-----------|--------|--------|------|------|------|----------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14          | 29/13 | 28/12            | 27/11 | 26/10     | 25/9 | 24/8 | 23/7      | 22/6   | 21/5   | 20/4 | 19/3 | 18/2 | 17/1     | 16/0 | All Resets |

| 2020                        |                                 | 31:16     | _     | —              | BYTO  | TO<1:0> WBO BITO |       |           |      |      |           |        |        | 0000 |      |      |          |      |            |

| 3030                        | DCRCCON                         | 15:0      | _     | —              | _     |                  |       | PLEN<4:0> |      |      | CRCEN     | CRCAPP | CRCTYP | —    | —    | C    | RCCH<2:0 | >    | 0000       |

| 3040                        | DCRCDATA                        | 31:16     |       |                |       |                  |       |           |      |      | TA -21.05 |        |        |      |      |      |          |      | 0000       |

| 3040                        | DCRCDAIA                        | 15:0      |       | DCRCDATA<31:0> |       |                  |       |           |      |      |           |        |        |      |      |      |          |      |            |

| 2050                        | DCRCXOR                         | 31:16     |       | 0000           |       |                  |       |           |      |      |           |        | 0000   |      |      |      |          |      |            |

| 3050                        | DURUXUR                         | 15:0      |       | DCRCXOR<31:0>  |       |                  |       |           |      |      |           |        |        | 0000 |      |      |          |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| INE OIDTE    | CEGISTER 10-6. DEFIXECON: DIA CHANNEL X EVENT CONTROL REGISTER |                            |                   |                   |                   |                   |                  |                  |  |  |  |

|--------------|----------------------------------------------------------------|----------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7                                              | Bit<br>30/22/14/6          | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 31:24        | U-0                                                            | U-0                        | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        |                                                                | —                          | _                 | —                 | —                 |                   | —                | —                |  |  |  |

| 22:16        | R/W-1                                                          | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |  |

| 23:16        |                                                                |                            |                   | CHAIRQ•           | <7:0>(1)          |                   |                  |                  |  |  |  |

| 15.0         | R/W-1                                                          | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |  |

| 15:8         |                                                                | CHSIRQ<7:0> <sup>(1)</sup> |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | S-0                                                            | S-0                        | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |  |  |  |

| 7.0          | CFORCE                                                         | CABORT                     | PATEN             | SIRQEN            | AIRQEN            |                   |                  |                  |  |  |  |

#### REGISTER 10-8 DCHxECON: DMA CHANNEL 'x' EVENT CONTROL REGISTER

| Legend:           | S = Settable bit |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# bit 31-24 Unimplemented: Read as '0'

| bit 31-24 | Unimplemented: Read as '0'                                                                                 |

|-----------|------------------------------------------------------------------------------------------------------------|

| bit 23-16 | CHAIRQ<7:0>: Channel Transfer Abort IRQ bits <sup>(1)</sup>                                                |

|           | 11111111 = Interrupt 255 will abort any transfers in progress and set CHAIF flag                           |

|           | •                                                                                                          |

|           | •                                                                                                          |

|           | •                                                                                                          |

|           | 00000001 = Interrupt 1 will abort any transfers in progress and set CHAIF flag                             |

|           | 00000000 = Interrupt 0 will abort any transfers in progress and set CHAIF flag                             |

| bit 15-8  | CHSIRQ<7:0>: Channel Transfer Start IRQ bits <sup>(1)</sup>                                                |

|           | 11111111 = Interrupt 255 will initiate a DMA transfer                                                      |

|           | •                                                                                                          |

|           | •                                                                                                          |

|           |                                                                                                            |

|           | 00000001 = Interrupt 1 will initiate a DMA transfer<br>00000000 = Interrupt 0 will initiate a DMA transfer |

| h:4 7     |                                                                                                            |

| bit 7     | CFORCE: DMA Forced Transfer bit                                                                            |

|           | 1 = A DMA transfer is forced to begin when this bit is written to a '1'                                    |

|           | 0 = This bit always reads '0'                                                                              |

| bit 6     | CABORT: DMA Abort Transfer bit                                                                             |

|           | 1 = A DMA transfer is aborted when this bit is written to a '1'                                            |

|           | 0 = This bit always reads '0'                                                                              |

| bit 5     | PATEN: Channel Pattern Match Abort Enable bit                                                              |

|           | 1 = Abort transfer and clear CHEN on pattern match                                                         |

|           | 0 = Pattern match is disabled                                                                              |

| bit 4     | SIRQEN: Channel Start IRQ Enable bit                                                                       |

|           | 1 = Start channel cell transfer if an interrupt matching CHSIRQ occurs                                     |

- Start channel cell transfer if an interrupt matching CHSIRQ occurs 0 = Interrupt number CHSIRQ is ignored and does not start a transfer

- bit 3 AIRQEN: Channel Abort IRQ Enable bit

- 1 = Channel transfer is aborted if an interrupt matching CHAIRQ occurs

- 0 = Interrupt number CHAIRQ is ignored and does not terminate a transfer

- bit 2-0 Unimplemented: Read as '0'

- Note 1: See Table 7-1: "Interrupt IRQ, Vector and Bit Location" for the list of available interrupt IRQ sources.

# PIC32MX330/350/370/430/450/470

#### REGISTER 10-12: DCHxSSIZ: DMA CHANNEL 'x' SOURCE SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        |                   | -                 | —                 | —                 | —                 | —                 | —                | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        |                   | —                 | —                 | —                 | _                 | —                 | _                | _                |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         |                   | CHSSIZ<15:8>      |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | CHSSIZ            | <7:0>             |                   |                  |                  |  |  |  |

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSSIZ<15:0>: Channel Source Size bits

1111111111111111 = 65,535 byte source size

# **REGISTER 10-13: DCHxDSIZ: DMA CHANNEL 'x' DESTINATION SIZE REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | _                 | —                 | _                 | _                 | —                 | _                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | —                 | —                 | _                 | —                 | _                | —                |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         |                   | CHDSIZ<15:8>      |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7.0          | 7:0 CHDSIZ<7:0>   |                   |                   |                   |                   |                   |                  |                  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

# PIC32MX330/350/370/430/450/470

# REGISTER 11-1: U1OTGIR: USB OTG INTERRUPT STATUS REGISTER

|              |                   | ••••••            |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | _                 | _                 | —                 | —                 | -                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | _                 | _                 | —                 | —                 | _                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | —                 | —                 |                   |                   | —                 | —                 | -                | —                |

| 7.0          | R/WC-0, HS        | U-0              | R/WC-0, HS       |

| 7:0          | IDIF              | T1MSECIF          | LSTATEIF          | ACTVIF            | SESVDIF           | SESENDIF          | —                | VBUSVDIF         |

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable b  | oit                |

|-------------------|-------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-8 Unimplemented: Read as '0'

- bit 7 IDIF: ID State Change Indicator bit

- 1 = Change in ID state is detected

- 0 = No change in ID state is detected

# bit 6 T1MSECIF: 1 Millisecond Timer bit

- 1 = 1 millisecond timer has expired

- 0 = 1 millisecond timer has not expired

#### bit 5 LSTATEIF: Line State Stable Indicator bit

- 1 = USB line state has been stable for 1millisecond, but different from last time

- 0 = USB line state has not been stable for 1 millisecond

#### bit 4 ACTVIF: Bus Activity Indicator bit

- 1 = Activity on the D+, D-, ID or VBUS pins has caused the device to wake-up

- 0 = Activity has not been detected

- bit 3 SESVDIF: Session Valid Change Indicator bit

- 1 = VBUS voltage has dropped below the session end level

- 0 = VBUS voltage has not dropped below the session end level

# bit 2 SESENDIF: B-Device VBUS Change Indicator bit

- 1 = A change on the session end input was detected

- 0 = No change on the session end input was detected

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIF: A-Device VBUS Change Indicator bit

- 1 = Change on the session valid input is detected

- 0 = No change on the session valid input is detected

# TABLE 12-1: INPUT PIN SELECTION

| Peripheral Pin | [pin name]R SFR       | [pin name]R bits |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------|-----------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT3           | INT3R                 | INT3R<3:0>       | 0000 = RPD2<br>0001 = RPG8                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| T2CK           | T2CKR                 | T2CKR<3:0>       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| IC3            | IC3R                  | IC3R<3:0>        | 0101 = RPB9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| U1RX           | U1RXR                 | U1RXR<3:0>       | 0111 = RPC14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| U2RX           | U2RXR                 | U2RXR<3:0>       | RPn Pin Selection           0000 = RPD2           0001 = RPG8           0010 = RPF4           0011 = RPD10           0100 = RPF1           0101 = RPB9           0110 = RPB10           0111 = RPC14           1000 = RPB5           1001 = Reserved           1010 = RPC1(3)           1011 = RPD14(3)           1100 = RPG1(3)           1101 = RPA14(3)           1110 = Reserved           1111 = RPF2(1)           0000 = RPD3           0001 = RPG7           0010 = RPF5           0011 = RPB1           0100 = RPF5           0111 = RPC13           1000 = RPB3           1001 = RPB1           0110 = RPE5           0111 = RPC13           1000 = RPB3           1001 = RPB15           0110 = RPC4(3)           1101 = RPA15(3)           1110 = RPF2(1)           1111 = RPF7(2)           0000 = RPD9           0001 = RPB8           0011 = RPB15           0100 = RPB3           0110 = RPB3           0110 = RPB15           0100 = RPB3           0111 = RPB7 |

| U5CTS          | U5CTSR <sup>(3)</sup> | U5CTSR<3:0>      | 1011 = RPD14 <sup>(3)</sup><br>1100 = RPG1 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| REFCLKI        | REFCLKIR              | REFCLKIR<3:0>    | 1110 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| INT4           | INT4R                 | INT4R<3:0>       | 0000 <b>= RPD3</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| T5CK           | T5CKR                 | T5CKR<3:0>       | 0010 = RPF5<br>0011 = RPD11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| IC4            | IC4R                  | IC4R<3:0>        | 0101 = RPB1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| U3RX           | U3RXR                 | U3RXR<3:0>       | 0111 = RPC13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| U4CTS          | U4CTSR                | U4CTSR<3:0>      | 1001 = Reserved<br>1010 = RPC4 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| SDI1           | SDI1R                 | SDI1R<3:0>       | 1100 = RPG0 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| SDI2           | SDI2R                 | SDI2R<3:0>       | 1110 = RPF2 <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| INT2           | INT2R                 | INT2R<3:0>       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| T4CK           | T4CKR                 | T4CKR<3:0>       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| IC2            | IC2R                  | IC2R<3:0>        | 0101 <b>= RPB0</b>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| IC5<br>U1CTS   | IC5R                  | IC5R<3:0>        | 0111 = RPB7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|                | U1CTSR                | U1CTSR<3:0>      | 1001 = RPF12 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| U2CTS          | U2CTSR                | U2CTSR<3:0>      | 1011 = RPF8 <sup>(3)</sup><br>1100 = RPC3 <sup>(3)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SS1            | SS1R                  | SS1R<3:0>        | 1110 = Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                | SS1R                  | SS1R<3:0>        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

**Note 1:** This selection is not available on 64-pin USB devices.

2: This selection is only available on 100-pin General Purpose devices.

3: This selection is not available on 64-pin USB and General Purpose devices.

4: This selection is only available on General Purpose devices.

NOTES:

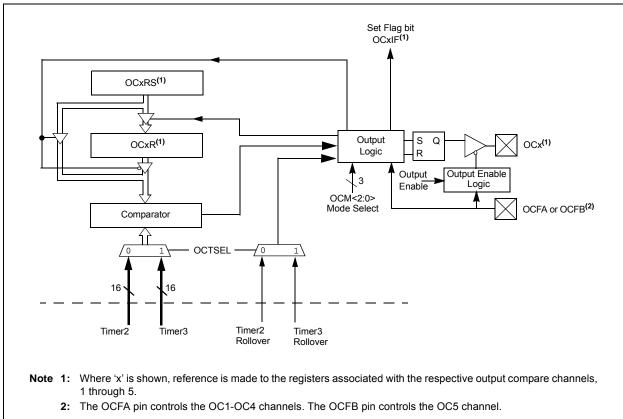

# 17.0 OUTPUT COMPARE

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 16. "Output Compare" (DS60001111), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Output Compare module is used to generate a single pulse or a train of pulses in response to selected time base events. For all modes of operation, the Output Compare module compares the values stored in the OCxR and/or the OCxRS registers to the value in the selected timer. When a match occurs, the Output Compare module generates an event based on the selected mode of operation.

The following are key features of this module:

- Multiple Output Compare modules in a device

- Programmable interrupt generation on compare event

- Single and Dual Compare modes

- Single and continuous output pulse generation

- Pulse-Width Modulation (PWM) mode

- Hardware-based PWM Fault detection and automatic output disable

- Can operate from either of two available 16-bit time bases or a single 32-bit time base

# FIGURE 17-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

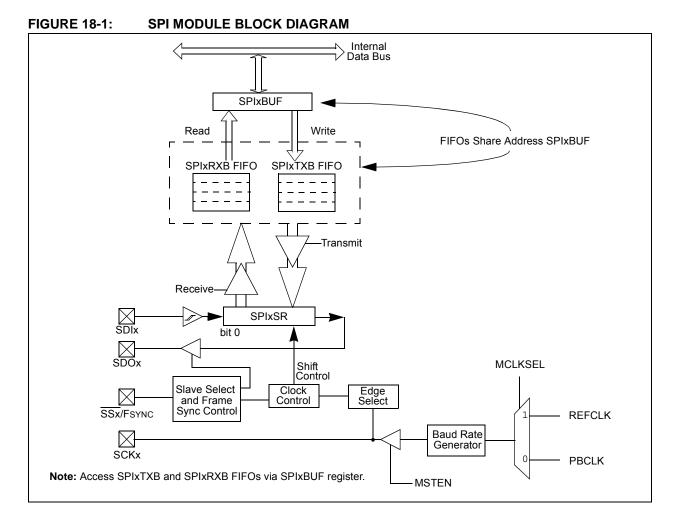

# 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial Peripheral Interface (SPI)" (DS60001106), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The SPI module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontroller devices. These peripheral devices may be Serial EEPROMs, Shift registers, display drivers, Analog-to-Digital Converters (ADC), etc. The PIC32 SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces. Some of the key features of the SPI module are:

- · Master and Slave modes support

- · Four different clock formats

- Enhanced Framed SPI protocol support

- User-configurable 8-bit, 16-bit and 32-bit data width

- Separate SPI FIFO buffers for receive and transmit

FIFO buffers act as 4/8/16-level deep FIFOs based on 32/16/8-bit data width

- Programmable interrupt event on every 8-bit, 16-bit and 32-bit data transfer

- Operation during CPU Sleep and Idle mode

- Audio Codec Support:

- I<sup>2</sup>S protocol

- Left-justified

- Right-justified

- PCM

# 19.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/ pic32). The I<sup>2</sup>C module provides complete hardware support for both Slave and Multi-Master modes of the I<sup>2</sup>C serial communication standard. Figure 19-1 illustrates the I<sup>2</sup>C module block diagram.

Each  $I^2C$  module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for the I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and arbitrates accordingly

- · Provides support for address bit masking

# REGISTER 19-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER

|              | -                 |                   |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | -                 | _                 | -                 | —                 |                   | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | _                 | _                 | —                 | _                | _                |

| 15.0         | R-0, HSC          | R-0, HSC          | U-0               | U-0               | U-0               | R/C-0, HS         | R-0, HSC         | R-0, HSC         |

| 15:8         | ACKSTAT           | TRSTAT            | -                 | -                 | _                 | BCL               | GCSTAT           | ADD10            |

| 7:0          | R/C-0, HS         | R/C-0, HS         | R-0, HSC          | R/C-0, HSC        | R/C-0, HSC        | R-0, HSC          | R-0, HSC         | R-0, HSC         |

| 7:0          | IWCOL             | I2COV             | D_A               | Р                 | S                 | R_W               | RBF              | TBF              |

| Legend:           | HS = Set in hardware | HSC = Hardware set/clear  | ed                |

|-------------------|----------------------|---------------------------|-------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, re | ead as '0'        |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared      | C = Clearable bit |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 ACKSTAT: Acknowledge Status bit

(when operating as  $I^2C$  master, applicable to master transmit operation)

- 1 = Acknowledge was not received from slave

- 0 = Acknowledge was received from slave

Hardware set or clear at end of slave Acknowledge.

- bit 14 **TRSTAT:** Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation)

- 1 = Master transmit is in progress (8 bits + ACK)

- 0 = Master transmit is not in progress

Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge.

- bit 13-11 Unimplemented: Read as '0'

- bit 10 BCL: Master Bus Collision Detect bit

1 = A bus collision has been detected during a master operation

0 = No collision

Hardware set at detection of bus collision. This condition can only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module.

- bit 9 **GCSTAT:** General Call Status bit

- 1 = General call address was received

- 0 = General call address was not received

Hardware set when address matches general call address. Hardware clear at Stop detection.

bit 8 ADD10: 10-bit Address Status bit

1 = 10-bit address was matched

0 = 10-bit address was not matched

Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.

- bit 7 IWCOL: Write Collision Detect bit

- 1 = An attempt to write the I2CxTRN register failed because the I<sup>2</sup>C module is busy

- 0 = No collision

Hardware set at occurrence of write to I2CxTRN while busy (cleared by software).

bit 6 I2COV: Receive Overflow Flag bit

1 = A byte was received while the I2CxRCV register is still holding the previous byte 0 = No overflow

Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

- bit 5 **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave)

- 1 = Indicates that the last byte received was data

- 0 = Indicates that the last byte received was device address

Hardware clear at device address match. Hardware set by reception of slave byte.

# REGISTER 19-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER (CONTINUED)

| <ul> <li>1 = Indicates that a Stop bit has been detected last         0 = Stop bit was not detected last         Hardware set or clear when Start, Repeated Start or Stop detected.     </li> <li>5: Start bit         1 = Indicates that a Start (or Repeated Start) bit has been detected last         0 = Start bit was not detected last         Hardware set or clear when Start, Repeated Start or Stop detected.     </li> <li>bit 2         R_W: Read/Write Information bit (when operating as I<sup>2</sup>C slave)         1 = Read – indicates data transfer is output from slave         0 = Write – indicates data transfer is input to slave         Hardware set or clear after reception of I<sup>2</sup>C device address byte.     </li> <li>bit 1         RBF: Receive Buffer Full Status bit         1 = Receive complete, I2CxRCV is full         0 = Receive not complete, I2CxRCV is empty         Hardware set when I2CxRCV is written with received byte. Hardware clear when software         reads I2CxRCV.     </li> <li>bit 0         TBF: Transmit Buffer Full Status bit         1 = Transmit in progress         I2CxTRN is full         </li> </ul> | bit 4 | P: Stop bit                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------|

| <ul> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> <li>bit 3 S: Start bit <ol> <li>= Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>= Start bit was not detected last</li> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> </ol> </li> <li>bit 2 R_W: Read/Write Information bit (when operating as I<sup>2</sup>C slave) <ol> <li>= Read – indicates data transfer is output from slave</li> <li>Write – indicates data transfer is input to slave</li> <li>Write – indicates data transfer is of I<sup>2</sup>C device address byte.</li> </ol> </li> <li>bit 1 RBF: Receive Buffer Full Status bit <ol> <li>= Receive not complete, I2CxRCV is full</li> <li>= Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> </ol> </li> <li>bit 0 TBF: Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                         |       | 1 = Indicates that a Stop bit has been detected last                              |

| bit 3       S: Start bit         1 = Indicates that a Start (or Repeated Start) bit has been detected last         0 = Start bit was not detected last         Hardware set or clear when Start, Repeated Start or Stop detected.         bit 2       R_W: Read/Write Information bit (when operating as I <sup>2</sup> C slave)         1 = Read – indicates data transfer is output from slave         0 = Write – indicates data transfer is input to slave         Hardware set or clear after reception of I <sup>2</sup> C device address byte.         bit 1       RBF: Receive Buffer Full Status bit         1 = Receive complete, I2CxRCV is full       0 = Receive not complete, I2CxRCV is empty         Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.         bit 0       TBF: Transmit Buffer Full Status bit                                                                                                                                                                                                                                                                                                  |       |                                                                                   |

| <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last<br/>Hardware set or clear when Start, Repeated Start or Stop detected.</li> <li>bit 2 R_W: Read/Write Information bit (when operating as I<sup>2</sup>C slave)</li> <li>1 = Read – indicates data transfer is output from slave</li> <li>0 = Write – indicates data transfer is input to slave<br/>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> <li>bit 1 RBF: Receive Buffer Full Status bit</li> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty<br/>Hardware set when I2CxRCV is written with received byte. Hardware clear when software<br/>reads I2CxRCV.</li> <li>bit 0 TBF: Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                                                                                                                                                   |       | Hardware set or clear when Start, Repeated Start or Stop detected.                |

| <ul> <li>0 = Start bit was not detected last<br/>Hardware set or clear when Start, Repeated Start or Stop detected.</li> <li>bit 2 R_W: Read/Write Information bit (when operating as I<sup>2</sup>C slave)         <ol> <li>1 = Read – indicates data transfer is output from slave</li> <li>0 = Write – indicates data transfer is input to slave</li> <li>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> </ol> </li> <li>bit 1 RBF: Receive Buffer Full Status bit         <ol> <li>= Receive complete, I2CxRCV is full</li> <li>= Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> </ol> </li> <li>bit 0 TBF: Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                            | bit 3 | S: Start bit                                                                      |

| bit 2 <b>R_W:</b> Read/Write Information bit (when operating as I²C slave)1 = Read – indicates data transfer is output from slave0 = Write – indicates data transfer is input to slaveHardware set or clear after reception of I²C device address byte.bit 1 <b>RBF:</b> Receive Buffer Full Status bit1 = Receive complete, I2CxRCV is full0 = Receive not complete, I2CxRCV is emptyHardware set when I2CxRCV is written with received byte. Hardware clear when softwarebit 0 <b>TBF:</b> Transmit Buffer Full Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |                                                                                   |

| <ul> <li>1 = Read – indicates data transfer is output from slave</li> <li>0 = Write – indicates data transfer is input to slave</li> <li>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> <li>bit 1 RBF: Receive Buffer Full Status bit</li> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> <li>bit 0 TBF: Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       | Hardware set or clear when Start, Repeated Start or Stop detected.                |

| <ul> <li>0 = Write – indicates data transfer is input to slave<br/>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> <li>bit 1 <b>RBF:</b> Receive Buffer Full Status bit</li> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty<br/>Hardware set when I2CxRCV is written with received byte. Hardware clear when software<br/>reads I2CxRCV.</li> <li>bit 0 <b>TBF:</b> Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave) |

| <ul> <li>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> <li>bit 1 <b>RBF:</b> Receive Buffer Full Status bit</li> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> <li>bit 0 <b>TBF:</b> Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       | 1 = Read – indicates data transfer is output from slave                           |

| bit 1 <b>RBF:</b> Receive Buffer Full Status bit         1 = Receive complete, I2CxRCV is full         0 = Receive not complete, I2CxRCV is empty         Hardware set when I2CxRCV is written with received byte. Hardware clear when software         reads I2CxRCV.         bit 0 <b>TBF:</b> Transmit Buffer Full Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |                                                                                   |

| <ul> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> <li>bit 0 TBF: Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       | Hardware set or clear after reception of I <sup>2</sup> C device address byte.    |

| <ul> <li>0 = Receive not complete, I2CxRCV is empty<br/>Hardware set when I2CxRCV is written with received byte. Hardware clear when software<br/>reads I2CxRCV.</li> <li>bit 0 TBF: Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 1 | RBF: Receive Buffer Full Status bit                                               |