Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| /oltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

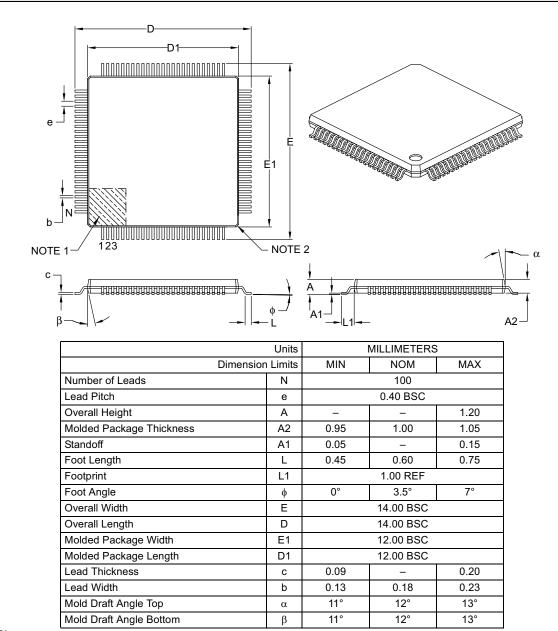

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx350f128ht-v-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 1-1: PINOUT I/O DESCRIPTIONS

| IABLE 1- |                        | Pin Numb        | er              |             |                |                                                                                                                                                                                        |

|----------|------------------------|-----------------|-----------------|-------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                            |

| AN0      | 16                     | 25              | B14             | ı           | Analog         |                                                                                                                                                                                        |

| AN1      | 15                     | 24              | A15             | I           | Analog         |                                                                                                                                                                                        |

| AN2      | 14                     | 23              | B13             | I           | Analog         |                                                                                                                                                                                        |

| AN3      | 13                     | 22              | A13             | I           | Analog         |                                                                                                                                                                                        |

| AN4      | 12                     | 21              | B11             | I           | Analog         |                                                                                                                                                                                        |

| AN5      | 11                     | 20              | A12             | I           | Analog         |                                                                                                                                                                                        |

| AN6      | 17                     | 26              | A20             | I           | Analog         |                                                                                                                                                                                        |

| AN7      | 18                     | 27              | B16             | I           | Analog         |                                                                                                                                                                                        |

| AN8      | 21                     | 32              | A23             | I           | Analog         |                                                                                                                                                                                        |

| AN9      | 22                     | 33              | B19             | I           | Analog         |                                                                                                                                                                                        |

| AN10     | 23                     | 34              | A24             | I           | Analog         |                                                                                                                                                                                        |

| AN11     | 24                     | 35              | B20             | I           | Analog         |                                                                                                                                                                                        |

| AN12     | 27                     | 41              | B23             | I           | Analog         |                                                                                                                                                                                        |

| AN13     | 28                     | 42              | A28             | I           | Analog         | Analog input shappala                                                                                                                                                                  |

| AN14     | 29                     | 43              | B24             | I           | Analog         | Analog input channels.                                                                                                                                                                 |

| AN15     | 30                     | 44              | A29             | I           | Analog         |                                                                                                                                                                                        |

| AN16     | 4                      | 10              | A7              | I           | Analog         |                                                                                                                                                                                        |

| AN17     | 5                      | 11              | B6              | I           | Analog         |                                                                                                                                                                                        |

| AN18     | 6                      | 12              | A8              | I           | Analog         |                                                                                                                                                                                        |

| AN19     | 8                      | 14              | A9              | I           | Analog         |                                                                                                                                                                                        |

| AN20     | 62                     | 98              | A66             | I           | Analog         |                                                                                                                                                                                        |

| AN21     | 64                     | 100             | A67             | I           | Analog         |                                                                                                                                                                                        |

| AN22     | 1                      | 3               | B2              | I           | Analog         |                                                                                                                                                                                        |

| AN23     | 2                      | 4               | A4              | I           | Analog         |                                                                                                                                                                                        |

| AN24     | 49                     | 76              | A52             | I           | Analog         |                                                                                                                                                                                        |

| AN25     | 50                     | 77              | B42             | I           | Analog         |                                                                                                                                                                                        |

| AN26     | 51                     | 78              | A53             | I           | Analog         |                                                                                                                                                                                        |

| AN27     | 3                      | 5               | B3              | I           | Analog         |                                                                                                                                                                                        |

| CLKI     | 39                     | 63              | B34             | I           | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.                                                                                                                 |

| CLKO     | 40                     | 64              | A42             | 0           | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with the OSC2 pin function. |

| OSC1     | 39                     | 63              | B34             | I           | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                        |

| OSC2     | 40                     | 64              | A42             | 0           | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                               |

| SOSCI    | 47                     | 73              | A47             | I           | ST/CMOS        | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                         |

| SOSCO    | 48                     | 74              | B40             | 0           | _              | 32.768 kHz low-power oscillator crystal output.                                                                                                                                        |

|          |                        |                 |                 |             |                |                                                                                                                                                                                        |

Legend: CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

TTL = TTL input buffer

Analog = Analog input O = Output P = Power I = Input

Note 1: This pin is only available on devices without a USB module.

- 2: This pin is only available on devices with a USB module.

- 3: This pin is not available on 64-pin devices.

### 7.1 Interrupts Control Registers

#### TABLE 7-2: INTERRUPT REGISTER MAP

| ess                         |                  |               |        | Bits 20 |         |         |             |         |            |         |          |                       |                       |                      |           |                      |        |        |               |

|-----------------------------|------------------|---------------|--------|---------|---------|---------|-------------|---------|------------|---------|----------|-----------------------|-----------------------|----------------------|-----------|----------------------|--------|--------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name | Bit Range     | 31/15  | 30/14   | 29/13   | 28/12   | 27/11       | 26/10   | 25/9       | 24/8    | 23/7     | 22/6                  | 21/5                  | 20/4                 | 19/3      | 18/2                 | 17/1   | 16/0   | All<br>Resets |

| 1000                        | INTCON           | 31:16         | _      | _       | _       | _       |             | 1       | _          | 1       | _        | _                     | _                     | _                    | _         | _                    | _      | SS0    | 0000          |

| 1000                        | INTCON           | 15:0          | _      | _       | _       | MVEC    | -           |         | TPC<2:0>   |         | _        | _                     | _                     | INT4EP               | INT3EP    | INT2EP               | INT1EP | INT0EP | 0000          |

| 1010                        | INTSTAT          | 31:16         | _      | _       | _       | _       | _           |         | _          | _       | _        | _                     | _                     | _                    | _         | _                    | _      | _      | 0000          |

| 1010                        |                  | 15:0          | _      | _       | _       | _       | _           |         | SRIPL<2:0> |         | _        | _                     |                       |                      | VEC<5:    | )>                   |        |        | 0000          |

| 1020                        | IPTMR            | 31:16<br>15:0 |        |         |         |         |             |         |            | IPTMR<3 | 31:0>    |                       |                       |                      |           |                      |        |        | 0000          |

| 4000                        | IFS0             | 31:16         | FCEIF  | RTCCIF  | FSCMIF  | AD1IF   | OC5IF       | IC5IF   | IC5EIF     | T5IF    | INT4IF   | OC4IF                 | IC4IF                 | IC4EIF               | T4IF      | INT3IF               | OC3IF  | IC3IF  | 0000          |

| 1030                        | IF50             | 15:0          | IC3EIF | T3IF    | INT2IF  | OC2IF   | IC2IF       | IC2EIF  | T2IF       | INT1IF  | OC1IF    | IC1IF                 | IC1EIF                | T1IF                 | INT0IF    | CS1IF                | CS0IF  | CTIF   | 0000          |

| 1010                        | IE04             | 31:16         | U3RXIF | U3EIF   | I2C2MIF | I2C2SIF | I2C2BIF     | U2TXIF  | U2RXIF     | U2EIF   | SPI2TXIF | SPI2RXIF              | SPI2EIF               | PMPEIF               | PMPIF     | CNGIF                | CNFIF  | CNEIF  | 0000          |

| 1040                        | IFS1             | 15:0          | CNDIF  | CNCIF   | CNBIF   | CNAIF   | I2C1MIF     | I2C1SIF | I2C1BIF    | U1TXIF  | U1RXIF   | U1EIF                 | SPI1TXIF              | SPI1RXIF             | SPI1EIF   | USBIF <sup>(2)</sup> | CMP2IF | CMP1IF | 0000          |

| 1050                        | IFS2             | 31:16         | _      | _       | _       | _       | _           | _       | _          | _       | _        | _                     | _                     | _                    | _         | _                    | _      | _      | 0000          |

| 1050                        | IF52             | 15:0          | _      | _       | _       | _       | DMA3IF      | DMA2IF  | DMA1IF     | DMA0IF  | CTMUIF   | U5TXIF <sup>(1)</sup> | U5RXIF <sup>(1)</sup> | U5EIF <sup>(1)</sup> | U4TXIF    | U4RXIF               | U4EIF  | U3TXIF | 0000          |

| 1060                        | IEC0             | 31:16         | FCEIE  | RTCCIE  | FSCMIE  | AD1IE   | OC5IE       | IC5IE   | IC5EIE     | T5IE    | INT4IE   | OC4IE                 | IC4IE                 | IC4EIE               | T4IE      | INT3IE               | OC3IE  | IC3IE  | 0000          |

| 1000                        | IECU             | 15:0          | IC3EIE | T3IE    | INT2IE  | OC2IE   | IC2IE       | IC2EIE  | T2IE       | INT1IE  | OC1IE    | IC1IE                 | IC1EIE                | T1IE                 | INT0IE    | CS1IE                | CS0IE  | CTIE   | 0000          |

| 1070                        | IEC1             | 31:16         | U3RXIE | U3EIE   | I2C2MIE | I2C2SIE | I2C2BIE     | U2TXIE  | U2RXIE     | U2EIE   | SPI2TXIE | SPI2RXIE              | SPI2EIE               | PMPEIE               | PMPIE     | CNGIE                | CNFIE  | CNEIE  | 0000          |

| 1070                        | IECT             | 15:0          | CNDIE  | CNCIE   | CNBIE   | CNAIE   | I2C1MIE     | I2C1SIE | I2C1BIE    | U1TXIE  | U1RXIE   | U1EIE                 | SPI1TXIE              | SPI1RXIE             | SPI1EIE   | USBIE <sup>(2)</sup> | CMP2IE | CMP1IE | 0000          |

| 1080                        | IEC2             | 31:16         |        | _       | _       | -       | -           | _       | _          | _       | _        | _                     | _                     | _                    | _         | _                    | _      | _      | 0000          |

| 1000                        | IECZ             | 15:0          |        | _       | _       | -       | DMA3IE      | DMA2IE  | DMA1IE     | DMA0IE  | CTMUIE   | U5TXIE <sup>(1)</sup> | U5RXIE <sup>(1)</sup> | U5EIE <sup>(1)</sup> | U4TXIE    | U4RXIE               | U4EIE  | U3TXIE | 0000          |

| 1090                        | IPC0             | 31:16         |        | _       | _       |         | INT0IP<2:0> |         | INT0IS     | <1:0>   | _        | _                     | _                     | С                    | S1IP<2:0> |                      | CS1IS  | S<1:0> | 0000          |

| 1090                        | IFCU             | 15:0          | _      | _       | _       |         | CS0IP<2:0>  |         | CS0IS      | <1:0>   | _        | _                     | _                     | (                    | CTIP<2:0> |                      | CTIS   | <1:0>  | 0000          |

| 10A0                        | IPC1             | 31:16         |        | _       | _       |         | INT1IP<2:0> |         | INT1IS     | <1:0>   | _        | _                     | _                     | О                    | C1IP<2:0> |                      | OC1IS  | S<1:0> | 0000          |

| IUAU                        | IPC1             | 15:0          |        | _       | _       |         | IC1IP<2:0>  |         | IC1IS      | <1:0>   | _        | _                     | _                     | -                    | T1IP<2:0> |                      | T1IS   | <1:0>  | 0000          |

| 4000                        | IDCO             | 31:16         |        | _       | _       |         | INT2IP<2:0> |         | INT2IS     | <1:0>   | _        | _                     | _                     | О                    | C2IP<2:0> |                      | OC2IS  | S<1:0> | 0000          |

| 10B0                        | IPC2             | 15:0          | _      | _       | _       |         | IC2IP<2:0>  |         | IC2IS      | <1:0>   | _        | _                     | _                     | -                    | T2IP<2:0> |                      | T2IS   | <1:0>  | 0000          |

| 10C0                        | IPC3             | 31:16         | _      | _       | _       |         | INT3IP<2:0> |         | INT3IS     | <1:0>   | _        | _                     | _                     | О                    | C3IP<2:0> |                      | OC3IS  | S<1:0> | 0000          |

| 1000                        | IPC3             | 15:0          | _      | _       | _       |         | IC3IP<2:0>  |         | IC3IS      | <1:0>   | _        | _                     | _                     | -                    | T3IP<2:0> |                      | T3IS   | <1:0>  | 0000          |

| 1000                        | IDC4             | 31:16         | _      | _       | _       |         | INT4IP<2:0> |         | INT4IS     | <1:0>   | _        | _                     | _                     | О                    | C4IP<2:0> |                      | OC4IS  | S<1:0> | 0000          |

| 10D0                        | IPC4             | 15:0          | _      | _       | _       |         | IC4IP<2:0>  |         | IC4IS<     | <1:0>   | _        | _                     | _                     | -                    | T4IP<2:0> |                      | T4IS   | <1:0>  | 0000          |

| 1050                        | IDCE             | 31:16         | _      | _       | _       |         | AD1IP<2:0>  |         | AD1IS      | <1:0>   | _        | _                     | _                     | О                    | C5IP<2:0> |                      | OC5IS  | S<1:0> | 0000          |

| 10E0                        | IPC5             | 15:0          | _      | _       | _       |         | IC5IP<2:0>  |         | IC5IS<     | <1:0>   | _        | _                     | _                     | -                    | T5IP<2:0> |                      | T5IS-  | <1:0>  | 0000          |

PIC32MX330/350/370/430/450/470

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This bit is only available on 100-pin devices.

2: This bit is only implemented on devices with a USB module.

## 9.2 Control Registers

#### TABLE 9-1: PREFETCH REGISTER MAP

|                             | LE 9-1.               |               | Bits          |                       |            |            |             |                                           |            |            |                           |      |       |            |        |       |             |        |            |

|-----------------------------|-----------------------|---------------|---------------|-----------------------|------------|------------|-------------|-------------------------------------------|------------|------------|---------------------------|------|-------|------------|--------|-------|-------------|--------|------------|

| SS                          |                       |               |               |                       |            |            |             |                                           |            |            |                           |      |       |            |        |       |             |        |            |

| Virtual Address<br>(BF88_#) | Register<br>Name      | Bit Range     | 31/15         | 30/14                 | 29/13      | 28/12      | 27/11       | 26/10                                     | 25/9       | 24/8       | 23/7                      | 22/6 | 21/5  | 20/4       | 19/3   | 18/2  | 17/1        | 16/0   | All Resets |

|                             | CHECON <sup>(1)</sup> | 31:16         | _             | _                     | _          | _          | _           | _                                         | _          | _          |                           | _    | _     | _          | _      | _     | _           | CHECOH | 0000       |

| +000                        | CITLOON               | 15:0          |               | _                     | _          | _          | _           | _                                         | DCSZ       | Z<1:0>     | I                         | _    | PREFE | N<1:0>     | _      | P     | FMWS<2:0    | )>     | 0007       |

| 4010                        | CHEACC <sup>(1)</sup> |               | CHEWEN        | _                     | _          | _          | _           | _                                         | _          | _          | _                         | _    | _     | _          | _      | _     | _           | _      | 0000       |

|                             |                       | 15:0          | _             |                       | _          | _          | _           | _                                         | _          | _          | -                         | _    | _     | _          |        | CHEID | X<3:0>      |        | 00xx       |

| 4020                        | CHETAG <sup>(1)</sup> |               | LTAGBOOT      |                       | _          | _          | _           |                                           |            | _          |                           |      |       | LTAG<      |        |       | T . = . = = |        | xxx0       |

|                             |                       | 15:0          |               |                       |            |            |             | LTAG<                                     | 15:4>      |            |                           | 1    |       |            | LVALID | LLOCK | LTYPE       |        | xxx2       |

| 4030                        | CHEMSK <sup>(1)</sup> | 31:16         | _             | _                     | _          | _          |             | —<br>************************************ | _          | _          | _                         | _    | _     | _          | _      | _     | _           |        | 0000       |

|                             |                       |               |               | YYYY                  |            |            |             |                                           |            |            |                           |      |       |            |        | xxxx  |             |        |            |

| 4040                        | CHEW0                 | 31:16<br>15:0 |               | CHEW0<31:0> xxxx xxxx |            |            |             |                                           |            |            |                           |      |       |            |        |       |             |        |            |

|                             |                       | 31:16         |               | XXX                   |            |            |             |                                           |            |            |                           |      |       |            |        | -     |             |        |            |

| 4050                        | CHEW1                 | 15:0          |               | CHEW1<31:0> xxxx xxxx |            |            |             |                                           |            |            |                           |      |       |            |        |       |             |        |            |

|                             |                       | 31:16         |               |                       |            |            |             |                                           |            |            |                           |      |       |            |        |       |             |        | xxxx       |

| 4060                        | CHEW2                 | 15:0          |               |                       |            |            |             |                                           |            | CHEW2      | <31:0>                    |      |       |            |        |       |             |        | xxxx       |

|                             |                       | 31:16         |               |                       |            |            |             |                                           |            |            |                           |      |       |            |        |       |             |        | xxxx       |

| 4070                        | CHEW3                 | 15:0          |               |                       |            |            |             |                                           |            | CHEW3      | <31:0>                    |      |       |            |        |       |             |        | xxxx       |

| 4000                        | CUEL DU               | 31:16         | _             | _                     | _          | _          | _           | _                                         | _          |            |                           |      | CH    | IELRU<24:1 | 6>     |       |             |        | 0000       |

| 4080                        | CHELRU                | 15:0          | •             |                       |            | •          | •           | •                                         | •          | CHELRU     | <15:0>                    |      |       |            |        |       |             |        | 0000       |

| 4090                        | CHEHIT                | 31:16         |               |                       |            |            |             |                                           |            |            |                           |      |       |            |        | xxxx  |             |        |            |

| 4090                        | CHEITH                | 15:0          |               |                       |            |            |             |                                           |            | CHEHII     | <b>~</b> 51.0 <i>&gt;</i> |      |       |            |        |       |             |        | xxxx       |

| 40A0                        | CHEMIS                | 31:16         |               |                       |            |            |             |                                           |            | CHEMIS     | <31:0>                    |      |       |            |        |       |             |        | xxxx       |

|                             |                       | 15:0          |               |                       |            |            |             |                                           |            |            |                           |      |       |            |        |       |             |        | xxxx       |

| 40C0                        | CHEPFABT              | 31:16         |               |                       |            |            |             |                                           |            | CHEPFAE    | T<31:0>                   |      |       |            |        |       |             |        | XXXX       |

| Legen                       | d                     | 15:0          | n value on Re |                       | ınimnlaman | tod road a | a 'o' Basat | values are                                | ahaun in h | ovadocimal |                           |      |       |            |        |       |             |        | XXXX       |

PIC32MX330/350/370/430/450/470

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

#### 10.1 Control Registers

#### TABLE 10-1: DMA GLOBAL REGISTER MAP

| ess                         |                                 | ø.        |               | Bits S 10/14 29/13 28/12 27/11 26/10 25/9 24/8 23/7 22/6 21/5 20/4 19/3 18/2 17/1 16/0 |       |         |         |       |      |        |         |      |      |      |      |      |          |      |         |

|-----------------------------|---------------------------------|-----------|---------------|----------------------------------------------------------------------------------------|-------|---------|---------|-------|------|--------|---------|------|------|------|------|------|----------|------|---------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14                                                                                  | 29/13 | 28/12   | 27/11   | 26/10 | 25/9 | 24/8   | 23/7    | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1     | 16/0 | II Rese |

| 2000                        | DMACON                          | 31:16     |               | 1                                                                                      | _     | _       | _       | _     | _    | _      | _       | _    | _    | _    | _    | _    | _        | _    | 0000    |

| 3000                        | DIMACON                         | 15:0      | ON            | _                                                                                      |       | SUSPEND | DMABUSY | _     |      |        | _       | _    | _    | _    | _    |      | _        | _    | 0000    |

| 3010                        | DMASTAT                         | 31:16     | _             |                                                                                        | _     | _       | _       | I     | _    | -      | _       | _    | _    | _    | _    |      | _        | _    | 0000    |

| 3010                        | DIVIAGIAI                       | 15:0      | _             | _                                                                                      | -     | _       |         | I     | -    | -      | -       | -    | _    | -    | RDWR |      | MACH<2:0 | >    | 0000    |

| 3020                        | DMAADDR                         | 31:16     |               |                                                                                        |       |         |         |       |      | DMAADD | R<31·0> |      |      |      |      |      |          |      | 0000    |

| 5520                        | DIVII (ADDIX                    | 15:0      | DMAADDR<31:0> |                                                                                        |       |         |         |       |      |        |         |      |      |      |      |      |          |      |         |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information

PIC32MX330/350/370/430/450/470

#### TABLE 10-2: DMA CRC REGISTER MAP

| ess                         |                                 |                    |                     |       |       |        |       |       |      | В    | its  |      |      |      |      |      |      |      |            |

|-----------------------------|---------------------------------|--------------------|---------------------|-------|-------|--------|-------|-------|------|------|------|------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range          | 31/15               | 30/14 | 29/13 | 28/12  | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 2020                        | DCRCCON                         | 31:16              |                     |       | BYTO  | )<1:0> | WBO   | _     | _    | BITO | _    | _    |      | _    | _    | _    |      | _    | 0000       |

| 3030                        | DCRCCON                         | 15:0               |                     |       |       |        |       |       |      |      | 0000 |      |      |      |      |      |      |      |            |

| 2040                        | DCRCDATA                        | 31:16              | 6 DCRCDATA<31:0>    |       |       |        |       |       |      |      | 0000 |      |      |      |      |      |      |      |            |

| 3040                        | DCCCDATA                        | 15:0               | 15:0 DCRCDATA<31.02 |       |       |        |       |       |      |      |      | 0000 |      |      |      |      |      |      |            |

| 2050                        | DCRCXOR                         | 31:16              | 1:16 DCRCXOR<31:0>  |       |       |        |       |       |      |      |      | 0000 |      |      |      |      |      |      |            |

| 3030                        | DCRCXOR                         | 15:0 DCRCXOR<31:0> |                     |       |       |        |       |       |      |      | 0000 |      |      |      |      |      |      |      |            |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| O   |

|-----|

| S   |

| 8   |

| 2   |

| 8   |

| FF  |

| င္က |

| ğ   |

| 9   |

| ű   |

|     |

| TARIF 10-3. | DMA CHANNEL   | <b>0 THROUGH CHANNEL</b> | 3 REGISTER MAP |

|-------------|---------------|--------------------------|----------------|

| IADLL IU-J. | DIVIA CHANNEL | U IIINOUGII CHAMME       | JILGIJILK WAF  |

| ess                         |                                 |               |                                                        | Bits g               |       |       |        |       |      |          |               |        |        |        |        |        |        |        |            |

|-----------------------------|---------------------------------|---------------|--------------------------------------------------------|----------------------|-------|-------|--------|-------|------|----------|---------------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15                                                  | 30/14                | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8     | 23/7          | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 0000                        | DOLLOCON                        | 31:16         | _                                                      | _                    | _     | _     |        | _     | _    | _        | _             | _      | _      |        | _      | _      | _      | _      | 0000       |

| 3060                        | DCH0CON                         | 15:0          | CHBUSY                                                 | _                    | _     | _     | -      | _     | _    | CHCHNS   | CHEN          | CHAED  | CHCHN  | CHAEN  | _      | CHEDET | CHPR   | I<1:0> | 0000       |

| 3070 [                      | DCH0ECON                        | 31:16         | _                                                      | _                    | _     | _     | -      | _     | _    | _        |               |        |        | CHAIR  | Q<7:0> |        |        |        | 00FF       |

| 3070                        | DCHOLCON                        | 15:0          |                                                        |                      |       | CHSIR | Q<7:0> |       |      |          | CFORCE        | CABORT | PATEN  | SIRQEN | AIRQEN | _      | _      | _      | FFF8       |

| 3080                        | DCH0INT                         | 31:16         | _                                                      |                      | _     | _     | _      | _     | _    | _        | CHSDIE        | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE | 0000       |

| 0000                        |                                 | 15:0          | _                                                      | _                    | _     | _     | _      | _     | _    | _        | CHSDIF        | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3090                        | DCH0SSA                         | 31:16         |                                                        |                      |       |       |        |       |      | CHSSA    | \<31:0>       |        |        |        |        |        |        |        | 0000       |

| 0000                        |                                 | 15:0          |                                                        |                      |       |       |        |       |      | 000,     |               |        |        |        |        |        |        |        | 0000       |

| 30A0                        | DCH0DSA                         | 31:16         |                                                        |                      |       |       |        |       |      | CHDSA    | A<31:0>       |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 15:0          |                                                        |                      |       |       |        |       |      |          | 1             |        |        |        |        |        |        |        | 0000       |

| 30B0                        | DCH0SSIZ                        | 31:16         | _                                                      | 0000<br>CHSSIZe15:05 |       |       |        |       |      |          |               |        |        |        |        |        |        |        |            |

|                             |                                 | 15:0          |                                                        | CHSSIZ<15:0> 0000    |       |       |        |       |      |          |               |        |        |        |        |        |        |        |            |

| 30C0                        | DCH0DSIZ                        | 31:16         | _                                                      |                      |       |       |        |       |      |          |               |        |        |        |        |        |        |        |            |

| -                           |                                 | 15:0          |                                                        |                      |       |       |        |       |      | CHDSI    | Z<15:0><br>I  |        |        |        |        |        |        |        | 0000       |

| 30D0                        | DCH0SPTR                        | 31:16         | _                                                      |                      | _     | _     | _      | _     | _    | - CHODE  | —<br>D 445-05 | _      | _      | _      | _      | _      | _      | _      | 0000       |

|                             |                                 | 15:0          |                                                        |                      |       |       |        |       |      | CHSPT    | K<15:0>       |        |        |        |        |        |        |        | 0000       |

| 30E0                        | DCH0DPTR                        | 31:16<br>15:0 | _                                                      |                      | _     | _     |        | _     | _    | CHDPT    | D<15:0>       | _      | _      | _      | _      | _      | _      | _      | 0000       |

|                             |                                 | 31:16         | _ [                                                    |                      |       |       |        |       |      | CODFI    | K 15.02       |        |        |        |        |        |        | _      | 0000       |

| 30F0                        | DCH0CSIZ                        | 15:0          | _                                                      |                      | _     | _     | _      | _     | _    | CHCSIZ   | 7<15:0>       | _      | _      |        | _      | _      | _      | _      | 0000       |

| +                           |                                 | 31:16         | _ [                                                    |                      | _     | _     | _      | _     | _    |          |               | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3100                        | DCH0CPTR                        | 15:0          |                                                        |                      |       |       |        |       |      | CHCPT    | R<15:0>       |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 31:16         | _                                                      |                      | _     | _     | _      | _     | _    | <u> </u> | _             | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3110                        | DCH0DAT                         | 15:0          | _                                                      |                      | _     | _     | _      |       |      |          |               |        |        | CHPDA  |        |        |        |        | 0000       |

|                             |                                 | 31:16         | _                                                      | _                    | _     | _     | _      | _     | _    | _        | _             | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3120                        | DCH1CON                         |               | CHBUSY                                                 | _                    | _     | _     | -      | _     | _    | CHCHNS   | CHEN          | CHAED  | CHCHN  | CHAEN  | _      | CHEDET | CHPR   | I<1:0> | 0000       |

| 0400                        | 5011150011                      | 31:16         | _                                                      | _                    | _     | _     | _      | _     | _    | _        |               | Į.     | Į.     | CHAIR  | Q<7:0> |        |        |        | 00FF       |

| 3130 [                      | DCH1ECON                        | 15:0          | CHSIRQ<7:0> CFORCE CABORT PATEN SIRQEN AIRQEN — — FFF8 |                      |       |       |        |       |      |          |               |        |        |        |        |        |        |        |            |

| 2140                        | DOLIAINT                        | 31:16         | _                                                      | _                    | _     | _     | _      | _     | _    | _        | CHSDIE        | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE | 0000       |

| 3140                        | DCH1INT                         | 15:0          | _                                                      |                      |       |       |        |       |      |          | CHSDIF        | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3150                        | DCH1SSA                         | 31:16         | CHSSA<31:0>                                            |                      |       |       |        |       |      |          |               |        |        |        |        |        |        |        |            |

| 3130                        | роптоон                         | 15:0          |                                                        |                      |       |       |        |       |      | UH33F    | 1-01.0-       |        |        |        |        |        |        |        | 0000       |

| 3160                        | DCH1DSA                         | 31:16         |                                                        |                      |       |       |        |       |      | CHDS/    | \<31:0>       |        |        |        |        |        |        |        | 0000       |

| 3100                        | DOITIDGA                        | 15:0          |                                                        |                      |       |       |        |       |      | CUDSF    | 7-01.0-       |        |        |        |        |        |        |        | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

#### REGISTER 10-5: DCRCDATA: DMA CRC DATA REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31.24        |                   | DCRCDATA<31:24>   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 22:46        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16        |                   |                   |                   | DCRCDATA          | A<23:16>          |                   |                  |                  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         |                   |                   |                   | DCRCDAT           | A<15:8>           |                   |                  |                  |  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          | DCRCDATA<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 DCRCDATA<31:0>: CRC Data Register bits

Writing to this register will seed the CRC generator. Reading from this register will return the current value of the CRC. Bits greater than PLEN will return '0' on any read.

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

Only the lower 16 bits contain IP header checksum information. The upper 16 bits are always '0'. Data written to this register is converted and read back in 1's complement form (i.e., current IP header checksum value).

When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

Bits greater than PLEN will return '0' on any read.

#### REGISTER 10-6: DCRCXOR: DMA CRCXOR ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31.24        |                   |                   |                   | DCRCXOR           | <31:24>           |                   |                  |                  |  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23.10        |                   |                   |                   | DCRCXOF           | <23:16>           |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         |                   |                   |                   | DCRCXO            | R<15:8>           |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | DCRCXOR<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 DCRCXOR<31:0>: CRC XOR Register bits

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

This register is unused.

When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

- 1 = Enable the XOR input to the Shift register

- 0 = Disable the XOR input to the Shift register; data is shifted in directly from the previous stage in the register

| TABLE 11-1: | USB REGIS | STER MAP | (CONTINUED) | ) |

|-------------|-----------|----------|-------------|---|

|-------------|-----------|----------|-------------|---|

| ess                                         |                                 |           |       |       |       |       |       |       |      |      | Bit  | s    |      |          |        |        |         |        |            |

|---------------------------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|--------|--------|---------|--------|------------|

| Virtual Address (BF88_#)  Register Name (1) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3   | 18/2   | 17/1    | 16/0   | All Resets |

| 5390                                        | U1EP9                           | 31:16     | _     | _     | _     | _     | _     | _     | _    |      | _    | _    | _    | _        | _      | _      | _       | I      | 0000       |

| 3390                                        | OILF9                           | 15:0      | _     | _     | _     | _     | _     | _     | _    |      | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53A0                                        | U1EP10                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | -    | _    | _    | _        | _      | _      | _       |        | 0000       |

| 33A0                                        | OTEFIO                          | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53B0                                        | U1EP11                          | 31:16     | _     | _     | _     | _     | _     | _     | _    |      | ı    | -    | _    | _        | -      | -      |         | I      | 0000       |

| 3360                                        | UIEFII                          | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53C0                                        | U1EP12                          | 31:16     | _     | _     | _     | _     | _     | _     | _    |      | ı    | -    | _    | _        | -      | -      |         | I      | 0000       |

| 3300                                        | OTEF 12                         | 15:0      | _     | _     | _     | _     | _     | _     | _    |      | ı    | -    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53D0                                        | U1EP13                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _        | _      | _      | _       | I      | 0000       |

| 3300                                        | OTEF 13                         | 15:0      | _     | _     | _     | _     | _     | _     | _    |      | ı    | -    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                                        | LIAEDAA                         | 31:16     | _     | _     | _     | _     |       | _     | _    | _    | -    | _    | _    | _        | -      | _      | 1       | -      | 0000       |

| 53E0                                        | U1EP14                          | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| E2E0                                        | LIAEDAE                         | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _        | _      | _      | _       | _      | 0000       |

| 53F0                                        | U1EP15                          | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

- 2: This register does not have associated SET and INV registers.

- 3: This register does not have associated CLR, SET and INV registers.

- 4: Reset value for this bit is undefined.

REGISTER 11-2: U10TGIE: USB OTG INTERRUPT ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | -                 | 1                 | -                 | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 |                   | -                 | -                 | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | R/W-0            |

| 7:0          | IDIE              | T1MSECIE          | LSTATEIE          | ACTVIE            | SESVDIE           | SESENDIE          | _                | VBUSVDIE         |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 IDIE: ID Interrupt Enable bit

1 = ID interrupt is enabled0 = ID interrupt is disabled

bit 6 T1MSECIE: 1 Millisecond Timer Interrupt Enable bit

1 = 1 millisecond timer interrupt is enabled0 = 1 millisecond timer interrupt is disabled

bit 5 LSTATEIE: Line State Interrupt Enable bit

1 = Line state interrupt is enabled0 = Line state interrupt is disabled

hit 4 ACTVIE: Doe Activity Intermed Freehle hi

bit 4 ACTVIE: Bus Activity Interrupt Enable bit

1 = ACTIVITY interrupt is enabled0 = ACTIVITY interrupt is disabled

bit 3 SESVDIE: Session Valid Interrupt Enable bit

1 = Session valid interrupt is enabled

0 = Session valid interrupt is disabled

bit 2 SESENDIE: B-Session End Interrupt Enable bit

1 = B-session end interrupt is enabled

0 = B-session end interrupt is disabled

bit 1 Unimplemented: Read as '0'

bit 0 **VBUSVDIE:** A-VBUS Valid Interrupt Enable bit

1 = A-VBUS valid interrupt is enabled

0 = A-VBUS valid interrupt is disabled

### REGISTER 11-11: U1CON: USB CONTROL REGISTER (CONTINUED)

bit 1 PPBRST: Ping-Pong Buffers Reset bit

1 = Reset all Even/Odd buffer pointers to the EVEN BD banks

0 = Even/Odd buffer pointers not being Reset

bit 0 USBEN: USB Module Enable bit (4)

1 = USB module and supporting circuitry is enabled0 = USB module and supporting circuitry is disabled

**SOFEN:** SOF Enable bit<sup>(5)</sup>

1 = SOF token sent every 1 ms

0 = SOF token is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 11-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set the RESUME bit for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a low-speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

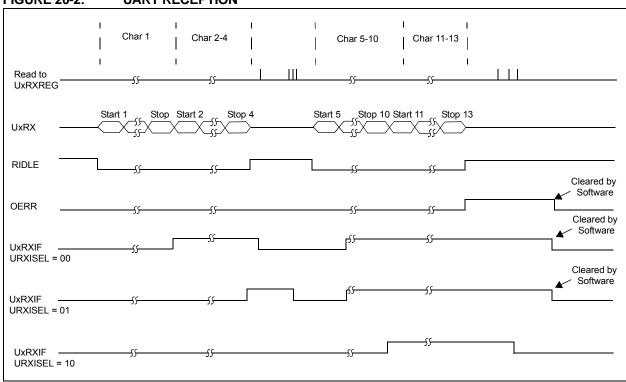

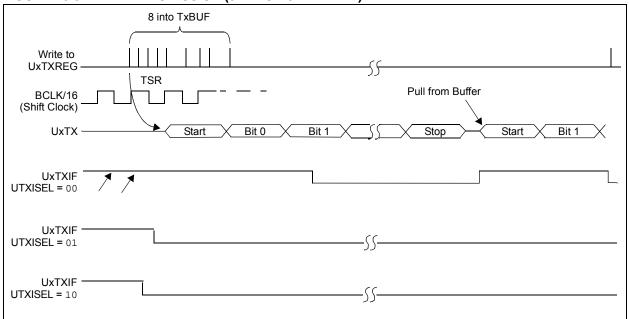

#### 20.2 Timing Diagrams

Figure 20-2 and Figure 20-3 illustrate typical receive and transmit timing for the UART module.

#### FIGURE 20-3: TRANSMISSION (8-BIT OR 9-BIT DATA)

#### REGISTER 21-5: PMSTAT: PARALLEL PORT STATUS REGISTER (SLAVE MODES ONLY)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | -                 | _                 | -                 | _                 | -                | _                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R-0               | R/W-0, HS, SC     | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         | IBF               | IBOV              | -                 | _                 | IB3F              | IB2F              | IB1F             | IB0F             |

| 7.0          | R-1               | R/W-0, HS, SC     | U-0               | U-0               | R-1               | R-1               | R-1              | R-1              |

| 7:0          | OBE               | OBUF              | _                 | _                 | OB3E              | OB2E              | OB1E             | OB0E             |

Legend:HS = Set by HardwareSC = Cleared by softwareR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 IBF: Input Buffer Full Status bit

1 = All writable input buffer registers are full

0 = Some or all of the writable input buffer registers are empty

bit 14 IBOV: Input Buffer Overflow Status bit

1 = A write attempt to a full input byte buffer occurred (must be cleared in software)

0 = No overflow occurred

bit 13-12 Unimplemented: Read as '0'

bit 11-8 IBxF: Input Buffer 'x' Status Full bits

1 = Input Buffer contains data that has not been read (reading buffer will clear this bit)

0 = Input Buffer does not contain any unread data

bit 7 **OBE:** Output Buffer Empty Status bit

1 = All readable output buffer registers are empty

0 = Some or all of the readable output buffer registers are full

bit 6 **OBUF:** Output Buffer Underflow Status bit

1 = A read occurred from an empty output byte buffer (must be cleared in software)

0 = No underflow occurred

bit 5-4 Unimplemented: Read as '0'

bit 3-0 **OBxE:** Output Buffer 'x' Status Empty bits

1 = Output buffer is empty (writing data to the buffer will clear this bit)

0 = Output buffer contains data that has not been transmitted

#### 27.0 POWER-SAVING FEATURES

Note:

This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 10. "Power-Saving Features" (DS60001130), which is available from the Documentation > Reference Manual section of the PIC32 Microchip web site (www.microchip.com/pic32).

This section describes power-saving features for the PIC32MX330/350/370/430/450/470 family of devices. These PIC32 devices offer a total of nine methods and modes, organized into two categories, that allow the user to balance power consumption with device performance. In all of the methods and modes described in this section, power-saving is controlled by software.

#### 27.1 Power Saving with CPU Running

When the CPU is running, power consumption can be controlled by reducing the CPU clock frequency, lowering the PBCLK and by individually disabling modules. These methods are grouped into the following categories:

- FRC Run mode: the CPU is clocked from the FRC clock source with or without postscalers.

- LPRC Run mode: the CPU is clocked from the LPRC clock source.

- Sosc Run mode: the CPU is clocked from the Sosc clock source.

In addition, the Peripheral Bus Scaling mode is available where peripherals are clocked at the programmable fraction of the CPU clock (SYSCLK).

#### 27.2 CPU Halted Methods

The device supports two power-saving modes, Sleep and Idle, both of which Halt the clock to the CPU. These modes operate with all clock sources, as listed below:

- Posc Idle mode: the system clock is derived from the Posc. The system clock source continues to operate. Peripherals continue to operate, but can optionally be individually disabled.

- FRC Idle mode: the system clock is derived from the FRC with or without postscalers. Peripherals continue to operate, but can optionally be individually disabled.

- Sosc Idle mode: the system clock is derived from the Sosc. Peripherals continue to operate, but can optionally be individually disabled.

- LPRC Idle mode: the system clock is derived from the LPRC. Peripherals continue to operate, but can optionally be individually disabled. This is the lowest power mode for the device with a clock

running.

Sleep mode: the CPU, the system clock source and any peripherals that operate from the system clock source are Halted. Some peripherals can operate in Sleep using specific clock sources. This is the lowest power mode for the device.

#### 27.3 Power-Saving Operation

Peripherals and the CPU can be Halted or disabled to further reduce power consumption.

#### 27.3.1 SLEEP MODE

Sleep mode has the lowest power consumption of the device power-saving operating modes. The CPU and most peripherals are Halted. Select peripherals can continue to operate in Sleep mode and can be used to wake the device from Sleep. See the individual peripheral module sections for descriptions of behavior in Sleep.

Sleep mode includes the following characteristics:

- · The CPU is Halted.

- The system clock source is typically shutdown.

See Section 27.3.3 "Peripheral Bus Scaling Method" for specific information.

- There can be a wake-up delay based on the oscillator selection.

- The Fail-Safe Clock Monitor (FSCM) does not operate during Sleep mode.

- The BOR circuit remains operative during Sleep mode.

- The WDT, if enabled, is not automatically cleared prior to entering Sleep mode.

- Some peripherals can continue to operate at limited functionality in Sleep mode. These peripherals include I/O pins that detect a change in the input signal, WDT, ADC, UART and peripherals that use an external clock input or the internal LPRC oscillator (e.g., RTCC, Timer1 and Input Capture).

- I/O pins continue to sink or source current in the same manner as they do when the device is not in Sleep.

- The USB module can override the disabling of the Posc or FRC. Refer to the USB section for specific details.

- Modules can be individually disabled by software prior to entering Sleep in order to further reduce consumption.

| PIC32M | X330/3 | 50/3/0 | /430/4 | 00/4/0 |  |  |

|--------|--------|--------|--------|--------|--|--|

| NOTES: |        |        |        |        |  |  |

|        |        |        |        |        |  |  |

|        |        |        |        |        |  |  |

|        |        |        |        |        |  |  |

|        |        |        |        |        |  |  |

|        |        |        |        |        |  |  |

|        |        |        |        |        |  |  |

|        |        |        |        |        |  |  |

|        |        |        |        |        |  |  |

|        |        |        |        |        |  |  |

|        |        |        |        |        |  |  |

|        |        |        |        |        |  |  |

|        |        |        |        |        |  |  |

|        |        |        |        |        |  |  |

|        |        |        |        |        |  |  |

|        |        |        |        |        |  |  |

|        |        |        |        |        |  |  |

|        |        |        |        |        |  |  |

|        |        |        |        |        |  |  |

|        |        |        |        |        |  |  |

|        |        |        |        |        |  |  |

TABLE 31-6: DC CHARACTERISTICS: IDLE CURRENT (IDLE)

|                   |                        |               | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) |                                                                                                                                                                                    |                                          |                           |  |  |

|-------------------|------------------------|---------------|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|---------------------------|--|--|

| DC CHARACT        | ERISTICS               |               | Operating                                                             | Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                                          |                           |  |  |

| Parameter<br>No.  | Typical <sup>(2)</sup> | Maximum       | Units Conditions                                                      |                                                                                                                                                                                    |                                          |                           |  |  |

| Idle Current (III | DLE): Core Of          | f, Clock on E | Base Curre                                                            | nt (Note 1)                                                                                                                                                                        |                                          |                           |  |  |

| DC30a             | 1                      | 2.2           | mA                                                                    | 4 MHz                                                                                                                                                                              |                                          |                           |  |  |

| DC31a             | 3                      | 5             | mA                                                                    | 10 MHz (Note 3)                                                                                                                                                                    |                                          |                           |  |  |

| DC32a             | 5                      | 7             | mA                                                                    | A 20 MHz (Note 3)                                                                                                                                                                  |                                          |                           |  |  |

| DC33a             | 8                      | 13            | mA                                                                    |                                                                                                                                                                                    | 40 MHz (Note 3)                          |                           |  |  |