Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                |

|---------------------------|--------------------------------------------------------------------------------|

| Product Status            | Active                                                                         |

| Core Processor            | MIPS32® M4K™                                                                   |

| Core Size                 | 32-Bit Single-Core                                                             |

| Speed                     | 80MHz                                                                          |

| Connectivity              | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals               | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O             | 85                                                                             |

| Program Memory Size       | 128KB (128K x 8)                                                               |

| Program Memory Type       | FLASH                                                                          |

| EEPROM Size               | -                                                                              |

| RAM Size                  | 32K x 8                                                                        |

| oltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters           | A/D 28x10b                                                                     |

| Oscillator Type           | Internal                                                                       |

| Operating Temperature     | -40°C ~ 85°C (TA)                                                              |

| Mounting Type             | Surface Mount                                                                  |

| Package / Case            | 100-TQFP                                                                       |

| Supplier Device Package   | 100-TQFP (14x14)                                                               |

| Purchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx350f128l-i-pf |

## TABLE 4: PIN NAMES FOR 100-PIN DEVICES

**100-PIN TQFP (TOP VIEW)**(1,2,3)

PIC32MX330F064L PIC32MX350F128L PIC32MX350F256L PIC32MX370F512L

100

1

| Pin# | Full Pin Name                        |

|------|--------------------------------------|

| 1    | RG15                                 |

| 2    | VDD                                  |

| 3    | AN22/RPE5/PMD5/RE5                   |

| 4    | AN23/PMD6/RE6                        |

| -    | AN27/PMD7/RE7                        |

| 5    |                                      |

| 6    | RPC1/RC1<br>RPC2/RC2                 |

| 7    |                                      |

| 8    | RPC3/RC3                             |

| 9    | RPC4/CTED7/RC4                       |

| 10   | AN16/C1IND/RPG6/SCK2/PMA5/RG6        |

| 11   | AN17/C1INC/RPG7/PMA4/RG7             |

| 12   | AN18/C2IND/RPG8/PMA3/RG8             |

| 13   | MCLR                                 |

| 14   | AN19/C2INC/RPG9/PMA2/RG9             |

| 15   | Vss                                  |

| 16   | VDD                                  |

| 17   | TMS/CTED1/RA0                        |

| 18   | RPE8/RE8                             |

| 19   | RPE9/RE9                             |

| 20   | AN5/C1INA/RPB5/RB5                   |

| 21   | AN4/C1INB/RB4                        |

| 22   | PGED3/AN3/C2INA/RPB3/RB3             |

| 23   | PGEC3/AN2/C2INB/RPB2/CTED13/RB2      |

| 24   | PGEC1/AN1/RPB1/CTED12/RB1            |

| 25   | PGED1/AN0/RPB0/RB0                   |

| 26   | PGEC2/AN6/RPB6/RB6                   |

| 27   | PGED2/AN7/RPB7/CTED3/RB7             |

| 28   | VREF-/CVREF-/PMA7/RA9                |

| 29   | VREF+/CVREF+/PMA6/RA10               |

| 30   | AVDD                                 |

| 31   | AVss                                 |

| 32   | AN8/RPB8/CTED10/RB8                  |

| 33   | AN9/RPB9/CTED4/RB9                   |

| 34   | CVREFOUT/AN10/RPB10/CTED11PMA13/RB10 |

| 35   | AN11/PMA12/RB11                      |

| Pin# | Full Pin Name                   |

|------|---------------------------------|

| 36   | Vss                             |

| 37   | VDD                             |

| 38   | TCK/CTED2/RA1                   |

| 39   | RPF13/RF13                      |

| 40   | RPF12/RF12                      |

| 41   | AN12/PMA11/RB12                 |

| 42   | AN13/PMA10/RB13                 |

| 43   | AN14/RPB14/CTED5/PMA1/RB14      |

| 44   | AN15/RPB15/OCFB/CTED6/PMA0/RB15 |

| 45   | Vss                             |

| 46   | VDD                             |

| 47   | RPD14/RD14                      |

| 48   | RPD15/RD15                      |

| 49   | RPF4/PMA9/RF4                   |

| 50   | RPF5/PMA8/RF5                   |

| 51   | RPF3/RF3                        |

| 52   | RPF2/RF2                        |

| 53   | RPF8/RF8                        |

| 54   | RPF7/RF7                        |

| 55   | RPF6/SCK1/INT0/RF6              |

| 56   | SDA1/RG3                        |

| 57   | SCL1/RG2                        |

| 58   | SCL2/RA2                        |

| 59   | SDA2/RA3                        |

| 60   | TDI/CTED9/RA4                   |

| 61   | TDO/RA5                         |

| 62   | VDD                             |

| 63   | OSC1/CLKI/RC12                  |

| 64   | OSC2/CLKO/RC15                  |

| 65   | Vss                             |

| 66   | RPA14/RA14                      |

| 67   | RPA15/RA15                      |

| 68   | RPD8/RTCC/RD8                   |

| 69   | RPD9/RD9                        |

| 70   | RPD10/PMCS2/RD10                |

Note

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

- 2: Every I/O port pin (RAx-RGx), with the exception of RF6, can be used as a change notification pin (CNAx-CNGx). See Section 12.0 "I/O Ports" for more information.

- 3: RPF6 (pin 55) and RPF7 (pin 54) are only remappable for input functions.

NOTES:

| PIC32MX3 | 330/350/3 | 3/0/430/ | /450/4/ | U |  |

|----------|-----------|----------|---------|---|--|

| NOTES:   |           |          |         |   |  |

|          |           |          |         |   |  |

|          |           |          |         |   |  |

|          |           |          |         |   |  |

|          |           |          |         |   |  |

|          |           |          |         |   |  |

|          |           |          |         |   |  |

|          |           |          |         |   |  |

|          |           |          |         |   |  |

|          |           |          |         |   |  |

|          |           |          |         |   |  |

|          |           |          |         |   |  |

|          |           |          |         |   |  |

|          |           |          |         |   |  |

|          |           |          |         |   |  |

|          |           |          |         |   |  |

|          |           |          |         |   |  |

|          |           |          |         |   |  |

#### REGISTER 6-2: RSWRST: SOFTWARE RESET REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                    |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                    |  |

| 45.0         | U-0 U-0           |                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |  |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                    |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | W-0, HC              |  |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | SWRST <sup>(1)</sup> |  |

**Legend:** HC = Cleared by hardware

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-1 Unimplemented: Read as '0'

bit 0 **SWRST:** Software Reset Trigger bit<sup>(1)</sup>

1 = Enable software Reset event

0 = No effect

**Note 1:** The system unlock sequence must be performed before the SWRST bit can be written. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

## 7.1 Interrupts Control Registers

## TABLE 7-2: INTERRUPT REGISTER MAP

| ess                         |                  |               |        |        |         |         |             |         |            | Bits    |          |                       |                       |                      |           |                      |        |        |               |

|-----------------------------|------------------|---------------|--------|--------|---------|---------|-------------|---------|------------|---------|----------|-----------------------|-----------------------|----------------------|-----------|----------------------|--------|--------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name | Bit Range     | 31/15  | 30/14  | 29/13   | 28/12   | 27/11       | 26/10   | 25/9       | 24/8    | 23/7     | 22/6                  | 21/5                  | 20/4                 | 19/3      | 18/2                 | 17/1   | 16/0   | All<br>Resets |

| 1000                        | INTCON           | 31:16         | _      | _      | _       | _       |             | 1       | _          | 1       | _        | _                     | _                     | _                    | _         | _                    | _      | SS0    | 0000          |

| 1000                        | INTCON           | 15:0          | _      | _      | _       | MVEC    | -           |         | TPC<2:0>   |         | _        | _                     | _                     | INT4EP               | INT3EP    | INT2EP               | INT1EP | INT0EP | 0000          |

| 1010                        | INTSTAT          | 31:16         | _      | _      | _       | _       | _           |         | _          | _       | _        | _                     | _                     | _                    | _         | _                    | _      | _      | 0000          |

| 1010                        |                  | 15:0          | _      | _      | _       | _       | _           |         | SRIPL<2:0> |         | _        | _                     |                       |                      | VEC<5:    | )>                   |        |        | 0000          |

| 1020                        | IPTMR            | 31:16<br>15:0 |        |        |         |         |             |         |            | IPTMR<3 | 31:0>    |                       |                       |                      |           |                      |        |        | 0000          |

| 4000                        | IFS0             | 31:16         | FCEIF  | RTCCIF | FSCMIF  | AD1IF   | OC5IF       | IC5IF   | IC5EIF     | T5IF    | INT4IF   | OC4IF                 | IC4IF                 | IC4EIF               | T4IF      | INT3IF               | OC3IF  | IC3IF  | 0000          |

| 1030                        | IF50             | 15:0          | IC3EIF | T3IF   | INT2IF  | OC2IF   | IC2IF       | IC2EIF  | T2IF       | INT1IF  | OC1IF    | IC1IF                 | IC1EIF                | T1IF                 | INT0IF    | CS1IF                | CS0IF  | CTIF   | 0000          |

| 1010                        | IE04             | 31:16         | U3RXIF | U3EIF  | I2C2MIF | I2C2SIF | I2C2BIF     | U2TXIF  | U2RXIF     | U2EIF   | SPI2TXIF | SPI2RXIF              | SPI2EIF               | PMPEIF               | PMPIF     | CNGIF                | CNFIF  | CNEIF  | 0000          |

| 1040                        | IFS1             | 15:0          | CNDIF  | CNCIF  | CNBIF   | CNAIF   | I2C1MIF     | I2C1SIF | I2C1BIF    | U1TXIF  | U1RXIF   | U1EIF                 | SPI1TXIF              | SPI1RXIF             | SPI1EIF   | USBIF <sup>(2)</sup> | CMP2IF | CMP1IF | 0000          |

| 1050                        | IFS2             | 31:16         | _      | _      | _       | _       | _           | _       | _          | _       | _        | _                     | _                     | _                    | _         | _                    | _      | _      | 0000          |

| 1050                        | IF52             | 15:0          | _      | _      | _       | _       | DMA3IF      | DMA2IF  | DMA1IF     | DMA0IF  | CTMUIF   | U5TXIF <sup>(1)</sup> | U5RXIF <sup>(1)</sup> | U5EIF <sup>(1)</sup> | U4TXIF    | U4RXIF               | U4EIF  | U3TXIF | 0000          |

| 1060                        | IEC0             | 31:16         | FCEIE  | RTCCIE | FSCMIE  | AD1IE   | OC5IE       | IC5IE   | IC5EIE     | T5IE    | INT4IE   | OC4IE                 | IC4IE                 | IC4EIE               | T4IE      | INT3IE               | OC3IE  | IC3IE  | 0000          |

| 1000                        | IECU             | 15:0          | IC3EIE | T3IE   | INT2IE  | OC2IE   | IC2IE       | IC2EIE  | T2IE       | INT1IE  | OC1IE    | IC1IE                 | IC1EIE                | T1IE                 | INT0IE    | CS1IE                | CS0IE  | CTIE   | 0000          |

| 1070                        | IEC1             | 31:16         | U3RXIE | U3EIE  | I2C2MIE | I2C2SIE | I2C2BIE     | U2TXIE  | U2RXIE     | U2EIE   | SPI2TXIE | SPI2RXIE              | SPI2EIE               | PMPEIE               | PMPIE     | CNGIE                | CNFIE  | CNEIE  | 0000          |

| 1070                        | IECI             | 15:0          | CNDIE  | CNCIE  | CNBIE   | CNAIE   | I2C1MIE     | I2C1SIE | I2C1BIE    | U1TXIE  | U1RXIE   | U1EIE                 | SPI1TXIE              | SPI1RXIE             | SPI1EIE   | USBIE <sup>(2)</sup> | CMP2IE | CMP1IE | 0000          |

| 1080                        | IEC2             | 31:16         |        | _      | _       | -       | -           | _       | _          | _       | _        | _                     | _                     | _                    | _         | _                    | _      | _      | 0000          |

| 1000                        | IECZ             | 15:0          |        | _      | _       | -       | DMA3IE      | DMA2IE  | DMA1IE     | DMA0IE  | CTMUIE   | U5TXIE <sup>(1)</sup> | U5RXIE <sup>(1)</sup> | U5EIE <sup>(1)</sup> | U4TXIE    | U4RXIE               | U4EIE  | U3TXIE | 0000          |

| 1090                        | IPC0             | 31:16         |        | _      | _       |         | INT0IP<2:0> |         | INT0IS     | <1:0>   | _        | _                     | _                     | С                    | S1IP<2:0> |                      | CS1IS  | S<1:0> | 0000          |

| 1090                        | IFCU             | 15:0          | _      | _      | _       |         | CS0IP<2:0>  |         | CS0IS      | <1:0>   | _        | _                     | _                     | (                    | CTIP<2:0> |                      | CTIS   | <1:0>  | 0000          |

| 10A0                        | IPC1             | 31:16         |        | _      | _       |         | INT1IP<2:0> |         | INT1IS     | <1:0>   | _        | _                     | _                     | О                    | C1IP<2:0> |                      | OC1IS  | S<1:0> | 0000          |

| IUAU                        | IPC1             | 15:0          |        | _      | _       |         | IC1IP<2:0>  |         | IC1IS      | <1:0>   | _        | _                     | _                     | -                    | T1IP<2:0> |                      | T1IS   | <1:0>  | 0000          |

| 4000                        | IDCO             | 31:16         |        | _      | _       |         | INT2IP<2:0> |         | INT2IS     | <1:0>   | _        | _                     | _                     | О                    | C2IP<2:0> |                      | OC2IS  | S<1:0> | 0000          |

| 10B0                        | IPC2             | 15:0          | _      | _      | _       |         | IC2IP<2:0>  |         | IC2IS      | <1:0>   | _        | _                     | _                     | -                    | T2IP<2:0> |                      | T2IS   | <1:0>  | 0000          |

| 10C0                        | IPC3             | 31:16         | _      | _      | _       |         | INT3IP<2:0> |         | INT3IS     | <1:0>   | _        | _                     | _                     | О                    | C3IP<2:0> |                      | OC3IS  | S<1:0> | 0000          |

| 1000                        | IPC3             | 15:0          | _      | _      | _       |         | IC3IP<2:0>  |         | IC3IS      | <1:0>   | _        | _                     | _                     | -                    | T3IP<2:0> |                      | T3IS   | <1:0>  | 0000          |

| 1000                        | IDC4             | 31:16         | _      | _      | _       |         | INT4IP<2:0> |         | INT4IS     | <1:0>   | _        | _                     | _                     | О                    | C4IP<2:0> |                      | OC4IS  | S<1:0> | 0000          |

| 10D0                        | IPC4             | 15:0          | _      | _      | _       |         | IC4IP<2:0>  |         |            | <1:0>   | _        | _                     | _                     | -                    | T4IP<2:0> |                      | T4IS   | <1:0>  | 0000          |

| 1050                        | IDCE             | 31:16         | _      | _      | _       |         | AD1IP<2:0>  |         | AD1IS      | <1:0>   | _        | _                     | _                     | О                    | C5IP<2:0> |                      | OC5IS  | S<1:0> | 0000          |

| 10E0                        | IPC5             | 15:0          | _      | _      | _       |         | IC5IP<2:0>  |         | IC5IS<     | <1:0>   | _        | _                     | _                     | -                    | T5IP<2:0> |                      | T5IS-  | <1:0>  | 0000          |

PIC32MX330/350/370/430/450/470

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This bit is only available on 100-pin devices.

2: This bit is only implemented on devices with a USB module.

#### REGISTER 7-2: INTSTAT: INTERRUPT STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1          | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------------|-------------------|-------------------|-------------------|---------------------------|------------------|--|--|--|

| 31:24        | U-0 U-0           |                   | U-0                     | U-0               | U-0               | U-0               | U-0                       | U-0              |  |  |  |

| 31.24        | -                 | _                 | -                       | _                 | _                 | -                 | _                         | _                |  |  |  |

| 22.46        | U-0               | U-0 U-0           |                         | U-0               | U-0               | U-0               | U-0                       | U-0              |  |  |  |

| 23:16        | _                 | _                 | _                       | _                 | _                 | _                 | _                         | _                |  |  |  |

| 45.0         | U-0               | U-0               | U-0                     | U-0               | U-0               | R/W-0             | R/W-0                     | R/W-0            |  |  |  |

| 15:8         | _                 | _                 | _                       | _                 | _                 | 8                 | SRIPL<2:0> <sup>(1)</sup> |                  |  |  |  |

| 7:0          | U-0               | U-0               | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0                     | R/W-0            |  |  |  |

| 7:0          | _                 | _                 | VEC<5:0> <sup>(1)</sup> |                   |                   |                   |                           |                  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-11 Unimplemented: Read as '0'

bit 10-8 SRIPL<2:0>: Requested Priority Level bits<sup>(1)</sup>

111-000 = The priority level of the latest interrupt presented to the CPU

bit 7-6 **Unimplemented:** Read as '0'

bit 5-0 **VEC<5:0>:** Interrupt Vector bits<sup>(1)</sup>

11111-00000 = The interrupt vector that is presented to the CPU

Note 1: This value should only be used when the interrupt controller is configured for Single Vector mode.

#### REGISTER 7-3: IPTMR: INTERRUPT PROXIMITY TIMER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 31:24        | IPTMR<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 23:16        | IPTMR<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 15:8         |                   |                   |                   | IPTMI             | R<15:8>           |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | IPTM              | R<7:0>            |                   |                  |                  |  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 **IPTMR<31:0>:** Interrupt Proximity Timer Reload bits

Used by the Interrupt Proximity Timer as a reload value when the Interrupt Proximity timer is triggered by an interrupt event.

#### REGISTER 9-1: CHECON: CACHE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0 U-0           |                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 |                   | _                | _                |

| 00:40        | U-0 U-0           |                   | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | CHECOH           |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | DCSZ             | <b>′</b> <1:0>   |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | R/W-1             | R/W-1            | R/W-1            |

| 7:0          |                   | _                 | PREFE             | :N<1:0>           | _                 | F                 | •                |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-17 Unimplemented: Write '0'; ignore read

bit 16 CHECOH: Cache Coherency Setting on a PFM Program Cycle bit

1 = Invalidate all data and instruction lines

0 = Invalidate all data lnes and instruction lines that are not locked

bit 15-10 Unimplemented: Write '0'; ignore read

bit 9-8 DCSZ<1:0>: Data Cache Size in Lines bits

11 = Enable data caching with a size of 4 Lines

10 = Enable data caching with a size of 2 Lines

01 = Enable data caching with a size of 1 Line

00 = Disable data caching

Changing these bits induce all lines to be reinitialized to the "invalid" state.

bit 7-6 **Unimplemented:** Write '0'; ignore read

bit 5-4 **PREFEN<1:0>:** Predictive Prefetch Enable bits

11 = Enable predictive prefetch for both cacheable and non-cacheable regions

10 = Enable predictive prefetch for non-cacheable regions only

01 = Enable predictive prefetch for cacheable regions only

00 = Disable predictive prefetch

bit 3 Unimplemented: Write '0'; ignore read

bit 2-0 **PFMWS<2:0>:** PFM Access Time Defined in Terms of SYSLK Wait States bits

111 = Seven Wait states

110 = Six Wait states

101 = Five Wait states

100 = Four Wait states

011 = Three Wait states

010 = Two Wait states

001 = One Wait state

000 = Zero Wait state

## 12.3 Peripheral Pin Select

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code or a complete redesign may be the only options.

Peripheral pin select configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The peripheral pin select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to these I/O pins. Peripheral pin select is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 12.3.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the peripheral pin select feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable port number.

#### 12.3.2 AVAILABLE PERIPHERALS

The peripherals managed by the peripheral pin select are all digital-only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs.

In comparison, some digital-only peripheral modules are never included in the peripheral pin select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include  $\rm I^2C$  among others. A similar requirement excludes all modules with analog inputs, such as the Analog-to-Digital Converter (ADC).

A key difference between remappable and non-remappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

# 12.3.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral pin select features are controlled through two sets of SFRs: one to map peripheral inputs, and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

#### 12.3.4 INPUT MAPPING

The inputs of the peripheral pin select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The [pin name]R registers, where [pin name] refers to the peripheral pins listed in Table 12-1, are used to configure peripheral input mapping (see Register 12-1). Each register contains sets of 4 bit fields. Programming these bit fields with an appropriate value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field is shown in Table 12-1.

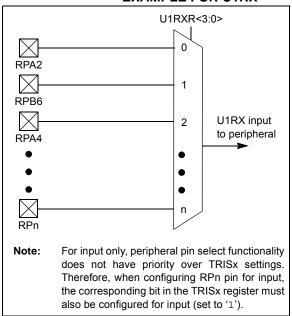

For example, Figure 12-2 illustrates the remappable pin selection for the U1RX input.

FIGURE 12-2: REMAPPABLE INPUT EXAMPLE FOR U1RX

**TABLE 12-1: INPUT PIN SELECTION**

| Peripheral Pin | [pin name]R SFR       | [pin name]R bits | [pin name]R Value to<br>RPn Pin Selection                                               |  |  |  |  |  |  |

|----------------|-----------------------|------------------|-----------------------------------------------------------------------------------------|--|--|--|--|--|--|

| INT3           | INT3R                 | INT3R<3:0>       | 0000 = RPD2<br>0001 = RPG8                                                              |  |  |  |  |  |  |

| T2CK           | T2CKR                 | T2CKR<3:0>       | 0010 = RPF4<br>0011 = RPD10                                                             |  |  |  |  |  |  |

| IC3            | IC3R                  | IC3R<3:0>        | 0100 = RPF1<br>0101 = RPB9<br>                                                          |  |  |  |  |  |  |

| U1RX           | U1RXR                 | U1RXR<3:0>       | 0110 - RPB10<br>0111 = RPC14<br>1000 = RPB5                                             |  |  |  |  |  |  |

| U2RX           | U2RXR                 | U2RXR<3:0>       | 1001 = Reserved<br>1010 = RPC1 <sup>(3)</sup>                                           |  |  |  |  |  |  |

| U5CTS          | U5CTSR <sup>(3)</sup> | U5CTSR<3:0>      | 1011 = RPD14 <sup>(3)</sup><br>1100 = RPG1 <sup>(3)</sup>                               |  |  |  |  |  |  |

| REFCLKI        | REFCLKIR              | REFCLKIR<3:0>    | 1101 = RPA14 <sup>(3)</sup><br>1110 = Reserved<br>1111 = RPF2 <sup>(1)</sup>            |  |  |  |  |  |  |

| INT4           | INT4R                 | INT4R<3:0>       | 0000 = RPD3<br>0001 = RPG7                                                              |  |  |  |  |  |  |

| T5CK           | T5CKR                 | T5CKR<3:0>       | 0010 = RPF5<br>0011 = RPD11                                                             |  |  |  |  |  |  |

| IC4            | IC4R                  | IC4R<3:0>        | 0100 = RPF0<br>0101 = RPB1<br>0110 = RPE5<br>0111 = RPC13<br>1000 = RPB3                |  |  |  |  |  |  |

| U3RX           | U3RXR                 | U3RXR<3:0>       |                                                                                         |  |  |  |  |  |  |

| Ū4CTS          | U4CTSR                | U4CTSR<3:0>      | 1001 = Reserved<br>1010 = RPC4 <sup>(3)</sup>                                           |  |  |  |  |  |  |

| SDI1           | SDI1R                 | SDI1R<3:0>       | 1011 = RPD15 <sup>(3)</sup><br>1100 = RPG0 <sup>(3)</sup>                               |  |  |  |  |  |  |

| SDI2           | SDI2R                 | SDI2R<3:0>       | 1101 = RPA15 <sup>(3)</sup><br>1110 = RPF2 <sup>(1)</sup><br>1111 = RPF7 <sup>(2)</sup> |  |  |  |  |  |  |

| INT2           | INT2R                 | INT2R<3:0>       | 0000 = RPD9<br>0001 = RPG6                                                              |  |  |  |  |  |  |

| T4CK           | T4CKR                 | T4CKR<3:0>       | 0010 = RPB8<br>0011 = RPB15                                                             |  |  |  |  |  |  |

| IC2            | IC2R                  | IC2R<3:0>        | 0100 = RPD4<br>0101 = RPB0                                                              |  |  |  |  |  |  |

| IC5            | IC5R                  | IC5R<3:0>        | 0110 = RPE3<br>0111 = RPB7<br>1000 = Reserved                                           |  |  |  |  |  |  |

| <u>U1CTS</u>   | U1CTSR                | U1CTSR<3:0>      | 1000 = ROSCIVED<br>1001 = RPF12 <sup>(3)</sup><br>1010 = RPD12 <sup>(3)</sup>           |  |  |  |  |  |  |

| <u>U2CTS</u>   | U2CTSR                | U2CTSR<3:0>      | 1011 = RPF8 <sup>(3)</sup><br>1100 = RPC3 <sup>(3)</sup>                                |  |  |  |  |  |  |

| SS1            | SS1R                  | SS1R<3:0>        | 1101 = RPE9 <sup>(3)</sup><br>1110 = Reserved<br>1111 = RPB2                            |  |  |  |  |  |  |

Note 1: This selection is not available on 64-pin USB devices.

<sup>2:</sup> This selection is only available on 100-pin General Purpose devices.

<sup>3:</sup> This selection is not available on 64-pin USB and General Purpose devices.

<sup>4:</sup> This selection is only available on General Purpose devices.

| IABL | E 12-18: | PER | RIPHERAL PIN SELECT | OUTPUT | REGISTER MAP |

|------|----------|-----|---------------------|--------|--------------|

|      |          |     |                     |        |              |

| SS                          |                       |           |       |       |       |       |       |       |      | В    | its  |      |      |      |      |       |        |      |            |

|-----------------------------|-----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| FB38                        | RPA14R <sup>(1)</sup> | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    |       |        |      | 0000       |

| 1 030                       | KFA 14K**             | 15:0      |       | _     | _     | _     |       | _     | _    |      | _    |      | _    | _    |      | RPA14 | l<3:0> |      | 0000       |

| FB3C                        | RPA15R <sup>(1)</sup> | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1 550                       | KFA ISK.              | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPA15 | 5<3:0> |      | 0000       |

| FB40                        | RPB0R                 | 31:16     |       | _     | _     | _     |       | _     | _    |      | _    |      | _    | _    | _    | _     | _      | _    | 0000       |

| 1 540                       | KEBOK                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB0  | <3:0>  |      | 0000       |

| FB44                        | RPB1R                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | -     |        | -    | 0000       |

| 1 044                       | KEDIK                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB1  | <3:0>  |      | 0000       |

| FB48                        | RPB2R                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | -     |        | -    | 0000       |

| FB40                        | KFB2K                 | 15:0      | 1     | _     |       | _     | -     | _     | _    | -    | _    | -    | _    |      |      | RPB2  | <3:0>  |      | 0000       |

| FB4C                        | RPB3R                 | 31:16     | -     | _     | _     | _     | _     | _     | _    | -    | _    | _    | _    | _    | _    | ı     |        | -    | 0000       |

| FB4C                        | KFB3K                 | 15:0      |       | _     | _     | _     | _     | _     | _    |      | _    | _    | _    |      |      | RPB3  | <3:0>  |      | 0000       |

| FB54                        | RPB5R                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB34                        | KPBOK                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB5  | <3:0>  |      | 0000       |

| ED E O                      | DDDGD                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB58                        | RPB6R                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB6  | <3:0>  |      | 0000       |

| FB5C                        | RPB7R                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FBSC                        | RPB/R                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB7  | <3:0>  |      | 0000       |

| ED.CO                       | DDDOD                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB60                        | RPB8R                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB8  | <3:0>  |      | 0000       |

| EDC4                        | DDDOD                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB64                        | RPB9R                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB9  | <3:0>  |      | 0000       |

| ED.CO                       | DDD40D                | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB68                        | RPB10R                | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB10 | )<3:0> |      | 0000       |

|                             | 555445                | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB78                        | RPB14R                | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB14 | 1<3:0> |      | 0000       |

| ED70                        | DDD45D                | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB7C                        | RPB15R                | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB15 | 5<3:0> |      | 0000       |

|                             | DD0 (D(1)             | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB84                        | RPC1R <sup>(1)</sup>  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPC1  | <3:0>  |      | 0000       |

|                             | (4)                   | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB88                        | RPC2R <sup>(1)</sup>  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPC2  | <3:0>  |      | 0000       |

|                             | (4)                   | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB8C                        | RPC3R <sup>(1)</sup>  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPC3  | <3:0>  |      | 0000       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available on 64-pin devices.

<sup>2:</sup> This register is only available on devices without a USB module.

<sup>3:</sup> This register is not available on 64-pin devices with a USB module.

TABLE 31-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

| IABLE 31-7         | . 20                | 2117 1117   |         |                                                       | onditions: 2.3V to 3.6V (unless otherwise stated) |  |  |  |  |  |

|--------------------|---------------------|-------------|---------|-------------------------------------------------------|---------------------------------------------------|--|--|--|--|--|

| DC CHARAG          | CTERIST             | ics         |         |                                                       | 0°C ≤ TA ≤ +70°C for Commercial                   |  |  |  |  |  |

| DO GIMICAGI EMBIGO |                     |             |         | $-40^{\circ}$ C $\leq$ TA $\leq$ +85°C for Industrial |                                                   |  |  |  |  |  |

|                    |                     |             |         | -40°C ≤ TA ≤ +105°C for V-temp                        |                                                   |  |  |  |  |  |

| Param. No.         | Typ. <sup>(2)</sup> | Max.        | Units   | Conditions                                            |                                                   |  |  |  |  |  |

| PIC32MX330         | 0 Device            | s Only      |         |                                                       |                                                   |  |  |  |  |  |

| Power-Dow          | n Curren            | it (IPD) (N | lote 1) |                                                       |                                                   |  |  |  |  |  |

| DC40k              | 20                  | 55          | μΑ      | -40°C                                                 |                                                   |  |  |  |  |  |

| DC40I              | 38                  | 55          | μΑ      | +25°C                                                 | Base Power-Down Current                           |  |  |  |  |  |

| DC40n              | 128                 | 167         | μΑ      | +85°C                                                 | Dase Fower-Down Current                           |  |  |  |  |  |

| DC40m              | 261                 | 419         | μA      | +105°C                                                |                                                   |  |  |  |  |  |

| PIC32MX43          | 0 Device            | s Only      |         |                                                       |                                                   |  |  |  |  |  |

| Power-Dow          | n Currer            | it (IPD) (N | lote 1) |                                                       |                                                   |  |  |  |  |  |

| DC40k              | 12                  | 28          | μА      | -40°C                                                 |                                                   |  |  |  |  |  |

| DC40I              | 21                  | 28          | μΑ      | +25°C                                                 | Base Power-Down Current                           |  |  |  |  |  |

| DC40n              | 128                 | 167         | μΑ      | +85°C                                                 | Dase i owei-bown current                          |  |  |  |  |  |

| DC40m              | 261                 | 419         | μA      | +105°C                                                |                                                   |  |  |  |  |  |

| PIC32MX35          | 0F128 D             | evices O    | nly     |                                                       |                                                   |  |  |  |  |  |

| Power-Dow          | n Currer            | it (IPD) (N | lote 1) |                                                       |                                                   |  |  |  |  |  |

| DC40k              | 31                  | 70          | μА      | -40°C                                                 |                                                   |  |  |  |  |  |

| DC40I              | 45                  | 70          | μΑ      | +25°C                                                 | Base Power-Down Current                           |  |  |  |  |  |

| DC40n              | 175                 | 280         | μΑ      | +85°C                                                 | Dase Fower-Down Current                           |  |  |  |  |  |

| DC40m              | 415                 | 600         | μA      | +105°C                                                |                                                   |  |  |  |  |  |

| PIC32MX45          | 0F128 D             | evices O    | nly     | •                                                     | •                                                 |  |  |  |  |  |

| Power-Dow          | n Curren            | it (IPD) (N | lote 1) |                                                       |                                                   |  |  |  |  |  |

| DC40k              | 19                  | 35          | μА      | -40°C                                                 |                                                   |  |  |  |  |  |

| DC40I              | 28                  | 35          | μΑ      | +25°C                                                 | Base Power-Down Current                           |  |  |  |  |  |

| DC40n              | 175                 | 280         | μΑ      | +85°C                                                 | Dase Fower-Down Current                           |  |  |  |  |  |

| DC40m              | 415                 | 600         | μA      | +105°C                                                |                                                   |  |  |  |  |  |

|                    |                     |             |         |                                                       |                                                   |  |  |  |  |  |

Note 1: The test conditions for IPD measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Sleep mode, program Flash memory Wait states = 7, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is set

- · WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- Voltage regulator is off during Sleep mode (VREGS bit in the RCON register = 0)

- 2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The  $\Delta$  current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- 4: Test conditions for ADC module differential current are as follows: Internal ADC RC oscillator enabled.

- 5: 120 MHz commercial devices only (0°C to +70°C).

#### TABLE 31-19: PLL CLOCK TIMING SPECIFICATIONS

|                    | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) |                                             |  |  |

|--------------------|-----------------------------------------------------------------------|---------------------------------------------|--|--|

| AC CHARACTERISTICS | Operating temperature                                                 | 0°C ≤ TA ≤ +70°C for Commercial             |  |  |

|                    |                                                                       | -40°C ≤ TA ≤ +85°C for Industrial           |  |  |

|                    |                                                                       | $-40$ °C $\leq$ TA $\leq$ +105°C for V-temp |  |  |

| Param.<br>No. | Symbol | Characteristics <sup>(1)</sup>                                      | Min.  | Typical | Max.  | Units | Conditions                        |

|---------------|--------|---------------------------------------------------------------------|-------|---------|-------|-------|-----------------------------------|

| OS50          | FPLLI  | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range | 3.92  | _       | 5     | MHz   | ECPLL, HSPLL, XTPLL, FRCPLL modes |

| OS51a         | Fsys   | On-Chip VCO System Frequency                                        | 60    | _       | 120   | MHz   | Commercial devices                |

| OS51b         |        |                                                                     | 60    | _       | 100   | MHz   | Industrial devices                |

| OS51c         |        |                                                                     | 60    | _       | 80    | MHz   | V-temp devices                    |

| OS52          | TLOCK  | PLL Start-up Time (Lock Time)                                       | _     | _       | 2     | ms    | _                                 |

| OS53          | DCLK   | CLKO Stability <sup>(2)</sup> (Period Jitter or Cumulative)         | -0.25 | _       | +0.25 | %     | Measured over 100 ms period       |

- Note 1: These parameters are characterized, but not tested in manufacturing.

- **2:** This jitter specification is based on clock-cycle by clock-cycle measurements. To get the effective jitter for individual time-bases on communication clocks, use the following formula:

$$Effective Jitter = \frac{D_{CLK}}{\sqrt{\frac{SYSCLK}{Communication Clock}}}$$

For example, if SYSCLK = 40 MHz and SPI bit rate = 20 MHz, the effective jitter is as follows:

$$Effective Jitter = \frac{D_{CLK}}{\sqrt{\frac{40}{20}}} = \frac{D_{CLK}}{1.41}$$

#### **TABLE 31-20: INTERNAL FRC ACCURACY**

| AC CHARACTERISTICS                              |                                                              | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |   |      |            |   |  |  |

|-------------------------------------------------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|------|------------|---|--|--|

| Param.<br>No.                                   | Characteristics   Min.   Typical   Max.   Units   Conditions |                                                                                                                                                                                                                                                          |   |      | Conditions |   |  |  |

| Internal FRC Accuracy @ 8.00 MHz <sup>(1)</sup> |                                                              |                                                                                                                                                                                                                                                          |   |      |            |   |  |  |

| F20b                                            | FRC                                                          | -0.9                                                                                                                                                                                                                                                     | _ | +0.9 | %          | _ |  |  |

Note 1: Frequency calibrated at 25°C and 3.3V. The TUN bits can be used to compensate for temperature drift.

TABLE 31-42: CTMU CURRENT SOURCE SPECIFICATIONS

| DC CHARACTERISTICS |           |                                                    | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |       |       |            |                                   |  |

|--------------------|-----------|----------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|------------|-----------------------------------|--|

| Param<br>No.       | Symbol    | Min.                                               | Тур.                                                                                                                                                                                                                                                     | Max.  | Units | Conditions |                                   |  |

| CTMU CUR           | RENT SOUR | CE                                                 |                                                                                                                                                                                                                                                          |       |       |            |                                   |  |

| CTMUI1             | IOUT1     | Base Range <sup>(1)</sup>                          | _                                                                                                                                                                                                                                                        | 0.55  | _     | μA         | CTMUICON<9:8> = 01                |  |

| CTMUI2             | IOUT2     | 10x Range <sup>(1)</sup>                           | _                                                                                                                                                                                                                                                        | 5.5   | _     | μA         | CTMUICON<9:8> = 10                |  |

| CTMUI3             | Іоит3     | 100x Range <sup>(1)</sup>                          |                                                                                                                                                                                                                                                          | 55    |       | μA         | CTMUICON<9:8> = 11                |  |

| CTMUI4             | Iout4     | 1000x Range <sup>(1)</sup>                         | _                                                                                                                                                                                                                                                        | 550   | _     | μA         | CTMUICON<9:8> = 00                |  |

| CTMUFV1            | VF        | Temperature Diode Forward Voltage <sup>(1,2)</sup> | _                                                                                                                                                                                                                                                        | 0.598 | _     | V          | TA = +25°C,<br>CTMUICON<9:8> = 01 |  |

|                    |           |                                                    | _                                                                                                                                                                                                                                                        | 0.658 | _     | V          | TA = +25°C,<br>CTMUICON<9:8> = 10 |  |

|                    |           |                                                    | _                                                                                                                                                                                                                                                        | 0.721 | _     | V          | TA = +25°C,<br>CTMUICON<9:8> = 11 |  |

| CTMUFV2            | VFVR      | Temperature Diode Rate of                          |                                                                                                                                                                                                                                                          | -1.92 | _     | mV/°C      | CTMUICON<9:8> = 01                |  |

|                    |           | Change <sup>(1,2)</sup>                            |                                                                                                                                                                                                                                                          | -1.74 | _     | mV/ºC      | CTMUICON<9:8> = 10                |  |

|                    |           |                                                    | _                                                                                                                                                                                                                                                        | -1.56 | _     | mV/°C      | CTMUICON<9:8> = 11                |  |

Note 1: Nominal value at center point of current trim range (CTMUICON<15:10> = 000000).

- **2:** Parameters are characterized but not tested in manufacturing. Measurements taken with the following conditions:

- VREF+ = AVDD = 3.3V

- · ADC module configured for conversion speed of 500 ksps

- All PMD bits are cleared (PMDx = 0)

- Executing a while(1) statement

- · Device operating from the FRC with no PLL

| PIC32MX | PIC32MX330/350/370/430/450/470 |  |  |  |  |  |

|---------|--------------------------------|--|--|--|--|--|

| NOTES:  |                                |  |  |  |  |  |

|         |                                |  |  |  |  |  |

|         |                                |  |  |  |  |  |

|         |                                |  |  |  |  |  |

|         |                                |  |  |  |  |  |

|         |                                |  |  |  |  |  |

|         |                                |  |  |  |  |  |

|         |                                |  |  |  |  |  |

|         |                                |  |  |  |  |  |

|         |                                |  |  |  |  |  |

|         |                                |  |  |  |  |  |

|         |                                |  |  |  |  |  |

|         |                                |  |  |  |  |  |

|         |                                |  |  |  |  |  |

|         |                                |  |  |  |  |  |

|         |                                |  |  |  |  |  |

|         |                                |  |  |  |  |  |

|         |                                |  |  |  |  |  |

|         |                                |  |  |  |  |  |

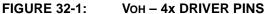

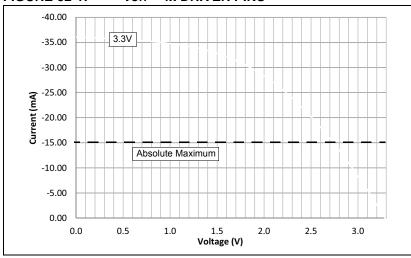

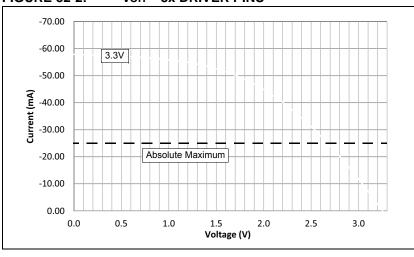

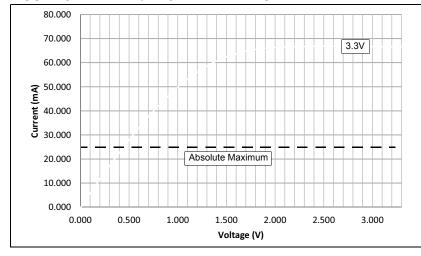

#### 32.0 DC AND AC DEVICE CHARACTERISTICS GRAPHS

**Note:** The graphs provided following this note are a statistical summary based on a limited number of samples and are provided for design guidance purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

FIGURE 32-3: Vol – 4x DRIVER PINS

FIGURE 32-2: VoH – 8x DRIVER PINS

FIGURE 32-4: Vol – 8x DRIVER PINS

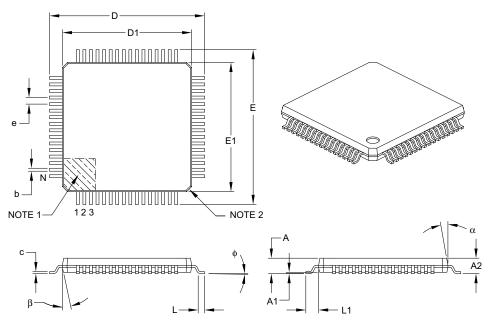

## 33.2 Package Details

The following sections give the technical details of the packages.

## 64-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units |            |           | MILLIMETERS |  |  |  |

|--------------------------|-------|------------|-----------|-------------|--|--|--|

| Dime                     | MIN   | NOM        | MAX       |             |  |  |  |

| Number of Leads          | N     | 64         |           |             |  |  |  |

| Lead Pitch               | е     |            | 0.50 BSC  |             |  |  |  |

| Overall Height           | А     | -          | _         | 1.20        |  |  |  |

| Molded Package Thickness | A2    | 0.95       | 1.00      | 1.05        |  |  |  |

| Standoff                 | A1    | 0.05       | _         | 0.15        |  |  |  |

| Foot Length              | L     | 0.45       | 0.60      | 0.75        |  |  |  |

| Footprint                | L1    | 1.00 REF   |           |             |  |  |  |

| Foot Angle               | ф     | 0° 3.5° 7° |           |             |  |  |  |

| Overall Width            | E     |            | 12.00 BSC |             |  |  |  |

| Overall Length           | D     |            | 12.00 BSC |             |  |  |  |

| Molded Package Width     | E1    | 10.00 BSC  |           |             |  |  |  |

| Molded Package Length    | D1    | 10.00 BSC  |           |             |  |  |  |

| Lead Thickness           | С     | 0.09       | _         | 0.20        |  |  |  |

| Lead Width               | b     | 0.17       | 0.22      | 0.27        |  |  |  |

| Mold Draft Angle Top     | α     | 11°        | 12°       | 13°         |  |  |  |

| Mold Draft Angle Bottom  | β     | 11°        | 12°       | 13°         |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085B

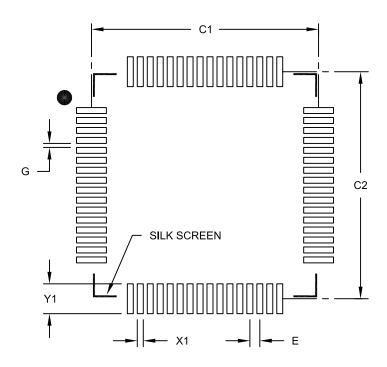

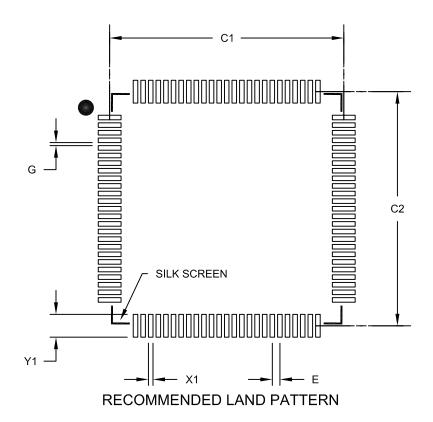

64-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**ote:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                          | MILLIMETERS |          |       |      |

|--------------------------|-------------|----------|-------|------|

| Dimension                | MIN         | NOM      | MAX   |      |

| Contact Pitch            | E           | 0.50 BSC |       |      |

| Contact Pad Spacing      | C1          |          | 11.40 |      |

| Contact Pad Spacing      | C2          |          | 11.40 |      |

| Contact Pad Width (X64)  | X1          |          |       | 0.30 |

| Contact Pad Length (X64) | Y1          |          |       | 1.50 |

| Distance Between Pads    | G           | 0.20     |       |      |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2085B

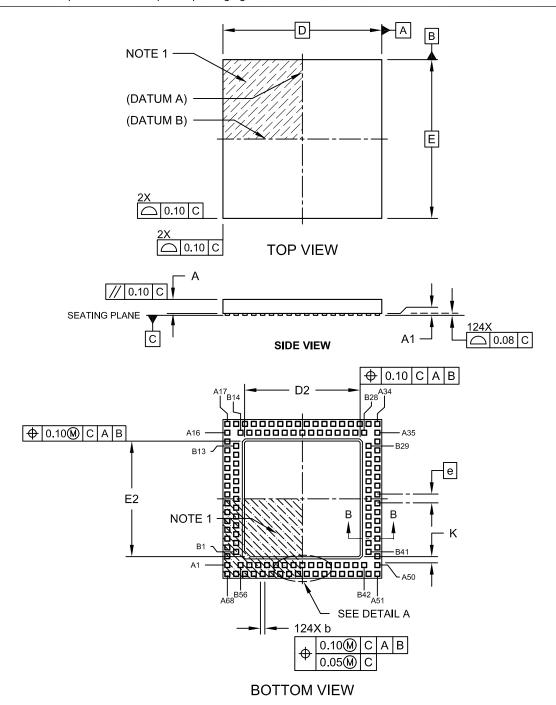

100-Lead Plastic Thin Quad Flatpack (PF) - 14x14x1 mm Body 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | MILLIMETERS |          |       |      |

|---------------------------|-------------|----------|-------|------|

| Dimension                 | MIN         | NOM      | MAX   |      |

| Contact Pitch             |             | 0.50 BSC |       |      |

| Contact Pad Spacing       | C1          |          | 15.40 |      |

| Contact Pad Spacing       | C2          |          | 15.40 |      |

| Contact Pad Width (X100)  | X1          |          |       | 0.30 |

| Contact Pad Length (X100) | Y1          |          |       | 1.50 |

| Distance Between Pads     | G           | 0.20     |       |      |

## Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2110B

## 124-Terminal Very Thin Leadless Array Package (TL) – 9x9x0.9 mm Body [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-193A Sheet 1 of 2

NOTES: