Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

|                            |                                                                                |

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx350f128l-v-pt |

#### REGISTER 4-1: BMXCON: BUS MATRIX CONFIGURATION REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

|              | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-1             | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | BMX<br>CHEDMA     | _                | _                |

|              | U-0               | U-0               | U-0               | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |

| 23:16        | _                 | _                 | _                 | BMX<br>ERRIXI     | BMX<br>ERRICD     | BMX<br>ERRDMA     | BMX<br>ERRDS     | BMX<br>ERRIS     |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

|              | U-0               | R/W-1             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-1            |

| 7:0          | _                 | BMX<br>WSDRM      | _                 | _                 | _                 | E                 | BMXARB<2:0       | >                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared

bit 31-27 Unimplemented: Read as '0'

bit 26 BMXCHEDMA: BMX PFM Cacheability for DMA Accesses bit

1 = Enable program Flash memory (data) cacheability for DMA accesses (requires cache to have data caching enabled)

0 = Disable program Flash memory (data) cacheability for DMA accesses (hits are still read from the cache, but misses do not update the cache)

bit 25-21 Unimplemented: Read as '0'

bit 20 BMXERRIXI: Enable Bus Error from IXI bit

1 = Enable bus error exceptions for unmapped address accesses initiated from IXI shared bus

0 = Disable bus error exceptions for unmapped address accesses initiated from IXI shared bus

bit 19 BMXERRICD: Enable Bus Error from ICD Debug Unit bit

1 = Enable bus error exceptions for unmapped address accesses initiated from ICD

0 = Disable bus error exceptions for unmapped address accesses initiated from ICD

bit 18 BMXERRDMA: Bus Error from DMA bit

1 = Enable bus error exceptions for unmapped address accesses initiated from DMA

0 = Disable bus error exceptions for unmapped address accesses initiated from DMA

bit 17 BMXERRDS: Bus Error from CPU Data Access bit (disabled in Debug mode)

1 = Enable bus error exceptions for unmapped address accesses initiated from CPU data access

0 = Disable bus error exceptions for unmapped address accesses initiated from CPU data access

bit 16 **BMXERRIS:** Bus Error from CPU Instruction Access bit (disabled in Debug mode)

1 = Enable bus error exceptions for unmapped address accesses initiated from CPU instruction access

0 = Disable bus error exceptions for unmapped address accesses initiated from CPU instruction access

bit 15-7 Unimplemented: Read as '0'

bit 6 BMXWSDRM: CPU Instruction or Data Access from Data RAM Wait State bit

1 = Data RAM accesses from CPU have one wait state for address setup

0 = Data RAM accesses from CPU have zero wait states for address setup

bit 5-3 Unimplemented: Read as '0'

bit 2-0 **BMXARB<2:0>:** Bus Matrix Arbitration Mode bits

111 = Reserved (using these configuration modes will produce undefined behavior)

:

011 = Reserved (using these configuration modes will produce undefined behavior)

010 = Arbitration Mode 2

001 = Arbitration Mode 1 (default)

000 = Arbitration Mode 0

#### REGISTER 7-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        | _                 | _                 | _                 |                   | IP3<2:0>          |                   | IS3<             | :1:0>            |

| 22:16        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | _                 | _                 | _                 |                   | IP2<2:0>          |                   | IS2<             | :1:0>            |

| 15.0         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | IP1<2:0>          |                   |                   | IS1<              | :1:0>             |                  |                  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 |                   | IP0<2:0>          |                   | IS0<             | 1:0>             |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-29 Unimplemented: Read as '0'

bit 28-26 IP3<2:0>: Interrupt Priority bits

111 = Interrupt priority is 7

•

010 = Interrupt priority is 2

001 = Interrupt priority is 1

000 = Interrupt is disabled

bit 25-24 IS3<1:0>: Interrupt Subpriority bits

11 = Interrupt subpriority is 3

10 = Interrupt subpriority is 2

01 = Interrupt subpriority is 1

00 = Interrupt subpriority is 0

bit 23-21 Unimplemented: Read as '0'

bit 20-18 IP2<2:0>: Interrupt Priority bits

111 = Interrupt priority is 7

.

010 = Interrupt priority is 2

001 = Interrupt priority is 1

000 = Interrupt is disabled

bit 17-16 IS2<1:0>: Interrupt Subpriority bits

11 = Interrupt subpriority is 3

10 = Interrupt subpriority is 2

01 = Interrupt subpriority is 1

00 = Interrupt subpriority is 0

bit 15-13 Unimplemented: Read as '0'

bit 12-10 IP1<2:0>: Interrupt Priority bits

111 = Interrupt priority is 7

•

,

010 = Interrupt priority is 2

001 = Interrupt priority is 1

000 = Interrupt is disabled

**Note:** This register represents a generic definition of the IPCx register. Refer to Table 7-1 for the exact bit definitions.

#### **REGISTER 8-1:** OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

**UFRCEN:** USB FRC Clock Enable bit<sup>(1)</sup> bit 2

1 = Enable FRC as the clock source for the USB clock source

0 = Use the Primary Oscillator or USB PLL as the USB clock source

bit 1 SOSCEN: Secondary Oscillator (Sosc) Enable bit

1 = Enable Secondary Oscillator

0 = Disable Secondary Oscillator

bit 0 **OSWEN:** Oscillator Switch Enable bit

Note:

1 = Initiate an oscillator switch to selection specified by NOSC<2:0> bits

0 = Oscillator switch is complete

Note 1: This bit is available on PIC32MX4XX devices only.

Writes to this register require an unlock sequence. Refer to Section 6. "Oscillator" (DS60001112) in the

"PIC32 Family Reference Manual" for details.

REGISTER 10-1: DMACON: DMA CONTROLLER CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                      | _                 | _                | _                |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                      | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0                  | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | _                 | _                 | SUSPEND           | DMABUSY <sup>(1)</sup> | _                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 | _                 | _                 | _                      | _                 | _                | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 ON: DMA On bit<sup>(1)</sup>

1 = DMA module is enabled0 = DMA module is disabled

bit 14-13 **Unimplemented:** Read as '0' bit 12 **SUSPEND:** DMA Suspend bit

1 = DMA transfers are suspended to allow CPU uninterrupted access to data bus

0 = DMA operates normally

bit 11 **DMABUSY:** DMA Module Busy bit<sup>(1)</sup>

1 = DMA module is active

0 = DMA module is disabled and not actively transferring data

bit 10-0 Unimplemented: Read as '0'

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 10-9: DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | 1                 | _                 | _                 | -                 | _                 | _                 | _                | _                |

| 22.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | CHSDIE            | CHSHIE            | CHDDIE            | CHDHIE            | CHBCIE            | CHCCIE            | CHTAIE           | CHERIE           |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CHSDIF            | CHSHIF            | CHDDIF            | CHDHIF            | CHBCIF            | CHCCIF            | CHTAIF           | CHERIF           |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-24 Unimplemented: Read as '0'

bit 23 CHSDIE: Channel Source Done Interrupt Enable bit

1 = Interrupt is enabled

0 = Interrupt is disabled

bit 22 CHSHIE: Channel Source Half Empty Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 21 CHDDIE: Channel Destination Done Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 20 **CHDHIE:** Channel Destination Half Full Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 19 CHBCIE: Channel Block Transfer Complete Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 18 CHCCIE: Channel Cell Transfer Complete Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 17 CHTAIE: Channel Transfer Abort Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 16 CHERIE: Channel Address Error Interrupt Enable bit

1 = Interrupt is enabled0 = Interrupt is disabled

bit 15-8 Unimplemented: Read as '0'

bit 7 CHSDIF: Channel Source Done Interrupt Flag bit

1 = Channel Source Pointer has reached end of source (CHSPTR = CHSSIZ)

0 = No interrupt is pending

bit 6 CHSHIF: Channel Source Half Empty Interrupt Flag bit

1 = Channel Source Pointer has reached midpoint of source (CHSPTR = CHSSIZ/2)

0 = No interrupt is pending

bit 5 **CHDDIF:** Channel Destination Done Interrupt Flag bit

1 = Channel Destination Pointer has reached end of destination (CHDPTR = CHDSIZ)

0 = No interrupt is pending

TABLE 12-6: PORTC REGISTER MAP FOR PIC32MX330F064H, PIC32MX350F128H, PIC32MX350F256H, PIC32MX370F512H, PIC32MX430F064H, PIC32MX450F128H, PIC32MX450F256H, AND PIC32MX470F512H DEVICES ONLY

| ess                         |                                 | •         |           |           |           |           |       |       |      | Bits |      |      |      |      |      |      |      |      |               |

|-----------------------------|---------------------------------|-----------|-----------|-----------|-----------|-----------|-------|-------|------|------|------|------|------|------|------|------|------|------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15     | 30/14     | 29/13     | 28/12     | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All<br>Resets |

| 6210                        | TRISC                           | 31:16     | _         | 1         |           | 1         | 1     | _     | -    | -    | _    | _    | 1    |      | _    | _    | -    | I    | 0000          |

| 0210                        | 111100                          | 15:0      | TRISC15   | TRISC14   | TRISC13   | TRISC12   | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _    | _    | xxxx          |

| 6220                        | PORTC                           | 31:16     | _         | _         | _         | _         |       | _     | _    | _    | _    | _    |      | _    | _    | _    | _    | _    | 0000          |

| OLLO                        | 1 01110                         | 15:0      | RC15      | RC14      | RC13      | RC12      | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _    | _    | xxxx          |

| 6230                        | LATC                            | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _    | _    | 0000          |

| 0200                        | Dilo                            | 15:0      | LATC15    | LATC14    | LATC13    | LATC12    | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _    | _    | xxxx          |

| 6240                        | ODCC                            | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _    | _    | 0000          |

| 02.10                       | 0500                            | 15:0      | ODCC15    | ODCC14    | ODCC13    | ODCC12    | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _    | _    | xxxx          |

| 6250                        | CNPUC                           | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _    | _    | 0000          |

| 0200                        | 0111 00                         | 15:0      | CNPUC15   | CNPUC14   | CNPUC13   | CNPUC12   | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _    | _    | xxxx          |

| 6260                        | CNPDC                           | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _    | _    | 0000          |

| 0200                        | ON DO                           | 15:0      | CNPDC15   | CNPDC14   | CNPDC13   | CNPDC12   | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _    | _    | xxxx          |

| 6270                        | CNCONC                          | 31:16     | _         | _         | _         | _         | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _    | _    | 0000          |

| 0270                        | ONOONO                          | 15:0      | ON        | _         | SIDL      | _         | _     | _     | _    | _    | _    | _    | _    | _    | _    | _    | _    | _    | 0000          |

| 6280                        | CNENC                           | 31:16     | _         | _         |           | _         | _     | _     |      |      | _    | _    | _    |      | _    | _    |      |      | 0000          |

| 0200                        | CIVEIVO                         | 15:0      | CNIEC15   | CNIEC14   | CNIEC13   | CNIEC12   | _     | _     |      |      | _    | _    | _    |      | _    | _    |      |      | xxxx          |

| 6200                        | CNSTATC                         | 31:16     | _         |           | -         |           | I     | _     | -    | -    | _    | _    | 1    | -    | _    | _    | -    | ı    | 0000          |

| 0290                        | CINCIAIC                        | 15:0      | CNSTATC15 | CNSTATC14 | CNSTATC13 | CNSTATC12 | I     | _     |      | -    | _    | _    | I    | -    | _    | _    | -    |      | xxxx          |

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

TABLE 12-8: PORTD REGISTER MAP FOR PIC32MX330F064H, PIC32MX350F128H, PIC32MX350F256H, PIC32MX370F512H, PIC32MX430F064H, PIC32MX450F128H, PIC32MX450F256H, PIC32MX470F512H DEVICES ONLY

| SS                          |                                 |           |       |       |       |       |               |               |              | В            | its          |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|---------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11         | 26/10         | 25/9         | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6300                        | ANSELD                          | 31:16     | _     | _     | _     | _     | _             | _             | _            |              | _            | _            | _            | _            | _            | _            | _            |              | 0000          |

|                             | 7 11 10 2 2 2                   | 15:0      | _     | _     | _     | _     | _             | _             | _            | _            | _            | _            | _            | _            | ANSELD3      | ANSELD2      | ANSELD1      | _            | 000E          |

| 6310                        | TRISD                           | 31:16     |       |       |       |       |               |               |              |              |              |              |              |              |              |              |              |              | 0000          |

|                             |                                 | 15:0      |       |       |       |       | TRISD11       | TRISD10       | TRISD9       | TRISD8       | TRISD7       | TRISD6       | TRISD5       | TRISD4       | TRISD3       | TRISD2       | TRISD1       | TRISD0       | XXXX          |

| 5320                        | PORTD                           | 31:16     |       |       |       |       |               |               |              |              |              |              |              |              |              |              |              |              | 0000          |

|                             |                                 | 15:0      |       |       |       |       | RD11          | RD10          | RD9          | RD8          | RD7          | RD6          | RD5          | RD4          | RD3          | RD2          | RD1          | RD0          | XXXX          |

| 6330                        | LATD                            | 31:16     |       |       |       |       |               |               |              |              |              |              |              |              |              |              |              |              | 0000          |

|                             |                                 | 15:0      |       |       |       |       | LATD11        | LATD10        | LATD9        | LATD8        | LATD7        | LATD6        | LATD5        | LATD4        | LATD3        | LATD2        | LATD1        | LATD0        | XXXX          |

| 6340                        | ODCD                            | 31:16     | _     | _     | _     |       |               |               |              |              |              |              | _            |              |              | _            | _            |              | 0000          |

|                             |                                 | 15:0      | _     | _     | _     |       | ODCD11        | ODCD10        | ODCD9        | ODCD8        | ODCD7        | ODCD6        | ODCD5        | ODCD4        | ODCD3        | ODCD2        | ODCD1        | ODCD0        | XXXX          |

| 6350                        | CNPUD                           | 31:16     | _     | _     | _     |       |               |               |              |              |              |              |              |              |              |              |              |              | 0000          |

|                             |                                 | 15:0      | _     | _     | _     |       | CNPUD11       | CNPUD10       | CNPUD9       | CNPUD8       | CNPUD7       | CNPUD6       | CNPUD5       | CNPUD4       | CNPUD3       | CNPUD2       | CNPUD1       | CNPUD0       | XXXX          |

| 6360                        | CNPDD                           | 31:16     | _     | _     | _     |       | _             | _             | _            | _            |              | _            | _            | _            | _            | _            | _            | _            | 0000          |

|                             | _                               | 15:0      | _     | _     | _     |       | CNPDD11       | CNPDD10       | CNPDD9       | CNPDD8       | CNPDD7       | CNPDD6       | CNPDD5       | CNPDD4       | CNPDD3       | CNPDD2       | CNPDD1       | CNPDD0       | xxxx          |

| 6370                        | CNCOND                          | 31:16     | _     | _     | _     |       | _             | _             |              | _            |              | _            | _            |              |              |              |              |              | 0000          |

|                             |                                 | 15:0      | ON    | _     | SIDL  |       | _             | _             |              |              |              | _            |              |              |              |              |              |              | 0000          |

| 6380                        | CNEND                           | 31:16     | _     | _     | _     |       | _             | _             | _            | _            |              | _            | _            |              | _            | _            | _            |              | 0000          |

|                             | 0.12.12                         | 15:0      | _     | _     | _     |       | CNIED11       | CNIED10       | CNIED9       | CNIED8       | CNIED7       | CNIED6       | CNIED5       | CNIED4       | CNIED3       | CNIED2       | CNIED1       | CNIED0       | xxxx          |

|                             |                                 | 31:16     | _     | _     | _     | _     | _             | _             | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 6390                        | CNSTATD                         | 15:0      | _     | _     | _     | _     | CN<br>STATD11 | CN<br>STATD10 | CN<br>STATD9 | CN<br>STATD8 | CN<br>STATD7 | CN<br>STATD6 | CN<br>STATD5 | CN<br>STATD4 | CN<br>STATD3 | CN<br>STATD2 | CN<br>STATD1 | CN<br>STATD0 | xxxx          |

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for

TABLE 12-13: PORTF REGISTER MAP FOR PIC32MX330F064H, PIC32MX350F128H, PIC32MX350F256H, AND PIC32MX370F512H DEVICES ONLY

| ess                         |                                 |           |       |       |       |       |       |       |      | Ві   | ts   |        |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|--------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6   | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6510                        | TRISF                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _      | _            | _            | _            | _            | _            | _            | 0000          |

|                             |                                 | 15:0      | _     | _     | _     |       | _     | _     |      |      |      | TRISF6 | TRISF5       | TRISF4       | TRISF3       | TRISF2       | TRISF1       | TRISF0       | xxxx          |

| 6520                        | PORTF                           | 31:16     | _     |       | _     |       | _     | _     |      |      |      | _      | _            | _            | _            | _            | _            | _            | 0000          |

|                             |                                 | 15:0      | _     | _     | _     | _     | _     | _     |      | -    | _    | RF6    | RF5          | RF4          | RF3          | RF2          | RF1          | RF0          | XXXX          |

| 6530                        | LATF                            | 31:16     | _     | _     | _     | _     | _     | _     | -    | -    | _    | _      | _            | _            | _            | _            | _            | _            | 0000          |

| 0000                        |                                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | LATF6  | LATF5        | LATF4        | LATF3        | LATF2        | LATF1        | LATF0        | xxxx          |

| 6540                        | ODCF                            | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _      | _            | _            | _            | _            | _            | _            | 0000          |

| 0040                        | ODOI                            | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | ODCF6  | ODCF5        | ODCF4        | ODCF3        | ODCF2        | ODCF1        | ODCF0        | xxxx          |

| 6550                        | CNPUF                           | 31:16     | _     | _     | _     | _     | _     | _     | -    | -    | _    | _      | _            | _            | _            | _            | _            | _            | 0000          |

| 0000                        | CIVI OI                         | 15:0      | _     | _     | _     | _     | _     | _     | -    | 1    | _    | CNPUF6 | CNPUF5       | CNPUF4       | CNPUF3       | CNPUF2       | CNPUF1       | CNPUF0       | xxxx          |

| 6560                        | CNPDF                           | 31:16     | _     |       | _     | -     | _     | _     | ı    | I    | _    | _      | _            |              | 1            | _            | _            | I            | 0000          |

| 0300                        | CINFDI                          | 15:0      | _     |       | _     | _     | _     |       |      |      | _    | CNPDF6 | CNPDF5       | CNPDF4       | CNPDF3       | CNPDF2       | CNPDF1       | CNPDF0       | xxxx          |

| 6570                        | CNCONF                          | 31:16     | 1     |       | _     | _     | _     | _     | _    | _    | _    | _      | _            | _            | _            | _            | _            | _            | 0000          |

| 0370                        | CNCONF                          | 15:0      | ON    |       | SIDL  | _     | _     | _     | _    | _    | _    | _      | _            | _            | _            | _            | _            | _            | 0000          |

| 6580                        | CNENF                           | 31:16     | _     | 1     | _     | _     | _     | _     | _    | _    | _    | _      | _            | _            | _            | _            | _            | _            | 0000          |

| 0000                        | CNENF                           | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _      | CNIEF5       | CNIEF4       | CNIEF3       | CNIEF2       | CNIEF1       | CNIEF0       | xxxx          |

|                             |                                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _      | _            | _            | _            | _            | _            | _            | 0000          |

| 6590                        | CNSTATF                         | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _      | CN<br>STATF5 | CN<br>STATF4 | CN<br>STATF3 | CN<br>STATF2 | CN<br>STATF1 | CN<br>STATF0 | xxxx          |

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

TABLE 12-16: PORTG REGISTER MAP FOR PIC32MX330F064H, PIC32MX350F128H, PIC32MX350F256H, PIC32MX370F512H, PIC32MX430F064H, PIC32MX450F128H, PIC32MX450F256H, AND PIC32MX470F512H DEVICES ONLY

| ess                         |                                 |           |       |       |       |       |       |       |              | Ві           | ts           |              |      |      |                    |                    |      |      |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|--------------|--------------|--------------|--------------|------|------|--------------------|--------------------|------|------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9         | 24/8         | 23/7         | 22/6         | 21/5 | 20/4 | 19/3               | 18/2               | 17/1 | 16/0 | All<br>Resets |

| 6600                        | ANSELG                          | 31:16     |       | _     | _     | _     | _     |       | _            | _            | -            | _            | _    | _    | _                  | _                  | _    | _    | 0000          |

| 0000                        | 7.1.0220                        | 15:0      | _     | _     | _     | _     | _     | _     | ANSELG9      | ANSELG8      | ANSELG7      | ANSELG6      | _    | _    | _                  | _                  | _    | _    | 01C0          |

| 6610                        | TRISG                           | 31:16     | _     | _     | _     | _     | _     | _     | _            | _            | _            | _            | _    | _    | _                  | _                  | _    | _    | 0000          |

| 0010                        | 111100                          | 15:0      | _     | _     | _     | _     | _     | _     | TRISG9       | TRISG8       | TRISG7       | TRISG6       | _    | _    | TRISG3             | TRISG2             | _    | _    | xxxx          |

| 6620                        | PORTG                           | 31:16     | _     | _     | _     | _     | _     | _     | _            | _            | _            | _            | _    | _    |                    | _                  | _    | _    | 0000          |

| 0020                        | 1 01110                         | 15:0      | _     | _     | _     | _     | _     | _     | RG9          | RG8          | RG7          | RG6          |      | _    | RG3 <sup>(2)</sup> | RG2 <sup>(2)</sup> |      | _    | xxxx          |

| 6630                        | LATG                            | 31:16     | _     | _     | _     | _     | _     | _     | _            | _            | _            | _            |      | _    | _                  | _                  |      | _    | 0000          |

| 0000                        | Litto                           | 15:0      | _     | _     | _     | _     | _     | _     | LATG9        | LATG8        | LATG7        | LATG6        |      | _    | LATG3              | LATG2              |      | _    | xxxx          |

| 6640                        | ODCG                            | 31:16     | _     | _     | _     | _     | _     | _     | _            | _            | _            | _            |      | _    | _                  | _                  |      | _    | 0000          |

| 00+0                        | ОВСО                            | 15:0      | _     | _     | _     | _     | _     | -     | ODCG9        | ODCG8        | ODCG7        | ODCG6        | _    | _    | ODCG3              | ODCG2              | _    | _    | xxxx          |

| 6650                        | CNPUG                           | 31:16     | _     | _     | _     | _     | _     | -     | _            | _            | _            | _            | _    | _    | _                  | _                  | _    | _    | 0000          |

| 0000                        | CIVI OC                         | 15:0      | _     | _     | _     | _     | _     | -     | CNPUG9       | CNPUG8       | CNPUG7       | CNPUG6       | _    | _    | CNPUG3             | CNPUG2             | _    | _    | xxxx          |

| 6660                        | CNPDG                           | 31:16     | _     | _     | _     | _     | _     | -     | _            | _            | _            | _            | _    | _    | _                  | _                  | _    | _    | 0000          |

| 0000                        | CIVI DO                         | 15:0      | _     | _     | _     | _     | _     | -     | CNPDG9       | CNPDG8       | CNPDG7       | CNPDG6       | _    | _    | CNPDG3             | CNPDG2             | _    | _    | xxxx          |

| 6670                        | CNCONG                          | 31:16     | _     | _     | _     | _     | _     | -     | _            | _            | _            | _            | _    | _    | _                  | _                  | _    | _    | 0000          |

| 0070                        | CINCOING                        | 15:0      | ON    | _     | SIDL  | _     | _     | -     | _            | _            | _            | _            | _    | _    | _                  | _                  | _    | _    | 0000          |

| 6680                        | CNENG                           | 31:16     | _     | _     | _     | _     | _     | -     | _            | _            | _            | _            | _    | _    | _                  | _                  | _    | _    | 0000          |

| 0000                        | CINLING                         | 15:0      | _     | 1     | -     | -     | _     | 1     | CNIEG9       | CNIEG8       | CNIEG7       | CNIEG6       | _    | _    | CNIEG3             | CNIEG2             | _    | _    | xxxx          |

|                             |                                 | 31:16     | _     | 1     | -     | -     | _     | 1     | _            | -            | -            | _            | _    | _    | _                  | -                  | _    |      | 0000          |

| 6690                        | CNSTATG                         | 15:0      | _     |       |       |       | _     | -     | CN<br>STATG9 | CN<br>STATG8 | CN<br>STATG7 | CN<br>STATG6 | _    | _    | CN<br>STATG3       | CN<br>STATG2       | _    | _    | xxxx          |

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

<sup>2:</sup> This bit is only available on devices without a USB module.

| PIC32M2 | X330/35 | 0/3/0/4 | 130/450 | /4/0 |  |

|---------|---------|---------|---------|------|--|

| NOTES:  |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

#### REGISTER 16-1: ICXCON: INPUT CAPTURE 'x' CONTROL REGISTER (CONTINUED)

bit 2-0 ICM<2:0>: Input Capture Mode Select bits

111 = Interrupt-Only mode (only supported while in Sleep mode or Idle mode)

110 = Simple Capture Event mode – every edge, specified edge first and every edge thereafter

101 = Prescaled Capture Event mode – every sixteenth rising edge

100 = Prescaled Capture Event mode – every fourth rising edge

011 = Simple Capture Event mode – every rising edge

010 = Simple Capture Event mode – every falling edge

001 = Edge Detect mode – every edge (rising and falling)000 = Input Capture module is disabled

**Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

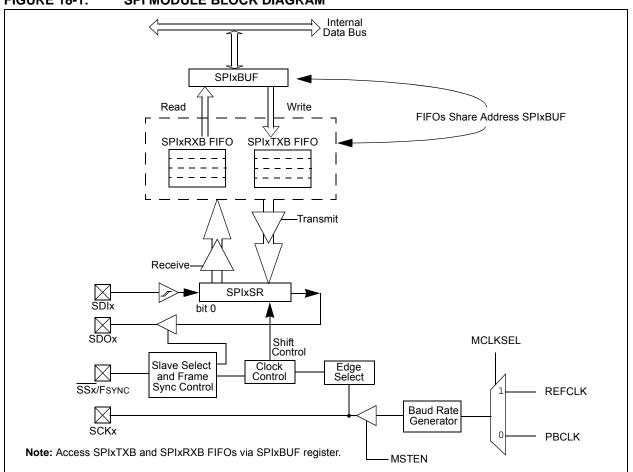

# 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note:

This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 23.** "**Serial Peripheral Interface (SPI)**" (DS60001106), which is available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The SPI module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontroller devices. These peripheral devices may be Serial EEPROMs, Shift registers, display drivers, Analog-to-Digital Converters (ADC), etc. The PIC32 SPI module is compatible with Motorola® SPI and SIOP interfaces.

Some of the key features of the SPI module are:

- · Master and Slave modes support

- · Four different clock formats

- · Enhanced Framed SPI protocol support

- User-configurable 8-bit, 16-bit and 32-bit data width

- Separate SPI FIFO buffers for receive and transmit

- FIFO buffers act as 4/8/16-level deep FIFOs based on 32/16/8-bit data width

- Programmable interrupt event on every 8-bit, 16-bit and 32-bit data transfer

- · Operation during CPU Sleep and Idle mode

- Audio Codec Support:

- I<sup>2</sup>S protocol

- Left-justified

- Right-justified

- PCM

FIGURE 18-1: SPI MODULE BLOCK DIAGRAM

## REGISTER 19-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER (CONTINUED)

- bit 4 **P:** Stop bit

- 1 = Indicates that a Stop bit has been detected last

- 0 = Stop bit was not detected last

Hardware set or clear when Start, Repeated Start or Stop detected.

- bit 3 S: Start bit

- 1 = Indicates that a Start (or Repeated Start) bit has been detected last

- 0 = Start bit was not detected last

Hardware set or clear when Start, Repeated Start or Stop detected.

- bit 2  $\mathbf{R}_{\mathbf{W}}$ : Read/Write Information bit (when operating as  $I^2$ C slave)

- 1 = Read indicates data transfer is output from slave

- 0 = Write indicates data transfer is input to slave

Hardware set or clear after reception of I<sup>2</sup>C device address byte.

- bit 1 RBF: Receive Buffer Full Status bit

- 1 = Receive complete, I2CxRCV is full

- 0 = Receive not complete, I2CxRCV is empty

Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.

- bit 0 TBF: Transmit Buffer Full Status bit

- 1 = Transmit in progress, I2CxTRN is full

- 0 = Transmit complete, I2CxTRN is empty

Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.

#### REGISTER 22-3: RTCTIME: RTC TIME VALUE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-x               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31:24        | HR10<3:0> HR01<3:0> |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 22.46        | R/W-x               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        |                     | MIN10             | <3:0>             |                   | MIN01<3:0>        |                   |                  |                  |  |  |  |

| 45.0         | R/W-x               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         |                     | SEC10             | <3:0>             |                   | SEC01             | <3:0>             |                  |                  |  |  |  |

| 7.0          | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 7:0          |                     | _                 | _                 | _                 | _                 |                   |                  | _                |  |  |  |

#### Legend:

bit 7-0

Note:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-28 **HR10<3:0>:** Binary-Coded Decimal Value of Hours bits, 10s place digits; contains a value from 0 to 2 bit 27-24 **HR01<3:0>:** Binary-Coded Decimal Value of Hours bits, 1s place digit; contains a value from 0 to 9 bit 23-20 **MIN10<3:0>:** Binary-Coded Decimal Value of Minutes bits, 10s place digits; contains a value from 0 to 5 bit 19-16 **MIN01<3:0>:** Binary-Coded Decimal Value of Minutes bits, 1s place digit; contains a value from 0 to 9 bit 15-12 **SEC10<3:0>:** Binary-Coded Decimal Value of Seconds bits, 10s place digits; contains a value from 0 to 5 bit 11-8 **SEC01<3:0>:** Binary-Coded Decimal Value of Seconds bits, 1s place digit; contains a value from 0 to 9

This register is only writable when RTCWREN = 1 (RTCCON<3>).

Unimplemented: Read as '0'

#### REGISTER 22-6: ALRMDATE: ALARM DATE VALUE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                     | _                 |                   | -                 | _                 | -                 | _                |                  |  |  |  |

| 22.46        | R/W-x                 | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        |                       | MONT              | H10<3:0>          |                   | MONTH01<3:0>      |                   |                  |                  |  |  |  |

| 45.0         | R/W-x                 | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         | DAY10<1:0> DAY01<3:0> |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | U-0                   | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 7:0          |                       | _                 | _                 |                   | WDAY01<3:0>       |                   |                  |                  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-24 Unimplemented: Read as '0'

bit 23-20 MONTH10<3:0>: Binary Coded Decimal value of months bits, 10s place digits; contains a value of 0 or 1

bit 19-16 MONTH01<3:0>: Binary Coded Decimal value of months bits, 1s place digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary Coded Decimal value of days bits, 10s place digits; contains a value from 0 to 3

bit 11-8 DAY01<3:0>: Binary Coded Decimal value of days bits, 1s place digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

bit 3-0 WDAY01<3:0>: Binary Coded Decimal value of weekdays bits, 1s place digit; contains a value from 0 to 6

#### 29.0 INSTRUCTION SET

The PIC32MX330/350/370/430/450/470 family instruction set complies with the MIPS32 $^{\$}$  Release 2 instruction set architecture. The PIC32 device family does not support the following features:

- · Core extend instructions

- · Coprocessor 1 instructions

- · Coprocessor 2 instructions

Note: Refer to "MIPS32® Architecture for Programmers Volume II: The MIPS32® Instruction Set" at www.imgtec.com for more information.

TABLE 31-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARACTERISTICS |                        |         | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                                           |  |  |  |

|--------------------|------------------------|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--|--|--|

| Parameter No.      | Typical <sup>(3)</sup> | Maximum | Units Conditions                                                                                                                                                                                                                                         |                                           |  |  |  |

| Operating (        | Current (IDD)          | (1,2)   |                                                                                                                                                                                                                                                          |                                           |  |  |  |

| DC20               | 2.5                    | 4       | mA                                                                                                                                                                                                                                                       | 4 MHz                                     |  |  |  |

| DC21               | 6                      | 9       | mA                                                                                                                                                                                                                                                       | 10 MHz (Note 4)                           |  |  |  |

| DC22               | 11                     | 17      | mA                                                                                                                                                                                                                                                       | mA 20 MHz (Note 4)                        |  |  |  |

| DC23               | 21                     | 32      | mA                                                                                                                                                                                                                                                       | 40 MHz (Note 4)                           |  |  |  |

| DC24               | 30                     | 45      | mA                                                                                                                                                                                                                                                       | 60 MHz (Note 4)                           |  |  |  |

| DC25               | 40                     | 60      | mA                                                                                                                                                                                                                                                       | 80 MHz                                    |  |  |  |

| DC25a              | 50                     | 75      | mA                                                                                                                                                                                                                                                       | 100 MHz, -40°C ≤ TA ≤ +85°C               |  |  |  |

| DC25c              | 72                     | 84      | mA                                                                                                                                                                                                                                                       | 120 MHz, 0°C ≤ TA ≤ +70°C                 |  |  |  |

| DC26               | 100                    | _       | μA                                                                                                                                                                                                                                                       | +25°C, 3.3V LPRC (31 kHz) <b>(Note 4)</b> |  |  |  |

- **Note 1:** A device's IDD supply current is mainly a function of the operating voltage and frequency. Other factors, such as PBCLK (Peripheral Bus Clock) frequency, number of peripheral modules enabled, internal code execution pattern, execution from Program Flash memory vs. SRAM, I/O pin loading and switching rate, oscillator type, as well as temperature, can have an impact on the current consumption.

- 2: The test conditions for IDD measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- · OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU, program Flash, and SRAM data memory are operational, program Flash memory Wait states = 7, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating (ON bit = 0), but the associated PMD bit is clear

- · WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- CPU executing while(1) statement from Flash

- · RTCC and JTAG are disabled

- **3:** Data in "Typical" column is at 3.3V, 25°C at specified operating frequency unless otherwise stated. Parameters are for design guidance only and are not tested.

- 4: This parameter is characterized, but not tested in manufacturing.

TABLE 31-12: DC CHARACTERISTICS: PROGRAM MEMORY<sup>(3)</sup>

| DC CHARACTERISTICS |                          |                                       | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                        |      |       |                                               |  |  |

|--------------------|--------------------------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|-----------------------------------------------|--|--|

| Param.<br>No.      | Symbol   Characteristics |                                       | Min.                                                                                                                                                                                                                                                     | Typical <sup>(1)</sup> | Max. | Units | Conditions                                    |  |  |

| D130               | ЕР                       | Cell Endurance                        | 20,000                                                                                                                                                                                                                                                   | _                      |      | E/W   | _                                             |  |  |

| D131               | VPR                      | VDD for Read                          | 2.3                                                                                                                                                                                                                                                      | _                      | 3.6  | V     | _                                             |  |  |

| D132               | VPEW                     | VDD for Erase or Write                | 2.3                                                                                                                                                                                                                                                      | _                      | 3.6  | V     | _                                             |  |  |

| D134               | TRETD                    | Characteristic Retention              | 20                                                                                                                                                                                                                                                       | _                      | _    | Year  | Provided no other specifications are violated |  |  |

| D135               | IDDP                     | Supply Current during<br>Programming  | _                                                                                                                                                                                                                                                        | 10                     | _    | mA    | _                                             |  |  |

| D138               | Tww                      | Word Write Cycle Time <sup>(4)</sup>  | 44                                                                                                                                                                                                                                                       | _                      | 59   | μs    | _                                             |  |  |

| D136               | Trw                      | Row Write Cycle Time <sup>(2,4)</sup> | 2.8                                                                                                                                                                                                                                                      | 3.3                    | 3.8  | ms    | _                                             |  |  |

| D137               | TPE                      | Page Erase Cycle Time <sup>(4)</sup>  | 22                                                                                                                                                                                                                                                       |                        | 29   | ms    |                                               |  |  |

| D139               | TCE                      | Chip Erase Cycle Time <sup>(4)</sup>  | 86                                                                                                                                                                                                                                                       | _                      | 116  | ms    | _                                             |  |  |

- **Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

- 2: The minimum SYSCLK for row programming is 8 MHz. Care should be taken to minimize bus activities during row programming, such as suspending any memory-to-memory DMA operations. If heavy bus loads are expected, selecting Bus Matrix Arbitration mode 2 (rotating priority) may be necessary. The default Arbitration mode is mode 1 (CPU has lowest priority).

- **3:** Refer to the "PIC32 Flash Programming Specification" (DS60001145) for operating conditions during programming and erase cycles.

- **4:** This parameter depends on the FRC accuracy (see Table 31-20) and the FRC tuning values (see Register 8-2).

TABLE 31-13: DC CHARACTERISTICS: PROGRAM FLASH MEMORY WAIT STATE

| DC CHARACTERISTICS         | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |       |                 |  |  |  |  |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------|--|--|--|--|

|                            |                                                                                                                                                                                                                                                          |       |                 |  |  |  |  |

| Required Flash Wait States | SYSCLK                                                                                                                                                                                                                                                   | Units | Conditions      |  |  |  |  |

| 0 Wait State               | 0-40                                                                                                                                                                                                                                                     | MHz   | -40°C to +85°C  |  |  |  |  |

| o wait state               | 0-30                                                                                                                                                                                                                                                     | MHz   | -40°C to +105°C |  |  |  |  |

| 1 Wait State               | 41-80                                                                                                                                                                                                                                                    | MHz   | -40°C to +85°C  |  |  |  |  |

| i Wait State               | 31-60                                                                                                                                                                                                                                                    | MHz   | -40°C to +105°C |  |  |  |  |

| 2 Mait States              | 81-100                                                                                                                                                                                                                                                   | MHz   | -40°C to +85°C  |  |  |  |  |

| 2 Wait States              | 61-80                                                                                                                                                                                                                                                    | MHz   | -40°C to +105°C |  |  |  |  |

| 3 Wait States              | 101-120                                                                                                                                                                                                                                                  | MHz   | 0°C to +70°C    |  |  |  |  |

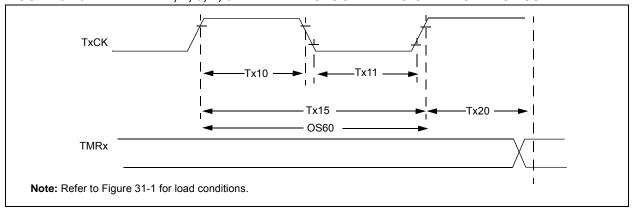

FIGURE 31-6: TIMER1, 2, 3, 4, 5 EXTERNAL CLOCK TIMING CHARACTERISTICS

### TABLE 31-24: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS<sup>(1)</sup>

|                    | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) |                                                                                                           |  |  |  |  |  |

|--------------------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| AC CHARACTERISTICS | Operating temperature                                                 | $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |  |  |  |  |  |

|                    |                                                                       | $-40^{\circ}$ C $\leq$ TA $\leq$ $+105^{\circ}$ C for V-temp                                              |  |  |  |  |  |

| Param.<br>No. | Symbol    | Characteristics <sup>(2)</sup>                                                                          |                              | Min.                                    | Typical | Max. | Units | Conditions                         |

|---------------|-----------|---------------------------------------------------------------------------------------------------------|------------------------------|-----------------------------------------|---------|------|-------|------------------------------------|

| TA10          | ТтхН      | TxCK<br>High Time                                                                                       | Synchronous, with prescaler  | [(12.5 ns or 1 TPB)/N]<br>+ 25 ns       | _       | _    | ns    | Must also meet parameter TA15      |

|               |           |                                                                                                         | Asynchronous, with prescaler | 10                                      | _       | _    | ns    | _                                  |

| TA11 TTXL     |           | TxCK<br>Low Time                                                                                        | Synchronous, with prescaler  | [(12.5 ns or 1 TPB)/N] —<br>+ 25 ns     |         | _    | ns    | Must also meet parameter TA15      |

|               |           |                                                                                                         | Asynchronous, with prescaler | 10                                      | _       | _    | ns    | _                                  |

| TA15          | ТтхР      | TxCK<br>Input Period                                                                                    | Synchronous, with prescaler  | [(Greater of 25 ns or 2 TPB)/N] + 30 ns | _       | _    | ns    | VDD > 2.7V                         |

|               |           |                                                                                                         |                              | [(Greater of 25 ns or 2 TPB)/N] + 50 ns | _       | _    | ns    | VDD < 2.7V                         |

|               |           |                                                                                                         | Asynchronous, with prescaler | 20                                      | _       | _    | ns    | V <sub>DD</sub> > 2.7V<br>(Note 3) |

|               |           |                                                                                                         |                              | 50                                      | _       | _    | ns    | V <sub>DD</sub> < 2.7V<br>(Note 3) |

| OS60          | Fт1       | SOSC1/T1CK Oscillator<br>Input Frequency Range<br>(oscillator enabled by setting<br>TCS bit (T1CON<1>)) |                              | 32                                      | _       | 100  | kHz   | _                                  |

| TA20          | TCKEXTMRL | Delay from External TxCK<br>Clock Edge to Timer<br>Increment                                            |                              | _                                       |         | 1    | Трв   | _                                  |

Note 1: Timer1 is a Type A.

2: This parameter is characterized, but not tested in manufacturing.

**3:** N = Prescale Value (1, 8, 64, 256).

TABLE 31-35: ADC MODULE SPECIFICATIONS (CONTINUED)

| AC CHARACTERISTICS <sup>(5)</sup> |                                                       |                                | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |              |      |       |                                                         |  |  |  |

|-----------------------------------|-------------------------------------------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|-------|---------------------------------------------------------|--|--|--|

| Param.<br>No.                     | Symbol                                                | Characteristics                | Min.                                                                                                                                                                                                                                                     | Typical      | Max. | Units | Conditions                                              |  |  |  |

| ADC Ac                            | ADC Accuracy – Measurements with Internal VREF+/VREF- |                                |                                                                                                                                                                                                                                                          |              |      |       |                                                         |  |  |  |

| AD20d                             | D20d Nr Resolution                                    |                                |                                                                                                                                                                                                                                                          | I0 data bits |      | bits  | (Note 3)                                                |  |  |  |

| AD21d                             | INL                                                   | Integral Nonlinearity          | > -1                                                                                                                                                                                                                                                     | _            | < 1  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |  |  |

| AD22d                             | DNL                                                   | Differential Nonlinearity      | > -1                                                                                                                                                                                                                                                     | _            | < 1  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Notes 2,3) |  |  |  |