#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 124-VFTLA Dual Rows, Exposed Pad                                                |

| Supplier Device Package    | 124-VTLA (9x9)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx350f128lt-i-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                          |            |              |                                    |                  | Rei             | nappab                                | ole Pe | ripher               | als                                | s)                           |                    |                     |      |     |     |      |                                          |          |      |       |

|------------------------------------------|------------|--------------|------------------------------------|------------------|-----------------|---------------------------------------|--------|----------------------|------------------------------------|------------------------------|--------------------|---------------------|------|-----|-----|------|------------------------------------------|----------|------|-------|

| Device                                   | Pins       | Packages     | Program Memory (KB) <sup>(1)</sup> | Data Memory (KB) | Remappable Pins | Timers/Capture/Compare <sup>(2)</sup> | UART   | SPI/I <sup>2</sup> S | External Interrupts <sup>(3)</sup> | 10-bit 1 Msps ADC (Channels) | Analog Comparators | USB On-The-Go (OTG) | CTMU | 1²C | РМР | RTCC | DMA Channels<br>(Programmable/Dedicated) | I/O Pins | JTAG | Trace |

| PIC32MX330F064H                          | 64         | QFN,<br>TQFP | 64+12                              | 16               | 37              | 5/5/5                                 | 4      | 2/2                  | 5                                  | 28                           | 2                  | Ν                   | Y    | 2   | Y   | Y    | 4/0                                      | 53       | Y    | N     |

| PIC32MX330F064L                          | 100<br>124 | TQFP<br>VTLA | 64+12                              | 16               | 54              | 5/5/5                                 | 5      | 2/2                  | 5                                  | 28                           | 2                  | N                   | Y    | 2   | Y   | Y    | 4/0                                      | 85       | Y    | Y     |

| PIC32MX350F128H                          | 64         | QFN,<br>TQFP | 128+12                             | 32               | 37              | 5/5/5                                 | 4      | 2/2                  | 5                                  | 28                           | 2                  | N                   | Y    | 2   | Y   | Y    | 4/0                                      | 53       | Y    | N     |

| PIC32MX350F128L                          | 100<br>124 | TQFP<br>VTLA | 128+12                             | 32               | 54              | 5/5/5                                 | 5      | 2/2                  | 5                                  | 28                           | 2                  | N                   | Y    | 2   | Y   | Y    | 4/0                                      | 85       | Y    | Y     |

| PIC32MX350F256H                          | 64         | QFN,<br>TQFP | 256+12                             | 64               | 37              | 5/5/5                                 | 4      | 2/2                  | 5                                  | 28                           | 2                  | N                   | Y    | 2   | Y   | Y    | 4/0                                      | 53       | Y    | N     |

| PIC32MX350F256L                          | 100<br>124 | TQFP         | 256+12                             | 64               | 54              | 5/5/5                                 | 5      | 2/2                  | 5                                  | 28                           | 2                  | N                   | Y    | 2   | Y   | Y    | 4/0                                      | 85       | Y    | Y     |

| PIC32MX370F512H                          | 64         | QFN,<br>TQFP | 512+12                             | 128              | 37              | 5/5/5                                 | 4      | 2/2                  | 5                                  | 28                           | 2                  | N                   | Y    | 2   | Y   | Y    | 4/0                                      | 53       | Y    | N     |

| PIC32MX370F512L                          | 100<br>124 | TQFP<br>VTLA | 512+12                             | 128              | 54              | 5/5/5                                 | 5      | 2/2                  | 5                                  | 28                           | 2                  | N                   | Y    | 2   | Y   | Y    | 4/0                                      | 85       | Y    | Y     |

| PIC32MX430F064H                          | 64         | QFN,<br>TQFP | 64+12                              | 16               | 34              | 5/5/5                                 | 4      | 2/2                  | 5                                  | 28                           | 2                  | Y                   | Y    | 2   | Y   | Y    | 4/2                                      | 49       | Y    | N     |

| PIC32MX430F064L                          | 100<br>124 | TQFP<br>VTLA | 64+12                              | 16               | 51              | 5/5/5                                 | 5      | 2/2                  | 5                                  | 28                           | 2                  | Y                   | Y    | 2   | Y   | Y    | 4/2                                      | 81       | Y    | Y     |

| PIC32MX450F128H                          | 64         | QFN,<br>TQFP | 128+12                             | 32               | 34              | 5/5/5                                 | 4      | 2/2                  | 5                                  | 28                           | 2                  | Y                   | Y    | 2   | Y   | Y    | 4/2                                      | 49       | Y    | N     |

| PIC32MX450F128HB (see Note 4)            | 64         | QFN,<br>TQFP | 128+12                             | 32               | 34              | 5/5/5                                 | 4      | 2/2                  | 5                                  | 28                           | 2                  | Y                   | Y    | 2   | Y   | Y    | 4/2                                      | 49       | Y    | N     |

| PIC32MX450F128L                          | 100<br>124 | TQFP<br>VTLA | 128+12                             | 32               | 51              | 5/5/5                                 | 5      | 2/2                  | 5                                  | 28                           | 2                  | Y                   | Y    | 2   | Y   | Y    | 4/2                                      | 81       | Y    | Y     |

| PIC32MX450F256H                          | 64         | QFN,<br>TQFP | 256+12                             | 64               | 34              | 5/5/5                                 | 4      | 2/2                  | 5                                  | 28                           | 2                  | Y                   | Y    | 2   | Y   | Y    | 4/2                                      | 49       | Y    | N     |

| PIC32MX450F256L                          | 100<br>124 | TQFP<br>VTLA | 256+12                             | 64               | 51              | 5/5/5                                 | 5      | 2/2                  | 5                                  | 28                           | 2                  | Y                   | Y    | 2   | Y   | Y    | 4/2                                      | 81       | Y    | Y     |

| PIC32MX470F512H                          | 64         | QFN,<br>TQFP | 512+12                             | 128              | 34              | 5/5/5                                 | 4      | 2/2                  | 5                                  | 28                           | 2                  | Y                   | Y    | 2   | Y   | Y    | 4/2                                      | 49       | Y    | N     |

| PIC32MX470F512L                          | 100<br>124 | TQFP<br>VTLA | 512+12                             | 128              | 51              | 5/5/5                                 | 5      | 2/2                  | 5                                  | 28                           | 2                  | Y                   | Y    | 2   | Y   | Y    | 4/2                                      | 81       | Y    | Y     |

| PIC32MX470F512LB<br>(see <b>Note 4</b> ) | 100<br>124 | TQFP<br>VTLA | 512+12                             | 128              | 51              | 5/5/5                                 | 5      | 2/2                  | 5                                  | 28                           | 2                  | Y                   | Y    | 2   | Y   | Y    | 4/2                                      | 81       | Y    | Y     |

### TABLE 1:PIC32MX330/350/370/430/450/470 CONTROLLER FAMILY FEATURES

Note 1: All devices feature 12 KB of Boot Flash memory.

2: Four out of five timers are remappable.

3: Four out of five external interrupts are remappable.

4: This PIC32 device is targeted to specific audio software packages that are tracked for licensing royalty purposes. All peripherals and electrical characteristics are identical to their corresponding base part numbers

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 23:16        | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 15.0         | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | -                 | _                 | _                 | _                 |                   | _                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 |                   |                   | TUN<              | 5:0> <b>(1)</b>   |                  |                  |

## REGISTER 8-2: OSCTUN: FRC TUNING REGISTER

| Legend:           | y = Value set from Configuration bits on POR |                          |                    |  |  |  |  |  |

|-------------------|----------------------------------------------|--------------------------|--------------------|--|--|--|--|--|

| R = Readable bit  | W = Writable bit                             | U = Unimplemented bit, r | ead as '0'         |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                             | '0' = Bit is cleared     | x = Bit is unknown |  |  |  |  |  |

#### bit 31-6 Unimplemented: Read as '0'

**Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation, and is neither characterized nor tested.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | —                 | _                 | _                 |                   | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 23:16        | —                 | —                 | —                 | _                 | —                 | —                 | _                | CHECOH           |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8         | —                 | —                 | —                 | -                 | —                 |                   | DCSZ             | 2<1:0>           |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | R/W-1             | R/W-1            | R/W-1            |

| 7:0          | _                 | —                 | PREFE             | N<1:0>            | _                 | F                 | PFMWS<2:0>       | >                |

#### REGISTER 9-1: CHECON: CACHE CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-17 Unimplemented: Write '0'; ignore read

- bit 16 CHECOH: Cache Coherency Setting on a PFM Program Cycle bit

- 1 = Invalidate all data and instruction lines

- 0 = Invalidate all data lnes and instruction lines that are not locked

- bit 15-10 Unimplemented: Write '0'; ignore read

- bit 9-8 DCSZ<1:0>: Data Cache Size in Lines bits

- 11 = Enable data caching with a size of 4 Lines

- 10 = Enable data caching with a size of 2 Lines

- 01 = Enable data caching with a size of 1 Line

- 00 = Disable data caching

Changing these bits induce all lines to be reinitialized to the "invalid" state.

bit 7-6 **Unimplemented:** Write '0'; ignore read

#### bit 5-4 **PREFEN<1:0>:** Predictive Prefetch Enable bits

- 11 = Enable predictive prefetch for both cacheable and non-cacheable regions

- 10 = Enable predictive prefetch for non-cacheable regions only

- 01 = Enable predictive prefetch for cacheable regions only

- 00 = Disable predictive prefetch

- bit 3 Unimplemented: Write '0'; ignore read

#### bit 2-0 PFMWS<2:0>: PFM Access Time Defined in Terms of SYSLK Wait States bits

- 111 = Seven Wait states

- 110 = Six Wait states

- 101 = Five Wait states

- 100 = Four Wait states

- 011 = Three Wait states

- 010 = Two Wait states

- 001 = One Wait state

- 000 = Zero Wait state

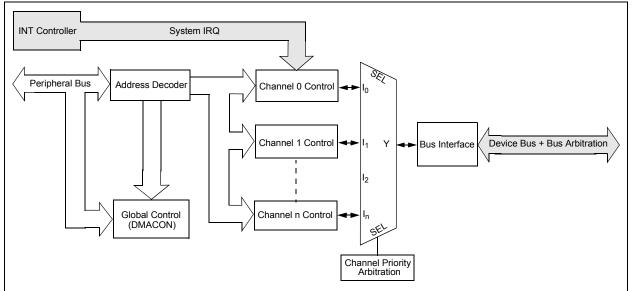

## 10.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 31. "Direct Memory Access (DMA) Controller" (DS60001117), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32 Direct Memory Access (DMA) controller is a bus master module useful for data transfers between different devices without CPU intervention. The source and destination of a DMA transfer can be any of the memory mapped modules existent in the PIC32 (such as Peripheral Bus (PBUS) devices: SPI, UART, PMP, etc.) or memory itself.

Following are some of the key features of the DMA controller module:

- Four identical channels, each featuring:

- Auto-increment source and destination address registers

- Source and destination pointers

- Memory to memory and memory to peripheral transfers

- Automatic word-size detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source and destination

- Fixed priority channel arbitration

- · Flexible DMA channel operating modes:

- Manual (software) or automatic (interrupt) DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- · Flexible DMA requests:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any (appropriate) observable interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Pattern (data) match transfer termination

- · Multiple DMA channel status interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- DMA debug support features:

- Most recent address accessed by a DMA channel

- Most recent DMA channel to transfer data

- · CRC Generation module:

- CRC module can be assigned to any of the available channels

- CRC module is highly configurable

## FIGURE 10-1: DMA BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   |                   |                   | DCRCDAT           | A<31:24>          |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | DCRCDATA<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         |                   |                   |                   | DCRCDAT           | A<15:8>           |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | DCRCDATA<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

### REGISTER 10-5: DCRCDATA: DMA CRC DATA REGISTER

## Legend:

| Legena:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-0 DCRCDATA<31:0>: CRC Data Register bits

Writing to this register will seed the CRC generator. Reading from this register will return the current value of the CRC. Bits greater than PLEN will return '0' on any read.

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): Only the lower 16 bits contain IP header checksum information. The upper 16 bits are always '0'. Data written to this register is converted and read back in 1's complement form (i.e., current IP header checksum value).

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Bits greater than PLEN will return '0' on any read.

## REGISTER 10-6: DCRCXOR: DMA CRCXOR ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   |                   |                   | DCRCXOF           | ?<31:24>          |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | DCRCXOR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         |                   |                   |                   | DCRCXO            | R<15:8>           |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | DCRCXOR<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-0 DCRCXOR<31:0>: CRC XOR Register bits

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): This register is unused.

When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

- 1 = Enable the XOR input to the Shift register

- 0 = Disable the XOR input to the Shift register; data is shifted in directly from the previous stage in the register

## TABLE 11-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       |       |       |       | ,     |      |      | Bit  | s    |      |          |        |        |         |        | 6          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|--------|--------|---------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3   | 18/2   | 17/1    | 16/0   | All Resets |

| 5390                        | U1EP9                           | 31:16     | —     | —     |       | —     | _     | _     | —    | —    |      |      | —    | —        | —      | —      | —       | _      | 0000       |

| 5390                        | UIEF9                           | 15:0      | —     | _     |       | _     | _     | _     | —    | _    | —    |      | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53A0                        | U1EP10                          | 31:16     | —     | _     |       | _     |       |       | _    |      |      |      | _    | —        | _      | _      | —       | -      | 0000       |

| 53A0                        | UIEFIU                          | 15:0      | _     | _     |       | _     | -     | -     | _    | _    | _    |      | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53B0                        | U1EP11                          | 31:16     | _     | _     | —     | _     | _     | _     | _    | _    | _    | _    | _    | —        | _      | _      | _       | _      | 0000       |

| 5560                        | UIEFII                          | 15:0      | _     | _     | —     | _     | _     | _     | _    | _    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53C0                        | U1EP12                          | 31:16     | _     | _     | —     | _     | —     | —     | -    | -    | —    | —    | _    | —        | _      | _      | —       | _      | 0000       |

| 5300                        | UIEFIZ                          | 15:0      | _     | _     | —     | _     | —     | —     | -    | -    | —    | —    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53D0                        | U1EP13                          | 31:16     | _     |       | —     | _     | —     | —     |      | _    | _    | _    |      | —        | —      | _      | —       | _      | 0000       |

| 55D0                        | UIEF 13                         | 15:0      | _     | _     | —     | _     | —     | —     | -    | -    | —    | —    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     | _     |       | _     | _     | _     | _     | _    | -    | _    | _    | _    | _        | _      | _      | _       | _      | 0000       |

| 53E0                        | U1EP14                          | 15:0      | _     |       | _     | _     | _     | _     |      | _    |      |      | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     | _     |       | _     | _     | _     | _     |      | _    |      |      | _    | _        | _      | _      | _       | _      | 0000       |

| 53F0                        | U1EP15                          | 15:0      | _     |       | _     | _     | _     | _     |      | _    |      |      | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 |                   |                   |                   | —                 |                  | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -                 | _                 |                   |                   | -                 | —                 |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | -                 | _                 |                   |                   | -                 | —                 |                  | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | R/W-0            |

| 7.0          | IDIE              | T1MSECIE          | LSTATEIE          | ACTVIE            | SESVDIE           | SESENDIE          |                  | VBUSVDIE         |

## REGISTER 11-2: U10TGIE: USB OTG INTERRUPT ENABLE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **IDIE:** ID Interrupt Enable bit

- 1 = ID interrupt is enabled

- 0 = ID interrupt is disabled

- bit 6 T1MSECIE: 1 Millisecond Timer Interrupt Enable bit

- 1 = 1 millisecond timer interrupt is enabled

- 0 = 1 millisecond timer interrupt is disabled

- bit 5 LSTATEIE: Line State Interrupt Enable bit

- 1 = Line state interrupt is enabled

- 0 = Line state interrupt is disabled

- bit 4 ACTVIE: Bus Activity Interrupt Enable bit

- 1 = ACTIVITY interrupt is enabled

- 0 = ACTIVITY interrupt is disabled

- bit 3 SESVDIE: Session Valid Interrupt Enable bit

- 1 = Session valid interrupt is enabled

- 0 = Session valid interrupt is disabled

- bit 2 SESENDIE: B-Session End Interrupt Enable bit

- 1 = B-session end interrupt is enabled

- 0 = B-session end interrupt is disabled

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIE: A-VBUS Valid Interrupt Enable bit

- 1 = A-VBUS valid interrupt is enabled

- 0 = A-VBUS valid interrupt is disabled

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31.24        | —                 | —                 |                   | —                 |                   |                   |                  |                  |  |  |  |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        | —                 | —                 | _                 | —                 | -                 | -                 | —                | —                |  |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 15.0         | —                 | —                 | _                 | —                 | —                 | -                 | —                | —                |  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0              | R/W-0            |  |  |  |  |  |

| 7:0          | UTEYE             | UOEMON            |                   | USBSIDL           | _                 |                   | _                | UASUSPND         |  |  |  |  |  |

#### REGISTER 11-20: U1CNFG1: USB CONFIGURATION 1 REGISTER

#### Legend:

| R = Readable bit  | Readable bit W = Writable bit |                      | read as '0'        |

|-------------------|-------------------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7 UTEYE: USB Eye-Pattern Test Enable bit

- 1 = Eye-Pattern Test is enabled

- 0 = Eye-Pattern Test is disabled

#### bit 6 **UOEMON:** USB OE Monitor Enable bit

1 = OE signal is active; it indicates intervals during which the D+/D- lines are driving

0 = OE signal is inactive

#### bit 5 Unimplemented: Read as '0'

- bit 4 USBSIDL: Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

#### bit 3-1 Unimplemented: Read as '0'

#### bit 0 UASUSPND: Automatic Suspend Enable bit

- 1 = USB module automatically suspends upon entry to Sleep mode. See the USUSPEND bit (U1PWRC<1>) in Register 11-5.

- 0 = USB module does not automatically suspend upon entry to Sleep mode. Software must use the USUSPEND bit (U1PWRC<1>) to suspend the module, including the USB 48 MHz clock

| REGISTER 18-2: SPIxCON | 2: SPI CONTROL REGISTER 2 |

|------------------------|---------------------------|

|------------------------|---------------------------|

| Bit<br>Range | Bit Bit 31/23/15/7 30/22/14/ |     |     |          | Bit<br>26/18/10/2        | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |                         |

|--------------|------------------------------|-----|-----|----------|--------------------------|------------------|------------------|-------------------------|

| 31:24        | U-0                          | U-0 | U-0 | U-0      | U-0                      | U-0              | U-0              | U-0                     |

| 31.24        | _                            |     | —   | —        | —                        | _                | _                | —                       |

| 23:16        | U-0                          | U-0 | U-0 | U-0      | U-0                      | U-0              | U-0              | U-0                     |

| 23.10        | —                            | _   | _   | —        | —                        | —                | _                | —                       |

| 15:8         | R/W-0                        | U-0 | U-0 | R/W-0    | R/W-0                    | R/W-0            | R/W-0            | R/W-0                   |

| 10.0         | SPISGNEXT                    | _   | _   | FRMERREN | SPIROVEN                 | SPITUREN         | IGNROV           | IGNTUR                  |

| 7:0          | R/W-0                        | U-0 | U-0 | U-0      | R/W-0                    | U-0              | R/W-0            | R/W-0                   |

| 7:0          | AUDEN <sup>(1)</sup>         |     | _   |          | AUDMONO <sup>(1,2)</sup> |                  | AUDMOD           | )<1:0> <sup>(1,2)</sup> |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

bit 31-16 Unimplemented: Read as '0'

- bit 15 SPISGNEXT: Sign Extend Read Data from the RX FIFO bit

- 1 = Data from RX FIFO is sign extended

- 0 = Data from RX FIFO is not sign extened

- bit 14-13 Unimplemented: Read as '0'

- bit 12 FRMERREN: Enable Interrupt Events via FRMERR bit

- 1 = Frame Error overflow generates error events

- 0 = Frame Error does not generate error events

- bit 11 SPIROVEN: Enable Interrupt Events via SPIROV bit

- 1 = Receive overflow generates error events

- 0 = Receive overflow does not generate error events

- bit 10 **SPITUREN:** Enable Interrupt Events via SPITUR bit

- 1 = Transmit Underrun Generates Error Events

- 0 = Transmit Underrun Does Not Generates Error Events

- bit 9 **IGNROV:** Ignore Receive Overflow bit (for Audio Data Transmissions)

- 1 = A ROV is not a critical error; during ROV data in the fifo is not overwritten by receive data

- 0 = A ROV is a critical error which stop SPI operation

- bit 8 **IGNTUR:** Ignore Transmit Underrun bit (for Audio Data Transmissions)

- 1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty

- 0 = A TUR is a critical error which stop SPI operation

- bit 7 AUDEN: Enable Audio CODEC Support bit<sup>(1)</sup>

- 1 = Audio protocol is enabled

- 0 = Audio protocol is disabled

- bit 6-5 Unimplemented: Read as '0'

## bit 3 AUDMONO: Transmit Audio Data Format bit<sup>(1,2)</sup>

- 1 = Audio data is mono (Each data word is transmitted on both left and right channels)

0 = Audio data is stereo

- bit 2 Unimplemented: Read as '0'

- bit 1-0 AUDMOD<1:0>: Audio Protocol Mode bit<sup>(1,2)</sup>

- 11 = PCM/DSP mode

- 10 = Right Justified mode

- 01 = Left Justified mode

- $00 = I^2 S \mod I$

- **Note 1:** This bit can only be written when the ON bit = 0.

- 2: This bit is only valid for AUDEN = 1.

## REGISTER 19-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER

| Bit<br>Range | Bit Bit<br>31/23/15/7 30/22/14/6 |           | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|----------------------------------|-----------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 04.04        | U-0                              | U-0       | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 31:24        | —                                | -         | _                 | -                 | —                 |                   | _                | _                |  |  |  |  |  |  |

| 00.40        | U-0                              | U-0       | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 23:16        | —                                | _         | _                 | _                 | _                 | —                 | _                | _                |  |  |  |  |  |  |

| 15.0         | R-0, HSC                         | R-0, HSC  | U-0               | U-0               | U-0               | R/C-0, HS         | R-0, HSC         | R-0, HSC         |  |  |  |  |  |  |

| 15:8         | ACKSTAT                          | TRSTAT    | -                 | -                 | _                 | BCL               | GCSTAT           | ADD10            |  |  |  |  |  |  |

| 7:0          | R/C-0, HS                        | R/C-0, HS | R-0, HSC          | R/C-0, HSC        | R/C-0, HSC        | R-0, HSC          | R-0, HSC         | R-0, HSC         |  |  |  |  |  |  |

| 7:0          | IWCOL                            | I2COV     | D_A               | Р                 | S                 | R_W               | RBF              | TBF              |  |  |  |  |  |  |

| Legend:           | HS = Set in hardware | n hardware HSC = Hardware set/cleared |                   |  |  |

|-------------------|----------------------|---------------------------------------|-------------------|--|--|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, read as '0'    |                   |  |  |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared                  | C = Clearable bit |  |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 ACKSTAT: Acknowledge Status bit

(when operating as  $I^2C$  master, applicable to master transmit operation)

- 1 = Acknowledge was not received from slave

- 0 = Acknowledge was received from slave

Hardware set or clear at end of slave Acknowledge.

- bit 14 **TRSTAT:** Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation)

- 1 = Master transmit is in progress (8 bits + ACK)

- 0 = Master transmit is not in progress

Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge.

- bit 13-11 Unimplemented: Read as '0'

- bit 10 BCL: Master Bus Collision Detect bit

1 = A bus collision has been detected during a master operation

0 = No collision

Hardware set at detection of bus collision. This condition can only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module.

- bit 9 **GCSTAT:** General Call Status bit

- 1 = General call address was received

- 0 = General call address was not received

Hardware set when address matches general call address. Hardware clear at Stop detection.

bit 8 ADD10: 10-bit Address Status bit

1 = 10-bit address was matched

0 = 10-bit address was not matched

Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.

- bit 7 IWCOL: Write Collision Detect bit

- 1 = An attempt to write the I2CxTRN register failed because the I<sup>2</sup>C module is busy

- 0 = No collision

Hardware set at occurrence of write to I2CxTRN while busy (cleared by software).

bit 6 I2COV: Receive Overflow Flag bit

1 = A byte was received while the I2CxRCV register is still holding the previous byte 0 = No overflow

Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

- bit 5 **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave)

- 1 = Indicates that the last byte received was data

- 0 = Indicates that the last byte received was device address

Hardware clear at device address match. Hardware set by reception of slave byte.

#### 20.1 **Control Registers**

## TABLE 20-1: UART1 THROUGH UART5 REGISTER MAP

| ess)                        |                              | Ð         |                                    |         |        |       |        |       |       | Bi          | ts          |         |       |          |          |       |        |       | s          |

|-----------------------------|------------------------------|-----------|------------------------------------|---------|--------|-------|--------|-------|-------|-------------|-------------|---------|-------|----------|----------|-------|--------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name             | Bit Range | 31/15                              | 30/14   | 29/13  | 28/12 | 27/11  | 26/10 | 25/9  | 24/8        | 23/7        | 22/6    | 21/5  | 20/4     | 19/3     | 18/2  | 17/1   | 16/0  | All Resets |

| 6000                        | U1MODE <sup>(1)</sup>        | 31:16     | _                                  |         | -      | _     | _      |       |       | _           | _           | —       | _     | _        |          | _     |        |       | 0000       |

| 0000                        | UTMODE: /                    | 15:0      | ON                                 |         | SIDL   | IREN  | RTSMD  |       | UEN   | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSEI | _<1:0> | STSEL | 0000       |

| 6010                        | U1STA <sup>(1)</sup>         | 31:16     | —                                  | _       | —      | _     | —      | _     | _     | ADM_EN      |             |         |       | ADDR     | <7:0>    |       |        |       | 0000       |

| 0010                        | 01317                        | 15:0      | UTXISE                             | L<1:0>  | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISE      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR  | OERR   | URXDA | FFFF       |

| 6020                        | U1TXREG                      | 31:16     | —                                  | _       | —      | _     | —      | _     | _     | —           | _           | _       | —     | —        | _        | —     | _      | _     | 0000       |

| 0020                        | 15:0                         |           | —                                  | _       | —      | _     | _      | _     | _     | TX8         |             |         |       | Transmit | Register |       |        |       | 0000       |

| 6030                        | U1RXREG                      | 31:16     | —                                  | —       | —      | —     | —      | —     | —     | —           | —           | —       | —     | —        | —        | —     | —      | —     | 0000       |

| 0000                        | ONVILO                       | 15:0      | —                                  | —       | —      | —     | —      | —     | —     | RX8         |             |         |       | Receive  | Register |       |        |       | 0000       |

| 6040                        | U1BRG <sup>(1)</sup>         | 31:16     | —                                  | —       | —      | —     | —      | —     | —     | —           |             | —       | —     | —        | —        | —     | —      | —     | 0000       |

| 0010                        | OTDICO                       | 15:0      | Baud Rate Generator Prescaler 0000 |         |        |       |        |       |       |             |             |         |       |          |          |       |        |       |            |

| 6200                        | U2MODE <sup>(1)</sup>        | 31:16     | —                                  | —       | —      | —     | —      | —     | —     | —           | _           | —       | —     | —        | —        | —     | —      | —     | 0000       |

|                             |                              | 15:0      | ON                                 | —       | SIDL   | IREN  | RTSMD  | —     | UEN   |             | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSEI | _<1:0> | STSEL | 0000       |

| 6210                        | U2STA <sup>(1)</sup>         | 31:16     | —                                  | —       | —      | _     | —      | —     | —     | ADM_EN      |             |         | 1     | ADDR     |          |       |        |       | 0000       |

|                             | 5210 U2STA <sup>(1)</sup> 15 | 15:0      | UTXISE                             | L<1:0>  | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISE      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR  | OERR   | URXDA | FFFF       |

| 6220                        | U2TXREG                      | 31:16     | —                                  |         | —      | _     | _      | _     |       | —           | _           | —       | —     |          | —        | _     | —      | _     | 0000       |

|                             |                              | 15:0      | —                                  |         | —      | _     | _      | _     |       | TX8         |             |         |       | Transmit | Register |       |        |       | 0000       |

| 6230                        | U2RXREG                      | 31:16     | —                                  | —       | —      | —     | —      | —     | —     | —           | _           | —       | —     | —        | —        | —     | —      | —     | 0000       |

|                             |                              | 15:0      | —                                  | —       | —      | —     | —      | —     | —     | RX8         |             |         |       | Receive  | Register |       |        |       | 0000       |

| 6240                        | U2BRG <sup>(1)</sup>         | 31:16     | _                                  | _       | _      | _     | —      | —     |       | —           | _           | —       | —     | _        | —        | _     | —      | —     | 0000       |

|                             |                              | 15:0      |                                    |         |        |       |        |       | Bau   | d Rate Gene | erator Pres | caler   |       |          |          |       |        |       | 0000       |

| 6400                        | U3MODE <sup>(1)</sup>        | 31:16     | _                                  | _       | —      | _     | —      | _     | _     | —           |             | —       | —     | —        | —        | —     | —      | —     | 0000       |

|                             |                              | 15:0      | ON                                 | _       | SIDL   | IREN  | RTSMD  | _     | UEN   | -           | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSEI | _<1:0> | STSEL | 0000       |

| 6410                        | U3STA <sup>(1)</sup>         | 31:16     | —                                  | —       | —      | -     | -      | -     | -     | ADM_EN      |             |         | 10051 | ADDR     | -        |       | 0505   |       | 0000       |

|                             |                              | 15:0      | UTXISE                             | :L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISE      | =L<1:0> | ADDEN | RIDLE    | PERR     | FERR  | OERR   | URXDA | FFFF       |

| 6420                        | U3TXREG                      | 31:16     | _                                  | _       |        | —     | _      | _     | _     | —<br>       | —           | —       | —     | —<br>—   | —        | -     | —      | —     | 0000       |

|                             |                              | 15:0      | -                                  | _       | —      | _     | _      | _     |       | TX8         |             |         |       | Transmit | -        |       |        |       | 0000       |

| 6430                        | U3RXREG                      | 31:16     | _                                  | _       | _      | _     | _      | _     | _     | -           | —           | —       | —     | —        | —        | —     | —      | —     | 0000       |

|                             |                              | 15:0      | — [                                |         |        |       |        |       |       |             |             | 0000    |       |          |          |       |        |       |            |

x = unknown value on Reset; ---- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV registers" for more informa-Note 1: tion.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31:24        | _                 | —                 | _                 | —                 | _                 |                   |                  | —                |  |  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |

| 23:16        |                   | MONT              | H10<3:0>          |                   | MONTH01<3:0>      |                   |                  |                  |  |  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |

| 15:8         |                   | DAY               | 10<1:0>           |                   | DAY01<3:0>        |                   |                  |                  |  |  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |

| 7:0          | _                 |                   |                   | WDAY01<3:0>       |                   |                   |                  |                  |  |  |  |  |  |

### REGISTER 22-6: ALRMDATE: ALARM DATE VALUE REGISTER

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | oit, read as '0'   |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-24 Unimplemented: Read as '0'

bit 23-20 MONTH10<3:0>: Binary Coded Decimal value of months bits, 10s place digits; contains a value of 0 or 1

bit 19-16 MONTH01<3:0>: Binary Coded Decimal value of months bits, 1s place digit; contains a value from 0 to 9

bit 15-12 **DAY10<3:0>:** Binary Coded Decimal value of days bits, 10s place digits; contains a value from 0 to 3

bit 11-8 **DAY01<3:0>:** Binary Coded Decimal value of days bits, 1s place digit; contains a value from 0 to 9 bit 7-4 **Unimplemented:** Read as '0'

bit 3-0 WDAY01<3:0>: Binary Coded Decimal value of weekdays bits, 1s place digit; contains a value from 0 to 6

### REGISTER 23-3: AD1CON3: ADC CONTROL REGISTER 3

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4        | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|--------------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | —                 | —                 | _                 | —                        | —                 | —                 | —                | —                |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | _                 | —                 | _                 | _                        | _                 | —                 | _                | _                |  |  |  |  |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0                    | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | ADRC              | —                 | _                 | SAMC<4:0> <sup>(1)</sup> |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0                    | R/W-0             | R/W-0             | R/W              | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | ADCS<                    | 7:0> <b>(2)</b>   |                   |                  |                  |  |  |  |  |

## Legend:

| =ogona.           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ADRC:** ADC Conversion Clock Source bit

- 1 = Clock derived from FRC

- 0 = Clock derived from Peripheral Bus Clock (PBCLK)

- bit 14-13 Unimplemented: Read as '0'

- - • 00000001 =TPB • 2 • (ADCS<7:0> + 1) = 4 • TPB = TAD 00000000 =TPB • 2 • (ADCS<7:0> + 1) = 2 • TPB = TAD

- **Note 1:** This bit is only used if the SSRC<2:0> bits (AD1CON1<7:5>) = 111.

- 2: This bit is not used if the ADRC bit (AD1CON3<15>) = 1.

NOTES:

## 30.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

## 30.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

## 30.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 30.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- · MPLAB X IDE compatibility

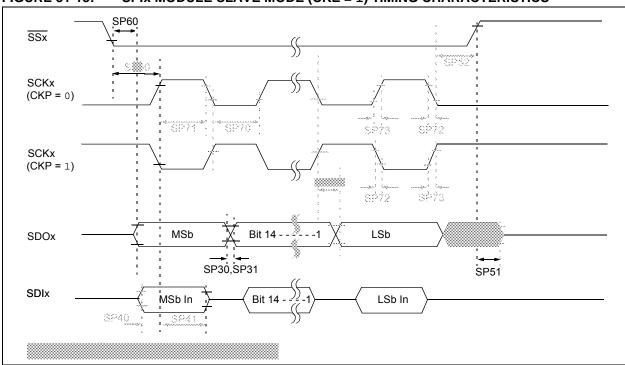

### FIGURE 31-13: SPIX MODULE SLAVE MODE (CKE = 1) TIMING CHARACTERISTICS

## TABLE 31-32: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS         |                                           | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |        |                        |      |            |                    |

|----------------------------|-------------------------------------------|------------------------------------------------------|--------|------------------------|------|------------|--------------------|

| Param.<br>No.              | Symbol                                    | Characteristics <sup>(1)</sup>                       | Min.   | Typical <sup>(2)</sup> | Max. | Units      | Conditions         |

| SP70                       | TscL                                      | SCKx Input Low Time (Note 3)                         | Tsck/2 |                        |      | ns         | —                  |

| SP71                       | TscH                                      | SCKx Input High Time (Note 3)                        | Tsck/2 | —                      | _    | ns         | —                  |

| SP72                       | TscF                                      | SCKx Input Fall Time                                 | —      | 5                      | 10   | ns         | —                  |

| SP73                       | TscR                                      | SCKx Input Rise Time                                 | —      | 5                      | 10   | ns         | —                  |

| SP30                       | TDOF                                      | SDOx Data Output Fall Time (Note 4)                  | _      | _                      |      | ns         | See parameter DO32 |

| SP31                       | TDOR                                      | SDOx Data Output Rise Time (Note 4)                  | —      | —                      | _    | ns         | See parameter DO31 |

| SP35 TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge | _                                                    | —      | 20                     | ns   | VDD > 2.7V |                    |

|                            |                                           |                                                      | —      | 30                     | ns   | VDD < 2.7V |                    |

| SP40                       | TDIV2scH,<br>TDIV2scL                     | Setup Time of SDIx Data Input to SCKx Edge           | 10     | —                      |      | ns         | —                  |

| SP41                       | TscH2diL,<br>TscL2diL                     | Hold Time of SDIx Data Input<br>to SCKx Edge         | 10     | —                      |      | ns         | —                  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: The minimum clock period for SCKx is 40 ns.

4: Assumes 50 pF load on all SPIx pins.

## TABLE 31-32: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS (CONTINUED)

| AC CHARACTERISTICS |                       | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |              |                        |      |       |            |

|--------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------------------------|------|-------|------------|

| Param.<br>No.      | Symbol                | Characteristics <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                      | Min.         | Typical <sup>(2)</sup> | Max. | Units | Conditions |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\downarrow$ or SCKx $\uparrow$ Input                                                                                                                                                                                                                                                                           | 175          |                        |      | ns    | —          |

| SP51               | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance<br>(Note 4)                                                                                                                                                                                                                                                                                                  | 5            |                        | 25   | ns    | _          |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx ↑ after SCKx Edge                                                                                                                                                                                                                                                                                                                               | Тscк +<br>20 | _                      | _    | ns    | _          |

| SP60               | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge                                                                                                                                                                                                                                                                                                            |              |                        | 25   | ns    | _          |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: The minimum clock period for SCKx is 40 ns.

4: Assumes 50 pF load on all SPIx pins.

NOTES:

NOTES: