Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx350f128lt-v-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.9 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

# 2.10 EMI/EMC/EFT (IEC 61000-4-4 and IEC 61000-4-2) Suppression Considerations

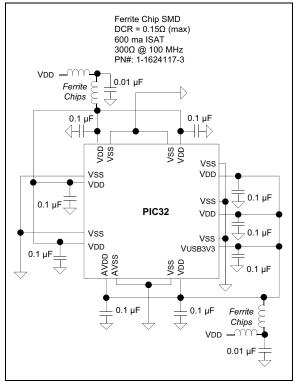

The use of LDO regulators is preferred to reduce overall system noise and provide a cleaner power source. However, when utilizing switching Buck/ Boost regulators as the local power source for PIC32 devices, as well as in electrically noisy environments or test conditions required for IEC 61000-4-4 and IEC 61000-4-2, users should evaluate the use of T-Filters (i.e., L-C-L) on the power pins, as shown in Figure 2-5. In addition to a more stable power source, use of this type of T-Filter can greatly reduce susceptibility to EMI sources and events.

FIGURE 2-5: EMI/EMC/EFT SUPPRESSION CIRCUIT

Coprocessor 0 also contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including alignment errors in data, external events or program errors. Table 3-3 lists the exception types in order of priority.

| Exception | Description                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Reset     | Assertion MCLR or a Power-on Reset (POR).                                                                                               |

| DSS       | EJTAG debug single step.                                                                                                                |

| DINT      | EJTAG debug interrupt. Caused by the assertion of the external <i>EJ_DINT</i> input or by setting the EjtagBrk bit in the ECR register. |

| NMI       | Assertion of NMI signal.                                                                                                                |

| Interrupt | Assertion of unmasked hardware or software interrupt signal.                                                                            |

| DIB       | EJTAG debug hardware instruction break matched.                                                                                         |

| AdEL      | Fetch address alignment error. Fetch reference to protected address.                                                                    |

| IBE       | Instruction fetch bus error.                                                                                                            |

| DBp       | EJTAG breakpoint (execution of SDBBP instruction).                                                                                      |

| Sys       | Execution of SYSCALL instruction.                                                                                                       |

| Вр        | Execution of BREAK instruction.                                                                                                         |

| RI        | Execution of a reserved instruction.                                                                                                    |

| CpU       | Execution of a coprocessor instruction for a coprocessor that is not enabled.                                                           |

| CEU       | Execution of a CorExtend instruction when CorExtend is not enabled.                                                                     |

| Ov        | Execution of an arithmetic instruction that overflowed.                                                                                 |

| Tr        | Execution of a trap (when trap condition is true).                                                                                      |

| DDBL/DDBS | EJTAG Data Address Break (address only) or EJTAG data value break on store (address + value).                                           |

| AdEL      | Load address alignment error. Load reference to protected address.                                                                      |

| AdES      | Store address alignment error. Store to protected address.                                                                              |

| DBE       | Load or store bus error.                                                                                                                |

| DDBL      | EJTAG data hardware breakpoint matched in load data compare.                                                                            |

# TABLE 3-3: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE EXCEPTION TYPES

# 3.3 Power Management

The MIPS<sup>®</sup> M4K<sup>®</sup> processor core offers a number of power management features, including low-power design, active power management and power-down modes of operation. The core is a static design that supports slowing or Halting the clocks, which reduces system power consumption during Idle periods.

### 3.3.1 INSTRUCTION-CONTROLLED POWER MANAGEMENT

The mechanism for invoking Power-Down mode is through execution of the WAIT instruction. For more information on power management, see Section 27.0 "Power-Saving Features".

## 3.3.2 LOCAL CLOCK GATING

The majority of the power consumed by the PIC32MX330/350/370/430/450/470 family core is in the clock tree and clocking registers. The PIC32MX family uses extensive use of local gated-clocks to reduce this dynamic power consumption.

# 3.4 EJTAG Debug Support

The MIPS<sup>®</sup> M4K<sup>®</sup> processor core provides for an Enhanced JTAG (EJTAG) interface for use in the software debug of application and kernel code. In addition to standard User mode and Kernel modes of operation, the M4K<sup>®</sup> core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification define which registers are selected and how they are used.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04-04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | IFS31             | IFS30             | IFS29             | IFS28             | IFS27             | IFS26             | IFS25            | IFS24            |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | IFS23             | IFS22             | IFS21             | IFS20             | IFS19             | IFS18             | IFS17            | IFS16            |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | IFS15             | IFS14             | IFS13             | IFS12             | IFS11             | IFS10             | IFS9             | IFS8             |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | IFS7              | IFS6              | IFS5              | IFS4              | IFS3              | IFS2              | IFS1             | IFS0             |  |  |  |  |

### REGISTER 7-4: IFSx: INTERRUPT FLAG STATUS REGISTER

## Legend:

| 0                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 IFS31-IFS0: Interrupt Flag Status bits

- 1 = Interrupt request has occurred

- 0 = No interrupt request has occurred

**Note:** This register represents a generic definition of the IFSx register. Refer to Table 7-1 for the exact bit definitions.

## REGISTER 7-5: IECx: INTERRUPT ENABLE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IEC31             | IEC30             | IEC29             | IEC28             | IEC27             | IEC26             | IEC25            | IEC24            |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | IEC23             | IEC22             | IEC21             | IEC20             | IEC19             | IEC18             | IEC17            | IEC16            |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | IEC15             | IEC14             | IEC13             | IEC12             | IEC11             | IEC10             | IEC9             | IEC8             |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | IEC7              | IEC6              | IEC5              | IEC4              | IEC3              | IEC2              | IEC1             | IEC0             |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-0 IEC31-IEC0: Interrupt Enable bits

1 = Interrupt is enabled

0 = Interrupt is disabled

**Note:** This register represents a generic definition of the IECx register. Refer to Table 7-1 for the exact bit definitions.

### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

- bit 2 UFRCEN: USB FRC Clock Enable bit<sup>(1)</sup>

- 1 = Enable FRC as the clock source for the USB clock source

- 0 = Use the Primary Oscillator or USB PLL as the USB clock source

- bit 1 SOSCEN: Secondary Oscillator (Sosc) Enable bit

- 1 = Enable Secondary Oscillator

- 0 = Disable Secondary Oscillator

- bit 0 **OSWEN:** Oscillator Switch Enable bit

- 1 = Initiate an oscillator switch to selection specified by NOSC<2:0> bits

- 0 = Oscillator switch is complete

- Note 1: This bit is available on PIC32MX4XX devices only.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

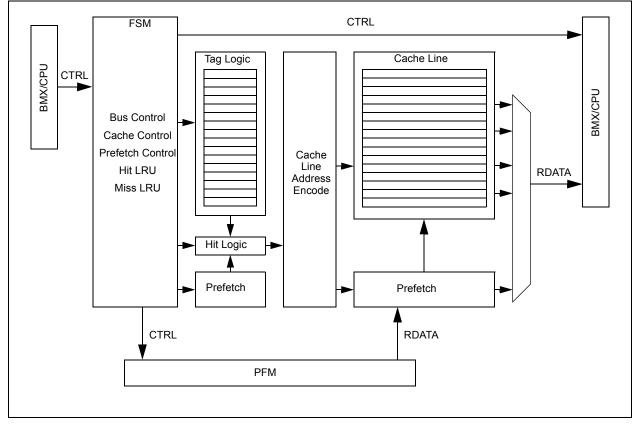

# 9.0 PREFETCH CACHE

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 4. "Prefetch Cache" (DS60001119), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

Prefetch cache increases performance for applications executing out of the cacheable program Flash memory regions by implementing instruction caching, constant data caching and instruction prefetching.

# 9.1 Features

- 16 fully associative lockable cache lines

- 16-byte cache lines

- Up to four cache lines allocated to data

- Two cache lines with address mask to hold repeated instructions

- · Pseudo LRU replacement policy

- · All cache lines are software writable

- · 16-byte parallel memory fetch

- · Predictive instruction prefetch

A simplified block diagram of the Prefetch Cache module is illustrated in Figure 9-1.

# FIGURE 9-1: PREFETCH CACHE MODULE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        | CHEWEN            | —                 |                   |                   | —                 |                   |                  | —                |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23.10        | -                 | —                 |                   | -                 | —                 |                   | -                | —                |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 10.0         | —                 | —                 | _                 | -                 | —                 | —                 | -                | —                |  |  |  |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   | _                 |                   |                   | CHEID             | X<3:0>           |                  |  |  |  |  |

## REGISTER 9-2: CHEACC: CACHE ACCESS REGISTER

## Legend:

| 0                 |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31 **CHEWEN:** Cache Access Enable bits for registers CHETAG, CHEMSK, CHEW0, CHEW1, CHEW2, and CHEW3

1 = The cache line selected by CHEIDX<3:0> is writeable

0 = The cache line selected by CHEIDX<3:0> is not writeable

bit 30-4 **Unimplemented:** Write '0'; ignore read

bit 3-0 CHEIDX<3:0>: Cache Line Index bits

The value selects the cache line for reading or writing.

## TABLE 10-3: DMA CHANNEL 0 THROUGH CHANNEL 3 REGISTER MAP (CONTINUED)

| ess                         |                                 |               |            |             |            |              |              |            |            | Bi     | ts                   |        |        |                  |                  |        |        |        |            |

|-----------------------------|---------------------------------|---------------|------------|-------------|------------|--------------|--------------|------------|------------|--------|----------------------|--------|--------|------------------|------------------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15      | 30/14       | 29/13      | 28/12        | 27/11        | 26/10      | 25/9       | 24/8   | 23/7                 | 22/6   | 21/5   | 20/4             | 19/3             | 18/2   | 17/1   | 16/0   | All Resets |

| 3170                        | DCH1SSIZ                        | 31:16         | _          | _           | _          | _            |              | _          | _          | _      |                      | —      | _      | _                | —                | _      | _      |        | 0000       |

| 0170                        | DOITIOOIZ                       | 15:0          |            |             |            |              |              |            |            | CHSSIZ | 2<15:0>              | t      |        |                  | i                |        | i      |        | 0000       |

| 3180                        | DCH1DSIZ                        | 31:16         | —          | —           | —          | _            | —            | —          | —          | —      | —                    | —      | —      | —                | —                | —      | —      | —      | 0000       |

| 0100                        | DOITIDOIL                       | 15:0          |            |             |            |              |              |            |            | CHDSIZ | 2<15:0>              |        |        |                  |                  |        |        |        | 0000       |

| 3190                        | DCH1SPTR                        | 31:16         | —          | —           | _          | —            | _            | —          | _          | —      | —                    | —      | _      | —                | —                | _      | —      | —      | 0000       |

|                             |                                 | 15:0          |            |             |            |              |              |            |            | CHSPT  | R<15:0>              |        |        |                  |                  |        |        |        | 0000       |

| 31A0                        | DCH1DPTR                        | 31:16         | —          | —           | —          | —            | —            | —          | —          | —      | —                    | —      | —      | —                | —                | —      | —      | —      | 0000       |

|                             |                                 | 15:0          |            |             |            |              |              |            |            | CHDPTI | R<15:0>              |        |        |                  |                  |        |        |        | 0000       |

| 31B0                        | DCH1CSIZ                        | 31:16         | _          | _           | —          |              | _            | —          | _          | —      | _                    | —      | _      | —                | _                | —      | —      | _      | 0000       |

|                             |                                 | 15:0          |            |             |            |              |              |            |            | CHCSIZ | 2<15:0>              |        |        |                  |                  |        |        |        | 0000       |

| 31C0                        | DCH1CPTR                        | 31:16         | _          | _           | —          | —            | _            | —          | _          | —      | —                    | —      | _      | —                | —                | —      | —      | _      | 0000       |

|                             |                                 | 15:0          |            |             |            |              |              |            |            | CHCPTI | ≺<15:0>              |        |        |                  |                  |        |        |        | 0000       |

| 31D0                        | DCH1DAT                         | 31:16         | _          | _           |            |              | _            |            |            | _      | _                    | —      | _      |                  |                  | _      | —      | _      | 0000       |

|                             |                                 | 15:0          |            | _           |            | _            | _            |            |            | _      |                      |        |        | CHPDA            |                  |        |        |        | 0000       |

| 31E0                        | DCH2CON                         | 31:16         | —          | _           |            | _            | _            |            |            | —      | -                    | -      | —      | —                | _                | -      | _      |        | 0000       |

| -                           |                                 | 15:0          | CHBUSY     | _           | _          | _            | _            | _          |            | CHCHNS | CHEN                 | CHAED  | CHCHN  | CHAEN            |                  | CHEDET | CHPR   | 1<1:0> | 0000       |

| 31F0                        | DCH2ECON                        | 31:16         | —          | _           | _          |              | -            | _          | _          | _      | CFORCE               | CABORT | PATEN  | CHAIR            |                  |        |        |        | 00FF       |

|                             |                                 | 15:0          |            |             |            | CHSIR        |              |            |            |        | CHSDIE               | CABORT | CHDDIE | SIRQEN<br>CHDHIE | AIRQEN<br>CHBCIE |        |        |        | FFF8       |

| 3200                        | DCH2INT                         | 31:16<br>15:0 | —          | _           | _          | _            | _            | _          | _          | _      | CHSDIE               | CHSHIE | CHDDIE | CHDHIE           | CHBCIE           | CHCCIE | CHTAIE | CHERIE | 0000       |

| -                           |                                 | 31:16         | —          | _           | _          |              | _            | _          | —          | —      | CHODIF               | CHONIF | CHUDIF | CUDULLE          | CUBCIL           | CHCCIF | CHIAIF | CHERIF | 0000       |

| 3210                        | DCH2SSA                         | 15:0          |            |             |            |              |              |            |            | CHSSA  | <31:0>               |        |        |                  |                  |        |        |        | 0000       |

| -                           |                                 | 31:16         |            |             |            |              |              |            |            |        |                      |        |        |                  |                  |        |        |        | 0000       |

| 3220                        | DCH2DSA                         | 15:0          |            |             |            |              |              |            |            | CHDSA  | <31:0>               |        |        |                  |                  |        |        |        | 0000       |

|                             |                                 | 31:16         | _          | _           | _          | _            | _            | _          | _          | _      | _                    |        | _      | _                | _                | _      | _      | _      | 0000       |

| 3230                        | DCH2SSIZ                        | 15:0          |            |             |            |              |              |            |            | CHSSIZ | /<15 <sup>.</sup> 0> |        |        |                  |                  |        |        |        | 0000       |

|                             |                                 | 31:16         | _          | _           | _          | _            | _            | _          | _          | _      |                      | _      | _      | _                | _                | _      | _      | _      | 0000       |

| 3240                        | DCH2DSIZ                        | 15:0          |            |             |            |              |              |            |            | CHDSIZ | /<15 <sup>.</sup> 0> |        |        |                  |                  |        |        |        | 0000       |

|                             |                                 | 31:16         | _          |             | _          |              |              | _          |            | _      |                      |        | _      | _                |                  |        |        |        | 0000       |

| 3250                        | DCH2SPTR                        | 15:0          |            |             |            |              |              |            |            | CHSPT  | R<15:0>              |        |        |                  |                  |        |        |        | 0000       |

|                             |                                 | 31:16         | _          |             | _          |              |              | _          |            | _      | _                    |        | _      | _                |                  |        |        | _      | 0000       |

| 3260                        | DCH2DPTR                        | 15:0          |            |             |            |              |              |            |            | CHDPT  | R<15:0>              |        |        |                  |                  |        |        |        | 0000       |

|                             |                                 | 31:16         | _          |             | _          |              |              | _          |            | _      | _                    |        | _      | _                |                  |        |        |        | 0000       |

| 3270                        | DCH2CSIZ                        | 15:0          |            |             |            |              |              |            |            | CHCSIZ | 2<15:0>              |        |        |                  |                  |        |        |        | 0000       |

| Leger                       | <b>d:</b> x = 11                |               | value on R | eset: — = I | unimplemer | nted, read a | s '0'. Reset | values are | shown in h |        |                      |        |        |                  |                  |        |        |        |            |

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | _                 | _                 |                   | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | -                 | -                 | _                 | _                 | —                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | _                 |                   | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          | _                 |                   | _                 |                   | RDWR              | [                 | DMACH<2:0>       | •                |

# REGISTER 10-2: DMASTAT: DMA STATUS REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

### bit 31-4 Unimplemented: Read as '0'

- bit 3 RDWR: Read/Write Status bit

- 1 = Last DMA bus access was a read

- 0 = Last DMA bus access was a write

- bit 2-0 **DMACH<2:0>:** DMA Channel bits These bits contain the value of the most recent active DMA channel.

### REGISTER 10-3: DMAADDR: DMA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 31:24        | DMAADDR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 23:16        | DMAADDR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8         | DMAADDR<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   |                   |                   | DMAADD            | R<7:0>            |                   |                  |                  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 DMAADDR<31:0>: DMA Module Address bits

These bits contain the address of the most recent DMA access.

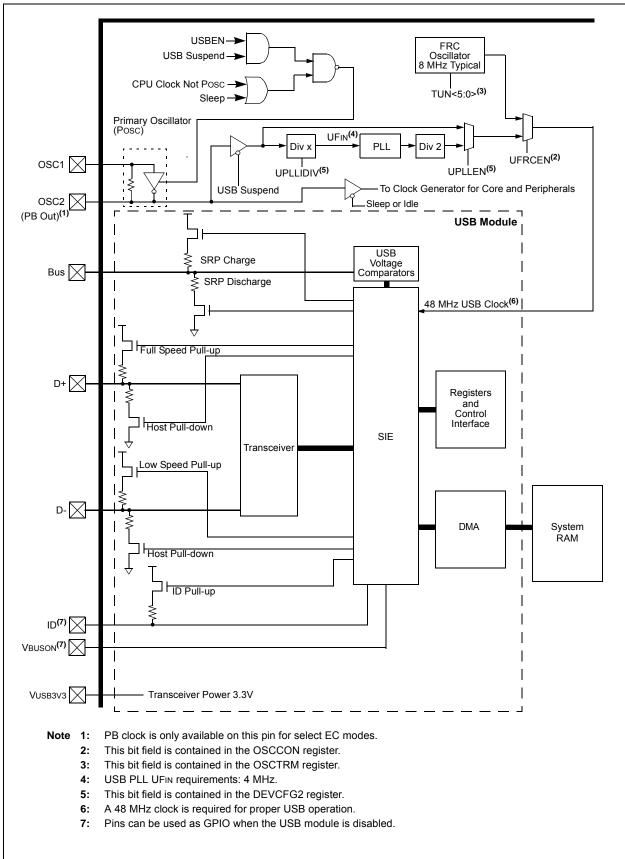

FIGURE 11-1: PIC32MX430/450/470 USB INTERFACE DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 |                   |                   |                   | —                 |                  | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -                 | _                 |                   |                   | -                 | —                 |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | -                 | _                 |                   |                   | -                 | —                 |                  | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | R/W-0            |

| 7.0          | IDIE              | T1MSECIE          | LSTATEIE          | ACTVIE            | SESVDIE           | SESENDIE          |                  | VBUSVDIE         |

## REGISTER 11-2: U10TGIE: USB OTG INTERRUPT ENABLE REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

### bit 31-8 Unimplemented: Read as '0'

- bit 7 **IDIE:** ID Interrupt Enable bit

- 1 = ID interrupt is enabled

- 0 = ID interrupt is disabled

- bit 6 T1MSECIE: 1 Millisecond Timer Interrupt Enable bit

- 1 = 1 millisecond timer interrupt is enabled

- 0 = 1 millisecond timer interrupt is disabled

- bit 5 LSTATEIE: Line State Interrupt Enable bit

- 1 = Line state interrupt is enabled

- 0 = Line state interrupt is disabled

- bit 4 ACTVIE: Bus Activity Interrupt Enable bit

- 1 = ACTIVITY interrupt is enabled

- 0 = ACTIVITY interrupt is disabled

- bit 3 SESVDIE: Session Valid Interrupt Enable bit

- 1 = Session valid interrupt is enabled

- 0 = Session valid interrupt is disabled

- bit 2 SESENDIE: B-Session End Interrupt Enable bit

- 1 = B-session end interrupt is enabled

- 0 = B-session end interrupt is disabled

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIE: A-VBUS Valid Interrupt Enable bit

- 1 = A-VBUS valid interrupt is enabled

- 0 = A-VBUS valid interrupt is disabled

## REGISTER 13-1: T1CON: TYPE A TIMER CONTROL REGISTER (CONTINUED)

- bit 2 TSYNC: Timer External Clock Input Synchronization Selection bit

- When TCS = 1:1 = External clock input is synchronized0 = External clock input is not synchronizedWhen TCS = 0:This bit is ignored.

- bit 1 **TCS:** Timer Clock Source Select bit 1 = External clock from TxCKI pin 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0 |  |  |  |

|--------------|----------------------|-------------------|---------------------|-------------------|--------------------|-------------------|--------------------|------------------|--|--|--|

| 31:24        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |  |  |  |

| 31.24        | —                    |                   | _                   | _                 |                    |                   | —                  | _                |  |  |  |

| 00.40        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |  |  |  |

| 23:16        | —                    | -                 | —                   | —                 | -                  | —                 | —                  | —                |  |  |  |

| 45.0         | R/W-0                | U-0               | R/W-0               | U-0               | U-0                | U-0               | U-0                | U-0              |  |  |  |

| 15:8         | ON <sup>(1,3)</sup>  | _                 | SIDL <sup>(4)</sup> | —                 | _                  | _                 | —                  | —                |  |  |  |

| 7.0          | R/W-0                | R/W-0             | R/W-0               | R/W-0             | R/W-0              | U-0               | R/W-0              | U-0              |  |  |  |

| 7:0          | TGATE <sup>(3)</sup> | Т                 | CKPS<2:0>(3         | 3)                | T32 <sup>(2)</sup> |                   | TCS <sup>(3)</sup> | _                |  |  |  |

### REGISTER 14-1: TxCON: TYPE B TIMER CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

### bit 31-16 **Unimplemented:** Read as '0'

- bit 15 **ON:** Timer On bit<sup>(1,3)</sup>

- 1 = Module is enabled

- 0 = Module is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit<sup>(4)</sup>

- 1 = Discontinue operation when device enters Idle mode0 = Continue operation even in Idle mode

### bit 12-8 Unimplemented: Read as '0'

- bit 7 **TGATE:** Timer Gated Time Accumulation Enable bit<sup>(3)</sup>

- When TCS = 1:

This bit is ignored and is read as '0'.

When TCS = 0:

- 1 = Gated time accumulation is enabled

- 0 = Gated time accumulation is disabled

### bit 6-4 TCKPS<2:0>: Timer Input Clock Prescale Select bits<sup>(3)</sup>

- 111 = 1:256 prescale value

- 110 = 1:64 prescale value

- 101 = 1:32 prescale value

- 100 = 1:16 prescale value

- 011 = 1:8 prescale value

- 010 = 1:4 prescale value

- 001 = 1:2 prescale value

- 000 = 1:1 prescale value

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit is available only on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer3 and Timer5). All timer functions are set through the even numbered timers.

- 4: While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

# 15.1 Watchdog Timer Control Registers

| DS60001185F-page |  |

|------------------|--|

| е<br>—           |  |

| 78               |  |

# TABLE 15-1: WATCHDOG TIMER CONTROL REGISTER MAP

| ess                        |                                 | æ         |       |       |       |       |       |       |      |      |      |      |      | s    |      |      |      |      |            |

|----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|------|------------|

| Virtual Addres<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 0000                       | WDTCON                          | 31:16     | _     | _     | _     | _     | -     | -     | —    | —    | _    | —    | —    | _    | _    | _    | —    | —    | 0000       |

| 0000                       | WDICON                          | 15:0      | D ON  |       |       |       |       |       |      |      |      | 0000 |      |      |      |      |      |      |            |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| REGIST    | ER 18-1:                   | SPIxCON: S                          | SPI CONTROL REGISTER (CONTINUED)                                                                                                                               |

|-----------|----------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 17    |                            |                                     | e Edge Select bit (Framed SPI mode only)                                                                                                                       |

|           |                            |                                     | on pulse coincides with the first bit clock                                                                                                                    |

| h:+ 40    |                            |                                     | on pulse precedes the first bit clock<br>fer Enable bit <sup>(2)</sup>                                                                                         |

| bit 16    |                            | ed Buffer mo                        |                                                                                                                                                                |

|           |                            | ed Buffer mod                       |                                                                                                                                                                |

| bit 15    |                            | ripheral On bi                      |                                                                                                                                                                |

|           |                            | ripheral is ena                     |                                                                                                                                                                |

|           |                            | ripheral is dis                     |                                                                                                                                                                |

| bit 14    | Unimpleme                  | ented: Read a                       | as '0'                                                                                                                                                         |

| bit 13    | SIDL: Stop                 | in Idle Mode b                      | pit                                                                                                                                                            |

|           |                            | •                                   | n when CPU enters in Idle mode                                                                                                                                 |

|           |                            | ue operation i                      |                                                                                                                                                                |

| bit 12    |                            | isable SDOx                         |                                                                                                                                                                |

|           |                            |                                     | d by the module. Pin is controlled by associated PORT register<br>ed by the module                                                                             |

| bit 11-10 |                            |                                     | t Communication Select bits                                                                                                                                    |

|           | When AUD                   |                                     | Communication Select bits                                                                                                                                      |

|           | MODE32                     | MODE16                              | Communication                                                                                                                                                  |

|           | 1                          | 1                                   | 24-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame                                                                                                          |

|           | 1                          | 0                                   | 32-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame                                                                                                          |

|           | 0                          | 1                                   | 16-bit Data, 16-bit FIFO, 32-bit Channel/64-bit Frame                                                                                                          |

|           | 0                          | 0                                   | 16-bit Data, 16-bit FIFO, 16-bit Channel/32-bit Frame                                                                                                          |

|           | When AUD                   | <b>FN =</b> 0:                      |                                                                                                                                                                |

|           | MODE32                     | MODE16                              | Communication                                                                                                                                                  |

|           | 1                          | x                                   | 32-bit                                                                                                                                                         |

|           | 0                          | 1                                   | 16-bit                                                                                                                                                         |

|           | 0                          | 0                                   | 8-bit                                                                                                                                                          |

| bit 9     |                            |                                     | nple Phase bit                                                                                                                                                 |

|           |                            | <u>le (MSTEN =</u><br>ata sampled a | $\pm$ ).<br>at end of data output time                                                                                                                         |

|           |                            |                                     | at middle of data output time                                                                                                                                  |

|           |                            | • (MSTEN = 0                        |                                                                                                                                                                |

|           |                            | -                                   | en SPI is used in Slave mode. The module always uses SMP = 0.                                                                                                  |

| bit 8     |                            | lock Edge Se                        |                                                                                                                                                                |

|           |                            |                                     | anges on transition from active clock state to Idle clock state (see CKP bit)<br>anges on transition from Idle clock state to active clock state (see CKP bit) |

| bit 7     |                            | -                                   | ble (Slave mode) bit                                                                                                                                           |

|           |                            | n used for Sla                      |                                                                                                                                                                |

|           |                            |                                     | Slave mode, pin controlled by port function.                                                                                                                   |

| bit 6     |                            | Polarity Sele                       |                                                                                                                                                                |

|           | 1 = Idle sta               | te for clock is                     | a high level; active state is a low level                                                                                                                      |

|           |                            |                                     | a low level; active state is a high level                                                                                                                      |

| bit 5     |                            | aster Mode Er                       | hable bit                                                                                                                                                      |

|           | 1 = Master<br>0 = Slave r  |                                     |                                                                                                                                                                |

|           |                            | lieue                               |                                                                                                                                                                |

| Note 1:   | When using                 | g the 1:1 PBC                       | LK divisor, the user software should not read or write the peripheral's SFRs in the                                                                            |

|           |                            | -                                   | ely following the instruction that clears the module's ON bit.                                                                                                 |

| 2:        | This bit car               | n only be writte                    | en when the ON bit = 0.                                                                                                                                        |

| 3:        | This bit is r<br>mode (FRN |                                     | e Framed SPI mode. The user should program this bit to '0' for the Framed SPI                                                                                  |

| 4:        | -                          | -                                   | PI module functions as if the CKP bit is equal to '1', regardless of the actual value                                                                          |

|           | of CKP.                    | <u> </u>                            |                                                                                                                                                                |

|           |                            |                                     |                                                                                                                                                                |

| REGISTE | ER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                              |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 8   | <ul> <li>TRMT: Transmit Shift Register is Empty bit (read-only)</li> <li>1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed)</li> <li>0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer</li> </ul>                                                                                                                              |

| bit 7-6 | URXISEL<1:0>: Receive Interrupt Mode Selection bit<br>11 = Reserved; do not use<br>10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full (i.e., has 6 or more data characters)<br>01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full (i.e., has 4 or more data characters)<br>00 = Interrupt flag bit is asserted while receive buffer is not empty (i.e., has at least 1 data character) |

| bit 5   | <ul> <li>ADDEN: Address Character Detect bit (bit 8 of received data = 1)</li> <li>1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                                                                                                                                                               |

| bit 4   | RIDLE: Receiver Idle bit (read-only)<br>1 = Receiver is Idle<br>0 = Data is being received                                                                                                                                                                                                                                                                                                                                                 |

| bit 3   | <ul> <li>PERR: Parity Error Status bit (read-only)</li> <li>1 = Parity error has been detected for the current character</li> <li>0 = Parity error has not been detected</li> </ul>                                                                                                                                                                                                                                                        |

| bit 2   | <ul> <li>FERR: Framing Error Status bit (read-only)</li> <li>1 = Framing error has been detected for the current character</li> <li>0 = Framing error has not been detected</li> </ul>                                                                                                                                                                                                                                                     |

| bit 1   | OERR: Receive Buffer Overrun Error Status bit.                                                                                                                                                                                                                                                                                                                                                                                             |

|         | This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and RSR to empty state.                                                                                                                                                                                                                                                                               |

|         | <ul><li>1 = Receive buffer has overflowed</li><li>0 = Receive buffer has not overflowed</li></ul>                                                                                                                                                                                                                                                                                                                                          |

- bit 0 URXDA: Receive Buffer Data Available bit (read-only)

- 1 = Receive buffer has data, at least one more character can be read

- 0 = Receive buffer is empty

NOTES:

### REGISTER 22-2: RTCALRM: RTC ALARM CONTROL REGISTER (CONTINUED)

bit 7-0 ARPT<7:0>: Alarm Repeat Counter Value bits<sup>(3)</sup> 11111111 = Alarm will trigger 256 times

0000000 = Alarm will trigger one time

The counter decrements on any alarm event. The counter only rolls over from 0x00 to 0xFF if CHIME = 1.

- **Note 1:** Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIME = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

Note: This register is reset only on a Power-on Reset (POR).

#### 23.1 **Control Registers**

# TABLE 23-1: ADC REGISTER MAP

| ess                         |                        |               |        |           |        |        |        |           |           | Bi          | ts       |           |        |         |        |           |        |        |            |

|-----------------------------|------------------------|---------------|--------|-----------|--------|--------|--------|-----------|-----------|-------------|----------|-----------|--------|---------|--------|-----------|--------|--------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name       | Bit Range     | 31/15  | 30/14     | 29/13  | 28/12  | 27/11  | 26/10     | 25/9      | 24/8        | 23/7     | 22/6      | 21/5   | 20/4    | 19/3   | 18/2      | 17/1   | 16/0   | All Resets |

| 9000                        | AD1CON1 <sup>(1)</sup> | 31:16         |        | _         |        |        |        |           |           | _           |          | _         |        |         |        |           |        |        | 000        |

|                             |                        | 15:0          | ON     | _         | SIDL   | —      | _      |           | FORM<2:0> |             |          | SSRC<2:0> |        | CLRASAM | _      | ASAM      | SAMP   | DONE   | 000        |

| 9010                        | AD1CON2 <sup>(1)</sup> | 31:16         | _      | —         | —      | —      | _      | —         | —         | —           | -        | —         | —      | -       | —      | —         | —      | —      | 000        |

|                             |                        | 15:0          |        | VCFG<2:0> |        | OFFCAL |        | CSCNA     | _         |             | BUFS     | _         |        | SMPI    | <3:0>  |           | BUFM   | ALTS   | 000        |

| 9020                        | AD1CON3 <sup>(1)</sup> | 31:16         | -      | _         | _      | —      | _      | —         | _         | —           | _        | _         | _      |         | —      | —         | —      |        | 0000       |

|                             |                        | 15:0          | ADRC   | —         |        |        |        | SAMC<4:0  |           |             | 0110114  |           |        | ADCS    |        |           |        |        | 0000       |

| 9040                        | AD1CHS(1)              | 31:16         | CH0NB  | —         |        |        |        | CH0SB<4:0 |           |             | CH0NA    |           |        |         |        | CH0SA<4:0 |        |        | 0000       |

|                             |                        | 15:0          |        | -         | —      | —      | -      | -         | -         | -           | -        | -         | —      | —       | -      | -         | -      | -      | 0000       |

| 9050                        | AD1CSSL <sup>(1)</sup> | 31:16         | -      | CSSL30    | CSSL29 | CSSL28 | CSSL27 | CSSL26    | CSSL25    | CSSL24      | CSSL23   | CSSL22    | CSSL21 | CSSL20  | CSSL19 | CSSL18    | CSSL17 | CSSL16 | _          |

|                             |                        | 15:0          | CSSL15 | CSSL14    | CSSL13 | CSSL12 | CSSL11 | CSSL10    | CSSL9     | CSSL8       | CSSL7    | CSSL6     | CSSL5  | CSSL4   | CSSL3  | CSSL2     | CSSL1  | CSSL0  | 0000       |

| 9070                        | ADC1BUF0               | 31:16<br>15:0 |        |           |        |        |        |           | ADC Res   | sult Word 0 | (ADC1BUF | 0<31:0>)  |        |         |        |           |        |        | 0000       |

|                             |                        |               |        |           |        |        |        |           |           |             |          |           |        |         |        |           |        |        | 0000       |

| 9080                        | ADC1BUF1               | 31:16<br>15:0 |        |           |        |        |        |           | ADC Res   | sult Word 1 | (ADC1BUF | 1<31:0>)  |        |         |        |           |        |        | 0000       |

|                             |                        |               |        |           |        |        |        |           |           |             |          |           |        |         |        |           |        |        | 0000       |

| 9090                        | ADC1BUF2               | 31:16<br>15:0 |        |           |        |        |        |           | ADC Res   | sult Word 2 | (ADC1BUF | 2<31:0>)  |        |         |        |           |        |        | 0000       |

|                             |                        | 31:16         |        |           |        |        |        |           |           |             |          |           |        |         |        |           |        |        | 0000       |

| 90A0                        | ADC1BUF3               | 15:0          |        |           |        |        |        |           | ADC Res   | sult Word 3 | (ADC1BUF | 3<31:0>)  |        |         |        |           |        |        | 0000       |

|                             |                        | 31:16         |        |           |        |        |        |           |           |             |          |           |        |         |        |           |        |        | 0000       |

| 90B0                        | ADC1BUF4               | 15:0          |        |           |        |        |        |           | ADC Res   | sult Word 4 | (ADC1BUF | 4<31:0>)  |        |         |        |           |        |        | 0000       |

|                             |                        | 31:16         |        |           |        |        |        |           |           |             |          |           |        |         |        |           |        |        | 0000       |

| 90C0                        | ADC1BUF5               | 15:0          |        |           |        |        |        |           | ADC Res   | sult Word 5 | (ADC1BUF | 5<31:0>)  |        |         |        |           |        |        | 0000       |

|                             |                        | 31:16         |        |           |        |        |        |           |           |             |          |           |        |         |        |           |        |        | 0000       |

| 90D0                        | ADC1BUF6               | 15:0          |        |           |        |        |        |           | ADC Res   | sult Word 6 | (ADC1BUF | 6<31:0>)  |        |         |        |           |        |        | 0000       |

|                             |                        | 31:16         |        |           |        |        |        |           |           |             |          |           |        |         |        |           |        |        | 0000       |

| 90E0                        | ADC1BUF7               | 15:0          |        |           |        |        |        |           | ADC Res   | sult Word 7 | (ADC1BUF | 7<31:0>)  |        |         |        |           |        |        | 0000       |

|                             |                        | 31:16         |        |           |        |        |        |           |           |             |          |           |        |         |        |           |        |        | 0000       |

| 90F0                        | ADC1BUF8               | 15:0          |        |           |        |        |        |           | ADC Res   | sult Word 8 | (ADC1BUF | 8<31:0>)  |        |         |        |           |        |        | 0000       |

|                             |                        | 31:16         |        |           |        |        |        |           |           |             |          |           |        |         |        |           |        |        | 0000       |

| 9100                        | ADC1BUF9               | 15:0          |        |           |        |        |        |           | ADC Res   | sult Word 9 | (ADC1BUF | 9<31:0>)  |        |         |        |           |        |        | 0000       |

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for details. Note 1:

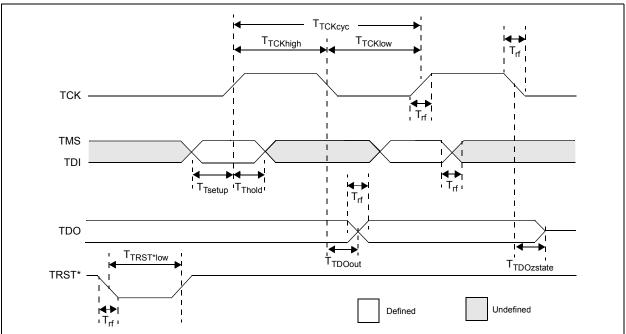

## FIGURE 31-23: EJTAG TIMING CHARACTERISTICS

### TABLE 31-43: EJTAG TIMING REQUIREMENTS

| АС СНА        | RACTERISTI | cs                                               | (unles |      | ise state | anditions: 2.3V to 3.6V<br>ed)<br>$0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |  |  |

|---------------|------------|--------------------------------------------------|--------|------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Param.<br>No. | Symbol     | Description <sup>(1)</sup>                       | Min.   | Max. | Units     | Conditions                                                                                                                                                                                           |  |  |

| EJ1           | Ттсксүс    | TCK Cycle Time                                   | 25     | —    | ns        | —                                                                                                                                                                                                    |  |  |

| EJ2           | Ттскнідн   | TCK High Time                                    | 10     | —    | ns        | —                                                                                                                                                                                                    |  |  |

| EJ3           | TTCKLOW    | TCK Low Time                                     | 10     | —    | ns        | —                                                                                                                                                                                                    |  |  |

| EJ4           | TTSETUP    | TAP Signals Setup Time Before<br>Rising TCK      | 5      | —    | ns        | _                                                                                                                                                                                                    |  |  |

| EJ5           | TTHOLD     | TAP Signals Hold Time After<br>Rising TCK        | 3      | _    | ns        | —                                                                                                                                                                                                    |  |  |

| EJ6           | Ττροουτ    | TDO Output Delay Time from<br>Falling TCK        |        | 5    | ns        | —                                                                                                                                                                                                    |  |  |

| EJ7           | TTDOZSTATE | TDO 3-State Delay Time from<br>Falling TCK       | _      | 5    | ns        | —                                                                                                                                                                                                    |  |  |

| EJ8           | TTRSTLOW   | TRST Low Time                                    | 25     | —    | ns        |                                                                                                                                                                                                      |  |  |

| EJ9           | Trf        | TAP Signals Rise/Fall Time, All Input and Output |        |      | ns        | _                                                                                                                                                                                                    |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

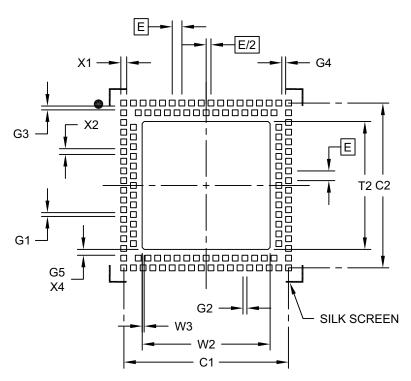

# 124-Very Thin Leadless Array Package (TL) – 9x9x0.9 mm Body [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                                      | Units |      |          |      |  |  |  |  |  |

|--------------------------------------|-------|------|----------|------|--|--|--|--|--|

| Dimension                            | MIN   | NOM  | MAX      |      |  |  |  |  |  |

| Contact Pitch                        | E     |      | 0.50 BSC |      |  |  |  |  |  |

| Pad Clearance                        | G1    | 0.20 |          |      |  |  |  |  |  |

| Pad Clearance                        | G2    | 0.20 |          |      |  |  |  |  |  |

| Pad Clearance                        | G3    | 0.20 |          |      |  |  |  |  |  |

| Pad Clearance                        | G4    | 0.20 |          |      |  |  |  |  |  |

| Contact to Center Pad Clearance (X4) | G5    | 0.30 |          |      |  |  |  |  |  |

| Optional Center Pad Width            | T2    |      |          | 6.60 |  |  |  |  |  |

| Optional Center Pad Length           | W2    |      |          | 6.60 |  |  |  |  |  |

| Optional Center Pad Chamfer (X4)     | W3    |      | 0.10     |      |  |  |  |  |  |

| Contact Pad Spacing                  | C1    |      | 8.50     |      |  |  |  |  |  |

| Contact Pad Spacing                  | C2    |      | 8.50     |      |  |  |  |  |  |

| Contact Pad Width (X124)             | X1    |      |          | 0.30 |  |  |  |  |  |

| Contact Pad Length (X124)            | X2    |      |          | 0.30 |  |  |  |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2193A