Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx350f256h-v-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 7: PIN NAMES FOR 124-PIN DEVICES

| 124               | -PIN VTLA (BOTTOM VIEW) <sup>(1,2,3,4)</sup>                             | 17       |                   |          |            | A        | 34                        |

|-------------------|--------------------------------------------------------------------------|----------|-------------------|----------|------------|----------|---------------------------|

|                   | A                                                                        | 17       | l                 | B13      | B29        |          | Conductive<br>Thermal Pad |

|                   | PIC32MX430F064L<br>PIC32MX450F128L<br>PIC32MX450F256L<br>PIC32MX470F512L |          |                   | B1<br>Bt | 56         | B41      | A51                       |

|                   |                                                                          |          | A1                |          |            |          |                           |

|                   | Polarit                                                                  | y Indica | ator              | A        | 68         |          |                           |

| Package<br>Bump # | Full Pin Name                                                            |          | Package<br>Bump # |          |            | Full Pin | Name                      |

| A1                | No Connect                                                               |          | A38               | D-       |            |          |                           |

| A2                | RG15                                                                     |          | A39               | SCL2/F   | RA2        |          |                           |

| A3                | Vss                                                                      |          | A40               | TDI/CT   | ED9/RA4    |          |                           |

| A4                | AN23/PMD6/RE6                                                            |          | A41               | Vdd      |            |          |                           |

| A5                | RPC1/RC1                                                                 |          | A42               |          | CLKO/RC15  |          |                           |

| A6                | RPC3/RC3                                                                 |          | A43               | Vss      |            |          |                           |

| A7                | AN16/C1IND/RPG6/SCK2/PMA5/RG6                                            |          | A44               | SDA1/F   | RPA15/RA15 | 5        |                           |

| A8                | AN18/C2IND/RPG8/PMA3/RG8                                                 |          | A45               | RPD9/F   | 209        |          |                           |

| A9                | AN19/C2INC/RPG9/PMA2/RG9                                                 |          | A46               |          | PMCS1/RD   | 11       |                           |

| A10               | VDD                                                                      |          | A47               |          | RPC13/RC   |          |                           |

| A11               | RPE8/RE8                                                                 |          | A48               | VDD      |            |          |                           |

| A12               | AN5/C1INA/RPB5/VBUSON/RB5                                                |          | A49               | No Cor   | nect       |          |                           |

| A13               | PGED3/AN3/C2INA/RPB3/RB3                                                 |          | A50               | No Cor   |            |          |                           |

| A14               | VDD                                                                      |          | A51               | No Cor   | nect       |          |                           |

| A15               | PGEC1/AN1/RPB1/CTED12/RB1                                                |          | A52               |          | RPD1/RD1   |          |                           |

| A16               | No Connect                                                               |          | A53               | AN26/F   | RPD3/RD3   |          |                           |

| A17               | No Connect                                                               |          | A54               | PMD13    |            |          |                           |

| A18               | No Connect                                                               |          | A55               | _        | PMRD/RD5   |          |                           |

| A19               | No Connect                                                               |          | A56               | PMD15    | -          |          |                           |

| A20               | PGEC2/AN6/RPB6/RB6                                                       |          | A50<br>A57        | No Cor   |            |          |                           |

| A20<br>A21        | VREF-/CVREF-/PMA7/RA9                                                    | _        |                   | No Cor   |            |          |                           |

| A21<br>A22        | AVDD                                                                     | _        | A58<br>A59        | VDD      |            |          |                           |

| A22<br>A23        | AN8/RPB8/CTED10/RB8                                                      | $\dashv$ | A59<br>A60        |          | MD10/RF1   |          |                           |

| A23<br>A24        | CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                    | _        | A60<br>A61        | _        | PMD8/RG0   |          |                           |

| A24<br>A25        | Vss                                                                      | _        | A61<br>A62        |          | TED8/RA7   |          |                           |

| A25               | TCK/CTED2/RA1                                                            | _        | A62               | Vss      |            |          |                           |

| A20               | RPF12/RF12                                                               |          | A64               | PMD1/    | RF1        |          |                           |

| A28               | AN13/PMA10/RB13                                                          | $\dashv$ | A65               | TRD1/F   |            |          |                           |

| A29               | AN15/RPB15/OCFB/CTED6/PMA0/RB15                                          | -        | A66               |          | MD2/RE2    |          |                           |

| A30               | VDD                                                                      |          | A67               | _        | MD2/RE2    |          |                           |

| A31               | RPD15/RD15                                                               | -        | A68               | No Cor   |            |          |                           |

| A32               | RPF5/PMA8/RF5                                                            |          | B1                | VDD      |            |          |                           |

| A33               | No Connect                                                               | $\dashv$ | B1<br>B2          |          | RPE5/PMD5  | /RE5     |                           |

| A33<br>A34        | No Connect                                                               | _        | B2<br>B3          | -        | MD7/RE7    |          |                           |

| A34<br>A35        | USBID/RF3                                                                | _        | B3<br>B4          | RPC2/F   |            |          |                           |

| A35<br>A36        | RPF2/RF2                                                                 | _        |                   |          | CTED7/RC4  |          |                           |

| 700               |                                                                          | 1        | B5                |          |            |          |                           |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See Section 12.0 "I/O Ports" for more information.

3: Shaded package bumps are 5V tolerant.

4: It is recommended that the user connect the printed circuit board (PCB) ground to the conductive thermal pad on the bottom of the package. And to not run non-Vss PCB traces under the conductive thermal pad on the same side of the PCB layout.

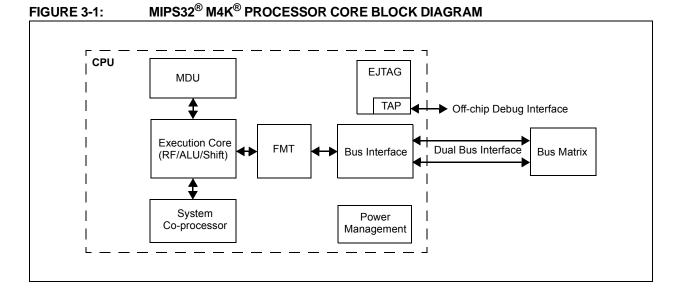

# 3.0 CPU

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 2.** "CPU" (DS60001113), which is available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). Resources for the MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core are available at http://www.imgtec.com.

The the MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core is the heart of the PIC32MX330/350/370/430/450/470 device processor. The CPU fetches instructions, decodes each instruction, fetches source operands, executes each instruction and writes the results of instruction execution to the proper destinations.

# 3.1 Features

- 5-stage pipeline

- · 32-bit address and data paths

- MIPS32<sup>®</sup> Enhanced Architecture (Release 2):

- Multiply-accumulate and multiply-subtract instructions

- Targeted multiply instruction

- Zero/One detect instructions

- WAIT instruction

- Conditional move instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- GPR shadow registers to minimize latency for interrupt handlers

- Bit field manipulation instructions

- MIPS16e<sup>®</sup> Code Compression:

- 16-bit encoding of 32-bit instructions to improve code density

- Special PC-relative instructions for efficient loading of addresses and constants

- SAVE and RESTORE macro instructions for setting up and tearing down stack frames within subroutines

- Improved support for handling 8 and 16-bit data types

- Simple Fixed Mapping Translation (FMT) Mechanism:

- Simple Dual Bus Interface:

- Independent 32-bit address and data buses

- Transactions can be aborted to improve interrupt latency

- Autonomous Multiply/Divide Unit (MDU):

- Maximum issue rate of one 32x16 multiply per clock

- Maximum issue rate of one 32x32 multiply every other clock

- Early-in iterative divide. Minimum 11 and maximum 33 clock latency (dividend (*rs*) sign extension-dependent)

- · Power Control:

- Minimum frequency: 0 MHz

- Low-Power mode (triggered by WAIT instruction)

- Extensive use of local gated clocks

- EJTAG Debug and Instruction Trace:

- Support for single stepping

- Virtual instruction and data address/value

- Breakpoints

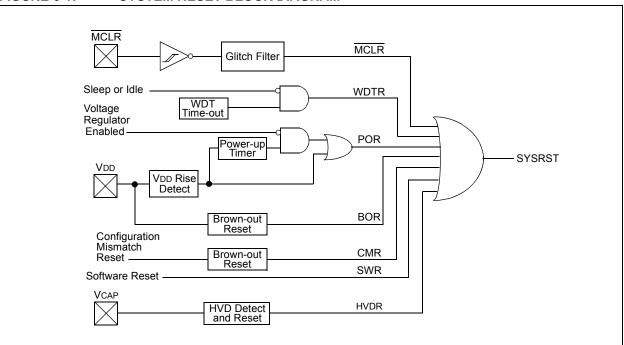

# 6.0 RESETS

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 7.** "**Resets**" (DS60001118), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). The Reset module combines all Reset sources and controls the device Master Reset signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- MCLR: Master Clear Reset pin

- · SWR: Software Reset

- WDTR: Watchdog Timer Reset

- · BOR: Brown-out Reset

- CMR: Configuration Mismatch Reset

- HVDR: High Voltage Detect Reset

A simplified block diagram of the Reset module is illustrated in Figure 6-1.

# FIGURE 6-1: SYSTEM RESET BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|

| 04.04        | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0                | U-0                |

| 31:24        | _                 | —                 | HVDR              | —                 | _                 |                   | _                  | —                  |

| 00.40        | U-0                | U-0                |

| 23:16        | _                 | —                 | _                 | —                 | _                 |                   | _                  | —                  |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0, HS          | R/W-0              |

| 15:8         | —                 | —                 | —                 | —                 | _                 | —                 | CMR                | VREGS              |

| 7.0          | R/W-0, HS         | R/W-0, HS         | U-0               | R/W-0, HS         | R/W-0, HS         | R/W-0, HS         | R/W-1, HS          | R/W-1, HS          |

| 7:0          | EXTR              | SWR               |                   | WDTO              | SLEEP             | IDLE              | BOR <sup>(1)</sup> | POR <sup>(1)</sup> |

#### **REGISTER 6-1: RCON: RESET CONTROL REGISTER**

| Legend:           | HS = Set by hardware | e                    |                    |

|-------------------|----------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared | x = Bit is unknown |

bit 31-30 Unimplemented: Read as '0'

- bit 29 HVDR: High Voltage Detect Reset Flag bit 1 = High Voltage Detect (HVD) Reset has occurred 0 = HVD Reset has not occurred bit 28-10 Unimplemented: Read as '0' bit 9 **CMR:** Configuration Mismatch Reset Flag bit 1 = Configuration mismatch Reset has occurred 0 = Configuration mismatch Reset has not occurred bit 8 VREGS: Voltage Regulator Standby Enable bit 1 = Regulator is enabled and is on during Sleep mode 0 = Regulator is set to Stand-by Tracking mode EXTR: External Reset (MCLR) Pin Flag bit bit 7 1 = Master Clear (pin) Reset has occurred 0 = Master Clear (pin) Reset has not occurred bit 6 SWR: Software Reset Flag bit 1 = Software Reset was executed 0 = Software Reset as not executed bit 5 Unimplemented: Read as '0' bit 4 WDTO: Watchdog Timer Time-out Flag bit 1 = WDT Time-out has occurred 0 = WDT Time-out has not occurred bit 3 **SLEEP:** Wake From Sleep Flag bit 1 = Device was in Sleep mode 0 = Device was not in Sleep mode bit 2 **IDLE:** Wake From Idle Flag bit 1 = Device was in Idle mode 0 = Device was not in Idle mode **BOR:** Brown-out Reset Flag bit<sup>(1)</sup> bit 1 1 = Brown-out Reset has occurred 0 = Brown-out Reset has not occurred bit 0 **POR:** Power-on Reset Flag bit<sup>(1)</sup> 1 = Power-on Reset has occurred

- 0 = Power-on Reset has not occurred

**Note 1:** User software must clear this bit to view next detection.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|

| 24.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |  |  |

| 31:24        |                   |                   |                   | CHEW1<            | :31:24>           |                   |                  |                  |  |  |  |  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |  |  |

| 23:16        | CHEW1<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |  |  |

| 15:8         |                   |                   |                   | CHEW1             | <15:8>            |                   |                  |                  |  |  |  |  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | CHEW1             | <7:0>             |                   |                  |                  |  |  |  |  |  |  |  |

## REGISTER 9-6: CHEW1: CACHE WORD 1

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-0 **CHEW1<31:0>:** Word 1 of the cache line selected by the CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

# REGISTER 9-7: CHEW2: CACHE WORD 2

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 24.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x R/W-x       |                   | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |  |

| 31:24        |                   |                   |                   | CHEW2<            | 31:24>            |                   |                  |                  |  |  |  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |  |

| 23:16        | CHEW2<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |  |

| 15:8         |                   |                   |                   | CHEW2             | <15:8>            |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | CHEW2             | <7:0>             |                   |                  |                  |  |  |  |  |  |  |

| Legend:           |                  |                                    |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

bit 31-0 **CHEW2<31:0>:** Word 2 of the cache line selected by the CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | -                 | —                 | _                 | _                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | -                 | -                 | —                 | _                 | _                | —                |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         |                   | —                 | _                 | _                 | —                 |                   | _                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHPDAT            | 7:0>              |                   |                  |                  |

# REGISTER 10-18: DCHxDAT: DMA CHANNEL 'x' PATTERN DATA REGISTER

# Legend:

| ========          |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

### bit 31-8 Unimplemented: Read as '0'

## bit 7-0 **CHPDAT<7:0>:** Channel Data Register bits

Pattern Terminate mode: Data to be matched must be stored in this register to allow terminate on match.

All other modes: Unused.

|                             |                                 | P         | C32MX         | 430F064       | L, PIC3       | 2MX450        | F128L,        | PIC32M        | X450F2       | 56L, AN      | ID PIC3      | 2MX47        | 0F512L       | DEVIC        | ES ONL       | .Y           |              |              |               |

|-----------------------------|---------------------------------|-----------|---------------|---------------|---------------|---------------|---------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| ess                         |                                 |           |               |               |               |               |               |               |              | Bits         | 6            |              |              |              |              |              |              |              |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14         | 29/13         | 28/12         | 27/11         | 26/10         | 25/9         | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6300                        | ANSELD                          | 31:16     | —             | —             | —             | —             | —             |               | —            | —            | —            |              | —            | —            | —            |              | —            |              | 0000          |

|                             |                                 | 15:0      | _             | —             | —             | _             | —             | —             | —            | —            | —            | _            | —            | —            | ANSELD3      | ANSELD2      | ANSELD1      | _            | 000E          |

| 6310                        | TRISD                           | 31:16     | _             | —             | —             | —             | _             | —             | —            | —            | —            |              | —            | _            | _            | _            | —            | _            | 0000          |

|                             | _                               | 15:0      | TRISD15       | TRISD14       | TRISD13       | TRISD12       | TRISD11       | TRISD10       | TRISD9       | TRISD8       | TRISD7       | TRISD6       | TRISD5       | TRISD4       | TRISD3       | TRISD2       | TRISD1       | TRISD0       | xxxx          |

| 5320                        | PORTD                           | 31:16     | _             | —             | _             | —             | —             | —             | —            | —            | —            |              | —            | —            |              | —            | —            | _            | 0000          |

|                             | _                               | 15:0      | RD15          | RD14          | RD13          | RD12          | RD11          | RD10          | RD9          | RD8          | RD7          | RD6          | RD5          | RD4          | RD3          | RD2          | RD1          | RD0          | xxxx          |

| 6330                        | LATD                            | 31:16     |               | —             | —             | —             | —             | —             | —            | —            | —            | —            | —            | —            | —            |              | —            | —            | 0000          |

|                             |                                 | 15:0      | LATD15        | LATD14        | LATD13        | LATD12        | LATD11        | LATD10        | LATD9        | LATD8        | LATD7        | LATD6        | LATD5        | LATD4        | LATD3        | LATD2        | LATD1        | LATD0        | XXXX          |

| 6340                        | ODCD                            | 31:16     | —             | —             | —             | —             | —             | —             | —            | —            | —            | —            | —            | —            | —            | —            | —            | _            | 0000          |

|                             |                                 | 15:0      | ODCD15        | ODCD14        | ODCD13        | ODCD12        | ODCD11        | ODCD10        | ODCD9        | ODCD8        | ODCD7        | ODCD6        | ODCD5        | ODCD4        | ODCD3        | ODCD2        | ODCD1        | ODCD0        | xxxx          |

| 6350                        | CNPUD                           | 31:16     | -             | —             | —             | —             | —             | -             | —            | —            | —            | —            | —            | —            | —            | —            | —            | -            | 0000          |

|                             |                                 | 15:0      | CNPUD15       | CNPUD14       | CNPUD13       | CNPUD12       | CNPUD11       | CNPUD10       |              | CNPUD8       | CNPUD7       | CNPUD6       | CNPUD5       | CNPUD4       | CNPUD3       | CNPUD2       | CNPUD1       | CNPUD0       | xxxx          |

| 6360                        | CNPDD                           | 31:16     | -             | —             | —             | —             | —             | -             | —            | —            | —            | —            | _            | —            | —            | —            | —            | _            | 0000          |

|                             |                                 |           | CNPDD15       | -             | CNPDD13       | CNPDD12       | CNPDD11       | CNPDD10       |              | CNPDD8       | -            | CNPDD6       |              | CNPDD4       | CNPDD3       | CNPDD2       | CNPDD1       | CNPDD0       | XXXX          |

| 6370                        | CNCOND                          | 31:16     | _             |               | -             |               |               |               |              |              |              |              |              |              |              | _            |              |              | 0000          |

|                             |                                 | 15:0      | ON            |               | SIDL          |               |               |               |              |              |              |              |              |              |              | _            |              |              | 0000          |

| 6380                        | CNEND                           | 31:16     | -             | -             | -             | -             |               |               | -            | -            | -            |              | -            | -            | -            | -            |              |              | 0000          |

|                             |                                 | 15:0      | CNIED15       | CNIED14       | CNIED13       | CNIED12       | CNIED11       | CNIED10       | CNIED9       | CNIED8       | CNIED7       | CNIED6       | CNIED5       | CNIED4       | CNIED3       | CNIED2       | CNIED1       | CNIED0       | XXXX          |

| 6200                        |                                 | 31:16     | -             | -             | —             | —             | —             | -             | -            | -            | -            | -            | —            | -            | —            | —            | —            | -            | 0000          |

| 6390                        | CNSTATD                         | 15:0      | CNS<br>TATD15 | CN<br>STATD14 | CN<br>STATD13 | CN<br>STATD12 | CN<br>STATD11 | CN<br>STATD10 | CN<br>STATD9 | CN<br>STATD8 | CN<br>STATD7 | CN<br>STATD6 | CN<br>STATD5 | CN<br>STATD4 | CN<br>STATD3 | CN<br>STATD2 | CN<br>STATD1 | CN<br>STATD0 | xxxx          |

# TABLE 12-7: PORTD REGISTER MAP FOR PIC32MX330F064L, PIC32MX350F128L, PIC32MX350F256L, PIC32MX370F512L,

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

# 18.1 Control Registers

# TABLE 18-1: SPI2 AND SPI2 REGISTER MAP

| ess                         |                                 | 6         |               |         |        |              |              |              |           | Bit    | S       |        |        |          |             |          |        |         |            |

|-----------------------------|---------------------------------|-----------|---------------|---------|--------|--------------|--------------|--------------|-----------|--------|---------|--------|--------|----------|-------------|----------|--------|---------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14   | 29/13  | 28/12        | 27/11        | 26/10        | 25/9      | 24/8   | 23/7    | 22/6   | 21/5   | 20/4     | 19/3        | 18/2     | 17/1   | 16/0    | All Resets |

| 5800                        | SPI1CON                         | 31:16     | FRMEN         | FRMSYNC | FRMPOL | MSSEN        | FRMSYPW      | FF           | RMCNT<2:0 | )>     | MCLKSEL | —      |        |          |             | _        | SPIFE  | ENHBUF  | 0000       |

| 3800                        | SFILCON                         | 15:0      | ON            | _       | SIDL   | DISSDO       | MODE32       | MODE16       | SMP       | CKE    | SSEN    | CKP    | MSTEN  | DISSDI   | STXISE      | EL<1:0>  | SRXISE | EL<1:0> | 0000       |

| 5910                        | SPI1STAT                        | 31:16     | _             | _       | _      |              | RXE          | BUFELM<4:    | 0>        |        |         | _      |        |          | TXI         | BUFELM<4 | :0>    |         | 0000       |

| 5610                        | SFIISTAI                        | 15:0      | _             | _       | _      | FRMERR       | SPIBUSY      | _            | _         | SPITUR | SRMT    | SPIROV | SPIRBE |          | SPITBE      | _        | SPITBF | SPIRBF  | 19EB       |

| 5820                        | SPI1BUF                         | 31:16     |               |         |        |              |              |              |           | DATA<  | 31.0>   |        |        |          |             |          |        |         | 0000       |

| 5620                        |                                 | 15:0      | 00            |         |        |              |              |              |           |        |         | 0000   |        |          |             |          |        |         |            |

| 5830                        | SPI1BRG                         | 31:16     | _             | —       | —      |              | —            | —            | —         |        | —       | —      | —      | —        | —           | —        | —      | —       | 0000       |

| 5650                        |                                 | 15:0      | —             | —       | —      | _            | —            | —            | _         |        |         |        |        | BRG<8:0> |             |          |        |         | 0000       |

|                             |                                 | 31:16     | —             | —       | —      | _            | —            | —            | _         | _      | _       | —      | —      | _        | —           | —        | —      | -       | 0000       |

| 5840                        | SPI1CON2                        | 15:0      | SPI<br>SGNEXT | -       | —      | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV    | IGNTUR | AUDEN   | —      | —      | —        | AUD<br>MONO | —        | AUDMC  | )D<1:0> | 0000       |

| 5400                        | SPI2CON                         | 31:16     | FRMEN         | FRMSYNC | FRMPOL | MSSEN        | FRMSYPW      | FF           | RMCNT<2:0 | )>     | MCLKSEL | _      | _      | —        | _           | _        | SPIFE  | ENHBUF  | 0000       |

| 5A00                        | SPIZCON                         | 15:0      | ON            | _       | SIDL   | DISSDO       | MODE32       | MODE16       | SMP       | CKE    | SSEN    | CKP    | MSTEN  | DISSDI   | STXISE      | EL<1:0>  | SRXISE | EL<1:0> | 0000       |

| 5440                        | SPI2STAT                        | 31:16     | —             | —       | _      |              | RXE          | BUFELM<4:    | 0>        |        |         | _      |        |          | TXI         | BUFELM<4 | :0>    |         | 0000       |

| SATU                        | 3F1231AI                        | 15:0      | _             |         | —      | FRMERR       | SPIBUSY      | _            | _         | SPITUR | SRMT    | SPIROV | SPIRBE | _        | SPITBE      | _        | SPITBF | SPIRBF  | 19EB       |

| 5A20                        | SPI2BUF                         | 31:16     |               |         |        |              |              |              |           | DATA<  | 31.05   |        |        |          |             |          |        |         | 0000       |

| 5A20                        | 3FI2D0I                         | 15:0      |               |         |        |              |              |              |           | DAIAS  | 51.02   |        |        |          |             |          |        |         | 0000       |

| 5A30                        | SPI2BRG                         | 31:16     | —             | —       | —      | _            | —            | —            | _         | _      | _       | —      | -      | _        | —           | —        | —      | -       | 0000       |

| 5A30                        |                                 | 15:0      | _             | —       | -      |              | _            | _            | _         |        |         |        |        | BRG<8:0> |             |          |        |         | 0000       |

|                             |                                 | 31:16     | _             | —       | —      | _            | —            | —            | _         | _      | _       | —      | —      | —        | _           | —        | —      | —       | 0000       |

| 5A40                        | SPI2CON2                        | 15:0      | SPI<br>SGNEXT | _       | _      | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV    | IGNTUR | AUDEN   | _      | _      |          | AUD<br>MONO | _        | AUDMC  | )D<1:0> | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except SPIxBUF have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

NOTES:

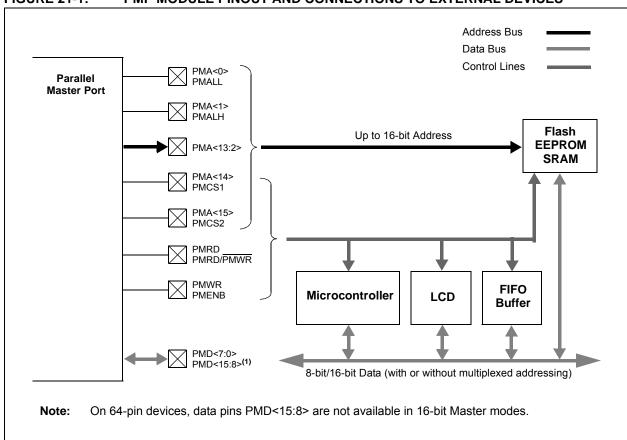

# 21.0 PARALLEL MASTER PORT (PMP)

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 13. "Parallel Master Port (PMP)" (DS60001128), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PMP is a parallel 8-bit/16-bit input/output module specifically designed to communicate with a wide variety of parallel devices, such as communications peripherals, LCDs, external memory devices and microcontrollers. Because the interface to parallel peripherals varies significantly, the PMP module is highly configurable.

The following are key features of the PMP module:

- 8-bit,16-bit interface

- · Up to 16 programmable address lines

- · Up to two Chip Select lines

- Programmable strobe options

- Individual read and write strobes, or

- Read/write strobe with enable strobe

- Address auto-increment/auto-decrement

- Programmable address/data multiplexing

- · Programmable polarity on control signals

- Parallel Slave Port support

- Legacy addressable

- Address support

- 4-byte deep auto-incrementing buffer

- · Programmable Wait states

- Operate during CPU Sleep and Idle modes

- Fast bit manipulation using CLR, SET and INV registers

- Freeze option for in-circuit debugging

Note: On 64-pin devices, data pins PMD<15:8> are not available in 16-bit Master modes.

# FIGURE 21-1: PMP MODULE PINOUT AND CONNECTIONS TO EXTERNAL DEVICES

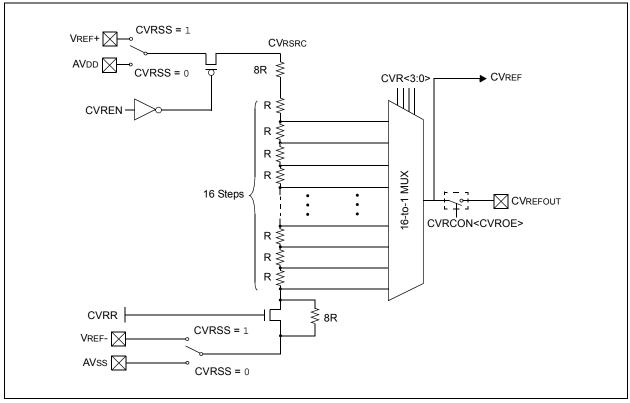

# 25.0 COMPARATOR VOLTAGE REFERENCE (CVREF)

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The CVREF module is a 16-tap, resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it also may be used independently of them. A block diagram of the module is illustrated in Figure 25-1. The resistor ladder is segmented to provide two ranges of voltage reference values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/Vss or an external voltage reference. The CVREF output is available for the comparators and typically available for pin output.

The CVREF module has the following features:

- High and low range selection

- · Sixteen output levels available for each range

- Internally connected to comparators to conserve device pins

- · Output can be connected to a pin

### FIGURE 25-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04        | R/P               | R/P               | R/P               | R/P               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | FVBUSONIO         | FUSBIDIO          | IOL1WAY           | PMDL1WAY          | —                 |                   | —                | _                |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | R/P               | R/P              | R/P              |  |  |  |  |

| 23.10        | —                 | —                 | —                 | —                 | _                 | FSRSSEL<2:0>      |                  |                  |  |  |  |  |

| 15.0         | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |  |  |

| 15:8         | USERID<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0          | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |  |  |

| 7:0          |                   | USERID<7:0>       |                   |                   |                   |                   |                  |                  |  |  |  |  |

# REGISTER 28-4: DEVCFG3: DEVICE CONFIGURATION WORD 3

| Legend:           | r = Reserved bit | P = Programmable bit   |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31 **FVBUSONIO:** USB VBUS\_ON Selection bit 1 = VBUSON pin is controlled by the USB module

- 0 = VBUSON pin is controlled by the OSB module0 = VBUSON pin is controlled by the port function

- bit 30 **FUSBIDIO:** USB USBID Selection bit 1 = USBID pin is controlled by the USB module 0 = USBID pin is controlled by the port function

- bit 29 IOL1WAY: Peripheral Pin Select Configuration bit

- 1 = Allow only one reconfiguration

- 0 = Allow multiple reconfigurations

- bit 28 PMDL1WAY: Peripheral Module Disable Configuration bit

- 1 = Allow only one reconfiguration

- 0 = Allow multiple reconfigurations

- bit 27-19 Unimplemented: Read as '0'

### bit 18-16 FSRSSEL<2:0>: Shadow Register Set Priority Select bit

These bits assign an interrupt priority to a shadow register.

- 111 = Shadow register set used with interrupt priority 7

- 110 = Shadow register set used with interrupt priority 6

- 101 = Shadow register set used with interrupt priority 5

- 100 = Shadow register set used with interrupt priority 4

- O11 = Shadow register set used with interrupt priority 3

- 010 = Shadow register set used with interrupt priority 2

- 001 = Shadow register set used with interrupt priority 1

- 000 = Shadow register set used with interrupt priority 0

- bit 15-0 USERID<15:0>: This is a 16-bit value that is user-defined and is readable via ICSP™ and JTAG

# TABLE 31-18: EXTERNAL CLOCK TIMING REQUIREMENTS

|               |                    |                                                                                                                  | (unless oth | erwise stat                                                                                                                                                                                                                                               |             |            |                                         |  |

|---------------|--------------------|------------------------------------------------------------------------------------------------------------------|-------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------|-----------------------------------------|--|

| AC CHA        | AC CHARACTERISTICS |                                                                                                                  |             | $\begin{array}{ll} \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |             |            |                                         |  |

| Param.<br>No. | Symbol             | Characteristics                                                                                                  | Min.        | Typical <sup>(1)</sup>                                                                                                                                                                                                                                    | Max.        | Units      | Conditions                              |  |

| OS10          | Fosc               | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes)                               | DC<br>4     | _                                                                                                                                                                                                                                                         | 50<br>50    | MHz<br>MHz | EC (Note 4)<br>ECPLL (Note 3)           |  |

| OS11          |                    | Oscillator Crystal Frequency                                                                                     | 3           |                                                                                                                                                                                                                                                           | 10          | MHz        | XT (Note 4)                             |  |

| OS12          |                    |                                                                                                                  | 4           |                                                                                                                                                                                                                                                           | 10          | MHz        | XTPLL<br>(Notes 3,4)                    |  |

| OS13          |                    |                                                                                                                  | 10          |                                                                                                                                                                                                                                                           | 25          | MHz        | HS (Note 4)                             |  |

| OS14          |                    |                                                                                                                  | 10          | _                                                                                                                                                                                                                                                         | 25          | MHz        | HSPLL<br>(Notes 3,4)                    |  |

| OS15          |                    |                                                                                                                  | 32          | 32.768                                                                                                                                                                                                                                                    | 100         | kHz        | Sosc (Note 4)                           |  |

| OS20          | Tosc               | Tosc = 1/Fosc = Tcy (Note 2)                                                                                     | _           | —                                                                                                                                                                                                                                                         | _           | _          | See parameter<br>OS10 for Fosc<br>value |  |

| OS30          | TosL,<br>TosH      | External Clock In (OSC1)<br>High or Low Time                                                                     | 0.45 x Tosc |                                                                                                                                                                                                                                                           | _           | ns         | EC (Note 4)                             |  |

| OS31          | TosR,<br>TosF      | External Clock In (OSC1)<br>Rise or Fall Time                                                                    | —           | _                                                                                                                                                                                                                                                         | 0.05 x Tosc | ns         | EC (Note 4)                             |  |

| OS40          | Tost               | Oscillator Start-up Timer Period<br>(Only applies to HS, HSPLL,<br>XT, XTPLL and Sosc Clock<br>Oscillator modes) | _           | 1024                                                                                                                                                                                                                                                      | _           | Tosc       | (Note 4)                                |  |

| OS41          | TFSCM              | Primary Clock Fail Safe<br>Time-out Period                                                                       | —           | 2                                                                                                                                                                                                                                                         | —           | ms         | (Note 4)                                |  |

| OS42          | Gм                 | External Oscillator<br>Transconductance (Primary<br>Oscillator only)                                             | _           | 12                                                                                                                                                                                                                                                        | _           | mA/V       | VDD = 3.3V,<br>TA = +25°C<br>(Note 4)   |  |

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are characterized but are not tested.

- 2: Instruction cycle period (TCY) equals the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin.

- **3:** PLL input requirements: 4 MHz  $\leq$  FPLLIN  $\leq$  5 MHz (use PLL prescaler to reduce Fosc). This parameter is characterized, but tested at 10 MHz only at manufacturing.

- 4: This parameter is characterized, but not tested in manufacturing.

# TABLE 31-19: PLL CLOCK TIMING SPECIFICATIONS

| AC CHARACTERISTICS |        |                                                                     | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |       |         |       |       |                                      |  |

|--------------------|--------|---------------------------------------------------------------------|------------------------------------------------------|-------|---------|-------|-------|--------------------------------------|--|

| Param.<br>No.      | Symbol | Characteristics <sup>(1)</sup>                                      |                                                      | Min.  | Typical | Max.  | Units | Conditions                           |  |

| OS50               | Fplli  | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range |                                                      | 3.92  | —       | 5     | MHz   | ECPLL, HSPLL, XTPLL,<br>FRCPLL modes |  |

| OS51a              | Fsys   | On-Chip VCO System                                                  | n Frequency                                          | 60    | _       | 120   | MHz   | Commercial devices                   |  |

| OS51b              |        |                                                                     |                                                      | 60    | —       | 100   | MHz   | Industrial devices                   |  |

| OS51c              | ]      |                                                                     |                                                      | 60    | —       | 80    | MHz   | V-temp devices                       |  |

| OS52               | TLOCK  | PLL Start-up Time (Lock Time)                                       |                                                      | _     | _       | 2     | ms    | —                                    |  |

| OS53               | DCLK   | CLKO Stability <sup>(2)</sup><br>(Period Jitter or Cumu             | ulative)                                             | -0.25 | _       | +0.25 | %     | Measured over 100 ms<br>period       |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

2: This jitter specification is based on clock-cycle by clock-cycle measurements. To get the effective jitter for individual time-bases on communication clocks, use the following formula:

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{SYSCLK}{CommunicationClock}}}$$

For example, if SYSCLK = 40 MHz and SPI bit rate = 20 MHz, the effective jitter is as follows:

$$EffectiveJitter = \frac{D_{CLK}}{\sqrt{\frac{40}{20}}} = \frac{D_{CLK}}{1.41}$$

### TABLE 31-20: INTERNAL FRC ACCURACY

| AC CHARACTERISTICS                              |                 | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercial} \\ & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |         |      |       |            |  |  |

|-------------------------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|------------|--|--|

| Param.<br>No.                                   | Characteristics | Min.                                                                                                                                                                                                                                                                                                                                                    | Typical | Max. | Units | Conditions |  |  |

| Internal FRC Accuracy @ 8.00 MHz <sup>(1)</sup> |                 |                                                                                                                                                                                                                                                                                                                                                         |         |      |       |            |  |  |

| F20b                                            | FRC             | -0.9                                                                                                                                                                                                                                                                                                                                                    | _       | +0.9 | %     | —          |  |  |

Note 1: Frequency calibrated at 25°C and 3.3V. The TUN bits can be used to compensate for temperature drift.

| AC CHA        | RACTERIS |                   | $\begin{tabular}{ l l l l l l l l l l l l l l l l l l l$ |      |      |       |                            |

|---------------|----------|-------------------|----------------------------------------------------------|------|------|-------|----------------------------|

| Param.<br>No. | Symbol   | I Characteristics |                                                          | Min. | Max. | Units | Conditions                 |

| IS34          | THD:STO  | Stop Condition    | 100 kHz mode                                             | 4000 | _    | ns    | —                          |

|               |          | Hold Time         | 400 kHz mode                                             | 600  | _    | ns    |                            |

|               |          |                   | 1 MHz mode<br>(Note 1)                                   | 250  |      | ns    |                            |

| IS40          | TAA:SCL  | Output Valid from | 100 kHz mode                                             | 0    | 3500 | ns    | —                          |

|               |          | Clock             | 400 kHz mode                                             | 0    | 1000 | ns    |                            |

|               |          |                   | 1 MHz mode<br>(Note 1)                                   | 0    | 350  | ns    |                            |

| IS45          | TBF:SDA  | Bus Free Time     | 100 kHz mode                                             | 4.7  | —    | μs    | The amount of time the bus |

|               |          |                   | 400 kHz mode                                             | 1.3  |      | μs    | must be free before a new  |

|               |          |                   | 1 MHz mode<br><b>(Note 1)</b>                            | 0.5  | -    | μS    | transmission can start     |

| IS50          | Св       | Bus Capacitive Lo | ading                                                    |      | 400  | pF    | _                          |

# TABLE 31-34: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE) (CONTINUED)

**Note 1:** Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

| AC CHARACTERISTICS <sup>(2)</sup> |                                      |             | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercial} \\ & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |            |                                |                         |  |

|-----------------------------------|--------------------------------------|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------------------------|-------------------------|--|

| ADC Input                         | ADC Speed                            | TAD<br>Min. | Sampling<br>Time<br>Min.                                                                                                                                                                                                                                                                                                                               | Rs<br>Max. | VDD ADC Channels Contiguration |                         |  |

| AN0-AN14                          | 1 Msps to 400<br>ksps <sup>(1)</sup> | 65 ns       | 132 ns                                                                                                                                                                                                                                                                                                                                                 | 500Ω       | 3.0V to 3.6V                   | ANX CHX ADC             |  |

|                                   | Up to 400 ksps                       | 200 ns      | 200 ns                                                                                                                                                                                                                                                                                                                                                 | 5.0 kΩ     | 2.5V to 3.6V                   | ANX CHX<br>ANX OF VREF- |  |

| AN15-AN27                         | 400 ksps <sup>(1)</sup>              | 154 ns      | 1000 ns                                                                                                                                                                                                                                                                                                                                                | 500Ω       | 3.0V to 3.6V                   | ANX CHX<br>ANX ADC      |  |

#### TABLE 31-36: 10-BIT CONVERSION RATE PARAMETERS ſ

**Note 1:** External VREF- and VREF+ pins must be used for correct operation.

2: These parameters are characterized, but not tested in manufacturing.

# PIC32MX330/350/370/430/450/470

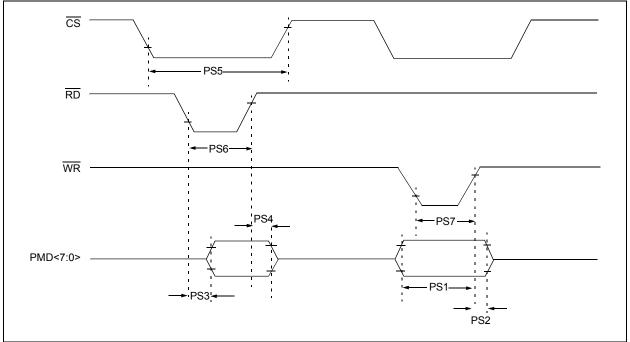

# FIGURE 31-20: PARALLEL SLAVE PORT TIMING

# TABLE 31-38: PARALLEL SLAVE PORT REQUIREMENTS

| AC CHARACTERISTICS |              |                                                                                  | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |      |       |            |  |

|--------------------|--------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------|--|

| Para<br>m.No.      | Symbol       | Characteristics <sup>(1)</sup>                                                   | Min.                                                                                                                                                                                                                                                                                                                                               | Тур. | Max. | Units | Conditions |  |

| PS1                | TdtV2wr<br>H | Data In Valid before $\overline{WR}$ or $\overline{CS}$<br>Inactive (setup time) | 20                                                                                                                                                                                                                                                                                                                                                 |      | —    | ns    | _          |  |

| PS2                | TwrH2dt<br>I | WR or CS Inactive to Data-In Invalid (hold time)                                 | 40                                                                                                                                                                                                                                                                                                                                                 | —    | —    | ns    | _          |  |

| PS3                | TrdL2dt<br>V | RD and CS Active to Data-Out Valid                                               | _                                                                                                                                                                                                                                                                                                                                                  |      | 60   | ns    | _          |  |

| PS4                | TrdH2dtl     | RD Active or CS Inactive to Data-Out Invalid                                     | 0                                                                                                                                                                                                                                                                                                                                                  |      | 10   | ns    | _          |  |

| PS5                | Tcs          | CS Active Time                                                                   | Трв + 40                                                                                                                                                                                                                                                                                                                                           |      | —    | ns    | —          |  |

| PS6                | Twr          | WR Active Time                                                                   | Трв + 25                                                                                                                                                                                                                                                                                                                                           |      | _    | ns    | _          |  |

| PS7                | Trd          | RD Active Time                                                                   | Трв + 25                                                                                                                                                                                                                                                                                                                                           | _    | _    | ns    | _          |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

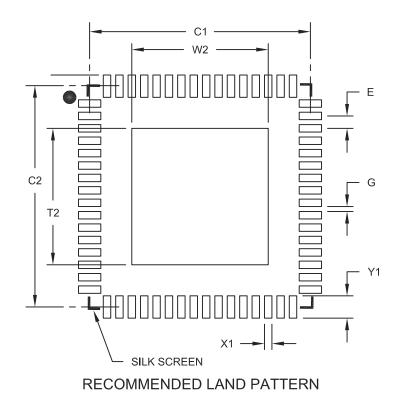

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 0.40 mm Contact Length and 5.40x5.40mm Exposed Pad

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |          |      |      |  |

|----------------------------|-------------|----------|------|------|--|

| Dimensio                   | n Limits    | MIN      | NOM  | MAX  |  |

| Contact Pitch              | E           | 0.50 BSC |      |      |  |

| Optional Center Pad Width  | W2          |          |      | 5.50 |  |

| Optional Center Pad Length | T2          |          |      | 5.50 |  |

| Contact Pad Spacing        | C1          |          | 8.90 |      |  |

| Contact Pad Spacing        | C2          |          | 8.90 |      |  |

| Contact Pad Width (X64)    | X1          |          |      | 0.30 |  |

| Contact Pad Length (X64)   | Y1          |          |      | 0.85 |  |

| Distance Between Pads      | G           | 0.20     |      |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2154A

# **Revision E (October 2015)**

This revision includes the following updates, as listed in Table A-4.

# TABLE A-4: MAJOR SECTION UPDATES

| Section                                                  | Update Description                                                             |

|----------------------------------------------------------|--------------------------------------------------------------------------------|

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs" | Section 2.10 "Sosc Design Recommendations" was removed.                        |

| 31.0 "Electrical<br>Characteristics"                     | The Power-Down Current (IPD) DC Characteristics were updated (see Table 31-7). |

# **Revision F (September 2016)**

This revision includes the following updates, as listed in Table A-5.

# TABLE A-5: MAJOR SECTION UPDATES

| Section                                                    | Update Description                                                                                                                                                                                             |  |  |  |  |  |  |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| "32-bit Microcontrollers (up<br>to 512 KB Flash and 128 KB | The PIC32MX450F128HB and PIC32MX470F512LB devices and Note 4 were added to the family features table (see Table 1).                                                                                            |  |  |  |  |  |  |

| SRAM) with Audio/                                          | Note 2 in the 64-pin device pin table was updated (see Table 2).                                                                                                                                               |  |  |  |  |  |  |

| Graphics/Touch (HMI), USB,<br>and Advanced Analog"         | Note 2 in the 64-pin device pin table was updated and Note 4 was removed (see Table 3).                                                                                                                        |  |  |  |  |  |  |

|                                                            | Note 2 and Note 3 in the 100-pin device pin table was updated (see Table 4).                                                                                                                                   |  |  |  |  |  |  |

|                                                            | Note 3 in the 124-pin device pin table was updated (see Table 6).                                                                                                                                              |  |  |  |  |  |  |

|                                                            | Note 2 in the 124-pin device pin table was updated (see Table 7).                                                                                                                                              |  |  |  |  |  |  |