Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 64K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-VQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx350f256ht-i-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

1

#### TABLE 4: PIN NAMES FOR 100-PIN DEVICES

#### 100-PIN TQFP (TOP VIEW)<sup>(1,2,3)</sup>

#### PIC32MX330F064L PIC32MX350F128L PIC32MX350F256L PIC32MX370F512L

100

Pin # Full Pin Name Pin # Full Pin Name **RG15** Vss 1 36 2 VDD 37 VDD AN22/RPE5/PMD5/RE5 TCK/CTED2/RA1 3 38 AN23/PMD6/RE6 **RPF13/RF13** 4 39 AN27/PMD7/RE7 RPF12/RF12 5 40 RPC1/RC1 6 41 AN12/PMA11/RB12 RPC2/RC2 AN13/PMA10/RB13 7 42 8 RPC3/RC3 43 AN14/RPB14/CTED5/PMA1/RB14 RPC4/CTED7/RC4 44 AN15/RPB15/OCFB/CTED6/PMA0/RB15 9 10 AN16/C1IND/RPG6/SCK2/PMA5/RG6 45 Vss AN17/C1INC/RPG7/PMA4/RG7 11 46 Voo AN18/C2IND/RPG8/PMA3/RG8 47 RPD14/RD14 12 MCLR 48 RPD15/RD15 13 AN19/C2INC/RPG9/PMA2/RG9 49 RPF4/PMA9/RF4 14 RPF5/PMA8/RF5 15 Vss 50 VDD RPF3/RF3 16 51 TMS/CTED1/RA0 RPF2/RF2 17 52 RPE8/RE8 RPF8/RF8 18 53 RPE9/RE9 RPF7/RF7 54 19 AN5/C1INA/RPB5/RB5 RPF6/SCK1/INT0/RF6 20 55 AN4/C1INB/RB4 SDA1/RG3 21 56 22 PGED3/AN3/C2INA/RPB3/RB3 57 SCL1/RG2 PGEC3/AN2/C2INB/RPB2/CTED13/RB2 SCL2/RA2 58 23 24 PGEC1/AN1/RPB1/CTED12/RB1 59 SDA2/RA3 PGED1/AN0/RPB0/RB0 TDI/CTED9/RA4 25 60 PGEC2/AN6/RPB6/RB6 TDO/RA5 26 61 PGED2/AN7/RPB7/CTED3/RB7 62 VDD 27 VREF-/CVREF-/PMA7/RA9 63 OSC1/CLKI/RC12 28 VREF+/CVREF+/PMA6/RA10 OSC2/CLKO/RC15 29 64 30 AVDD 65 Vss 31 AVss 66 RPA14/RA14 AN8/RPB8/CTED10/RB8 32 67 **RPA15/RA15** AN9/RPB9/CTED4/RB9 RPD8/RTCC/RD8 33 68 CVREFOUT/AN10/RPB10/CTED11PMA13/RB10 RPD9/RD9 69 34 35 AN11/PMA12/RB11 70 RPD10/PMCS2/RD10

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RGx), with the exception of RF6, can be used as a change notification pin (CNAx-CNGx). See Section 12.0 "VO Ports" for more information.

3: RPF6 (pin 55) and RPF7 (pin 54) are only remappable for input functions.

#### TABLE 5: PIN NAMES FOR 100-PIN DEVICES

100-PIN TQFP (TOP VIEW)<sup>(1,2)</sup>

#### PIC32MX430F064L PIC32MX450F128L PIC32MX450F256L PIC32MX470F512L

|       |                                       |       | 1                               |

|-------|---------------------------------------|-------|---------------------------------|

| Pin # | Full Pin Name                         | Pin # | Full Pin Name                   |

| 1     | RG15                                  | 36    | Vss                             |

| 2     | Vdd                                   | 37    | VDD                             |

| 3     | AN22/RPE5/PMD5/RE5                    | 38    | TCK/CTED2/RA1                   |

| 4     | AN23/PMD6/RE6                         | 39    | RPF13/RF13                      |

| 5     | AN27/PMD7/RE7                         | 40    | RPF12/RF12                      |

| 6     | RPC1/RC1                              | 41    | AN12/PMA11/RB12                 |

| 7     | RPC2/RC2                              | 42    | AN13/PMA10/RB13                 |

| 8     | RPC3/RC3                              | 43    | AN14/RPB14/CTED5/PMA1/RB14      |

| 9     | RPC4/CTED7/RC4                        | 44    | AN15/RPB15/OCFB/CTED6/PMA0/RB15 |

| 10    | AN16/C1IND/RPG6/SCK2/PMA5/RG6         | 45    | Vss                             |

| 11    | AN17/C1INC/RPG7/PMA4/RG7              | 46    | VDD                             |

| 12    | AN18/C2IND/RPG8/PMA3/RG8              | 47    | RPD14/RD14                      |

| 13    | MCLR                                  | 48    | RPD15/RD15                      |

| 14    | AN19/C2INC/RPG9/PMA2/RG9              | 49    | RPF4/PMA9/RF4                   |

| 15    | Vss                                   | 50    | RPF5/PMA8/RF5                   |

| 16    | VDD                                   | 51    | USBID/RF3                       |

| 17    | TMS/CTED1/RA0                         | 52    | RPF2/RF2                        |

| 18    | RPE8/RE8                              | 53    | RPF8/RF8                        |

| 19    | RPE9/RE9                              | 54    | VBUS                            |

| 20    | AN5/C1INA/RPB5/VBUSON/RB5             | 55    | VUSB3V3                         |

| 21    | AN4/C1INB/RB4                         | 56    | D-                              |

| 22    | PGED3/AN3/C2INA/RPB3/RB3              | 57    | D+                              |

| 23    | PGEC3/AN2/C2INB/RPB2/CTED13/RB2       | 58    | SCL2/RA2                        |

| 24    | PGEC1/AN1/RPB1/CTED12/RB1             | 59    | SDA2/RA3                        |

| 25    | PGED1/AN0/RPB0/RB0                    | 60    | TDI/CTED9/RA4                   |

| 26    | PGEC2/AN6/RPB6/RB6                    | 61    | TDO/RA5                         |

| 27    | PGED2/AN7/RPB7/CTED3/RB7              | 62    | VDD                             |

| 28    | VREF-/CVREF-/PMA7/RA9                 | 63    | OSC1/CLKI/RC12                  |

| 29    | VREF+/CVREF+/PMA6/RA10                | 64    | OSC2/CLKO/RC15                  |

| 30    | AVDD                                  | 65    | Vss                             |

| 31    | AVss                                  | 66    | SCL1/RPA14/RA14                 |

| 32    | AN8/RPB8/CTED10/RB8                   | 67    | SDA1/RPA15/RA15                 |

| 33    | AN9/RPB9/CTED4/RB9                    | 68    | RPD8/RTCC/RD8                   |

| 34    | CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10 | 69    | RPD9/RD9                        |

| 35    | AN11/PMA12/RB11                       | 70    | RPD10/SCK1/PMCS2/RD10           |

100

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RBx-RGx) can be used as a change notification pin (CNBx-CNGx). See Section 12.0 "I/O Ports" for more information.

|          |                                                              | Pin Numb        | er                               |     |    |                                                     |

|----------|--------------------------------------------------------------|-----------------|----------------------------------|-----|----|-----------------------------------------------------|

| Pin Name | ame 64-pin<br>QFN/<br>TQFP TQFP VTLA Pin Buffer<br>Type Type |                 | Description                      |     |    |                                                     |

| RB0      | 16                                                           | 25              | B14                              | I/O | ST |                                                     |

| RB1      | 15                                                           | 24              | A15                              | I/O | ST | 7                                                   |

| RB2      | 14                                                           | 23              | B13                              | I/O | ST |                                                     |

| RB3      | 13                                                           | 22              | A13                              | I/O | ST |                                                     |

| RB4      | 12                                                           | 21              | B11                              | I/O | ST |                                                     |

| RB5      | 11                                                           | 20              | A12                              | I/O | ST |                                                     |

| RB6      | 17                                                           | 26              | A20                              | I/O | ST |                                                     |

| RB7      | 18                                                           | 27              | B16                              | I/O | ST | PORTB is a bidirectional I/O port                   |

| RB8      | 21                                                           | 32              | A23                              | I/O | ST |                                                     |

| RB9      | 22                                                           | 33              | B19                              | I/O | ST |                                                     |

| RB10     | 23                                                           | 34              | A24                              | I/O | ST |                                                     |

| RB11     | 24                                                           | 35              | B20                              | I/O | ST |                                                     |

| RB12     | 27                                                           | 41              | B23                              | I/O | ST |                                                     |

| RB13     | 28                                                           | 42              | A28                              | I/O | ST | 7                                                   |

| RB14     | 29                                                           | 43              | B24                              | I/O | ST | 7                                                   |

| RB15     | 30                                                           | 44              | A29                              | I/O | ST | 7                                                   |

| RC1      | —                                                            | 6               | A5                               | I/O | ST |                                                     |

| RC2      | —                                                            | 7               | B4                               | I/O | ST | 7                                                   |

| RC3      | —                                                            | 8               | A6                               | I/O | ST | 7                                                   |

| RC4      | —                                                            | 9               | B5                               | I/O | ST |                                                     |

| RC12     | 39                                                           | 63              | B34                              | I/O | ST | PORTC is a bidirectional I/O port                   |

| RC13     | 47                                                           | 73              | A47                              | I/O | ST | 7                                                   |

| RC14     | 48                                                           | 74              | B40                              | I/O | ST | 7                                                   |

| RC15     | 40                                                           | 64              | A42                              | I/O | ST | 7                                                   |

| RD0      | 46                                                           | 72              | B39                              | I/O | ST |                                                     |

| RD1      | 49                                                           | 76              | A52                              | I/O | ST | 7                                                   |

| RD2      | 50                                                           | 77              | B42                              | I/O | ST |                                                     |

| RD3      | 51                                                           | 78              | A53                              | I/O | ST | 7                                                   |

| RD4      | 52                                                           | 81              | B44                              | I/O | ST | 7                                                   |

| RD5      | 53                                                           | 82              | A55                              | I/O | ST |                                                     |

| RD6      | 54                                                           | 83              | B45                              | I/O | ST |                                                     |

| RD7      | 55                                                           | 84              | A56                              | I/O | ST | POPTD is a hidiractional UC sort                    |

| RD8      | 42                                                           | 68              | B37                              | I/O | ST | PORTD is a bidirectional I/O port                   |

| RD9      | 43                                                           | 69              | A45                              | I/O | ST |                                                     |

| RD10     | 44                                                           | 70              | B38                              | I/O | ST | 1                                                   |

| RD11     | 45                                                           | 71              | A46                              | I/O | ST | 1                                                   |

| RD12     | —                                                            | 79              | B43                              | I/O | ST | 1                                                   |

| RD13     | —                                                            | 80              | A54                              | I/O | ST | 1                                                   |

| RD14     | —                                                            | 47              | B26                              | I/O | ST | 1                                                   |

| RD15     | —                                                            | 48              | A31                              | I/O | ST | 1                                                   |

| -        |                                                              | itt Trigger inp | ible input or o<br>out with CMOS |     |    | alog = Analog input P = Power<br>= Output I = Input |

## TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices.

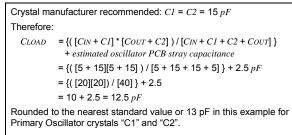

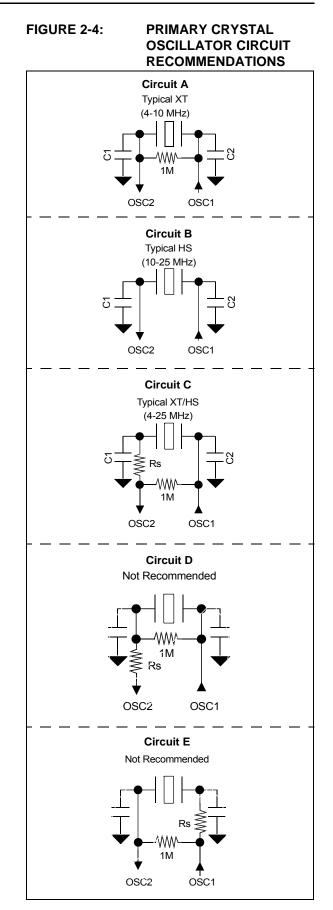

## 2.8.1 CRYSTAL OSCILLATOR DESIGN CONSIDERATION

The following example assumptions are used to calculate the Primary Oscillator loading capacitor values:

- CIN = PIC32\_OSC2\_Pin Capacitance = ~4-5 pF

- COUT = PIC32\_OSC1\_Pin Capacitance = ~4-5 pF

- C1 and C2 = XTAL manufacturing recommended loading capacitance

- Estimated PCB stray capacitance, (i.e.,12 mm length) = 2.5 pF

## EXAMPLE 2-1: CRYSTAL LOAD CAPACITOR CALCULATION

The following tips are used to increase oscillator gain, (i.e., to increase peak-to-peak oscillator signal):

- Select a crystal with a lower "minimum" power drive rating

- Select an crystal oscillator with a lower XTAL manufacturing "ESR" rating.

- Add a parallel resistor across the crystal. The smaller the resistor value the greater the gain. It is recommended to stay in the range of 600k to 1M

- C1 and C2 values also affect the gain of the oscillator. The lower the values, the higher the gain.

- C2/C1 ratio also affects gain. To increase the gain, make C1 slightly smaller than C2, which will also help start-up performance.

- Note: Do not add excessive gain such that the oscillator signal is clipped, flat on top of the sine wave. If so, you need to reduce the gain or add a series resistor, RS, as shown in circuit "C" in Figure 2-4. Failure to do so will stress and age the crystal, which can result in an early failure. Adjust the gain to trim the max peak-to-peak to ~VDD-0.6V. When measuring the oscillator signal you must use a FET scope probe or a probe with ≤ 1.5 pF or the scope probe itself will unduly change the gain and peak-to-peak levels.

#### 2.8.1.1 Additional Microchip References

- AN588 "PICmicro<sup>®</sup> Microcontroller Oscillator Design Guide"

- AN826 "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849 "Basic PICmicro<sup>®</sup> Oscillator Design"

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                 | —                 | _                 | —                 |                  | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | —                 | —                 | —                 |                   | —                 | —                | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |

| 15:8         |                   |                   |                   | BMXDU             | PBA<15:8>         |                   |                  |                  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | BMXDU             | PBA<7:0>          |                   |                  |                  |

## REGISTER 4-4: BMXDUPBA: DATA RAM USER PROGRAM BASE ADDRESS REGISTER

## Legend:

| Legenu.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-10 BMXDUPBA<15:10>: DRM User Program Base Address bits

When non-zero, the value selects the relative base address for User mode program space in RAM, BMXDUPBA must be greater than BMXDUDBA.

bit 9-0 BMXDUPBA<9:0>: Read-Only bits Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernel mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31:24        | CHEW1<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        | CHEW1<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         | CHEW1<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 7:0          |                   |                   |                   | CHEW1             | <7:0>             |                   |                  |                  |  |  |  |

#### REGISTER 9-6: CHEW1: CACHE WORD 1

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-0 **CHEW1<31:0>:** Word 1 of the cache line selected by the CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

## REGISTER 9-7: CHEW2: CACHE WORD 2

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31:24        | CHEW2<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        | CHEW2<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         |                   |                   |                   | CHEW2             | <15:8>            |                   |                  |                  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 7:0          |                   |                   |                   | CHEW2             | <7:0>             |                   |                  |                  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 **CHEW2<31:0>:** Word 2 of the cache line selected by the CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 04.04        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 31:24        |                     | —                 | _                 | _                 |                   | _                 | -                | —                     |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 23:16        | —                   | —                 | _                 | _                 | _                 | —                 | _                | —                     |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0                 |

| 15:8         | CHBUSY              | —                 | _                 | _                 | _                 | _                 | _                | CHCHNS <sup>(1)</sup> |

| 7.0          | R/W-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R-0               | R/W-0            | R/W-0                 |

| 7:0          | CHEN <sup>(2)</sup> | CHAED             | CHCHN             | CHAEN             | _                 | CHEDET            | CHPF             | RI<1:0>               |

#### REGISTER 10-7: DCHxCON: DMA CHANNEL 'x' CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 CHBUSY: Channel Busy bit

- 1 = Channel is active or has been enabled

- 0 = Channel is inactive or has been disabled

- bit 14-9 Unimplemented: Read as '0'

- bit 8 CHCHNS: Chain Channel Selection bit<sup>(1)</sup>

- 1 = Chain to channel lower in natural priority (CH1 will be enabled by CH2 transfer complete)

- 0 = Chain to channel higher in natural priority (CH1 will be enabled by CH0 transfer complete)

#### bit 7 CHEN: Channel Enable bit<sup>(2)</sup>

- 1 = Channel is enabled

- 0 = Channel is disabled

#### bit 6 CHAED: Channel Allow Events If Disabled bit

- 1 = Channel start/abort events will be registered, even if the channel is disabled

- 0 = Channel start/abort events will be ignored if the channel is disabled

#### bit CHCHN: Channel Chain Enable bit

- 1 = Allow channel to be chained

- 0 = Do not allow channel to be chained

- bit 4 CHAEN: Channel Automatic Enable bit

- 1 = Channel is continuously enabled, and not automatically disabled after a block transfer is complete

0 = Channel is disabled on block transfer complete

#### bit 3 Unimplemented: Read as '0'

- bit 2 CHEDET: Channel Event Detected bit

- 1 = An event has been detected

- 0 = No events have been detected

- bit 1-0 CHPRI<1:0>: Channel Priority bits

- 11 = Channel has priority 3 (highest)

- 10 = Channel has priority 2

- 01 = Channel has priority 1

- 00 = Channel has priority 0

- Note 1: The chain selection bit takes effect when chaining is enabled (i.e., CHCHN = 1).

- 2: When the channel is suspended by clearing this bit, the user application should poll the CHBUSY bit (if available on the device variant) to see when the channel is suspended, as it may take some clock cycles to complete a current transaction before the channel is suspended.

## REGISTER 10-9: DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER (CONTINUED)

bit 4 **CHDHIF:** Channel Destination Half Full Interrupt Flag bit

- 1 = Channel Destination Pointer has reached midpoint of destination (CHDPTR = CHDSIZ/2)

- 0 = No interrupt is pending

- bit 3 CHBCIF: Channel Block Transfer Complete Interrupt Flag bit

- 1 = A block transfer has been completed (the larger of CHSSIZ/CHDSIZ bytes has been transferred), or a pattern match event occurs

- 0 = No interrupt is pending

- bit 2 CHCCIF: Channel Cell Transfer Complete Interrupt Flag bit

- 1 = A cell transfer has been completed (CHCSIZ bytes have been transferred)

- 0 = No interrupt is pending

- bit 1 CHTAIF: Channel Transfer Abort Interrupt Flag bit

- 1 = An interrupt matching CHAIRQ has been detected and the DMA transfer has been aborted

- 0 = No interrupt is pending

- bit 0 CHERIF: Channel Address Error Interrupt Flag bit

- 1 = A channel address error has been detected

- Either the source or the destination address is invalid.

- 0 = No interrupt is pending

#### REGISTER 11-1: U1OTGIR: USB OTG INTERRUPT STATUS REGISTER

|              |                   | ••••••            |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | _                 |                   | —                 | —                 | -                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | _                 | _                 | —                 | —                 | _                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | —                 | —                 |                   |                   | —                 | —                 | -                | —                |

|              | R/WC-0, HS        | U-0              | R/WC-0, HS       |

| 7:0          | IDIF              | T1MSECIF          | LSTATEIF          | ACTVIF            | SESVDIF           | SESENDIF          | —                | VBUSVDIF         |

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable bit         |                    |  |

|-------------------|-------------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 IDIF: ID State Change Indicator bit

- 1 = Change in ID state is detected

- 0 = No change in ID state is detected

#### bit 6 T1MSECIF: 1 Millisecond Timer bit

- 1 = 1 millisecond timer has expired

- 0 = 1 millisecond timer has not expired

#### bit 5 LSTATEIF: Line State Stable Indicator bit

- 1 = USB line state has been stable for 1millisecond, but different from last time

- 0 = USB line state has not been stable for 1 millisecond

#### bit 4 ACTVIF: Bus Activity Indicator bit

- 1 = Activity on the D+, D-, ID or VBUS pins has caused the device to wake-up

- 0 = Activity has not been detected

- bit 3 SESVDIF: Session Valid Change Indicator bit

- 1 = VBUS voltage has dropped below the session end level

- 0 = VBUS voltage has not dropped below the session end level

#### bit 2 SESENDIF: B-Device VBUS Change Indicator bit

- 1 = A change on the session end input was detected

- 0 = No change on the session end input was detected

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIF: A-Device VBUS Change Indicator bit

- 1 = Change on the session valid input is detected

- 0 = No change on the session valid input is detected

NOTES:

## REGISTER 18-1: SPIxCON: SPI CONTROL REGISTER (CONTINUED)

- bit 4 **DISSDI:** Disable SDI bit 1 = SDI pin is not used by the SPI module (pin is controlled by PORT function)

- 0 = SDI pin is controlled by the SPI module

- bit 3-2 STXISEL<1:0>: SPI Transmit Buffer Empty Interrupt Mode bits

- 11 = Interrupt is generated when the buffer is not full (has one or more empty elements)

- 10 = Interrupt is generated when the buffer is empty by one-half or more

- 01 = Interrupt is generated when the buffer is completely empty

- 00 = Interrupt is generated when the last transfer is shifted out of SPISR and transmit operations are complete

- bit 1-0 SRXISEL<1:0>: SPI Receive Buffer Full Interrupt Mode bits

- 11 = Interrupt is generated when the buffer is full

- 10 = Interrupt is generated when the buffer is full by one-half or more

- 01 = Interrupt is generated when the buffer is not empty

- 00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **2:** This bit can only be written when the ON bit = 0.

- **3:** This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- 4: When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value of CKP.

## 19.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/ pic32). The  $I^2C$  module provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard. Figure 19-1 illustrates the  $I^2C$  module block diagram.

Each  $I^2C$  module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for the I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and arbitrates accordingly

- · Provides support for address bit masking

| Bit<br>3/15/7<br>R          | Bit<br>30/22/14/6<br>R | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                        | Bit<br>26/18/10/2                                                                   | Bit<br>25/17/9/1                                                                        | Bit<br>24/16/8/0                                                                               |  |  |

|-----------------------------|------------------------|-------------------|-------------------|------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|--|--|

| R                           | R                      | Р                 |                   |                                          |                                                                                     |                                                                                         | 24/10/0/0                                                                                      |  |  |

|                             |                        | R                 | R                 | R                                        | R                                                                                   | R                                                                                       | R                                                                                              |  |  |

| VER<3:0> <sup>(1)</sup>     |                        |                   |                   |                                          | DEVID<27:24> <sup>(1)</sup>                                                         |                                                                                         |                                                                                                |  |  |

| R                           | R                      | R                 | R                 | R                                        | R                                                                                   | R                                                                                       | R                                                                                              |  |  |

| DEVID<23:16> <sup>(1)</sup> |                        |                   |                   |                                          |                                                                                     |                                                                                         |                                                                                                |  |  |

| R                           | R                      | R                 | R                 | R                                        | R                                                                                   | R                                                                                       | R                                                                                              |  |  |

| DEVID<15:8> <sup>(1)</sup>  |                        |                   |                   |                                          |                                                                                     |                                                                                         |                                                                                                |  |  |

| R                           | R                      | R                 | R                 | R                                        | R                                                                                   | R                                                                                       | R                                                                                              |  |  |

| DEVID<7:0> <sup>(1)</sup>   |                        |                   |                   |                                          |                                                                                     |                                                                                         |                                                                                                |  |  |

| R                           | 2                      | R R               | R R               | DEVID<2<br>R R R R<br>DEVID<7<br>R R R R | DEVID<23:16> <sup>(1)</sup><br>R R R R R<br>DEVID<15:8> <sup>(1)</sup><br>R R R R R | DEVID<23:16> <sup>(1)</sup><br>R R R R R R<br>DEVID<15:8> <sup>(1)</sup><br>R R R R R R | DEVID<23:16>(1)       R     R     R     R       DEVID<15:8> <sup>(1)</sup> R     R     R     R |  |  |

## REGISTER 28-6: DEVID: DEVICE AND REVISION ID REGISTER

## Legend:

| Logona.           |                  |                                                 |                    |

|-------------------|------------------|-------------------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | Writable bit U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                            | x = Bit is unknown |

bit 31-28 VER<3:0>: Revision Identifier bits<sup>(1)</sup>

bit 27-0 **DEVID<27:0>:** Device ID<sup>(1)</sup>

Note 1: See the "PIC32 Flash Programming Specification" (DS60001145) for a list of Revision and Device ID values.

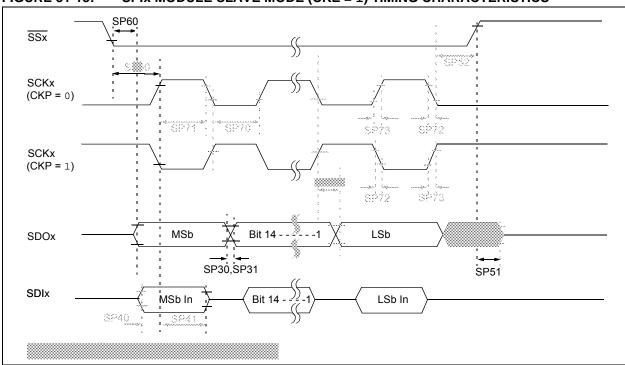

## FIGURE 31-13: SPIX MODULE SLAVE MODE (CKE = 1) TIMING CHARACTERISTICS

## TABLE 31-32: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHA        | ARACTERIS             | (unless o                                    | I Operating<br>otherwise st<br>g temperatur | t <b>ated)</b><br>e 0°C<br>-40° | ≤ TA ≤ +<br>°C ≤ TA ≤ | <b>3V to 3.6V</b><br>-70°C for Commercial<br>≤ +85°C for Industrial<br>≤ +105°C for V-temp |                    |

|---------------|-----------------------|----------------------------------------------|---------------------------------------------|---------------------------------|-----------------------|--------------------------------------------------------------------------------------------|--------------------|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>               | Min.                                        | Typical <sup>(2)</sup>          | Max.                  | Units                                                                                      | Conditions         |

| SP70          | TscL                  | SCKx Input Low Time (Note 3)                 | Tsck/2                                      |                                 |                       | ns                                                                                         | —                  |

| SP71          | TscH                  | SCKx Input High Time (Note 3)                | Tsck/2                                      | —                               | _                     | ns                                                                                         | —                  |

| SP72          | TscF                  | SCKx Input Fall Time                         | —                                           | 5                               | 10                    | ns                                                                                         | —                  |

| SP73          | TscR                  | SCKx Input Rise Time                         | —                                           | 5                               | 10                    | ns                                                                                         | —                  |

| SP30          | TDOF                  | SDOx Data Output Fall Time (Note 4)          | —                                           | —                               | _                     | ns                                                                                         | See parameter DO32 |

| SP31          | TDOR                  | SDOx Data Output Rise Time (Note 4)          | —                                           | —                               | _                     | ns                                                                                         | See parameter DO31 |

| SP35          | TscH2doV,             | SDOx Data Output Valid after                 | _                                           | —                               | 20                    | ns                                                                                         | VDD > 2.7V         |

|               | TscL2DoV              | SCKx Edge                                    |                                             | —                               | 30                    | ns                                                                                         | VDD < 2.7V         |

| SP40          | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge   | 10                                          | —                               |                       | ns                                                                                         | —                  |

| SP41          | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input<br>to SCKx Edge | 10                                          | —                               |                       | ns                                                                                         | —                  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: The minimum clock period for SCKx is 40 ns.

4: Assumes 50 pF load on all SPIx pins.

## TABLE 31-32: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS (CONTINUED)

| AC CHARACTERISTICS |                       |                                                                           | $ \begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commerc} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industri} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array} $ |                        |      |       |            |

|--------------------|-----------------------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|------------|

| Param.<br>No.      | Symbol                | Characteristics <sup>(1)</sup>                                            | Min.                                                                                                                                                                                                                                                                                                                                            | Typical <sup>(2)</sup> | Max. | Units | Conditions |

| SP50               | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\downarrow$ or SCKx $\uparrow$ Input | 175                                                                                                                                                                                                                                                                                                                                             |                        |      | ns    | —          |

| SP51               | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance<br>(Note 4)                        | 5                                                                                                                                                                                                                                                                                                                                               |                        | 25   | ns    | _          |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx ↑ after SCKx Edge                                                     | Тscк +<br>20                                                                                                                                                                                                                                                                                                                                    | _                      | _    | ns    | _          |

| SP60               | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge                                  |                                                                                                                                                                                                                                                                                                                                                 |                        | 25   | ns    |            |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: The minimum clock period for SCKx is 40 ns.

**4:** Assumes 50 pF load on all SPIx pins.

## TABLE 31-34: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

|               | RACTERIS | STICS           |                        | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commerci $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industria $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |      |       |                                            |

|---------------|----------|-----------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------------------------------|

| Param.<br>No. | Symbol   | Charact         | teristics              | Min.                                                                                                                                                                                                                                                | Max. | Units | Conditions                                 |

| IS10          | TLO:SCL  | Clock Low Time  | 100 kHz mode           | 4.7                                                                                                                                                                                                                                                 | _    | μS    | PBCLK must operate at a minimum of 800 kHz |

|               |          |                 | 400 kHz mode           | 1.3                                                                                                                                                                                                                                                 | _    | μS    | PBCLK must operate at a minimum of 3.2 MHz |

|               |          |                 | 1 MHz mode<br>(Note 1) | 0.5                                                                                                                                                                                                                                                 | _    | μS    | _                                          |

| IS11          | THI:SCL  | Clock High Time | 100 kHz mode           | 4.0                                                                                                                                                                                                                                                 | —    | μS    | PBCLK must operate at a minimum of 800 kHz |

|               |          |                 | 400 kHz mode           | 0.6                                                                                                                                                                                                                                                 | —    | μS    | PBCLK must operate at a minimum of 3.2 MHz |

|               |          |                 | 1 MHz mode<br>(Note 1) | 0.5                                                                                                                                                                                                                                                 | _    | μS    | —                                          |

| IS20          | TF:SCL   | SDAx and SCLx   | 100 kHz mode           | —                                                                                                                                                                                                                                                   | 300  | ns    | CB is specified to be from                 |

|               |          | Fall Time       | 400 kHz mode           | 20 + 0.1 Св                                                                                                                                                                                                                                         | 300  | ns    | 10 to 400 pF                               |

|               |          |                 | 1 MHz mode<br>(Note 1) | —                                                                                                                                                                                                                                                   | 100  | ns    |                                            |

| IS21          | TR:SCL   | SDAx and SCLx   | 100 kHz mode           | —                                                                                                                                                                                                                                                   | 1000 | ns    | CB is specified to be from                 |

|               |          | Rise Time       | 400 kHz mode           | 20 + 0.1 Св                                                                                                                                                                                                                                         | 300  | ns    | 10 to 400 pF                               |

|               |          |                 | 1 MHz mode<br>(Note 1) | —                                                                                                                                                                                                                                                   | 300  | ns    |                                            |

| IS25          | TSU:DAT  | Data Input      | 100 kHz mode           | 250                                                                                                                                                                                                                                                 | —    | ns    | —                                          |

|               |          | Setup Time      | 400 kHz mode           | 100                                                                                                                                                                                                                                                 | —    | ns    |                                            |

|               |          |                 | 1 MHz mode<br>(Note 1) | 100                                                                                                                                                                                                                                                 | —    | ns    |                                            |

| IS26          | THD:DAT  | Data Input      | 100 kHz mode           | 0                                                                                                                                                                                                                                                   | —    | ns    | _                                          |

|               |          | Hold Time       | 400 kHz mode           | 0                                                                                                                                                                                                                                                   | 0.9  | μS    |                                            |

|               |          |                 | 1 MHz mode<br>(Note 1) | 0                                                                                                                                                                                                                                                   | 0.3  | μS    |                                            |

| IS30          | TSU:STA  | Start Condition | 100 kHz mode           | 4700                                                                                                                                                                                                                                                |      | ns    | Only relevant for Repeated                 |

|               |          | Setup Time      | 400 kHz mode           | 600                                                                                                                                                                                                                                                 | —    | ns    | Start condition                            |

|               |          |                 | 1 MHz mode<br>(Note 1) | 250                                                                                                                                                                                                                                                 | —    | ns    |                                            |

| IS31          | THD:STA  | Start Condition | 100 kHz mode           | 4000                                                                                                                                                                                                                                                |      | ns    | After this period, the first               |

|               |          | Hold Time       | 400 kHz mode           | 600                                                                                                                                                                                                                                                 | —    | ns    | clock pulse is generated                   |

|               |          |                 | 1 MHz mode<br>(Note 1) | 250                                                                                                                                                                                                                                                 | —    | ns    |                                            |

| IS33          | Tsu:sto  | Stop Condition  | 100 kHz mode           | 4000                                                                                                                                                                                                                                                |      | ns    |                                            |

|               |          | Setup Time      | 400 kHz mode           | 600                                                                                                                                                                                                                                                 | —    | ns    |                                            |

|               |          |                 | 1 MHz mode<br>(Note 1) | 600                                                                                                                                                                                                                                                 | _    | ns    |                                            |

**Note 1:** Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

| AC CHA        | ARACTERIS  | STICS <sup>(5)</sup>           | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercial} \\ & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |              |      |       |                                                         |  |

|---------------|------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|-------|---------------------------------------------------------|--|

| Param.<br>No. | Symbol     | Characteristics                | Min.                                                                                                                                                                                                                                                                                                                                                   | Typical      | Max. | Units | Conditions                                              |  |

| ADC Ac        | curacy – N | leasurements with Inter        | nal VREF+/VR                                                                                                                                                                                                                                                                                                                                           | EF-          |      |       |                                                         |  |

| AD20d         | Nr         | Resolution                     |                                                                                                                                                                                                                                                                                                                                                        | 10 data bits |      | bits  | (Note 3)                                                |  |

| AD21d         | INL        | Integral Nonlinearity          | > -1                                                                                                                                                                                                                                                                                                                                                   | _            | < 1  | LSb   | VINL = AVss = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |

| AD22d         | DNL        | Differential Nonlinearity      | > -1                                                                                                                                                                                                                                                                                                                                                   |              | < 1  | LSb   | VINL = AVSS = 0V,<br>AVDD = 2.5V to 3.6V<br>(Notes 2,3) |  |

| AD23d         | Gerr       | Gain Error                     | > -4                                                                                                                                                                                                                                                                                                                                                   | _            | < 4  | LSb   | VINL = AVss = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |

| AD24d         | Eoff       | Offset Error                   | > -2                                                                                                                                                                                                                                                                                                                                                   | _            | < 2  | LSb   | VINL = AVss = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |

| AD25d         | _          | Monotonicity                   | _                                                                                                                                                                                                                                                                                                                                                      | —            |      | —     | Guaranteed                                              |  |

| Dynami        | c Performa | ince                           | •                                                                                                                                                                                                                                                                                                                                                      | •            |      | •     | •                                                       |  |

| AD31b         | SINAD      | Signal to Noise and Distortion | 55                                                                                                                                                                                                                                                                                                                                                     | 58           | _    | dB    | (Notes 3,4)                                             |  |

| AD34b         | ENOB       | Effective Number of Bits       | 9                                                                                                                                                                                                                                                                                                                                                      | 9.5          | _    | bits  | (Notes 3,4)                                             |  |

## TABLE 31-35: ADC MODULE SPECIFICATIONS (CONTINUED)

**Note 1:** These parameters are not characterized or tested in manufacturing.

2: With no missing codes.

3: These parameters are characterized, but not tested in manufacturing.

**4:** Characterized with a 1 kHz sine wave.

5: Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 31-10 for VBORMIN values.

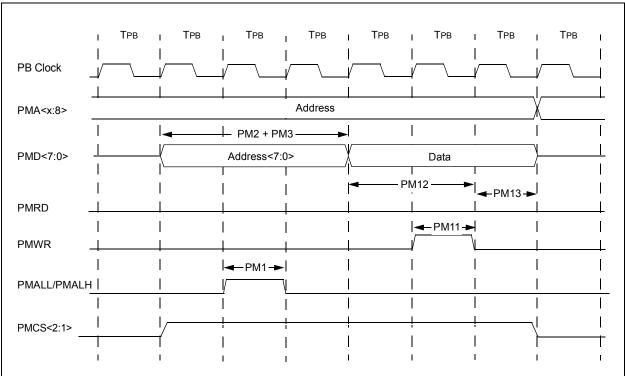

## FIGURE 31-22: PARALLEL MASTER PORT WRITE TIMING DIAGRAM

### TABLE 31-40: PARALLEL MASTER PORT WRITE TIMING REQUIREMENTS

| AC CHARACTERISTICS |         |                                                                           | $\begin{tabular}{ l l l l l l l l l l l l l l l l l l l$ |       |      |       |            |

|--------------------|---------|---------------------------------------------------------------------------|----------------------------------------------------------|-------|------|-------|------------|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>                                            | Min.                                                     | Тур.  | Max. | Units | Conditions |

| PM11               | Twr     | PMWR Pulse Width                                                          | _                                                        | 1 Трв | _    | _     | _          |

| PM12               | TDVSU   | Data Out Valid before PMWR or<br>PMENB goes Inactive (data setup<br>time) | —                                                        | 2 Трв | —    | —     | _          |

| PM13               | TDVHOLD | PMWR or PMEMB Invalid to Data<br>Out Invalid (data hold time)             | —                                                        | 1 Трв | _    | —     | —          |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

## 33.2 Package Details

The following sections give the technical details of the packages.

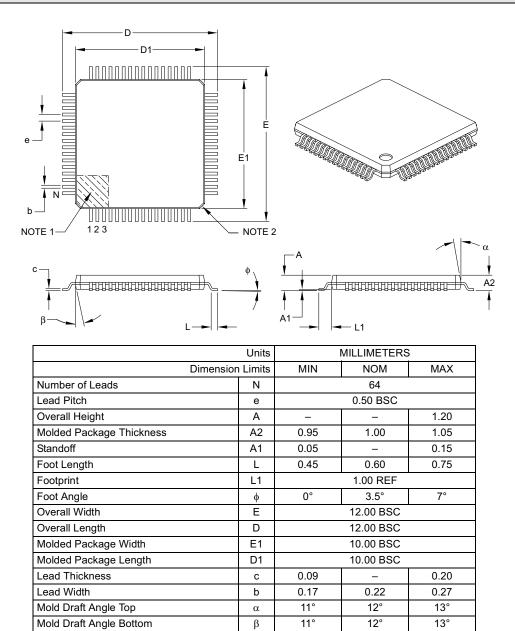

## 64-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085B

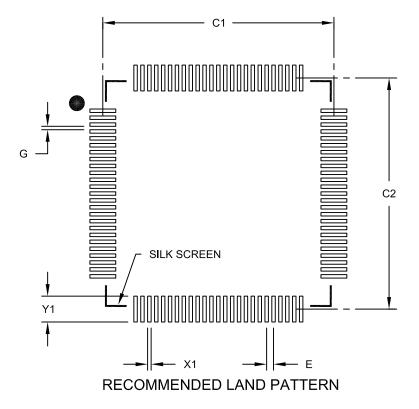

100-Lead Plastic Thin Quad Flatpack (PT)-12x12x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | MILLIMETERS |          |       |      |

|---------------------------|-------------|----------|-------|------|

| Dimensior                 | MIN         | NOM      | MAX   |      |

| Contact Pitch             |             | 0.40 BSC |       |      |

| Contact Pad Spacing       | C1          |          | 13.40 |      |

| Contact Pad Spacing       | C2          |          | 13.40 |      |

| Contact Pad Width (X100)  | X1          |          |       | 0.20 |

| Contact Pad Length (X100) | Y1          |          |       | 1.50 |

| Distance Between Pads     | G           | 0.20     |       |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2100B