Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 64K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-VQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx350f256ht-v-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

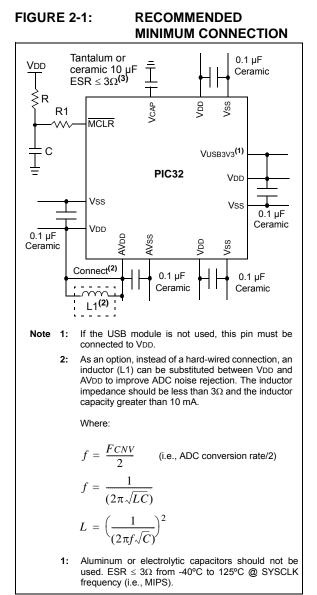

## 2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve power supply stability. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F. This capacitor should be located as close to the device as possible.

## 2.3 Capacitor on Internal Voltage Regulator (VCAP)

#### 2.3.1 INTERNAL REGULATOR MODE

A low-ESR (3 ohm) capacitor is required on the VCAP pin, which is used to stabilize the internal voltage regulator output. The VCAP pin must not be connected to VDD, and must have a CEFC capacitor, with at least a 6V rating, connected to ground. The type can be ceramic or tantalum. Refer to **Section 31.0 "Electrical Characteristics"** for additional information on CEFC specifications.

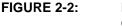

## 2.4 Master Clear (MCLR) Pin

The  $\overline{\text{MCLR}}$  pin provides two specific device functions:

- Device Reset

- · Device programming and debugging

Pulling The  $\overline{\text{MCLR}}$  pin low generates a device Reset. Figure 2-2 illustrates a typical  $\overline{\text{MCLR}}$  circuit. During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as illustrated in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components illustrated in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

3:

## EXAMPLE OF MCLR PIN CONNECTIONS

No pull-ups or bypass capacitors are allowed on

active debug/program PGECx/PGEDx pins.

## 2.9 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

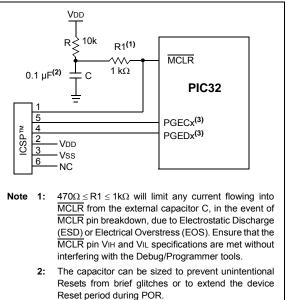

## 2.10 EMI/EMC/EFT (IEC 61000-4-4 and IEC 61000-4-2) Suppression Considerations

The use of LDO regulators is preferred to reduce overall system noise and provide a cleaner power source. However, when utilizing switching Buck/ Boost regulators as the local power source for PIC32 devices, as well as in electrically noisy environments or test conditions required for IEC 61000-4-4 and IEC 61000-4-2, users should evaluate the use of T-Filters (i.e., L-C-L) on the power pins, as shown in Figure 2-5. In addition to a more stable power source, use of this type of T-Filter can greatly reduce susceptibility to EMI sources and events.

FIGURE 2-5: EMI/EMC/EFT SUPPRESSION CIRCUIT

## 7.1 Interrupts Control Registers

## TABLE 7-2: INTERRUPT REGISTER MAP

| ess                         |                  | 6             |               |        |         |         |             |         |            | Bits   |          |                       |                       |                      |               |                      |        |               |               |

|-----------------------------|------------------|---------------|---------------|--------|---------|---------|-------------|---------|------------|--------|----------|-----------------------|-----------------------|----------------------|---------------|----------------------|--------|---------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name | Bit Range     | 31/15         | 30/14  | 29/13   | 28/12   | 27/11       | 26/10   | 25/9       | 24/8   | 23/7     | 22/6                  | 21/5                  | 20/4                 | 19/3          | 18/2                 | 17/1   | 16/0          | All<br>Resets |

| 1000                        | INTCON           | 31:16         | _             | —      | _       | _       | _           |         | _          | _      | _        | _                     | _                     |                      | _             | —                    | —      | SS0           | 0000          |

| 1000                        | INTCON           | 15:0          | _             | —      | —       | MVEC    | —           |         | TPC<2:0>   |        | —        | _                     | _                     | INT4EP               | INT3EP        | INT2EP               | INT1EP | INT0EP        | 0000          |

| 1010                        | INTSTAT          | 31:16         | _             |        | —       | —       | —           |         | —          |        | _        | _                     |                       | -                    |               | _                    | _      | —             | 0000          |

| 1010                        | INTSTAT          | 15:0          | _             | _      | —       | —       | -           |         | SRIPL<2:0> |        | -        | _                     |                       |                      | VEC<5:        | 0>                   |        |               | 0000          |

| 1020                        | IPTMR            | 31:16<br>15:0 | IPTMR<31:0>   |        |         |         |             |         |            |        |          | 0000                  |                       |                      |               |                      |        |               |               |

| 4000                        | 1500             | 31:16         | FCEIF         | RTCCIF | FSCMIF  | AD1IF   | OC5IF       | IC5IF   | IC5EIF     | T5IF   | INT4IF   | OC4IF                 | IC4IF                 | IC4EIF               | T4IF          | INT3IF               | OC3IF  | IC3IF         | 0000          |

| 1030                        | IFS0             | 15:0          | IC3EIF        | T3IF   | INT2IF  | OC2IF   | IC2IF       | IC2EIF  | T2IF       | INT1IF | OC1IF    | IC1IF                 | IC1EIF                | T1IF                 | <b>INT0IF</b> | CS1IF                | CS0IF  | CTIF          | 0000          |

| 1040                        | IFS1             | 31:16         | <b>U3RXIF</b> | U3EIF  | I2C2MIF | I2C2SIF | I2C2BIF     | U2TXIF  | U2RXIF     | U2EIF  | SPI2TXIF | SPI2RXIF              | SPI2EIF               | PMPEIF               | PMPIF         | CNGIF                | CNFIF  | CNEIF         | 0000          |

| 1040                        | IFOT             | 15:0          | CNDIF         | CNCIF  | CNBIF   | CNAIF   | I2C1MIF     | I2C1SIF | I2C1BIF    | U1TXIF | U1RXIF   | U1EIF                 | SPI1TXIF              | SPI1RXIF             | SPI1EIF       | USBIF <sup>(2)</sup> | CMP2IF | CMP1IF        | 0000          |

| 1050                        | IFS2             | 31:16         | _             | _      | —       | —       | —           |         | _          |        | —        | _                     | _                     |                      |               | _                    | _      | —             | 0000          |

| 1050                        | IF32             | 15:0          | _             |        | —       | —       | DMA3IF      | DMA2IF  | DMA1IF     | DMA0IF | CTMUIF   | U5TXIF <sup>(1)</sup> | U5RXIF <sup>(1)</sup> | U5EIF <sup>(1)</sup> | U4TXIF        | U4RXIF               | U4EIF  | <b>U3TXIF</b> | 0000          |

| 1060                        | IEC0             | 31:16         | FCEIE         | RTCCIE | FSCMIE  | AD1IE   | OC5IE       | IC5IE   | IC5EIE     | T5IE   | INT4IE   | OC4IE                 | IC4IE                 | IC4EIE               | T4IE          | INT3IE               | OC3IE  | IC3IE         | 0000          |

| 1000                        | ilou             | 15:0          | IC3EIE        | T3IE   | INT2IE  | OC2IE   | IC2IE       | IC2EIE  | T2IE       | INT1IE | OC1IE    | IC1IE                 | IC1EIE                | T1IE                 | INT0IE        | CS1IE                | CS0IE  | CTIE          | 0000          |

| 1070                        | IEC1             | 31:16         | <b>U3RXIE</b> | U3EIE  | I2C2MIE | I2C2SIE | I2C2BIE     | U2TXIE  | U2RXIE     | U2EIE  | SPI2TXIE | SPI2RXIE              | SPI2EIE               | PMPEIE               | PMPIE         | CNGIE                | CNFIE  | CNEIE         | 0000          |

|                             |                  | 15:0          | CNDIE         | CNCIE  | CNBIE   | CNAIE   | I2C1MIE     | I2C1SIE | I2C1BIE    | U1TXIE | U1RXIE   | U1EIE                 | SPI1TXIE              | SPI1RXIE             | SPI1EIE       | USBIE <sup>(2)</sup> | CMP2IE | CMP1IE        | 0000          |

| 1080                        | IEC2             | 31:16         | _             | _      | —       | _       | —           | —       | —          | —      | —        | —                     | —                     | —                    | —             | —                    | —      | —             | 0000          |

|                             | .202             | 15:0          | _             |        | —       | —       | DMA3IE      | DMA2IE  | DMA1IE     | DMA0IE | CTMUIE   | U5TXIE <sup>(1)</sup> | U5RXIE <sup>(1)</sup> | U5EIE <sup>(1)</sup> | U4TXIE        | U4RXIE               | U4EIE  | <b>U3TXIE</b> | 0000          |

| 1090                        | IPC0             | 31:16         | —             | —      | —       |         | INT0IP<2:0> |         | INTOIS     |        | —        | —                     |                       | CS1IP<2:0>           |               | CS1IS                |        | 0000          |               |

|                             |                  | 15:0          | —             | —      | —       |         | CS0IP<2:0>  |         | CS0IS      | -      | —        | —                     | —                     |                      | CTIP<2:0>     |                      | CTIS   |               | 0000          |

| 10A0                        | IPC1             | 31:16         | —             | —      | —       |         | INT1IP<2:0> |         | INT1IS     | -      | —        | —                     | —                     | -                    | 0C1IP<2:0>    |                      | OC1IS  |               | 0000          |

|                             |                  | 15:0          | —             | —      | —       |         | IC1IP<2:0>  |         | IC1IS-     | <1:0>  | _        | —                     | —                     |                      | T1IP<2:0>     |                      | T1IS   | <1:0>         | 0000          |

| 10B0                        | IPC2             | 31:16         | —             | —      | —       |         | INT2IP<2:0> |         | INT2IS     |        | —        | —                     |                       |                      | C2IP<2:0>     |                      | OC2IS  |               | 0000          |

|                             |                  | 15:0          | —             | —      | —       |         | IC2IP<2:0>  |         | IC2IS      | <1:0>  | —        | —                     |                       | T2IP<2:0>            |               | T2IS                 | <1:0>  | 0000          |               |

| 10C0                        | IPC3             | 31:16         | _             |        | —       |         | INT3IP<2:0> |         | INT3IS     |        | —        | —                     |                       | -                    | C3IP<2:0>     |                      | OC3IS  |               | 0000          |

|                             |                  | 15:0          | —             | —      | —       |         | IC3IP<2:0>  |         | IC3IS-     | <1:0>  | —        | —                     |                       | T3IP<2:0>            |               | T3IS-                |        | 0000          |               |

| 10D0                        | IPC4             | 31:16         | _             |        | —       |         | INT4IP<2:0> |         | INT4IS     | -      |          | —                     |                       | OC4IP<2:0>           |               | OC4IS                |        | 0000          |               |

|                             |                  | 15:0          | _             | _      | —       |         | IC4IP<2:0>  |         | IC4IS      |        | _        | _                     | _                     | T4IP<2:0>            |               | T4IS                 |        | 0000          |               |

| 10E0                        | IPC5             | 31:16         | _             |        | —       |         | AD1IP<2:0>  |         | AD1IS      |        |          | —                     |                       |                      | C5IP<2:0>     |                      | OC5IS  |               | 0000          |

|                             |                  | 15:0          | _             | —      | —       |         | IC5IP<2:0>  |         | IC5IS      | <1:0>  | —        | —                     | —                     | -                    | T5IP<2:0>     |                      | T5IS   | <1:0>         | 0000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This bit is only available on 100-pin devices.

2: This bit is only implemented on devices with a USB module.

| Bit<br>Range | Bit<br>31/23/15/7         | Bit<br>30/22/14/6              | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1  | Bit<br>24/16/8/0 |  |  |  |

|--------------|---------------------------|--------------------------------|-------------------|-------------------|---------------------|-------------------|-------------------|------------------|--|--|--|

| 04-04        | U-0                       | R/W-0                          | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0            |  |  |  |

| 31:24        |                           | - RODIV<14:8> <sup>(1,3)</sup> |                   |                   |                     |                   |                   |                  |  |  |  |

| 00.40        | R/W-0                     | R/W-0                          | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0            |  |  |  |

| 23:16        | RODIV<7:0> <sup>(3)</sup> |                                |                   |                   |                     |                   |                   |                  |  |  |  |

| 45.0         | R/W-0                     | U-0                            | R/W-0             | R/W-0             | R/W-0               | U-0               | R/W-0, HC         | R-0, HS, HC      |  |  |  |

| 15:8         | ON                        | _                              | SIDL              | OE                | RSLP <sup>(2)</sup> | —                 | DIVSWEN           | ACTIVE           |  |  |  |

|              | U-0                       | U-0                            | U-0               | U-0               | R/W-0               | R/W-0             | R/W-0             | R/W-0            |  |  |  |

| 7:0          |                           | _                              | _                 | _                 |                     | ROSEL             | -<3:0> <b>(1)</b> |                  |  |  |  |

#### **REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER**

| Legend:           | HC = Hardware Clearable | HS = Hardware Settable   |                    |  |

|-------------------|-------------------------|--------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, r | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared     | x = Bit is unknown |  |

- bit 31 Unimplemented: Read as '0'

- bit 30-16 **RODIV<14:0>:** Reference Clock Divider bits<sup>(1,3)</sup> This value selects the Reference Clock Divider bits. See Figure 8-1 for more information. bit 15 **ON:** Output Enable bit 1 = Reference Oscillator Module is enabled 0 = Reference Oscillator Module is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Peripheral Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

- bit 12 OE: Reference Clock Output Enable bit

- 1 = Reference clock is driven out on REFCLKO pin

- 0 = Reference clock is not driven out on REFCLKO pin

- bit 11 RSLP: Reference Oscillator Module Run in Sleep bit<sup>(2)</sup>

- 1 = Reference Oscillator Module output continues to run in Sleep

- 0 = Reference Oscillator Module output is disabled in Sleep

- bit 10 Unimplemented: Read as '0'

- bit 9 DIVSWEN: Divider Switch Enable bit

- 1 = Divider switch is in progress

- 0 = Divider switch is complete

- bit 8 ACTIVE: Reference Clock Request Status bit

- 1 = Reference clock request is active

- 0 = Reference clock request is not active

- bit 7-4 Unimplemented: Read as '0'

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- **2:** This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | ROTRIM<8:1>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | ROTRIM<0>         | _                 | —                 | _                 | —                 | —                 | -                | —                |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15:8         | —                 | _                 | —                 | _                 | —                 | —                 | _                | —                |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |

#### REGISTER 8-4: REFOTRIM: REFERENCE OSCILLATOR TRIM REGISTER

| Legend:           | y = Value set from Configuration bits on POR |                                    |                    |  |  |  |

|-------------------|----------------------------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                             | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                             | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-23 ROTRIM<8:0>: Reference Oscillator Trim bits

Note: While the ON bit (REFOCON<15>) is '1', writes to this register do not take effect until the DIVSWEN bit is also set to '1'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

|              | DCRCDATA<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | DCRCDATA<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | DCRCDATA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

|              |                   |                   |                   | DCRCDA            | TA<7:0>           |                   |                  |                  |  |  |  |

#### REGISTER 10-5: DCRCDATA: DMA CRC DATA REGISTER

## Legend:

| Legena:           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-0 DCRCDATA<31:0>: CRC Data Register bits

Writing to this register will seed the CRC generator. Reading from this register will return the current value of the CRC. Bits greater than PLEN will return '0' on any read.

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): Only the lower 16 bits contain IP header checksum information. The upper 16 bits are always '0'. Data written to this register is converted and read back in 1's complement form (i.e., current IP header checksum value).

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Bits greater than PLEN will return '0' on any read.

## REGISTER 10-6: DCRCXOR: DMA CRCXOR ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | DCRCXOR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | DCRCXOR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | DCRCXOR<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | DCRCXO            | R<7:0>            |                   |                  |                  |  |  |

| Legend:           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-0 DCRCXOR<31:0>: CRC XOR Register bits

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): This register is unused.

When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

- 1 = Enable the XOR input to the Shift register

- 0 = Disable the XOR input to the Shift register; data is shifted in directly from the previous stage in the register

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        |                   | _                 | _                 | _                 | _                 | _                 | _                | —                |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        |                   | —                 | -                 |                   | _                 |                   |                  | —                |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         | CHSPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   |                   | CHSPTF            | 8<7:0>            |                   |                  |                  |  |  |

#### REGISTER 10-14: DCHxSPTR: DMA CHANNEL 'x' SOURCE POINTER REGISTER

#### Legend:

| 0                 |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSPTR<15:0>: Channel Source Pointer bits

**Note:** When in Pattern Detect mode, this register is reset on a pattern detect.

#### REGISTER 10-15: DCHxDPTR: DMA CHANNEL 'x' DESTINATION POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 | —                 | _                 | _                 |                   | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | _                 | —                 | _                 | —                | —                |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         |                   |                   |                   | CHDPTR            | <15:8>            |                   |                  |                  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | CHDPTF            | R<7:0>            |                   |                  |                  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31-16 | <b>Unimplemented:</b> Read as '0' |

|-----------|-----------------------------------|

|-----------|-----------------------------------|

bit 15-0 CHDPTR<15:0>: Channel Destination Pointer bits

1111111111111111 = Points to byte 65,535 of the destination

## TABLE 12-4: PORTB REGISTER MAP

| ess                         |                                 | 0         |               |               |               |               |               |               |              | Bits         |              |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|---------------|---------------|---------------|---------------|---------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14         | 29/13         | 28/12         | 27/11         | 26/10         | 25/9         | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6100                        | ANSELB                          | 31:16     | —             | —             | -             | -             | —             | _             | -            | _            | _            | _            | —            |              | —            | — ·          | -            | —            | 0000          |

| 0100                        | ANOLLD                          | 15:0      | ANSELB15      | ANSELB14      | ANSELB13      | ANSELB12      | ANSELB11      | ANSELB10      | ANSELB9      | ANSELB8      | ANSELB7      | ANSELB6      | ANSELB5      | ANSELB4      | ANSELB3      | ANSELB2      | ANSELB1      | ANSELB0      | FFFF          |

| 6110                        | TRISB                           | 31:16     | _             | —             | _             | —             | —             | _             | _            | _            | _            | —            | —            | _            | —            | _            | _            | —            | 0000          |

| 0110                        | ITTIOD                          | 15:0      | TRISB15       | TRISB14       | TRISB13       | TRISB12       | TRISB11       | TRISB10       | TRISB9       | TRISB8       | TRISB7       | TRISB6       | TRISB5       | TRISB4       | TRISB3       | TRISB2       | TRISB1       | TRISB0       | $_{\rm XXXX}$ |

| 6120                        | PORTB                           | 31:16     | _             | —             | _             | —             | —             | _             | _            | _            | _            | —            | —            | _            | —            | _            | _            | —            | 0000          |

| 0120                        | TORTD                           | 15:0      | RB15          | RB14          | RB13          | RB12          | RB11          | RB10          | RB9          | RB8          | RB7          | RB6          | RB5          | RB4          | RB3          | RB2          | RB1          | RB0          | $_{\rm XXXX}$ |

| 6130                        | LATB                            | 31:16     | _             | —             | _             | —             | —             | _             | _            | _            | _            | —            | —            | _            | —            | _            | _            | —            | 0000          |

| 0130                        | LAID                            | 15:0      | LATB15        | LATB14        | LATB13        | LATB12        | LATB11        | LATB10        | LATB9        | LATB8        | LATB7        | LATB6        | LATB5        | LATB4        | LATB3        | LATB2        | LATB1        | LATB0        | $_{\rm XXXX}$ |

| 6140                        | ODCB                            | 31:16     | _             | —             | _             | —             | —             | _             | _            | _            | _            | —            | —            | _            | —            | _            | _            | —            | 0000          |

| 0140                        | ODOD                            | 15:0      | ODCB15        | ODCB14        | ODCB13        | ODCB12        | ODCB11        | ODCB10        | ODCB9        | ODCB8        | ODCB7        | ODCB6        | ODCB5        | ODCB4        | ODCB3        | ODCB2        | ODCB1        | ODCB0        | $_{\rm XXXX}$ |

| 6150                        | CNPUB                           | 31:16     | _             | —             | _             | —             | —             | _             | _            | _            | _            | —            | —            | _            | —            | _            | _            | —            | 0000          |

| 0150                        |                                 | 15:0      | CNPUB15       | CNPUB14       | CNPUB13       | CNPUB12       | CNPUB11       | CNPUB10       | CNPUB9       | CNPUB8       | CNPUB7       | CNPUB6       | CNPUB5       | CNPUB4       | CNPUB3       | CNPUB2       | CNPUB1       | CNPUB0       | $_{\rm XXXX}$ |

| 6160                        | CNPDB                           | 31:16     | _             | —             | _             | —             | —             | _             | _            | _            | _            | —            | —            | _            | —            | _            | _            | —            | 0000          |

| 0100                        |                                 | 15:0      | CNPDB15       | CNPDB14       | CNPDB13       | CNPDB12       | CNPDB11       | CNPDB10       | CNPDB9       | CNPDB8       | CNPDB7       | CNPDB6       | CNPDB5       | CNPDB4       | CNPDB3       | CNPDB2       | CNPDB1       | CNPDB0       | xxxx          |

| 6170                        | CNCONB                          | 31:16     | —             | _             |               |               |               |               | _            |              | _            | _            | —            | _            |              |              |              |              | 0000          |

| 0170                        | ONCOME                          | 15:0      | ON            | _             | SIDL          | _             | —             | _             | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 6180                        | CNENB                           | 31:16     | _             | —             | _             | _             | —             | _             | _            |              | _            | _            | —            | _            | _            | —            | _            | _            | 0000          |

| 0100                        | CINEIND                         | 15:0      | CNIEB15       | CNIEB14       | CNIEB13       | CNIEB12       | CNIEB11       | CNIEB10       | CNIEB9       | CNIEB8       | CNIEB7       | CNIEB6       | CNIEB5       | CNIEB4       | CNIEB3       | CNIEB2       | CNIEB1       | CNIEB0       | xxxx          |

|                             |                                 | 31:16     | —             | —             | _             | _             | —             | _             | _            |              | _            | _            | —            | _            | _            | —            | _            | _            | 0000          |

| 6190                        | CNSTATB                         | 15:0      | CN<br>STATB15 | CN<br>STATB14 | CN<br>STATB13 | CN<br>STATB12 | CN<br>STATB11 | CN<br>STATB10 | CN<br>STATB9 | CN<br>STATB8 | CN<br>STATB7 | CN<br>STATB6 | CN<br>STATB5 | CN<br>STATB4 | CN<br>STATB3 | CN<br>STATB2 | CN<br>STATB1 | CN<br>STATB0 | xxxx          |

Legend:

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for Note 1: more information.

|                             |                                 | 0         | NLY   |       |       |       |       |       |      |      |      |        |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|--------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| ess                         |                                 |           |       |       |       |       |       |       |      | Bi   | ts   |        |              |              |              |              |              |              |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6   | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6510                        | TRISF                           | 31:16     | _     | _     | —     | —     | _     | —     | —    | —    | -    | —      | _            |              | —            | —            | _            | -            | 0000          |

| 0010                        | TRIOT                           | 15:0      | _     | —     | _     | _     | _     | _     | —    | _    | -    | TRISF6 | TRISF5       | TRISF4       | TRISF3       | TRISF2       | TRISF1       | TRISF0       | xxxx          |

| 6520                        | PORTE                           | 31:16     | —     | —     | —     | —     | _     | —     | —    | —    |      | —      | _            | _            |              |              |              | _            | 0000          |

| 0020                        | 1 OKI                           | 15:0      | —     | —     | —     | _     | —     | —     |      | —    | -    | RF6    | RF5          | RF4          | RF3          | RF2          | RF1          | RF0          | xxxx          |

| 6530                        | LATF                            | 31:16     | _     | —     | _     | _     | _     | _     | —    | —    | -    | —      | —            | _            | —            | —            | -            | -            | 0000          |

| 0000                        | LAU                             | 15:0      | _     | —     | _     | _     | _     | _     | —    | —    | -    | LATF6  | LATF5        | LATF4        | LATF3        | LATF2        | LATF1        | LATF0        | xxxx          |

| 6540                        | ODCF                            | 31:16     | —     | —     | —     | —     | _     | —     | —    | —    |      | —      | _            | —            |              |              |              | _            | 0000          |

| 0040                        | ODOI                            | 15:0      | —     | —     | —     | —     | _     | —     | —    | —    |      | ODCF6  | ODCF5        | ODCF4        | ODCF3        | ODCF2        | ODCF1        | ODCF0        | xxxx          |

| 6550                        | CNPUF                           | 31:16     | —     | _     | —     |       | _     |       |      |      |      | —      | —            | _            |              |              | _            | _            | 0000          |

| 0000                        |                                 | 15:0      | —     | _     | —     |       | _     |       |      |      |      | CNPUF6 | CNPUF5       | CNPUF4       | CNPUF3       | CNPUF2       | CNPUF1       | CNPUF0       | xxxx          |

| 6560                        | CNPDF                           | 31:16     | —     | _     | —     |       | _     |       |      |      |      | —      | —            | _            |              |              | _            | _            | 0000          |

| 0000                        |                                 | 15:0      | —     | —     | —     | —     | _     | —     | —    | —    | _    | CNPDF6 | CNPDF5       | CNPDF4       | CNPDF3       | CNPDF2       | CNPDF1       | CNPDF0       | xxxx          |

| 6570                        | CNCONF                          | 31:16     | —     | _     | —     |       | _     |       |      |      |      | —      | —            | _            |              |              | _            | _            | 0000          |

| 00/0                        | oncon                           | 15:0      | ON    | —     | SIDL  | —     | _     | —     | —    |      | —    | —      | —            | —            | —            | —            | _            | —            | 0000          |

| 6580                        | CNENF                           | 31:16     | —     | _     | —     |       | _     |       |      |      |      | —      | —            | _            |              |              | _            | _            | 0000          |

| 0000                        | ONLIN                           | 15:0      | —     | _     | —     |       | _     |       |      |      |      | —      | CNIEF5       | CNIEF4       | CNIEF3       | CNIEF2       | CNIEF1       | CNIEF0       | xxxx          |

|                             |                                 | 31:16     | —     | —     | —     | —     | _     | —     | —    | —    |      | —      | —            | _            |              |              |              | _            | 0000          |

| 6590                        | CNSTATF                         | 15:0      | _     | _     | —     | —     | _     | —     | —    | —    | -    | _      | CN<br>STATF5 | CN<br>STATF4 | CN<br>STATF3 | CN<br>STATF2 | CN<br>STATF1 | CN<br>STATF0 | xxxx          |

## TABLE 12-13: PORTF REGISTER MAP FOR PIC32MX330F064H, PIC32MX350F128H, PIC32MX350F256H, AND PIC32MX370F512H DEVICES

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

NOTES:

## 18.1 Control Registers

## TABLE 18-1: SPI2 AND SPI2 REGISTER MAP

| ess                         |                                 | 6         |               |         |        |              |              |              |           | Bit    | s       |        |        |          |             |          |        |         |            |

|-----------------------------|---------------------------------|-----------|---------------|---------|--------|--------------|--------------|--------------|-----------|--------|---------|--------|--------|----------|-------------|----------|--------|---------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14   | 29/13  | 28/12        | 27/11        | 26/10        | 25/9      | 24/8   | 23/7    | 22/6   | 21/5   | 20/4     | 19/3        | 18/2     | 17/1   | 16/0    | All Resets |

| 5800                        | SPI1CON                         | 31:16     | FRMEN         | FRMSYNC | FRMPOL | MSSEN        | FRMSYPW      | FF           | RMCNT<2:0 | )>     | MCLKSEL | —      |        |          |             | _        | SPIFE  | ENHBUF  | 0000       |

| 3800                        | SFILCON                         | 15:0      | ON            | _       | SIDL   | DISSDO       | MODE32       | MODE16       | SMP       | CKE    | SSEN    | CKP    | MSTEN  | DISSDI   | STXISE      | EL<1:0>  | SRXISE | EL<1:0> | 0000       |

| 5910                        | SPI1STAT                        | 31:16     | _             | _       | _      |              | RXE          | BUFELM<4:    | 0>        |        |         | _      |        |          | TXI         | BUFELM<4 | :0>    |         | 0000       |

| 5610                        | SFIISTAI                        | 15:0      | _             | _       | _      | FRMERR       | SPIBUSY      | _            | _         | SPITUR | SRMT    | SPIROV | SPIRBE |          | SPITBE      | _        | SPITBF | SPIRBF  | 19EB       |

| 5820                        | SPI1BUF                         | 31:16     |               |         |        |              |              |              |           |        |         |        |        |          |             |          |        |         | 0000       |

| 5620                        |                                 | 15:0      |               |         |        |              |              |              |           | DATA<  | 51.02   |        |        |          |             |          |        |         | 0000       |

| 5830                        | SPI1BRG                         | 31:16     | _             |         |        |              |              |              |           |        |         | —      | —      | —        | —           | —        | —      | —       | 0000       |

| 5650                        |                                 | 15:0      | —             | —       | —      | _            | —            | —            | _         |        |         |        |        | BRG<8:0> |             |          |        |         | 0000       |

|                             |                                 | 31:16     | —             | —       | —      | _            | —            | —            | _         | _      | _       | —      | —      | _        | —           | —        | —      | -       | 0000       |

| 5840                        | SPI1CON2                        | 15:0      | SPI<br>SGNEXT | -       | —      | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV    | IGNTUR | AUDEN   | —      | —      | —        | AUD<br>MONO | —        | AUDMC  | )D<1:0> | 0000       |

| 5400                        | SPI2CON                         | 31:16     | FRMEN         | FRMSYNC | FRMPOL | MSSEN        | FRMSYPW      | FF           | RMCNT<2:0 | )>     | MCLKSEL | _      | _      | —        | _           | _        | SPIFE  | ENHBUF  | 0000       |

| 5A00                        | SPIZCON                         | 15:0      | ON            | _       | SIDL   | DISSDO       | MODE32       | MODE16       | SMP       | CKE    | SSEN    | CKP    | MSTEN  | DISSDI   | STXISE      | EL<1:0>  | SRXISE | EL<1:0> | 0000       |

| 5440                        | SPI2STAT                        | 31:16     | —             | —       | _      |              | RXE          | BUFELM<4:    | 0>        |        |         | _      |        |          | TXI         | BUFELM<4 | :0>    |         | 0000       |

| SATU                        | 3F1231AI                        | 15:0      | _             |         | —      | FRMERR       | SPIBUSY      | _            | _         | SPITUR | SRMT    | SPIROV | SPIRBE | _        | SPITBE      | _        | SPITBF | SPIRBF  | 19EB       |

| 5A20                        | SPI2BUF                         | 31:16     |               |         |        |              |              |              |           | DATA<  | 31.05   |        |        |          |             |          |        |         | 0000       |

| 5A20                        | 3FI2D0I                         | 15:0      |               |         |        |              |              |              |           |        |         |        |        | 0000     |             |          |        |         |            |

| 5A30                        | SPI2BRG                         | 31:16     | —             | —       | —      | _            | —            | —            | _         | _      | _       | —      | —      | _        | —           | —        | —      | -       | 0000       |

| 5A30                        |                                 | 15:0      | _             | —       | -      |              | _            | _            | _         |        |         |        |        | BRG<8:0> |             |          |        |         | 0000       |

|                             |                                 | 31:16     | _             | —       | —      | _            | —            | —            | _         | _      | _       | —      | —      | —        | _           | —        | —      | —       | 0000       |

| 5A40                        | SPI2CON2                        | 15:0      | SPI<br>SGNEXT | _       | _      | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV    | IGNTUR | AUDEN   | _      | _      |          | AUD<br>MONO | _        | AUDMC  | )D<1:0> | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except SPIxBUF have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

# PIC32MX330/350/370/430/450/470

## REGISTER 19-1: I2CxCON: I<sup>2</sup>C CONTROL REGISTER

|              | -                 |                   |                   |                   |                   |                   |                  |                  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | —                 | _                 | —                 | —                 | —                 | _                | _                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | —                 | _                 | _                 | —                 | _                 | _                | _                |  |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-1, HC         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | 0N <sup>(1)</sup> | —                 | SIDL              | SCLREL            | STRICT            | A10M              | DISSLW           | SMEN             |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |  |

| 7:0          | GCEN              | STREN             | ACKDT             | ACKEN             | RCEN              | PEN               | RSEN             | SEN              |  |

| Legend:           | HC = Cleared in Hardwar | Writable bit U = Unimplemented bit, read as '0'   |                    |  |  |  |  |

|-------------------|-------------------------|---------------------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit        | = Writable bit U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared                              | x = Bit is unknown |  |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** I<sup>2</sup>C Enable bit<sup>(1)</sup>

- 1 = Enables the  $I^2C$  module and configures the SDA and SCL pins as serial port pins

- 0 = Disables the  $I^2$ C module; all  $I^2$ C pins are controlled by PORT functions

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

- **SCLREL:** SCLx Release Control bit (when operating as I<sup>2</sup>C slave)

- 1 = Release SCLx clock

bit 12

- 0 = Hold SCLx clock low (clock stretch)

- If STREN = 1:

Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware clear at beginning of slave transmission. Hardware clear at end of slave reception.

#### If STREN = 0:

Bit is R/S (i.e., software can only write '1' to release clock). Hardware clear at beginning of slave transmission.

- bit 11 STRICT: Strict I<sup>2</sup>C Reserved Address Rule Enable bit

- 1 = Strict reserved addressing is enforced. Device does not respond to reserved address space or generate addresses in reserved address space.

- 0 = Strict I<sup>2</sup>C Reserved Address Rule is not enabled

#### bit 10 A10M: 10-bit Slave Address bit

- 1 = I2CxADD is a 10-bit slave address

- 0 = I2CxADD is a 7-bit slave address

- bit 9 **DISSLW:** Disable Slew Rate Control bit

- 1 = Slew rate control is disabled

- 0 = Slew rate control is enabled

- bit 8 SMEN: SMBus Input Levels bit

- 1 = Enable I/O pin thresholds compliant with SMBus specification

- 0 = Disable SMBus input thresholds

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

## REGISTER 19-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER (CONTINUED)

| <ul> <li>1 = Indicates that a Stop bit has been detected last         0 = Stop bit was not detected last         Hardware set or clear when Start, Repeated Start or Stop detected.     </li> <li>5: Start bit         1 = Indicates that a Start (or Repeated Start) bit has been detected last         0 = Start bit was not detected last         Hardware set or clear when Start, Repeated Start or Stop detected.     </li> <li>bit 2         <b>R_W:</b> Read/Write Information bit (when operating as I<sup>2</sup>C slave)         1 = Read – indicates data transfer is output from slave         0 = Write – indicates data transfer is input to slave         Hardware set or clear after reception of I<sup>2</sup>C device address byte.     </li> <li>bit 1         <b>RBF:</b> Receive Buffer Full Status bit         1 = Receive complete, I2CxRCV is full         0 = Receive not complete, I2CxRCV is empty         Hardware set when I2CxRCV is written with received byte. Hardware clear when software         reads I2CxRCV.     </li> <li>bit 0         <b>TBF:</b> Transmit Buffer Full Status bit         1 = Transmit in progress, I2CxTRN is full         </li> </ul> | bit 4 | P: Stop bit                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------|

| <ul> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> <li>bit 3 S: Start bit <ol> <li>= Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>= Start bit was not detected last</li> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> </ol> </li> <li>bit 2 R_W: Read/Write Information bit (when operating as I<sup>2</sup>C slave) <ol> <li>= Read – indicates data transfer is output from slave</li> <li>Write – indicates data transfer is input to slave</li> <li>Write – indicates data transfer is of I<sup>2</sup>C device address byte.</li> </ol> </li> <li>bit 1 RBF: Receive Buffer Full Status bit <ol> <li>= Receive not complete, I2CxRCV is full</li> <li>= Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> </ol> </li> <li>bit 0 TBF: Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                       |       |                                                                                   |

| bit 3       S: Start bit         1 = Indicates that a Start (or Repeated Start) bit has been detected last         0 = Start bit was not detected last         Hardware set or clear when Start, Repeated Start or Stop detected.         bit 2       R_W: Read/Write Information bit (when operating as I <sup>2</sup> C slave)         1 = Read – indicates data transfer is output from slave         0 = Write – indicates data transfer is input to slave         Hardware set or clear after reception of I <sup>2</sup> C device address byte.         bit 1       RBF: Receive Buffer Full Status bit         1 = Receive complete, I2CxRCV is full       0 = Receive not complete, I2CxRCV is empty         Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.         bit 0       TBF: Transmit Buffer Full Status bit                                                                                                                                                                                                                                                                                                                |       | •                                                                                 |

| <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last<br/>Hardware set or clear when Start, Repeated Start or Stop detected.</li> <li>bit 2 R_W: Read/Write Information bit (when operating as I<sup>2</sup>C slave)</li> <li>1 = Read – indicates data transfer is output from slave</li> <li>0 = Write – indicates data transfer is input to slave<br/>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> <li>bit 1 RBF: Receive Buffer Full Status bit</li> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty<br/>Hardware set when I2CxRCV is written with received byte. Hardware clear when software<br/>reads I2CxRCV.</li> <li>bit 0 TBF: Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                 |       | Hardware set or clear when Start, Repeated Start or Stop detected.                |

| <ul> <li>0 = Start bit was not detected last<br/>Hardware set or clear when Start, Repeated Start or Stop detected.</li> <li>bit 2 R_W: Read/Write Information bit (when operating as I<sup>2</sup>C slave)         <ol> <li>1 = Read – indicates data transfer is output from slave</li> <li>0 = Write – indicates data transfer is input to slave</li> <li>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> </ol> </li> <li>bit 1 RBF: Receive Buffer Full Status bit         <ol> <li>= Receive complete, I2CxRCV is full</li> <li>= Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> </ol> </li> <li>bit 0 TBF: Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                          | bit 3 | S: Start bit                                                                      |

| bit 2 <b>R_W:</b> Read/Write Information bit (when operating as I²C slave)1 = Read – indicates data transfer is output from slave0 = Write – indicates data transfer is input to slaveHardware set or clear after reception of I²C device address byte.bit 1 <b>RBF:</b> Receive Buffer Full Status bit1 = Receive complete, I2CxRCV is full0 = Receive not complete, I2CxRCV is emptyHardware set when I2CxRCV is written with received byte. Hardware clear when softwarebit 0 <b>TBF:</b> Transmit Buffer Full Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       |                                                                                   |

| <ul> <li>1 = Read – indicates data transfer is output from slave</li> <li>0 = Write – indicates data transfer is input to slave</li> <li>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> <li>bit 1 RBF: Receive Buffer Full Status bit</li> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> <li>bit 0 TBF: Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |       | Hardware set or clear when Start, Repeated Start or Stop detected.                |

| <ul> <li>0 = Write – indicates data transfer is input to slave<br/>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> <li>bit 1 <b>RBF:</b> Receive Buffer Full Status bit</li> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty<br/>Hardware set when I2CxRCV is written with received byte. Hardware clear when software<br/>reads I2CxRCV.</li> <li>bit 0 <b>TBF:</b> Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave) |

| <ul> <li>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> <li>bit 1 <b>RBF:</b> Receive Buffer Full Status bit</li> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> <li>bit 0 <b>TBF:</b> Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       | 1 = Read – indicates data transfer is output from slave                           |

| bit 1 <b>RBF:</b> Receive Buffer Full Status bit         1 = Receive complete, I2CxRCV is full         0 = Receive not complete, I2CxRCV is empty         Hardware set when I2CxRCV is written with received byte. Hardware clear when software         reads I2CxRCV.         bit 0 <b>TBF:</b> Transmit Buffer Full Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |       |                                                                                   |

| <ul> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> <li>bit 0 TBF: Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |       | Hardware set or clear after reception of I <sup>2</sup> C device address byte.    |

| <ul> <li>0 = Receive not complete, I2CxRCV is empty<br/>Hardware set when I2CxRCV is written with received byte. Hardware clear when software<br/>reads I2CxRCV.</li> <li>bit 0 TBF: Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | bit 1 | RBF: Receive Buffer Full Status bit                                               |

| Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.         bit 0 <b>TBF:</b> Transmit Buffer Full Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       | 1 = Receive complete, I2CxRCV is full                                             |