Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 256КВ (256К х 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 64K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

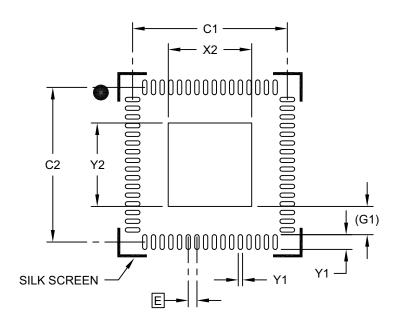

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx350f256ht-v-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the documents listed in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). This document contains device-specific information for PIC32MX330/350/370/430/450/470 devices.

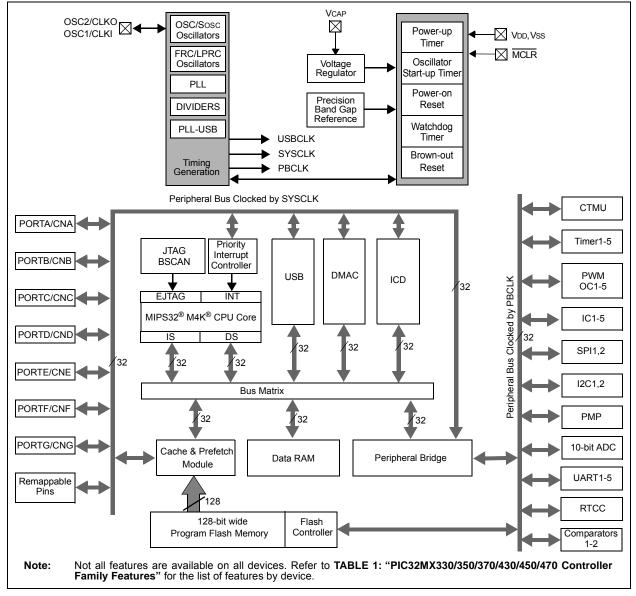

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MX330/350/ 370/430/450/470 family of devices.

Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

#### FIGURE 1-1: PIC32MX330/350/370/430/450/470 BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

|              | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-1             | U-0              | U-0              |  |  |  |  |

| 31:24        | _                 | —                 | —                 | —                 | —                 | BMX<br>CHEDMA     | —                | —                |  |  |  |  |

|              | U-0               | U-0               | U-0               | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |

| 23:16        | _                 | —                 | —                 | BMX<br>ERRIXI     | BMX<br>ERRICD     | BMX<br>ERRDMA     | BMX<br>ERRDS     | BMX<br>ERRIS     |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15:8         | —                 | —                 | —                 | _                 | _                 | —                 | —                | —                |  |  |  |  |

|              | U-0               | R/W-1             | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-1            |  |  |  |  |

| 7:0          | _                 | BMX<br>WSDRM      | —                 | —                 | —                 | E                 | 3MXARB<2:0       | >                |  |  |  |  |

#### REGISTER 4-1: BMXCON: BUS MATRIX CONFIGURATION REGISTER

#### Legend:

| Logona.           |                  |                                    |

|-------------------|------------------|------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

#### bit 31-27 Unimplemented: Read as '0'

- bit 26 BMXCHEDMA: BMX PFM Cacheability for DMA Accesses bit

- 1 = Enable program Flash memory (data) cacheability for DMA accesses (requires cache to have data caching enabled)

- 0 = Disable program Flash memory (data) cacheability for DMA accesses (hits are still read from the cache, but misses do not update the cache)

#### bit 25-21 Unimplemented: Read as '0'

#### bit 20 BMXERRIXI: Enable Bus Error from IXI bit

- 1 = Enable bus error exceptions for unmapped address accesses initiated from IXI shared bus

- 0 = Disable bus error exceptions for unmapped address accesses initiated from IXI shared bus

#### bit 19 **BMXERRICD:** Enable Bus Error from ICD Debug Unit bit

- 1 = Enable bus error exceptions for unmapped address accesses initiated from ICD

- 0 = Disable bus error exceptions for unmapped address accesses initiated from ICD

#### bit 18 BMXERRDMA: Bus Error from DMA bit

- 1 = Enable bus error exceptions for unmapped address accesses initiated from DMA

- 0 = Disable bus error exceptions for unmapped address accesses initiated from DMA

- bit 17 BMXERRDS: Bus Error from CPU Data Access bit (disabled in Debug mode)

- 1 = Enable bus error exceptions for unmapped address accesses initiated from CPU data access

- 0 = Disable bus error exceptions for unmapped address accesses initiated from CPU data access

- bit 16 BMXERRIS: Bus Error from CPU Instruction Access bit (disabled in Debug mode)

- 1 = Enable bus error exceptions for unmapped address accesses initiated from CPU instruction access

- 0 = Disable bus error exceptions for unmapped address accesses initiated from CPU instruction access

#### bit 15-7 Unimplemented: Read as '0'

- bit 6 BMXWSDRM: CPU Instruction or Data Access from Data RAM Wait State bit

- $\ensuremath{\mathtt{1}}$  = Data RAM accesses from CPU have one wait state for address setup

#### 0 = Data RAM accesses from CPU have zero wait states for address setup

#### bit 5-3 Unimplemented: Read as '0'

- bit 2-0 BMXARB<2:0>: Bus Matrix Arbitration Mode bits

- 111 = Reserved (using these configuration modes will produce undefined behavior)

- :

011 = Reserved (using these configuration modes will produce undefined behavior)

- 010 = Arbitration Mode 2

- 001 = Arbitration Mode 1 (default)

- 000 = Arbitration Mode 0

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|--|--|

| 24.24        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |  |  |  |

| 31:24        | BMXDRMSZ<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |  |  |

| 00.40        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |  |  |  |

| 23:16        | BMXDRMSZ<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |  |  |  |

| 15:8         | BMXDRMSZ<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | BMXDR             | MSZ<7:0>          |                   |                  | BMXDRMSZ<7:0>    |  |  |  |  |  |  |  |  |  |

#### BMXDRMSZ: DATA RAM SIZE REGISTER **REGISTER 4-5:**

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 BMXDRMSZ<31:0>: Data RAM Memory (DRM) Size bits

Static value that indicates the size of the Data RAM in bytes: 0x00004000 = Device has 16 KB RAM 0x00008000 = Device has 32 KB RAM 0x00010000 = Device has 64 KB RAM 0x00020000 = Device has 128 KB RAM

#### **REGISTER 4-6: BMXPUPBA: PROGRAM FLASH (PFM) USER PROGRAM BASE ADDRESS** REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 | —                 | _                 | —                 | —                 | —                 | —                | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | _                 | _                 | _                 | _                 | BMXPUPBA<19:16>   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0              | R-0              |  |  |  |

| 15:8         |                   | BMXPUPBA<15:8>    |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   |                   |                   | BMXPU             | PBA<7:0>          |                   |                  |                  |  |  |  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-20 Unimplemented: Read as '0'

bit 19-11 BMXPUPBA<19:11>: Program Flash (PFM) User Program Base Address bits

#### bit 10-0 BMXPUPBA<10:0>: Read-Only bits Value is always '0', which forces 2 KB increments

Note 1: At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernel mode data usage.

2: The value in this register must be less than or equal to BMXPFMSZ.

#### 9.0 PREFETCH CACHE

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 4. "Prefetch Cache" (DS60001119), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

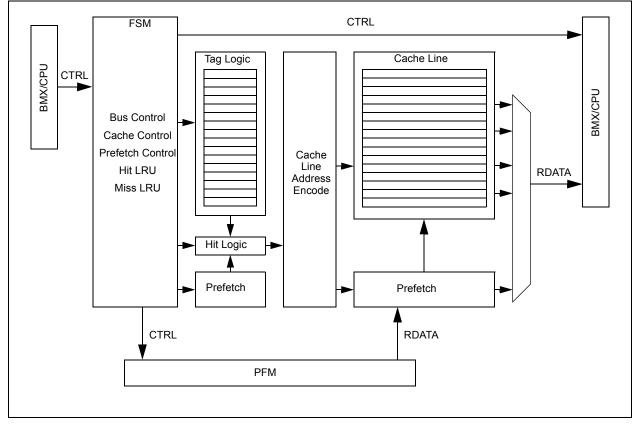

Prefetch cache increases performance for applications executing out of the cacheable program Flash memory regions by implementing instruction caching, constant data caching and instruction prefetching.

#### 9.1 Features

- 16 fully associative lockable cache lines

- 16-byte cache lines

- Up to four cache lines allocated to data

- Two cache lines with address mask to hold repeated instructions

- · Pseudo LRU replacement policy

- · All cache lines are software writable

- · 16-byte parallel memory fetch

- · Predictive instruction prefetch

A simplified block diagram of the Prefetch Cache module is illustrated in Figure 9-1.

#### FIGURE 9-1: PREFETCH CACHE MODULE BLOCK DIAGRAM

#### 9.2 Control Registers

#### TABLE 9-1: PREFETCH REGISTER MAP

| ess                         |                       |               |               |             |           |             |             |            |            | Bit        | s       |      |       |            |         |       |          |        |              |

|-----------------------------|-----------------------|---------------|---------------|-------------|-----------|-------------|-------------|------------|------------|------------|---------|------|-------|------------|---------|-------|----------|--------|--------------|

| Virtual Address<br>(BF88_#) | Register<br>Name      | Bit Range     | 31/15         | 30/14       | 29/13     | 28/12       | 27/11       | 26/10      | 25/9       | 24/8       | 23/7    | 22/6 | 21/5  | 20/4       | 19/3    | 18/2  | 17/1     | 16/0   | All Resets   |

| 4000                        | CHECON <sup>(1)</sup> | 31:16         | —             | _           | —         | —           |             | _          | —          | —          | _       |      | —     |            | —       | —     |          | CHECOH | 0000         |

| 1000                        |                       | 15:0          | —             | _           |           | —           | _           | _          | DCSZ       | <1:0>      | —       |      | PREFE | N<1:0>     | —       | P     | FMWS<2:0 | )>     | 0007         |

| 4010                        | CHEACC <sup>(1)</sup> |               | CHEWEN        | —           | —         | —           | —           | —          | —          | —          | —       | —    | —     | —          | —       | —     | —        | —      | 0000         |

|                             |                       | 15:0          | —             | _           | —         | —           | —           | _          | —          | —          | —       |      | —     | —          |         | CHEID | X<3:0>   |        | 00xx         |

| 4020                        | CHETAG <sup>(1)</sup> | 31:16         | LTAGBOOT      | —           | —         | —           | —           | —          | —          | —          |         |      |       | LTAG<      | :23:16> |       |          |        | xxx0         |

| 1020                        |                       |               |               |             |           |             |             | LTAG<      | 15:4>      |            |         |      |       |            | LVALID  | LLOCK | LTYPE    | —      | xxx2         |

| 4030                        | CHEMSK <sup>(1)</sup> | 31:16         | —             | —           | —         | —           | —           | —          | —          | —          | —       | —    | —     | _          | —       | —     | —        | —      | 0000         |

|                             |                       | 15:0          |               |             |           |             | LN          | 1ASK<15:5  | >          |            |         |      |       | —          | —       | _     | —        | —      | xxxx         |

| 4040                        | CHEW0                 | 31:16         |               | CHEW0<31:0> |           |             |             |            |            |            |         |      | XXXX  |            |         |       |          |        |              |

|                             |                       | 15:0          |               |             |           |             |             |            |            |            |         |      |       |            |         |       |          |        |              |

| 4050                        | CHEW1                 | 31:16         |               |             |           |             |             |            |            | CHEW1      | <31:0>  |      |       |            |         |       |          |        | xxxx         |

|                             |                       | 15:0          |               |             |           |             |             |            |            |            |         |      |       |            |         |       |          |        | xxxx         |

| 4060                        | CHEW2                 | 31:16         |               |             |           |             |             |            |            | CHEW2      | <31:0>  |      |       |            |         |       |          |        | xxxx         |

|                             |                       | 15:0          |               |             |           |             |             |            |            |            |         |      |       |            |         |       |          |        | XXXX         |

| 4070                        | CHEW3                 | 31:16         |               |             |           |             |             |            |            | CHEW3      | <31:0>  |      |       |            |         |       |          |        | XXXX         |

|                             |                       | 15:0          |               |             | _         | _           | _           | _          |            |            |         |      | CH    | IELRU<24:1 | 16>     |       |          |        | XXXX         |

| 4080                        | CHELRU                | 31:16<br>15:0 |               |             |           |             |             |            | _          | CHELRU     | <15.0>  |      | CI    |            | 10-     |       |          |        | 0000         |

|                             |                       |               |               |             |           |             |             |            |            | CHELRU     | <15.0>  |      |       |            |         |       |          |        | 0000         |

| 4090                        | CHEHIT                | 31:16<br>15:0 |               |             |           |             |             |            |            | CHEHIT     | <31:0>  |      |       |            |         |       |          |        | xxxx         |

|                             |                       |               |               |             |           |             |             |            |            |            |         |      |       |            |         |       |          |        | XXXX         |

| 40A0                        | CHEMIS                | 31:16<br>15:0 |               |             |           |             |             |            |            | CHEMIS     | <31:0>  |      |       |            |         |       |          |        | xxxx         |

|                             |                       | 31:16         |               |             |           |             |             |            |            |            |         |      |       |            |         |       |          |        | xxxx         |

| 40C0                        | CHEDEADT              | 15:0          |               |             |           |             |             |            |            | CHEPFAB    | T<31:0> |      |       |            |         |       |          |        | xxxx<br>xxxx |

| Legen                       |                       |               | n value on Re | sot = u     | nimplomon | tod road as | : '0' Reset | values are | shown in h | avadocimal |         |      |       |            |         |       |          |        | XXXX         |

Legend:

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31.24        |                   |                   |                   |                   | _                 |                   | -                | _                |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | -                 | _                 | -                 | -                 | _                 | —                 | _                | _                |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 10.0         | LMASK<10:3>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 7:0          |                   | _MASK<2:0>        |                   | _                 | _                 | _                 | _                | —                |  |  |

#### REGISTER 9-4: CHEMSK: CACHE TAG MASK REGISTER

#### Legend:

| Logonal           |                  |                                             |                    |

|-------------------|------------------|---------------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | able bit U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                        | x = Bit is unknown |

bit 31-16 Unimplemented: Write '0'; ignore read

- bit 15-5 LMASK<10:0>: Line Mask bits

- 1 = Enables mask logic to force a match on the corresponding bit position in the LTAG<19:0> bits (CHETAG<23:4>) and the physical address.

- 0 = Only writeable for values of CHEIDX<3:0> bits (CHEACC<3:0>) equal to 0x0A and 0x0B. Disables mask logic.

- bit 4-0 Unimplemented: Write '0'; ignore read

|              |                   |                   | ••••              | •                 |                   |                   |                  |                  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 24.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31:24        | CHEW0<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        | CHEW0<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         | CHEW0<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 7:0          | CHEW0<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |

#### REGISTER 9-5: CHEW0: CACHE WORD 0

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-0 **CHEW0<31:0>:** Word 0 of the cache line selected by the CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

## PIC32MX330/350/370/430/450/470

#### REGISTER 10-12: DCHxSSIZ: DMA CHANNEL 'x' SOURCE SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | -                 | —                 | —                 | —                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | —                 | —                 | _                 | —                 | _                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | CHSSIZ            | <15:8>            |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHSSIZ            | <7:0>             |                   |                  |                  |

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSSIZ<15:0>: Channel Source Size bits

1111111111111111 = 65,535 byte source size

#### **REGISTER 10-13: DCHxDSIZ: DMA CHANNEL 'x' DESTINATION SIZE REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | —                 | _                 | _                 | —                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | —                 | _                 | —                 | _                | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | CHDSIZ            | <15:8>            |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   |                   |                   | CHDSIZ            | <7:0>             |                   |                  |                  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

| RPn Port Pin         | RPnR SFR | RPnR bits   | RPnR Value to Periphera<br>Selection |

|----------------------|----------|-------------|--------------------------------------|

| RPD2                 | RPD2R    | RPD2R<3:0>  | 0000 = No Connect                    |

| RPG8                 | RPG8R    | RPG8R<3:0>  | 0001 = U3TX                          |

| RPF4                 | RPF4R    | RPF4R<3:0>  | 0010 = U4RTS<br>0011 = Reserved      |

| RPD10                | RPD10R   | RPD10R<3:0> | 0100 = Reserved                      |

| RPF1                 | RPF1R    | RPF1R<3:0>  | 0101 = Reserved                      |

| RPB9                 | RPB9R    | RPB9R<3:0>  | 0110 = SDO2                          |

| RPB10                | RPB10R   | RPB10R<3:0> | 0111 = Reserved<br>1000 = Reserved   |

| RPC14                | RPC14R   | RPC14R<3:0> | 1000 = Reserved                      |

| RPB5                 | RPB5R    | RPB5R<3:0>  | 1010 = Reserved                      |

| RPC1 <sup>(4)</sup>  | RPC1R    | RPC1R<3:0>  | 1011 <b>= OC3</b>                    |

| RPD14 <sup>(4)</sup> | RPD14R   | RPD14R<3:0> | 1100 = Reserved<br>1101 = C2OUT      |

| RPG1 <sup>(4)</sup>  | RPG1R    | RPG1R<3:0>  | 1110 = Reserved                      |

| RPA14 <sup>(4)</sup> | RPA14R   | RPA14R<3:0> | 1111 = Reserved                      |

| RPD3                 | RPD3R    | RPD3R<3:0>  | 0000 = No Connect                    |

| RPG7                 | RPG7R    | RPG7R<3:0>  | 0001 = U2TX                          |

| RPF5                 | RPF5R    | RPF5R<3:0>  | 0010 = Reserved                      |

| RPD11                | RPD11R   | RPD11R<3:0> |                                      |

| RPF0                 | RPF0R    | RPF0R<3:0>  | 0100 = 05RTS(*)                      |

| RPB1                 | RPB1R    | RPB1R<3:0>  | 0110 = SDO2                          |

| RPE5                 | RPE5R    | RPE5R<3:0>  | 0111 = Reserved                      |

| RPC13                | RPC13R   | RPC13R<3:0> | 1000 <b>= SDO1</b>                   |

| RPB3                 | RPB3R    | RPB3R<3:0>  | 1001 = Reserved                      |

| RPF3 <sup>(2)</sup>  | RPF3R    | RPF3R<3:0>  | 1010 = Reserved                      |

| RPC4 <sup>(4)</sup>  | RPC4R    | RPC4R<3:0>  | 1011 = OC4<br>1100 = Reserved        |

| RPD15 <sup>(4)</sup> | RPD15R   | RPD15R<3:0> | 1100 - Reserved                      |

| RPG0 <sup>(4)</sup>  | RPG0R    | RPG0R<3:0>  | 1110 = Reserved                      |

| RPA15 <sup>(4)</sup> | RPA15R   | RPA15R<3:0> | 1111 = Reserved                      |

#### TABLE 12-2: OUTPUT PIN SELECTION

Note 1: This selection is only available on General Purpose devices.

**2:** This selection is only available on 64-pin General Purpose devices.

3: This selection is only available on 100-pin General Purpose devices.

4: This selection is only available on 100-pin USB and General Purpose devices.

5: This selection is not available on 64-pin USB devices.

## TABLE 12-16:PORTG REGISTER MAP FOR PIC32MX330F064H, PIC32MX350F128H, PIC32MX350F256H, PIC32MX370F512H,<br/>PIC32MX430F064H, PIC32MX450F128H, PIC32MX450F256H, AND PIC32MX470F512H DEVICES ONLY

| ess                         |                                 | 6         |       |       |       |       |       |       |              | Bi           | its          |              |      |      |                    |                    |      |      |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|--------------|--------------|--------------|--------------|------|------|--------------------|--------------------|------|------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9         | 24/8         | 23/7         | 22/6         | 21/5 | 20/4 | 19/3               | 18/2               | 17/1 | 16/0 | All<br>Resets |

| 6600                        | ANSELG                          | 31:16     | _     | -     | _     | _     | _     |       | —            | _            | _            | —            |      |      | _                  | —                  | _    | _    | 0000          |

| 0000                        | ANSELG                          | 15:0      |       | -     | -     | -     | -     |       | ANSELG9      | ANSELG8      | ANSELG7      | ANSELG6      |      |      | _                  | —                  | —    | —    | 01C0          |

| 6610                        | TRISG                           | 31:16     | _     | -     | _     | _     | _     |       | —            | —            | -            | —            | _    | _    | —                  | —                  | _    | —    | 0000          |

| 0010                        | TRISO                           | 15:0      | _     | _     | _     | _     | _     | _     | TRISG9       | TRISG8       | TRISG7       | TRISG6       | _    | _    | TRISG3             | TRISG2             | _    | _    | xxxx          |

| 6620                        | PORTG                           | 31:16     | _     |       | -     | _     | -     |       | _            | _            |              | —            | _    |      | _                  | —                  | _    | _    | 0000          |

| 0020                        | FURIO                           | 15:0      | _     |       | -     | _     | -     |       | RG9          | RG8          | RG7          | RG6          | _    |      | RG3 <sup>(2)</sup> | RG2 <sup>(2)</sup> | _    | _    | xxxx          |

| 6630                        | LATG                            | 31:16     | _     |       | -     | —     |       |       | —            | —            |              | —            | -    |      | —                  | —                  | —    | —    | 0000          |

| 0030                        | LAIO                            | 15:0      | _     | —     | —     | —     | —     | _     | LATG9        | LATG8        | LATG7        | LATG6        | _    | _    | LATG3              | LATG2              | —    | —    | xxxx          |

| 6640                        | ODCG                            | 31:16     | _     | —     | —     | —     | —     | _     | —            | —            | _            | —            | _    | _    | —                  | —                  | —    | —    | 0000          |

| 0040                        | 0000                            | 15:0      | _     | —     | —     | —     | —     | _     | ODCG9        | ODCG8        | ODCG7        | ODCG6        | _    | _    | ODCG3              | ODCG2              | —    | —    | xxxx          |

| 6650                        | CNPUG                           | 31:16     | —     | _     | —     | —     | —     |       | —            | —            |              | —            | —    |      | —                  | —                  | _    | —    | 0000          |

| 0000                        |                                 | 15:0      | —     | _     | —     | —     | —     |       | CNPUG9       | CNPUG8       | CNPUG7       | CNPUG6       | —    |      | CNPUG3             | CNPUG2             | _    | —    | xxxx          |

| 6660                        | CNPDG                           | 31:16     | —     | _     | —     | —     | _     |       | —            | —            |              | —            | —    | _    | —                  | —                  | _    | —    | 0000          |

| 0000                        |                                 | 15:0      | —     | _     | —     | —     | _     |       | CNPDG9       | CNPDG8       | CNPDG7       | CNPDG6       | —    | _    | CNPDG3             | CNPDG2             | _    | —    | xxxx          |

| 6670                        | CNCONG                          | 31:16     | —     | _     | —     | —     | _     |       | —            | _            |              | —            | —    | _    | —                  | —                  | _    | —    | 0000          |

| 0070                        | oncono                          | 15:0      | ON    | _     | SIDL  | —     | _     |       | —            | _            |              | —            | —    | _    | —                  | —                  | _    | —    | 0000          |

| 6680                        | CNENG                           | 31:16     | —     | _     | —     | —     | _     |       | —            | _            |              | —            | —    | _    | —                  | —                  | _    | —    | 0000          |

| 0000                        | ONLING                          | 15:0      | —     | _     | —     | —     | _     |       | CNIEG9       | CNIEG8       | CNIEG7       | CNIEG6       | —    | _    | CNIEG3             | CNIEG2             | _    | —    | xxxx          |

|                             |                                 | 31:16     | —     | _     | —     | —     | —     |       | —            | _            | _            | —            | —    |      | —                  | —                  | _    | —    | 0000          |

| 6690                        | CNSTATG                         | 15:0      | —     | -     | _     | —     | _     | _     | CN<br>STATG9 | CN<br>STATG8 | CN<br>STATG7 | CN<br>STATG6 | —    |      | CN<br>STATG3       | CN<br>STATG2       | —    | —    | xxxx          |

Legend: x = Unknown value on Reset; - = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

2: This bit is only available on devices without a USB module.

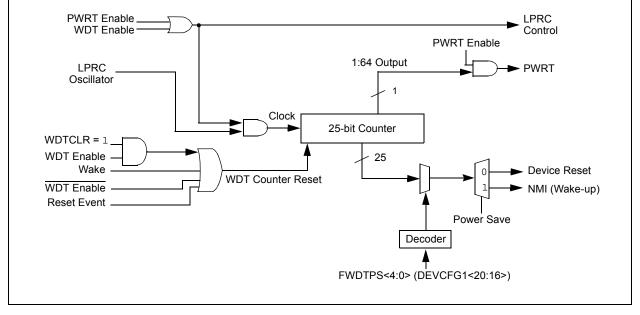

#### 15.0 WATCHDOG TIMER (WDT)

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog, Deadman, and Power-up Timers" (DS60001114), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32). The WDT, when enabled, operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

The following are some of the key features of the WDT module:

- · Configuration or software controlled

- User-configurable time-out period

- Can wake the device from Sleep or Idle

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                   | _                 | _                 | _                 | _                 | _                 | —                | _                |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                   | —                 | _                 | _                 | _                 | —                 | _                | _                |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1,2)</sup> | —                 | _                 | _                 | —                 | _                 | —                | —                |

| 7.0          | U-0                 | R-y               | R-y               | R-y               | R-y               | R-y               | R/W-0            | R/W-0            |

| 7:0          |                     |                   | S                 | WDTPS<4:0         | >                 |                   | WDTWINEN         | WDTCLR           |

#### REGISTER 15-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Legend:           | y = Values set from Configuration bits on POR       |                      |                    |  |  |  |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Watchdog Timer Enable bit<sup>(1,2)</sup>

- 1 = Enables the WDT if it is not enabled by the device configuration

- 0 = Disable the WDT if it was enabled in software

- bit 14-7 Unimplemented: Read as '0'

- bit 6-2 **SWDTPS<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value from Device Configuration bits On reset, these bits are set to the values of the WDTPS <4:0> of Configuration bits.

- bit 1 WDTWINEN: Watchdog Timer Window Enable bit

- 1 = Enable windowed Watchdog Timer

- 0 = Disable windowed Watchdog Timer

- bit 0 WDTCLR: Watchdog Timer Reset bit

- 1 = Writing a '1' will clear the WDT

- 0 = Software cannot force this bit to a '0'

- **Note 1:** A read of this bit results in a '1' if the Watchdog Timer is enabled by the device configuration or software.

- 2: When using the 1:1 PBCLK divisor, the user software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

## PIC32MX330/350/370/430/450/470

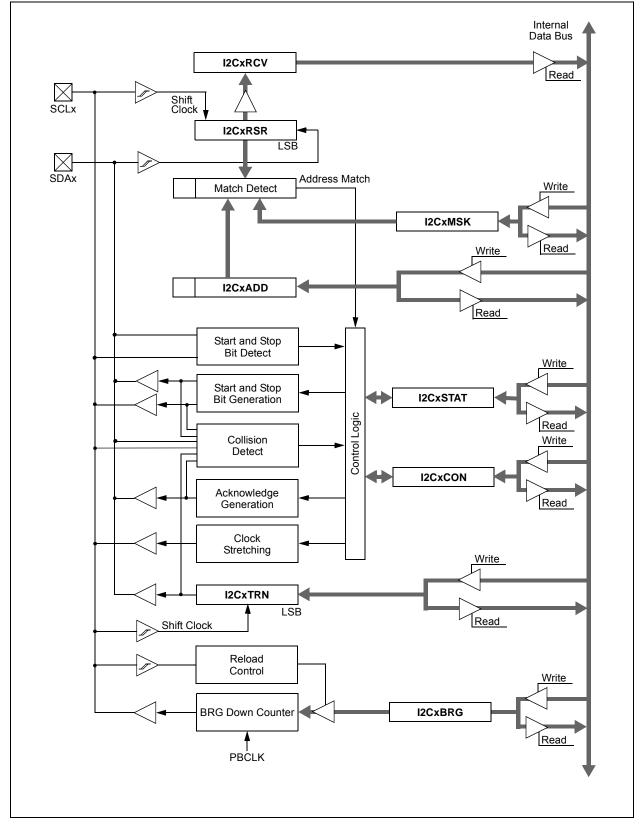

#### FIGURE 19-1: I<sup>2</sup>C BLOCK DIAGRAM

#### 22.1 Control Registers

#### TABLE 22-1: RTCC REGISTER MAP

| ess                         |                                 | 0         |        |       |         |          |       |              |                   |      | Bits         |          |       |      |              |         |         |       | 8         |

|-----------------------------|---------------------------------|-----------|--------|-------|---------|----------|-------|--------------|-------------------|------|--------------|----------|-------|------|--------------|---------|---------|-------|-----------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15  | 30/14 | 29/13   | 28/12    | 27/11 | 26/10        | 25/9              | 24/8 | 23/7         | 22/6     | 21/5  | 20/4 | 19/3         | 18/2    | 17/1    | 16/0  | All Reset |

| 0200                        | RTCCON                          | 31:16     | _      | _     | _       | -        | _     | — — CAL<9:0> |                   |      |              |          |       |      |              | 0000    |         |       |           |

| 0200                        | RICCON                          | 15:0      | ON     | _     | SIDL    | —        | _     | -            |                   | _    | RTSECSEL     | RTCCLKON | _     | _    | RTCWREN      | RTCSYNC | HALFSEC | RTCOE | 0000      |

| 0210                        | RTCALRM                         | 31:16     | —      | _     | _       | —        | _     | -            |                   | _    | —            | _        | _     | _    | —            | _       | —       | —     | 0000      |

| 0210                        | RICALNI                         | 15:0      | ALRMEN | CHIME | PIV     | ALRMSYNC |       | AMASI        | <b>&lt;</b> <3:0> |      |              |          |       | ARP1 | [<7:0>       |         |         |       | 0000      |

| 0220                        | RTCTIME                         | 31:16     |        | HR10  | 0<3:0>  |          |       | HR01         | <3:0>             |      |              | MIN10<   | 3:0>  |      |              | MIN01   | <3:0>   |       | xxxx      |

| 0220                        |                                 | 15:0      |        | SEC1  | 0<3:0>  |          |       | SEC07        | 1<3:0>            |      | —            | _        | _     | _    | _            | —       | —       | —     | xx00      |

| 0230                        | RTCDATE                         | 31:16     |        | YEAR  | 10<3:0> |          |       | YEAR0        | 1<3:0>            |      | MONTH10<3:0> |          |       |      | MONTH01<3:0> |         |         |       | xxxx      |

| 0230                        | RIODAIL                         | 15:0      |        | DAY1  | 0<3:0>  |          |       | DAY01        | 1<3:0>            |      | —            | _        | _     | _    |              | WDAY0   | 1<3:0>  |       | xx00      |

| 0240                        | ALRMTIME                        | 31:16     |        | HR10  | 0<3:0>  |          |       | HR01         | <3:0>             |      |              | MIN10<   | 3:0>  |      |              | MIN01   | <3:0>   |       | xxxx      |

| 0240                        |                                 | 15:0      |        | SEC1  | 0<3:0>  |          |       | SEC07        | 1<3:0>            |      | —            | _        | _     | _    | _            | —       | —       | —     | xx00      |

| 0250                        | ALRMDATE                        | 31:16     | _      | _     | _       | _        | —     | —            | —                 | _    |              | MONTH10  | <3:0> |      |              | MONTH   | 01<3:0> |       | 00xx      |

| 0200                        |                                 | 15:0      |        | DAY1  | 0<3:0>  |          |       | DAY01        | 1<3:0>            |      | —            | _        | _     | _    |              | WDAY0   | 1<3:0>  |       | xx0x      |

PIC32MX330/350/370/430/450/470

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|------------------|------------------|

| 04.04        | r-0               | r-1               | r-1               | R/P               | r-1               | r-1                   | r-1              | R/P              |

| 31:24        | _                 | —                 | —                 | CP                | —                 | —                     | —                | BWP              |

| 00.40        | r-1               | r-1               | r-1               | r-1               | R/P               | R/P                   | R/P              | R/P              |

| 23:16        | —                 | —                 | —                 | —                 |                   | PWP                   | <7:4>            |                  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | r-1               | r-1                   | r-1              | r-1              |

| 15:8         |                   | PWP<              | <3:0>             |                   | —                 | —                     | _                | —                |

| 7.0          | r-1               | r-1               | r-1               | R/P               | R/P               | R/P                   | R/P              | R/P              |

| 7:0          |                   | _                 | —                 | ICESE             | L<1:0>            | JTAGEN <sup>(1)</sup> | DEBU             | G<1:0>           |

#### REGISTER 28-1: DEVCFG0: DEVICE CONFIGURATION WORD 0

| Legend:           | r = Reserved bit | r = Reserved bit P = Programmable bit |                    |  |  |  |  |

|-------------------|------------------|---------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented b                   | it, read as '0'    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                  | x = Bit is unknown |  |  |  |  |

bit 31 **Reserved:** Write '0'

bit 30-29 Reserved: Write '1'

bit 28 **CP:** Code-Protect bit

Prevents boot and program Flash memory from being read or modified by an external programming device.

1 = Protection is disabled

0 = Protection is enabled

#### bit 27-25 Reserved: Write '1'

bit 24 BWP: Boot Flash Write-Protect bit

Prevents boot Flash memory from being modified during code execution.

1 = Boot Flash is writable

0 = Boot Flash is not writable

bit 23-20 Reserved: Write '1'

bit 19-12 **PWP<7:0>:** Program Flash Write-Protect bits

Prevents selected program Flash memory pages from being modified during code execution. The PWP bits represent the one's compliment of the number of write protected program Flash memory pages.

| 11111111 = Disabled    |

|------------------------|

| 11111110 = 0xBD00_0FFF |

| 11111101 = 0xBD00_1FFF |

| 11111100 = 0xBD00_2FFF |

| 11111011 = 0xBD00_3FFF |

| 11111010 = 0xBD00_4FFF |

| 11111001 = 0xBD00_5FFF |

| 11111000 = 0xBD00_6FFF |

| 11110111 = 0xBD00_7FFF |

| 11110110 = 0xBD00 8FFF |

| 11110101 = 0xBD00_9FFF |

| 11110100 = 0xBD00_AFFF |

| 11110011 = 0xBD00 BFFF |

| 11110010 = 0xBD00 CFFF |

| 11110001 = 0xBD00 DFFF |

| 11110000 = 0xBD00 EFFF |

| 11101111 = 0xBD00 FFFF |

| . –                    |

|                        |

|                        |

| 01111111 = 0xBD07 FFFF |

| _                      |

|                        |

Note 1: This bit sets the value for the JTAGEN bit in the CFGCON register.

#### 30.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 30.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 30.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

#### 30.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

#### 30.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

### 31.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MX330/350/370/430/450/470 electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC32MX330/350/370/430/450/470 devices are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions, above the parameters indicated in the operation listings of this specification, is not implied.

#### **Absolute Maximum Ratings**

#### (See Note 1)

| Ambient temperature under bias                                                  | 40°C to +105°C           |

|---------------------------------------------------------------------------------|--------------------------|

| Storage temperature                                                             |                          |

| Voltage on VDD with respect to Vss                                              |                          |

| Voltage on any pin that is not 5V tolerant, with respect to Vss (Note 3)        | 0.3V to (VDD + 0.3V)     |

| Voltage on any 5V tolerant pin with respect to Vss when VDD $\ge 2.3V$ (Note 3) | 0.3V to +6.0V            |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 2.3V (Note 3)     | 0.3V to +3.6V            |

| Voltage on D+ or D- pin with respect to VUSB3V3                                 | 0.3V to (VUSB3V3 + 0.3V) |

| Voltage on VBUS with respect to VSS                                             | 0.3V to +5.5V            |

| Maximum current out of Vss pin(s)                                               | 200 mA                   |

| Maximum current into VDD pin(s) (Note 2)                                        | 200 mA                   |

| Maximum output current sourced/sunk by any 4x I/O pin                           | 15 mA                    |

| Maximum output current sourced/sunk by any 8x I/O pin                           | 25 mA                    |

| Maximum current sunk by all ports                                               | 150 mA                   |

| Maximum current sourced by all ports (Note 2)                                   | 150 mA                   |

**Note 1:** Stresses above those listed under "**Absolute Maximum Ratings**" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 31-2).

- 3: See the "Device Pin Tables" section for the 5V tolerant pins.

#### TABLE 31-15: COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

| DC CHARACTERISTICS |         |                                                              | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercial} \\ & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |                    |       |                                                                  |  |

|--------------------|---------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------|-------|------------------------------------------------------------------|--|

| Param.<br>No.      | Symbol  | Characteristics                                              | Min.                                                                                                                                                                                                                                                                                                                                                   | Тур. | Max.               | Units | Comments                                                         |  |

| D312               | TSET    | Internal 4-bit DAC<br>Comparator Reference<br>Settling time. | _                                                                                                                                                                                                                                                                                                                                                      |      | 10                 | μs    | See Note 1                                                       |  |

| D313               | DACREFH | CVREF Input Voltage                                          | AVss                                                                                                                                                                                                                                                                                                                                                   |      | AVDD               | V     | CVRSRC with CVRSS = 0                                            |  |

|                    |         | Reference Range                                              | VREF-                                                                                                                                                                                                                                                                                                                                                  |      | VREF+              | V     | CVRSRC with CVRSS = 1                                            |  |

| D314               | DVREF   | CVREF Programmable<br>Output Range                           | 0                                                                                                                                                                                                                                                                                                                                                      | _    | 0.625 x<br>DACREFH | V     | 0 to 0.625 DACREFH with<br>DACREFH/24 step size                  |  |

|                    |         |                                                              | 0.25 x<br>DACREFH                                                                                                                                                                                                                                                                                                                                      | —    | 0.719 x<br>DACREFH | V     | 0.25 x DACREFH to 0.719<br>DACREFH with DACREFH/<br>32 step size |  |

| D315               | DACRES  | Resolution                                                   | _                                                                                                                                                                                                                                                                                                                                                      | _    | DACREFH/24         |       | CVRCON <cvrr> = 1</cvrr>                                         |  |

|                    |         |                                                              | —                                                                                                                                                                                                                                                                                                                                                      |      | DACREFH/32         |       | CVRCON <cvrr> = 0</cvrr>                                         |  |

| D316               | DACACC  | Absolute Accuracy <sup>(2)</sup>                             | —                                                                                                                                                                                                                                                                                                                                                      | _    | 1/4                | LSB   | DACREFH/24,<br>CVRCON <cvrr> = 1</cvrr>                          |  |

|                    |         |                                                              | _                                                                                                                                                                                                                                                                                                                                                      |      | 1/2                | LSB   | DACREFH/32,<br>CVRCON <cvrr> = 0</cvrr>                          |  |

**Note 1:** Settling time was measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but is not tested in manufacturing.

2: These parameters are characterized but not tested.

#### TABLE 31-16: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| DC CHARACTERISTICS |        |                                 | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |         |      |       |                                                                                                    |  |

|--------------------|--------|---------------------------------|------------------------------------------------------|---------|------|-------|----------------------------------------------------------------------------------------------------|--|

| Param.<br>No.      | Symbol | Characteristics                 | Min.                                                 | Typical | Max. | Units | Comments                                                                                           |  |

| D321               | Cefc   | External Filter Capacitor Value | 8                                                    | 10      |      | μF    | Capacitor must be low series<br>resistance (3 ohm). Typical<br>voltage on the VCAP pin is<br>1.8V. |  |

#### TABLE 31-35: ADC MODULE SPECIFICATIONS

| AC CHARACTERISTICS <sup>(5)</sup> |            |                                                      | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |              |                                  |          |                                                                                        |  |  |

|-----------------------------------|------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|----------------------------------|----------|----------------------------------------------------------------------------------------|--|--|

| Param.<br>No.                     | Symbol     | Characteristics                                      | Min.                                                                                                                                                                                                                                                                                                                                               | Typical      | Max.                             | Units    | Conditions                                                                             |  |  |

| Device \$                         | Supply     |                                                      |                                                                                                                                                                                                                                                                                                                                                    |              |                                  |          |                                                                                        |  |  |

| AD01                              | AVdd       | Module VDD Supply                                    | Greater of<br>VDD – 0.3<br>or 2.5                                                                                                                                                                                                                                                                                                                  | _            | Lesser of<br>VDD + 0.3<br>or 3.6 | V        | _                                                                                      |  |  |

| AD02                              | AVss       | Module Vss Supply                                    | Vss                                                                                                                                                                                                                                                                                                                                                | —            | Vss + 0.3                        | V        | _                                                                                      |  |  |

| Referen                           | ce Inputs  |                                                      |                                                                                                                                                                                                                                                                                                                                                    |              |                                  |          |                                                                                        |  |  |

| AD05                              | Vrefh      | Reference Voltage High                               | AVss + 2.0                                                                                                                                                                                                                                                                                                                                         | —            | AVdd                             | V        | (Note 1)                                                                               |  |  |

| AD05a                             |            |                                                      | 2.5                                                                                                                                                                                                                                                                                                                                                | —            | 3.6                              | V        | VREFH = AVDD (Note 3)                                                                  |  |  |

| AD06                              | Vrefl      | Reference Voltage Low                                | AVss                                                                                                                                                                                                                                                                                                                                               | —            | VREFH – 2.0                      | V        | (Note 1)                                                                               |  |  |

| AD07                              | Vref       | Absolute Reference<br>Voltage (VREFH – VREFL)        | 2.0                                                                                                                                                                                                                                                                                                                                                | -            | AVDD                             | V        | (Note 3)                                                                               |  |  |

| AD08                              | IREF       | Current Drain                                        | _                                                                                                                                                                                                                                                                                                                                                  | 250<br>—     | 400<br>3                         | μΑ<br>μΑ | ADC operating<br>ADC off                                                               |  |  |