Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                       |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 64K x 8                                                                        |

| /oltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 124-VFTLA Dual Rows, Exposed Pad                                               |

| Supplier Device Package    | 124-VTLA (9x9)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx350f256l-i-tl |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

TABLE 1-1: PINOUT I/O DESCRIPTIONS

| IABLE 1- |                        | Pin Numb        | er              |             |                |                                                                                                                                                                                        |

|----------|------------------------|-----------------|-----------------|-------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                            |

| AN0      | 16                     | 25              | B14             | ı           | Analog         |                                                                                                                                                                                        |

| AN1      | 15                     | 24              | A15             | I           | Analog         |                                                                                                                                                                                        |

| AN2      | 14                     | 23              | B13             | I           | Analog         |                                                                                                                                                                                        |

| AN3      | 13                     | 22              | A13             | I           | Analog         |                                                                                                                                                                                        |

| AN4      | 12                     | 21              | B11             | I           | Analog         |                                                                                                                                                                                        |

| AN5      | 11                     | 20              | A12             | I           | Analog         |                                                                                                                                                                                        |

| AN6      | 17                     | 26              | A20             | I           | Analog         |                                                                                                                                                                                        |

| AN7      | 18                     | 27              | B16             | I           | Analog         |                                                                                                                                                                                        |

| AN8      | 21                     | 32              | A23             | I           | Analog         |                                                                                                                                                                                        |

| AN9      | 22                     | 33              | B19             | I           | Analog         |                                                                                                                                                                                        |

| AN10     | 23                     | 34              | A24             | I           | Analog         |                                                                                                                                                                                        |

| AN11     | 24                     | 35              | B20             | I           | Analog         |                                                                                                                                                                                        |

| AN12     | 27                     | 41              | B23             | I           | Analog         |                                                                                                                                                                                        |

| AN13     | 28                     | 42              | A28             | I           | Analog         | Analog input shappala                                                                                                                                                                  |

| AN14     | 29                     | 43              | B24             | I           | Analog         | Analog input channels.                                                                                                                                                                 |

| AN15     | 30                     | 44              | A29             | I           | Analog         |                                                                                                                                                                                        |

| AN16     | 4                      | 10              | A7              | I           | Analog         |                                                                                                                                                                                        |

| AN17     | 5                      | 11              | B6              | I           | Analog         |                                                                                                                                                                                        |

| AN18     | 6                      | 12              | A8              | I           | Analog         |                                                                                                                                                                                        |

| AN19     | 8                      | 14              | A9              | I           | Analog         |                                                                                                                                                                                        |

| AN20     | 62                     | 98              | A66             | I           | Analog         |                                                                                                                                                                                        |

| AN21     | 64                     | 100             | A67             | I           | Analog         |                                                                                                                                                                                        |

| AN22     | 1                      | 3               | B2              | I           | Analog         |                                                                                                                                                                                        |

| AN23     | 2                      | 4               | A4              | I           | Analog         |                                                                                                                                                                                        |

| AN24     | 49                     | 76              | A52             | I           | Analog         |                                                                                                                                                                                        |

| AN25     | 50                     | 77              | B42             | I           | Analog         |                                                                                                                                                                                        |

| AN26     | 51                     | 78              | A53             | I           | Analog         |                                                                                                                                                                                        |

| AN27     | 3                      | 5               | B3              | I           | Analog         |                                                                                                                                                                                        |

| CLKI     | 39                     | 63              | B34             | I           | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.                                                                                                                 |

| CLKO     | 40                     | 64              | A42             | 0           | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes. Always associated with the OSC2 pin function. |

| OSC1     | 39                     | 63              | B34             | I           | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                        |

| OSC2     | 40                     | 64              | A42             | 0           | _              | Oscillator crystal output. Connects to crystal or resonator in Crystal Oscillator mode. Optionally functions as CLKO in RC and EC modes.                                               |

| SOSCI    | 47                     | 73              | A47             | I           | ST/CMOS        | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                         |

| SOSCO    | 48                     | 74              | B40             | 0           | _              | 32.768 kHz low-power oscillator crystal output.                                                                                                                                        |

|          |                        |                 |                 |             |                |                                                                                                                                                                                        |

Legend: CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

TTL = TTL input buffer

Analog = Analog input O = Output P = Power I = Input

Note 1: This pin is only available on devices without a USB module.

- 2: This pin is only available on devices with a USB module.

- 3: This pin is not available on 64-pin devices.

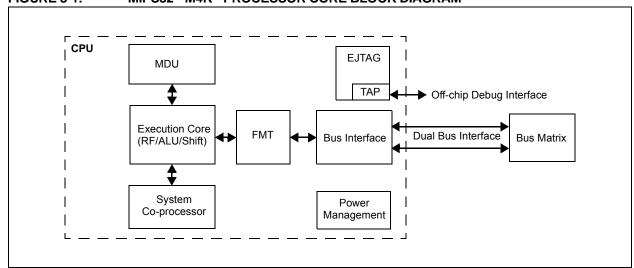

#### 3.0 CPU

Note:

This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 2.** "CPU" (DS60001113), which is available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). Resources for the MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core are available at http://www.imgtec.com.

The the MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core is the heart of the PIC32MX330/350/370/430/450/470 device processor. The CPU fetches instructions, decodes each instruction, fetches source operands, executes each instruction and writes the results of instruction execution to the proper destinations.

#### 3.1 Features

- · 5-stage pipeline

- · 32-bit address and data paths

- MIPS32® Enhanced Architecture (Release 2):

- Multiply-accumulate and multiply-subtract instructions

- Targeted multiply instruction

- Zero/One detect instructions

- WAIT instruction

- Conditional move instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- GPR shadow registers to minimize latency for interrupt handlers

- Bit field manipulation instructions

- MIPS16e<sup>®</sup> Code Compression:

- 16-bit encoding of 32-bit instructions to improve code density

- Special PC-relative instructions for efficient loading of addresses and constants

- SAVE and RESTORE macro instructions for setting up and tearing down stack frames within subroutines

- Improved support for handling 8 and 16-bit data types

- Simple Fixed Mapping Translation (FMT) Mechanism:

- · Simple Dual Bus Interface:

- Independent 32-bit address and data buses

- Transactions can be aborted to improve interrupt latency

- Autonomous Multiply/Divide Unit (MDU):

- Maximum issue rate of one 32x16 multiply per clock

- Maximum issue rate of one 32x32 multiply every other clock

- Early-in iterative divide. Minimum 11 and maximum 33 clock latency (dividend (rs) sign extension-dependent)

- · Power Control:

- Minimum frequency: 0 MHz

- Low-Power mode (triggered by WAIT instruction)

- Extensive use of local gated clocks

- · EJTAG Debug and Instruction Trace:

- Support for single stepping

- Virtual instruction and data address/value

- Breakpoints

FIGURE 3-1: MIPS32® M4K® PROCESSOR CORE BLOCK DIAGRAM

#### REGISTER 10-12: DCHxSSIZ: DMA CHANNEL 'x' SOURCE SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | CHSSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHSSIZ            | <7:0>             |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSSIZ<15:0>: Channel Source Size bits

1111111111111111 = 65,535 byte source size

•

:

00000000000000001 = 1 byte source size

0000000000000000 = 65,536 byte source size

#### REGISTER 10-13: DCHxDSIZ: DMA CHANNEL 'x' DESTINATION SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | CHDSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHDSIZ            | <7:0>             |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHDSIZ<15:0>: Channel Destination Size bits

111111111111111 = 65,535 byte destination size

•

00000000000000010 = 2 byte destination size

0000000000000001 = 1 byte destination size

0000000000000000 = 65,536 byte destination size

#### REGISTER 11-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER (CONTINUED)

bit 1 CRC5EF: CRC5 Host Error Flag bit<sup>(4)</sup>

1 = Token packet is rejected due to CRC5 error

0 = Token packet is accepted

EOFEF: EOF Error Flag bit<sup>(3,5)</sup>

1 = EOF error condition is detected

0 = No EOF error condition

bit 0 PIDEF: PID Check Failure Flag bit

1 = PID check is failed0 = PID check is passed

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- 2: This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

TABLE 12-2: OUTPUT PIN SELECTION (CONTINUED)

| RPn Port Pin         | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection        |

|----------------------|----------|-------------|----------------------------------------------|

| RPD9                 | RPD9R    | RPD9R<3:0>  | 0000 = No Connect                            |

| RPG6                 | RPG6R    | RPG6R<3:0>  | 0001 = U3RTS                                 |

| RPB8                 | RPB8R    | RPB8R<3:0>  | 0010 = U4TX                                  |

| RPB15                | RPB15R   | RPB15R<3:0> | 0011 = REFCLKO<br>0100 = U5TX <sup>(4)</sup> |

| RPD4                 | RPD4R    | RPD4R<3:0>  | 0100 = <b>GSTX</b> 9                         |

| RPB0                 | RPB0R    | RPB0R<3:0>  | 0110 = Reserved                              |

| RPE3                 | RPE3R    | RPE3R<3:0>  | 0111 = SS1                                   |

| RPB7                 | RPB7R    | RPB7R<3:0>  | 1000 = SDO1                                  |

| RPB2                 | RPB2R    | RPB2R<3:0>  | 1001 = Reserved                              |

| RPF12 <sup>(4)</sup> | RPF12R   | RPF12R<3:0> | 1010 = Reserved                              |

| RPD12 <sup>(4)</sup> | RPD12R   | RPD12R<3:0> | 1011 = OC5<br>1100 = Reserved                |

| RPF8 <sup>(4)</sup>  | RPF8R    | RPF8R<3:0>  | 1101 = C1OUT                                 |

| RPC3 <sup>(4)</sup>  | RPC3R    | RPC3R<3:0>  | 1110 = Reserved                              |

| RPE9 <sup>(4)</sup>  | RPE9R    | RPE9R<3:0>  | 1111 = Reserved                              |

| RPD1                 | RPD1R    | RPD1R<3:0>  | 0000 = No Connect                            |

| RPG9                 | RPG9R    | RPG9R<3:0>  | 0001 = U2RTS                                 |

| RPB14                | RPB14R   | RPB14R<3:0> | 0010 = Reserved<br>0011 = U1RTS              |

| RPD0                 | RPD0R    | RPD0R<3:0>  | 0100 = U5TX <sup>(4)</sup>                   |

| RPD8                 | RPD8R    | RPD8R<3:0>  | 0101 = Reserved                              |

| RPB6                 | RPB6R    | RPB6R<3:0>  | 0110 = <del>SS</del> 2                       |

| RPD5                 | RPD5R    | RPD5R<3:0>  | 0111 = Reserved<br>1000 = SDO1               |

| RPF3 <sup>(3)</sup>  | RPF3R    | RPF3R<3:0>  | 1000 = SBC1<br>1001 = Reserved               |

| RPF6 <sup>(1)</sup>  | RPF6R    | RPF6R<3:0>  | 1010 = Reserved                              |

| RPF13 <sup>(4)</sup> | RPF13R   | RPF13R<3:0> | 1011 = OC2                                   |

| RPC2 <sup>(4)</sup>  | RPC2R    | RPC2R<3:0>  | 1100 = OC1<br>1101 = Reserved                |

| RPE8 <sup>(4)</sup>  | RPE8R    | RPE8R<3:0>  | 1110 = Reserved                              |

| RPF2 <sup>(5)</sup>  | RPF2R    | RPF2R<3:0>  | 1111 = Reserved                              |

Note 1: This selection is only available on General Purpose devices.

- 2: This selection is only available on 64-pin General Purpose devices.

- **3:** This selection is only available on 100-pin General Purpose devices.

- 4: This selection is only available on 100-pin USB and General Purpose devices.

- 5: This selection is not available on 64-pin USB devices.

| PIC32M2 | PIC32MX330/350/370/430/450/470 |  |  |  |  |  |  |  |  |  |

|---------|--------------------------------|--|--|--|--|--|--|--|--|--|

| NOTES:  |                                |  |  |  |  |  |  |  |  |  |

|         |                                |  |  |  |  |  |  |  |  |  |

|         |                                |  |  |  |  |  |  |  |  |  |

|         |                                |  |  |  |  |  |  |  |  |  |

|         |                                |  |  |  |  |  |  |  |  |  |

|         |                                |  |  |  |  |  |  |  |  |  |

|         |                                |  |  |  |  |  |  |  |  |  |

|         |                                |  |  |  |  |  |  |  |  |  |

|         |                                |  |  |  |  |  |  |  |  |  |

|         |                                |  |  |  |  |  |  |  |  |  |

|         |                                |  |  |  |  |  |  |  |  |  |

|         |                                |  |  |  |  |  |  |  |  |  |

|         |                                |  |  |  |  |  |  |  |  |  |

|         |                                |  |  |  |  |  |  |  |  |  |

|         |                                |  |  |  |  |  |  |  |  |  |

|         |                                |  |  |  |  |  |  |  |  |  |

|         |                                |  |  |  |  |  |  |  |  |  |

|         |                                |  |  |  |  |  |  |  |  |  |

|         |                                |  |  |  |  |  |  |  |  |  |

#### REGISTER 16-1: ICXCON: INPUT CAPTURE 'x' CONTROL REGISTER (CONTINUED)

bit 2-0 ICM<2:0>: Input Capture Mode Select bits

111 = Interrupt-Only mode (only supported while in Sleep mode or Idle mode)

110 = Simple Capture Event mode – every edge, specified edge first and every edge thereafter

101 = Prescaled Capture Event mode – every sixteenth rising edge

100 = Prescaled Capture Event mode – every fourth rising edge

011 = Simple Capture Event mode – every rising edge

010 = Simple Capture Event mode – every falling edge

001 = Edge Detect mode – every edge (rising and falling)000 = Input Capture module is disabled

**Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### **Control Registers** 17.1

### TABLE 17-1: OUTPUT COMPARE 1 THROUGH OUTPUT COMPARE 5 REGISTER MAP

| ess                         |                                 |               |                   |             |           |       |       |        |      | Bi    | ts     |        |           |            |        |      |               |      | ,,         |

|-----------------------------|---------------------------------|---------------|-------------------|-------------|-----------|-------|-------|--------|------|-------|--------|--------|-----------|------------|--------|------|---------------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15             | 30/14       | 29/13     | 28/12 | 27/11 | 26/10  | 25/9 | 24/8  | 23/7   | 22/6   | 21/5      | 20/4       | 19/3   | 18/2 | 17/1          | 16/0 | All Resets |

|                             | OC1CON                          | 31:16<br>15:0 | —<br>ON           | _           | —<br>SIDL | _     | _     | _<br>_ |      | _     | _      | _<br>_ | —<br>OC32 | —<br>OCFLT | OCTSEL | _    | —<br>OCM<2:0> | _    | 0000       |

| 3010                        | OC1R                            | 31:16<br>15:0 |                   |             | •         |       |       |        |      | OC1R  | <31:0> |        |           | •          |        |      |               |      | xxxx       |

| 3020                        | OC1RS                           | 31:16<br>15:0 |                   | OC1RS<31:0> |           |       |       |        |      | xxxx  |        |        |           |            |        |      |               |      |            |

| 3200                        | OC2CON                          | 31:16<br>15:0 | —<br>ON           | _           | —<br>SIDL | _     | _     |        | _    | _     | _      | _      | —<br>OC32 | OCFLT      | OCTSEL | _    | OCM<2:0>      | _    | 0000       |

| 3210                        | OC2R                            | 31:16<br>15:0 | 011               |             | O.B.L     |       |       |        |      | OC2R  |        |        | 0002      | 00.21      | OOTOLL |      |               |      | xxxx       |

| 3220                        | OC2RS                           | 31:16<br>15:0 |                   |             |           |       |       |        |      | OC2RS | <31:0> |        |           |            |        |      |               |      | xxxx       |

| 3400                        | OC3CON                          | 31:16<br>15:0 | ON                |             | —<br>SIDL |       |       |        |      |       |        |        | —<br>OC32 | OCFLT      | OCTSEL | _    | OCM<2:0>      |      | 0000       |

| 3410                        | OC3R                            | 31:16<br>15:0 |                   |             | •         |       |       |        |      | OC3R  | <31:0> |        |           | •          | 1      |      |               |      | xxxx       |

| 3420                        | OC3RS                           | 31:16<br>15:0 |                   |             |           |       |       |        |      | OC3RS | <31:0> |        |           |            | _      |      |               |      | xxxx       |

| 3600                        | OC4CON                          | 31:16<br>15:0 | ON                | _           | —<br>SIDL | _     |       |        |      | _     |        | _      | —<br>ОС32 | OCFLT      | OCTSEL | _    | OCM<2:0>      | _    | 0000       |

| 3610                        | OC4R                            | 31:16<br>15:0 |                   |             |           |       |       |        |      | OC4R  | <31:0> |        |           |            |        |      |               |      | xxxx       |

| 3620                        | OC4RS                           | 31:16<br>15:0 |                   |             |           |       |       |        |      | OC4RS | <31:0> |        |           |            |        |      |               |      | xxxx       |

| 3800                        | OC5CON                          | 31:16<br>15:0 | ON                |             | —<br>SIDL |       |       |        |      |       |        |        | —<br>OC32 | OCFLT      | OCTSEL | _    | —<br>OCM<2:0> | _    | 0000       |

| 3810                        | OC5R                            | 31:16<br>15:0 | $\neg$ OC5R<31:0> |             |           |       |       |        |      |       | xxxx   |        |           |            |        |      |               |      |            |

| 3820                        | OC5RS                           | 31:16<br>15:0 |                   |             |           |       |       |        |      | OC5RS | <31:0> |        |           |            |        |      |               |      | xxxx       |

PIC32MX330/350/370/430/450/470

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information. Note 1:

REGISTER 17-1: OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | _                    | _                 |                   | _                | _                |

| 22.46        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                    | _                 | -                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | _                 | SIDL              | _                    | _                 | _                 | _                | _                |

| 7:0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | OC32              | OCFLT <sup>(2)</sup> | OCTSEL            |                   | OCM<2:0>         |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Output Compare Peripheral On bit<sup>(1)</sup>

1 = Output Compare peripheral is enabled

0 = Output Compare peripheral is disabled

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Mode bit

1 = Discontinue operation when CPU enters Idle mode

0 = Continue operation in Idle mode

bit 12-6 Unimplemented: Read as '0'

bit 5 OC32: 32-bit Compare Mode bit

1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisions to the 32-bit timer source

0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

bit 4 OCFLT: PWM Fault Condition Status bit<sup>(2)</sup>

1 = PWM Fault condition has occurred (cleared in HW only)

0 = No PWM Fault condition has occurred

bit 3 OCTSEL: Output Compare Timer Select bit

1 = Timer3 is the clock source for this Output Compare module

0 = Timer2 is the clock source for this Output Compare module

bit 2-0 OCM<2:0>: Output Compare Mode Select bits

111 = PWM mode on OCx; Fault pin is enabled

110 = PWM mode on OCx; Fault pin is disabled

101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

100 = Initialize OCx pin low; generate single output pulse on OCx pin

011 = Compare event toggles OCx pin

010 = Initialize OCx pin high; compare event forces OCx pin low

001 = Initialize OCx pin low; compare event forces OCx pin high

000 = Output compare peripheral is disabled but continues to draw current

Note 1: When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

2: This bit is only used when OCM<2:0> = '111'. It is read as '0' in all other modes.

#### **REGISTER 18-1: SPIXCON: SPI CONTROL REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|------------------------|--------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 31:24        | R/W-0                  | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 31.24        | FRMEN                  | FRMSYNC            | FRMPOL            | MSSEN             | FRMSYPW           | F                 | RMCNT<2:0        | <b> &gt;</b>          |

| 22:16        | R/W-0                  | U-0                | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0                 |

| 23:16        | MCLKSEL <sup>(2)</sup> | _                  | _                 | _                 | _                 | _                 | SPIFE            | ENHBUF <sup>(2)</sup> |

| 15.0         | R/W-0                  | U-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 15:8         | ON <sup>(1)</sup>      | _                  | SIDL              | DISSDO            | MODE32            | MODE16            | SMP              | CKE <sup>(3)</sup>    |

| 7:0          | R/W-0                  | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 7:0          | SSEN                   | CKP <sup>(4)</sup> | MSTEN             | DISSDI            | STXISE            | L<1:0>            | SRXIS            | EL<1:0>               |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 FRMEN: Framed SPI Support bit

1 = Framed SPI support is enabled (SSx pin used as FSYNC input/output)

0 = Framed SPI support is disabled

bit 30 FRMSYNC: Frame Sync Pulse Direction Control on SSx pin bit (Framed SPI mode only)

1 = Frame sync pulse input (Slave mode)

0 = Frame sync pulse output (Master mode)

bit 29 **FRMPOL:** Frame Sync Polarity bit (Framed SPI mode only)

1 = Frame pulse is active-high

0 = Frame pulse is active-low

bit 28 MSSEN: Master Mode Slave Select Enable bit

1 = Slave select SPI support enabled. The SS pin is automatically driven during transmission in Master mode. Polarity is determined by the FRMPOL bit.

0 = Slave select SPI support is disabled.

bit 27 FRMSYPW: Frame Sync Pulse Width bit

1 = Frame sync pulse is one character wide

0 = Frame sync pulse is one clock wide

bit 26-24 **FRMCNT<2:0>:** Frame Sync Pulse Counter bits. Controls the number of data characters transmitted per pulse. This bit is only valid in FRAMED\_SYNC mode.

111 = Reserved; do not use

110 = Reserved; do not use

101 = Generate a frame sync pulse on every 32 data characters

100 = Generate a frame sync pulse on every 16 data characters

011 = Generate a frame sync pulse on every 8 data characters

010 = Generate a frame sync pulse on every 4 data characters

001 = Generate a frame sync pulse on every 2 data characters

000 = Generate a frame sync pulse on every data character

bit 23 MCLKSEL: Master Clock Enable bit<sup>(2)</sup>

1 = REFCLK is used by the Baud Rate Generator

0 = PBCLK is used by the Baud Rate Generator

bit 22-18 Unimplemented: Read as '0'

**Note 1:** When using the 1:1 PBCLK divisor, the user software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

2: This bit can only be written when the ON bit = 0.

3: This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

**4:** When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value of CKP.

#### REGISTER 18-2: SPIxCON2: SPI CONTROL REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0       |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|------------------------|

| 31:24        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                    |

| 31.24        | _                    | _                 | _                 | _                 | _                        | _                 | _                | _                      |

| 23:16        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                    |

| 23.10        | _                    | _                 | _                 | _                 | _                        | _                 | _                | _                      |

| 15:8         | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0                  |

| 15.6         | SPISGNEXT            | _                 | _                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR                 |

| 7:0          | R/W-0                | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0                  |

| 7:0          | AUDEN <sup>(1)</sup> | _                 | _                 | _                 | AUDMONO <sup>(1,2)</sup> |                   | AUDMOD           | <1:0> <sup>(1,2)</sup> |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 SPISGNEXT: Sign Extend Read Data from the RX FIFO bit

1 = Data from RX FIFO is sign extended

0 = Data from RX FIFO is not sign extened

bit 14-13 Unimplemented: Read as '0'

bit 12 **FRMERREN:** Enable Interrupt Events via FRMERR bit

1 = Frame Error overflow generates error events

0 = Frame Error does not generate error events

bit 11 SPIROVEN: Enable Interrupt Events via SPIROV bit

1 = Receive overflow generates error events

0 = Receive overflow does not generate error events

bit 10 **SPITUREN:** Enable Interrupt Events via SPITUR bit

1 = Transmit Underrun Generates Error Events

0 = Transmit Underrun Does Not Generates Error Events

bit 9 IGNROV: Ignore Receive Overflow bit (for Audio Data Transmissions)

1 = A ROV is not a critical error; during ROV data in the fifo is not overwritten by receive data

0 = A ROV is a critical error which stop SPI operation

bit 8 **IGNTUR:** Ignore Transmit Underrun bit (for Audio Data Transmissions)

1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty

0 = A TUR is a critical error which stop SPI operation

bit 7 AUDEN: Enable Audio CODEC Support bit (1)

1 = Audio protocol is enabled

0 = Audio protocol is disabled

bit 6-5 **Unimplemented:** Read as '0'

bit 3 **AUDMONO:** Transmit Audio Data Format bit<sup>(1,2)</sup>

1 = Audio data is mono (Each data word is transmitted on both left and right channels)

0 = Audio data is stereo

bit 2 **Unimplemented:** Read as '0'

bit 1-0 AUDMOD<1:0>: Audio Protocol Mode bit(1,2)

11 = PCM/DSP mode

10 = Right Justified mode

01 = Left Justified mode

$00 = I^2S \text{ mode}$

**Note 1:** This bit can only be written when the ON bit = 0.

2: This bit is only valid for AUDEN = 1.

#### REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

- bit 8 **TRMT:** Transmit Shift Register is Empty bit (read-only)

- 1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed)

- 0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer

- bit 7-6 URXISEL<1:0>: Receive Interrupt Mode Selection bit

- 11 = Reserved; do not use

- 10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full (i.e., has 6 or more data characters)

- 01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full (i.e., has 4 or more data characters)

- 00 = Interrupt flag bit is asserted while receive buffer is not empty (i.e., has at least 1 data character)

- bit 5 **ADDEN:** Address Character Detect bit (bit 8 of received data = 1)

- 1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect

- 0 = Address Detect mode is disabled

- bit 4 RIDLE: Receiver Idle bit (read-only)

- 1 = Receiver is Idle

- 0 = Data is being received

- bit 3 **PERR:** Parity Error Status bit (read-only)

- 1 = Parity error has been detected for the current character

- 0 = Parity error has not been detected

- bit 2 **FERR:** Framing Error Status bit (read-only)

- 1 = Framing error has been detected for the current character

- 0 = Framing error has not been detected

- bit 1 **OERR:** Receive Buffer Overrun Error Status bit.

This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and RSR to empty state.

- 1 = Receive buffer has overflowed

- 0 = Receive buffer has not overflowed

- bit 0 **URXDA:** Receive Buffer Data Available bit (read-only)

- 1 = Receive buffer has data, at least one more character can be read

- 0 = Receive buffer is empty

#### REGISTER 22-6: ALRMDATE: ALARM DATE VALUE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 |                   | -                 | _                 | -                 | _                |                  |

| 22.46        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 23:16        |                   | MONT              | H10<3:0>          |                   |                   | MONTH             | 01<3:0>          |                  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15:8         |                   | DAY′              | 10<1:0>           |                   |                   | DAY01             | I<3:0>           |                  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 7:0          |                   | _                 | _                 |                   |                   | WDAY0             | 1<3:0>           |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-24 Unimplemented: Read as '0'

bit 23-20 MONTH10<3:0>: Binary Coded Decimal value of months bits, 10s place digits; contains a value of 0 or 1

bit 19-16 MONTH01<3:0>: Binary Coded Decimal value of months bits, 1s place digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary Coded Decimal value of days bits, 10s place digits; contains a value from 0 to 3

bit 11-8 DAY01<3:0>: Binary Coded Decimal value of days bits, 1s place digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

bit 3-0 WDAY01<3:0>: Binary Coded Decimal value of weekdays bits, 1s place digit; contains a value from 0 to 6

#### REGISTER 23-1: AD1CON1: ADC CONTROL REGISTER 1

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1    | Bit<br>24/16/8/0    |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------|---------------------|

| 24.24        | U-0                 | U-0                 |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                   | _                   |

| 22:46        | U-0                 | U-0                 |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                   | _                   |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0               | R/W-0               |

| 15:8         | ON <sup>(1)</sup> | _                 | SIDL              | _                 | _                 | F                 | ORM<2:0>            |                     |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0, HSC          | R/C-0, HSC          |

| 7:0          |                   | SSRC<2:0>         |                   | CLRASAM           | _                 | ASAM              | SAMP <sup>(2)</sup> | DONE <sup>(3)</sup> |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** ADC Operating Mode bit<sup>(1)</sup>

1 = ADC module is operating

0 = ADC module is not operating

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Mode bit

1 = Discontinue module operation when device enters Idle mode

0 = Continue module operation in Idle mode

bit 12-11 Unimplemented: Read as '0'

bit 10-8 FORM<2:0>: Data Output Format bits

011 = Signed Fractional 16-bit (DOUT = 0000 0000 0000 0000 sddd dddd dd00 0000)

010 = Fractional 16-bit (DOUT = 0000 0000 0000 0000 dddd dddd dd00 0000)

000 = Integer 16-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

111 = Signed Fractional 32-bit (DOUT = sddd dddd dd00 0000 0000 0000 0000)

101 = Signed Integer 32-bit (DOUT = ssss ssss ssss ssss ssss sssd dddd dddd)

100 = Integer 32-bit (DOUT = 0000 0000 0000 0000 0000 00dd dddd dddd)

bit 7-5 SSRC<2:0>: Conversion Trigger Source Select bits

111 = Internal counter ends sampling and starts conversion (auto convert)

110 = Reserved

101 = Reserved

100 = Reserved

011 = CTMU ends sampling and starts conversion

010 = Timer 3 period match ends sampling and starts conversion

001 = Active transition on INTO pin ends sampling and starts conversion

000 = Clearing SAMP bit ends sampling and starts conversion

- Note 1: When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: If ASAM = 0, software can write a '1' to start sampling. This bit is automatically set by hardware if ASAM = 1. If SSRC = 0, software can write a '0' to end sampling and start conversion. If SSRC ≠ 0, this bit is automatically cleared by hardware to end sampling and start conversion.

- 3: This bit is automatically set by hardware when ADC is complete. Software can write a '0' to clear this bit (a write of '1' is not allowed). Clearing this bit does not affect any operation already in progress. This bit is automatically cleared by hardware at the start of a new conversion.

TABLE 31-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

| DC CHARACTERISTICS |        |                                                                  | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |         |       |       |            |  |

|--------------------|--------|------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|-------|------------|--|

| Param.<br>No.      | Symbol | Characteristics                                                  | Min.                                                                                                                                                                                                                                                     | Typical | Max.  | Units | Conditions |  |

| Operating Voltage  |        |                                                                  |                                                                                                                                                                                                                                                          |         |       |       |            |  |

| DC10               | VDD    | Supply Voltage                                                   | 2.3                                                                                                                                                                                                                                                      | _       | 3.6   | V     | _          |  |

| DC12               | VDR    | RAM Data Retention Voltage (Note 1)                              | 1.75                                                                                                                                                                                                                                                     | _       | _     | V     | _          |  |

| DC16               | VPOR   | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal | 1.75                                                                                                                                                                                                                                                     | _       | 2.1   | V     | _          |  |

| DC17               | SVDD   | VDD Rise Rate<br>to Ensure Internal<br>Power-on Reset Signal     | 0.00005                                                                                                                                                                                                                                                  | _       | 0.115 | V/µs  | _          |  |

$\textbf{Note 1:} \quad \text{This is the limit to which $V$DD can be lowered without losing RAM data}.$

TABLE 31-12: DC CHARACTERISTICS: PROGRAM MEMORY<sup>(3)</sup>

| DC CHARACTERISTICS |        |                                       | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                        |      |       |                                               |  |

|--------------------|--------|---------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|-----------------------------------------------|--|

| Param.<br>No.      | Symbol | Characteristics                       | Min.                                                                                                                                                                                                                                                     | Typical <sup>(1)</sup> | Max. | Units | Conditions                                    |  |

| D130               | ЕР     | Cell Endurance                        | 20,000                                                                                                                                                                                                                                                   | _                      |      | E/W   | _                                             |  |

| D131               | VPR    | VDD for Read                          | 2.3                                                                                                                                                                                                                                                      | _                      | 3.6  | V     | _                                             |  |

| D132               | VPEW   | VDD for Erase or Write                | 2.3                                                                                                                                                                                                                                                      | _                      | 3.6  | V     | _                                             |  |

| D134               | TRETD  | Characteristic Retention              | 20                                                                                                                                                                                                                                                       | _                      | _    | Year  | Provided no other specifications are violated |  |

| D135               | IDDP   | Supply Current during<br>Programming  | _                                                                                                                                                                                                                                                        | 10                     | _    | mA    | _                                             |  |

| D138               | Tww    | Word Write Cycle Time(4)              | 44                                                                                                                                                                                                                                                       | _                      | 59   | μs    | _                                             |  |

| D136               | Trw    | Row Write Cycle Time <sup>(2,4)</sup> | 2.8                                                                                                                                                                                                                                                      | 3.3                    | 3.8  | ms    | _                                             |  |

| D137               | TPE    | Page Erase Cycle Time <sup>(4)</sup>  | 22                                                                                                                                                                                                                                                       |                        | 29   | ms    |                                               |  |

| D139               | TCE    | Chip Erase Cycle Time <sup>(4)</sup>  | 86                                                                                                                                                                                                                                                       | _                      | 116  | ms    | _                                             |  |

- **Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

- 2: The minimum SYSCLK for row programming is 8 MHz. Care should be taken to minimize bus activities during row programming, such as suspending any memory-to-memory DMA operations. If heavy bus loads are expected, selecting Bus Matrix Arbitration mode 2 (rotating priority) may be necessary. The default Arbitration mode is mode 1 (CPU has lowest priority).

- **3:** Refer to the "PIC32 Flash Programming Specification" (DS60001145) for operating conditions during programming and erase cycles.

- **4:** This parameter depends on the FRC accuracy (see Table 31-20) and the FRC tuning values (see Register 8-2).

TABLE 31-13: DC CHARACTERISTICS: PROGRAM FLASH MEMORY WAIT STATE

| DC CHARACTERISTICS         | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)  Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |       |                 |  |  |  |

|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------|--|--|--|

|                            | -40°C ≤ TA ≤ +105°C for V-temp                                                                                                                                                                         |       |                 |  |  |  |

| Required Flash Wait States | SYSCLK                                                                                                                                                                                                 | Units | Conditions      |  |  |  |

| 0 Wait State               | 0-40                                                                                                                                                                                                   | MHz   | -40°C to +85°C  |  |  |  |

| o wait state               | 0-30                                                                                                                                                                                                   | MHz   | -40°C to +105°C |  |  |  |

| 1 Wait State               | 41-80                                                                                                                                                                                                  | MHz   | -40°C to +85°C  |  |  |  |

| i wait State               | 31-60                                                                                                                                                                                                  | MHz   | -40°C to +105°C |  |  |  |

| 2 Mait States              | 81-100                                                                                                                                                                                                 | MHz   | -40°C to +85°C  |  |  |  |

| 2 Wait States              | 61-80                                                                                                                                                                                                  | MHz   | -40°C to +105°C |  |  |  |

| 3 Wait States              | 101-120                                                                                                                                                                                                | MHz   | 0°C to +70°C    |  |  |  |

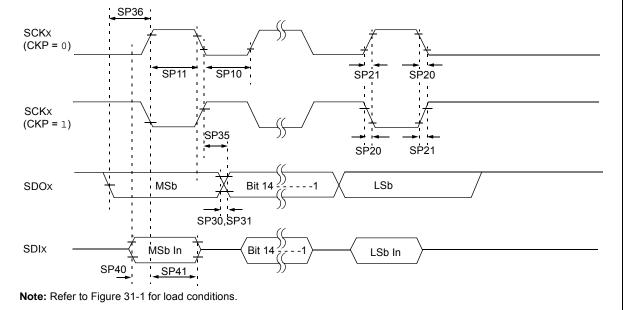

FIGURE 31-11: SPIX MODULE MASTER MODE (CKE = 1) TIMING CHARACTERISTICS

SP36

TABLE 31-30: SPIx MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                           | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)  Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                     |      |       |                    |

|--------------------|-----------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------|

| Param.<br>No.      | Symbol                | Characteristics <sup>(1)</sup>            | Min.                                                                                                                                                                                                                                                      | Typ. <sup>(2)</sup> | Max. | Units | Conditions         |

| SP10               | TscL                  | SCKx Output Low Time (Note 3)             | Tsck/2                                                                                                                                                                                                                                                    | _                   | _    | ns    | _                  |

| SP11               | TscH                  | SCKx Output High Time (Note 3)            | Tsck/2                                                                                                                                                                                                                                                    | _                   | _    | ns    | _                  |

| SP20               | TscF                  | SCKx Output Fall Time (Note 4)            | _                                                                                                                                                                                                                                                         | _                   |      | ns    | See parameter DO32 |

| SP21               | TscR                  | SCKx Output Rise Time (Note 4)            | _                                                                                                                                                                                                                                                         | _                   | _    | ns    | See parameter DO32 |

| SP30               | TDOF                  | SDOx Data Output Fall Time (Note 4)       | _                                                                                                                                                                                                                                                         | _                   | _    | ns    | See parameter DO32 |

| SP31               | TDOR                  | SDOx Data Output Rise Time (Note 4)       | _                                                                                                                                                                                                                                                         | _                   | _    | ns    | See parameter DO31 |

| SP35               | TscH2DoV,             | SDOx Data Output Valid after              | _                                                                                                                                                                                                                                                         | _                   | 15   | ns    | VDD > 2.7V         |

|                    | TscL2doV              | SCKx Edge                                 | _                                                                                                                                                                                                                                                         | _                   | 20   | ns    | VDD < 2.7V         |

| SP36               | TDOV2SC,<br>TDOV2SCL  | SDOx Data Output Setup to First SCKx Edge | 15                                                                                                                                                                                                                                                        | _                   | _    | ns    | _                  |

| SP40               | TDIV2scH,             | Setup Time of SDIx Data Input to          | 15                                                                                                                                                                                                                                                        | _                   | _    | ns    | VDD > 2.7V         |

|                    | TDIV2scL              | SCKx Edge                                 | 20                                                                                                                                                                                                                                                        | _                   | _    | ns    | VDD < 2.7V         |

| SP41               | TSCH2DIL,<br>TSCL2DIL | Hold Time of SDIx Data Input to SCKx Edge | 15                                                                                                                                                                                                                                                        | _                   | _    | ns    | VDD > 2.7V         |

|                    |                       |                                           | 20                                                                                                                                                                                                                                                        | _                   |      | ns    | VDD < 2.7V         |

- Note 1: These parameters are characterized, but not tested in manufacturing.

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- **3:** The minimum clock period for SCKx is 40 ns. Therefore, the clock generated in Master mode must not violate this specification.

- 4: Assumes 50 pF load on all SPIx pins.

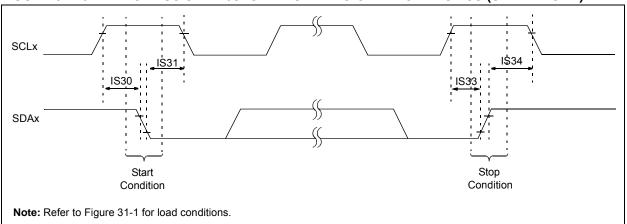

### FIGURE 31-16: I2Cx BUS START/STOP BITS TIMING CHARACTERISTICS (SLAVE MODE)

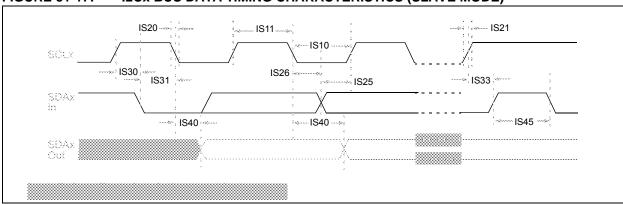

#### FIGURE 31-17: I2Cx BUS DATA TIMING CHARACTERISTICS (SLAVE MODE)

FIGURE 32-14: TYPICAL FRC FREQUENCY @ VDD = 3.3V

FIGURE 32-15: TYPICAL LPRC FREQUENCY @ VDD = 3.3V

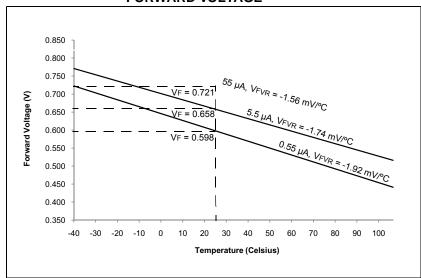

FIGURE 32-16: TYPICAL CTMU TEMPERATURE DIODE FORWARD VOLTAGE

| NVMDATA (Flash Program Data)57                      |

|-----------------------------------------------------|

| NVMKEY (Programming Unlock)56                       |

| NVMSRCADDR (Source Data Address)57                  |

| OCxCON (Output Compare x Control) 187               |

| OSCCON (Oscillator Control)76                       |

| PFABT (Prefetch Cache Abort Statistics)             |

| PMADDR (Parallel Port Address)219                   |

| PMAEN (Parallel Port Pin Enable)220                 |

|                                                     |

| PMCON (Parallel Port Control)                       |

| PMMODE (Parallel Port Mode)217                      |

| PMSTAT (Parallel Port Status (Slave Modes Only) 221 |

| REFOCON (Reference Oscillator Control)80            |

| REFOTRIM (Reference Oscillator Trim)82              |

| RPnR (Peripheral Pin Select Output)165              |

| RSWRST (Software Reset)62                           |

| RTCCON (RTC Control)225                             |

| RTCDATE (RTC Date Value)230                         |

| RTCTIME (RTC Time Value)229                         |

| SPIxCON (SPI Control)191                            |

| SPIxCON2 (SPI Control 2)194                         |

| SPIxSTAT (SPI Status)195                            |

| T1CON (Type A Timer Control)                        |

| TyCON (Type B Timer Central)                        |

| TxCON (Type B Timer Control)                        |

| U1ADDR (USB Address)                                |

| U1BDTP1 (USB BDT Page 1)133                         |

| U1BDTP2 (USB BDT Page 2)134                         |

| U1BDTP3 (USB BDT Page 3)134                         |

| U1CNFG1 (USB Configuration 1)135                    |

| U1CON (USB Control)129                              |

| U1EIE (USB Error Interrupt Enable)                  |

| U1EIR (USB Error Interrupt Status)125               |

| U1EP0-U1EP15 (USB Endpoint Control)                 |

| U1FRMH (USB Frame Number High)                      |

| U1FRML (USB Frame Number Low)131                    |

| U1IE (USB Interrupt Enable)124                      |

| U1IR (USB Interrupt)123                             |

| U10TGCON (USB OTG Control)123                       |

| U10TGIE (USB OTG Interrupt Enable)121               |

| UTOTGIE (USB OTG Interrupt Enable)                  |

| U1OTGIR (USB OTG Interrupt Status)118               |

| U1OTGSTAT (USB OTG Status)120                       |

| U1PWRC (USB Power Control)122                       |

| U1SOF (USB SOF Threshold)133                        |

| U1STAT (USB Status)128                              |

| U1TOK (USB Token)132                                |

| WDTCON (Watchdog Timer Control) 179                 |

| Resets                                              |

| Revision History                                    |

| RTCALRM (RTC ALARM Control)                         |

| · · · · · · · · · · · · · · · · · · ·               |

| S                                                   |

| Serial Peripheral Interface (SPI)                   |

| Software Simulator (MPLAB SIM)                      |

| Outware Simulator (INIT LAD SINI)                   |

| 1                                              |     |

|------------------------------------------------|-----|

| Timer1 Module                                  | 167 |

| Timer2/3, Timer4/5 Modules                     | 171 |

| Timing Diagrams                                |     |

| 10-Bit Analog-to-Digital Conversion            |     |

| (ASAM = 0, SSRC<2:0> = 000)                    | 320 |

| 10-Bit Analog-to-Digital Conversion (ASAM = 1, |     |

| SSRC<2:0> = 111, SAMC<4:0> = 00001)            | 321 |

| EJTAG                                          |     |

| External Clock                                 |     |

| I/O Characteristics                            |     |

| I2Cx Bus Data (Master Mode)                    |     |